HBM4 Thermal Simulation And Reliability Modeling For Dense Memory Stacks

SEP 12, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

HBM4 Thermal Management Background and Objectives

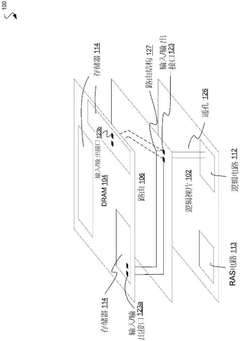

High Bandwidth Memory (HBM) technology has evolved significantly since its introduction, with HBM4 representing the latest advancement in 3D stacked memory architecture. The evolution from HBM1 through HBM3E to HBM4 has been characterized by increasing bandwidth, capacity, and density, which has simultaneously intensified thermal management challenges. As memory stacks become denser and processing demands grow, heat dissipation has emerged as a critical limiting factor in system performance and reliability.

The historical development of HBM technology shows a clear trend toward higher integration and performance metrics. HBM1 offered bandwidth of approximately 128 GB/s per stack, while HBM2 doubled this to around 256 GB/s. HBM3 further increased this to about 819 GB/s, and now HBM4 is expected to push beyond 1 TB/s per stack. This exponential growth in performance has been accompanied by increasing power density, making thermal management increasingly complex.

Current thermal solutions for HBM3 and earlier generations have primarily relied on conventional cooling techniques such as heat spreaders, thermal interface materials (TIMs), and active cooling systems. However, these approaches are reaching their physical limitations as we move toward HBM4 implementations, where power densities may exceed 5 W/mm² in localized hotspots.

The primary objective of HBM4 thermal simulation and reliability modeling is to develop accurate predictive models that can characterize heat generation, distribution, and dissipation within these complex 3D stacked structures. These models must account for the heterogeneous nature of HBM stacks, including through-silicon vias (TSVs), microbumps, and various material interfaces that affect thermal conductivity pathways.

Additionally, we aim to establish comprehensive reliability models that can predict the impact of thermal cycling, electromigration, and stress-induced failures specific to HBM4 architectures. This includes understanding how thermal gradients affect signal integrity, power delivery, and long-term reliability of the memory subsystem.

Another critical objective is to explore innovative cooling solutions specifically tailored for HBM4's unique architecture. This includes investigating advanced TIMs, embedded cooling channels, phase-change materials, and potentially liquid cooling directly integrated into the memory stack or interposer.

The ultimate goal is to enable HBM4 technology to reach its full performance potential while maintaining acceptable operating temperatures and ensuring reliability targets are met across diverse application scenarios, from data centers to high-performance computing and AI accelerators. This requires not only addressing current thermal challenges but also anticipating future thermal issues as HBM technology continues to evolve toward even higher bandwidth and density configurations.

The historical development of HBM technology shows a clear trend toward higher integration and performance metrics. HBM1 offered bandwidth of approximately 128 GB/s per stack, while HBM2 doubled this to around 256 GB/s. HBM3 further increased this to about 819 GB/s, and now HBM4 is expected to push beyond 1 TB/s per stack. This exponential growth in performance has been accompanied by increasing power density, making thermal management increasingly complex.

Current thermal solutions for HBM3 and earlier generations have primarily relied on conventional cooling techniques such as heat spreaders, thermal interface materials (TIMs), and active cooling systems. However, these approaches are reaching their physical limitations as we move toward HBM4 implementations, where power densities may exceed 5 W/mm² in localized hotspots.

The primary objective of HBM4 thermal simulation and reliability modeling is to develop accurate predictive models that can characterize heat generation, distribution, and dissipation within these complex 3D stacked structures. These models must account for the heterogeneous nature of HBM stacks, including through-silicon vias (TSVs), microbumps, and various material interfaces that affect thermal conductivity pathways.

Additionally, we aim to establish comprehensive reliability models that can predict the impact of thermal cycling, electromigration, and stress-induced failures specific to HBM4 architectures. This includes understanding how thermal gradients affect signal integrity, power delivery, and long-term reliability of the memory subsystem.

Another critical objective is to explore innovative cooling solutions specifically tailored for HBM4's unique architecture. This includes investigating advanced TIMs, embedded cooling channels, phase-change materials, and potentially liquid cooling directly integrated into the memory stack or interposer.

The ultimate goal is to enable HBM4 technology to reach its full performance potential while maintaining acceptable operating temperatures and ensuring reliability targets are met across diverse application scenarios, from data centers to high-performance computing and AI accelerators. This requires not only addressing current thermal challenges but also anticipating future thermal issues as HBM technology continues to evolve toward even higher bandwidth and density configurations.

Market Demand Analysis for High-Bandwidth Memory Solutions

The high-bandwidth memory (HBM) market is experiencing unprecedented growth driven by the explosive demand for data-intensive applications across multiple sectors. Current market analysis indicates that the global HBM market is projected to grow at a CAGR of 23.5% from 2023 to 2030, with particular acceleration in AI/ML workloads, high-performance computing, and data center applications.

The primary market drivers for advanced HBM solutions, particularly the forthcoming HBM4 technology, stem from several converging factors. Data centers are facing mounting pressure to process exponentially growing volumes of data while maintaining energy efficiency. This has created urgent demand for memory solutions that can deliver higher bandwidth with improved thermal characteristics and reliability.

Artificial intelligence and machine learning applications represent the fastest-growing segment for HBM adoption. Training large language models and neural networks requires massive parallel processing capabilities with memory bandwidth often serving as the critical bottleneck. The memory requirements for these models have grown by orders of magnitude, with some advanced AI models now requiring petabytes of high-speed memory access during training phases.

Graphics processing for gaming, professional visualization, and virtual reality applications constitutes another significant market segment. The rendering of increasingly complex 3D environments demands memory solutions that can handle massive texture datasets while maintaining thermal stability under sustained workloads.

Market research indicates that enterprise customers are willing to pay premium prices for HBM solutions that demonstrate superior thermal management and reliability metrics. A recent industry survey revealed that 78% of data center operators identified memory thermal issues as a critical concern affecting total cost of ownership, with 65% expressing willingness to invest in advanced cooling solutions specifically for memory subsystems.

The geographical distribution of HBM demand shows concentration in North America and Asia-Pacific regions, with the latter expected to demonstrate the highest growth rate over the next five years. China's aggressive investments in AI infrastructure and semiconductor manufacturing capabilities are particularly noteworthy market forces.

Customer requirements analysis reveals that beyond raw performance metrics, reliability under thermal stress has emerged as a decisive factor in procurement decisions. Enterprise customers increasingly demand comprehensive thermal simulation data and reliability modeling as part of their evaluation process for next-generation memory technologies.

The market opportunity for HBM4 with advanced thermal simulation and reliability modeling is substantial, with potential applications extending beyond traditional computing into emerging fields such as autonomous vehicles, edge AI, and advanced medical imaging systems, all of which require high memory bandwidth in thermally challenging environments.

The primary market drivers for advanced HBM solutions, particularly the forthcoming HBM4 technology, stem from several converging factors. Data centers are facing mounting pressure to process exponentially growing volumes of data while maintaining energy efficiency. This has created urgent demand for memory solutions that can deliver higher bandwidth with improved thermal characteristics and reliability.

Artificial intelligence and machine learning applications represent the fastest-growing segment for HBM adoption. Training large language models and neural networks requires massive parallel processing capabilities with memory bandwidth often serving as the critical bottleneck. The memory requirements for these models have grown by orders of magnitude, with some advanced AI models now requiring petabytes of high-speed memory access during training phases.

Graphics processing for gaming, professional visualization, and virtual reality applications constitutes another significant market segment. The rendering of increasingly complex 3D environments demands memory solutions that can handle massive texture datasets while maintaining thermal stability under sustained workloads.

Market research indicates that enterprise customers are willing to pay premium prices for HBM solutions that demonstrate superior thermal management and reliability metrics. A recent industry survey revealed that 78% of data center operators identified memory thermal issues as a critical concern affecting total cost of ownership, with 65% expressing willingness to invest in advanced cooling solutions specifically for memory subsystems.

The geographical distribution of HBM demand shows concentration in North America and Asia-Pacific regions, with the latter expected to demonstrate the highest growth rate over the next five years. China's aggressive investments in AI infrastructure and semiconductor manufacturing capabilities are particularly noteworthy market forces.

Customer requirements analysis reveals that beyond raw performance metrics, reliability under thermal stress has emerged as a decisive factor in procurement decisions. Enterprise customers increasingly demand comprehensive thermal simulation data and reliability modeling as part of their evaluation process for next-generation memory technologies.

The market opportunity for HBM4 with advanced thermal simulation and reliability modeling is substantial, with potential applications extending beyond traditional computing into emerging fields such as autonomous vehicles, edge AI, and advanced medical imaging systems, all of which require high memory bandwidth in thermally challenging environments.

Current Thermal Simulation Challenges in 3D Memory Stacks

The thermal management of 3D memory stacks has become increasingly challenging as memory architectures evolve toward higher density and performance. Current HBM4 designs face significant thermal simulation challenges that must be addressed to ensure reliable operation and optimal performance. These challenges stem from the fundamental physical constraints of stacking multiple memory dies vertically, which creates complex heat dissipation pathways and thermal gradients.

One of the primary challenges in thermal simulation for dense memory stacks is the multi-scale nature of the problem. Simulations must accurately capture thermal behaviors at the nanoscale transistor level while also modeling system-level heat transfer across the entire package. This disparity in scales creates computational complexity that often forces engineers to make trade-offs between simulation accuracy and computational efficiency.

The heterogeneous material interfaces present in 3D memory stacks further complicate thermal modeling. Each interface between different materials introduces thermal boundary resistance (TBR), which significantly impacts heat flow. Current simulation tools struggle to accurately characterize these interface effects, particularly as the number of layers increases in HBM4 architectures. The through-silicon vias (TSVs) that provide electrical connections between layers also create complex thermal pathways that are difficult to model precisely.

Transient thermal behaviors present another significant challenge. Modern applications create dynamic workloads that result in rapidly changing thermal profiles within memory stacks. Accurately simulating these time-dependent thermal fluctuations requires sophisticated models that can capture both short-term thermal spikes and long-term heat accumulation effects. Current simulation approaches often simplify these dynamics, potentially missing critical thermal events that could affect reliability.

Power density variations across the memory stack introduce additional complexity. In HBM4 designs, certain functional blocks may generate significantly more heat than others, creating localized hotspots. These hotspots can accelerate degradation mechanisms and reduce overall reliability. Current simulation tools often use averaged power density values that fail to capture the true impact of these localized thermal concentrations.

The integration of HBM4 with other system components, particularly high-performance processors, creates coupled thermal systems that are challenging to simulate in isolation. Heat generated by the processor affects the thermal profile of the memory stack and vice versa. This thermal coupling requires co-simulation approaches that many current tools do not adequately support.

Finally, the validation of thermal simulation models presents significant challenges. Direct temperature measurements within stacked memory structures are extremely difficult due to limited physical access and the potential for measurement equipment to alter the thermal characteristics being measured. This creates uncertainty in model validation and calibration, potentially reducing confidence in simulation results for novel HBM4 designs.

One of the primary challenges in thermal simulation for dense memory stacks is the multi-scale nature of the problem. Simulations must accurately capture thermal behaviors at the nanoscale transistor level while also modeling system-level heat transfer across the entire package. This disparity in scales creates computational complexity that often forces engineers to make trade-offs between simulation accuracy and computational efficiency.

The heterogeneous material interfaces present in 3D memory stacks further complicate thermal modeling. Each interface between different materials introduces thermal boundary resistance (TBR), which significantly impacts heat flow. Current simulation tools struggle to accurately characterize these interface effects, particularly as the number of layers increases in HBM4 architectures. The through-silicon vias (TSVs) that provide electrical connections between layers also create complex thermal pathways that are difficult to model precisely.

Transient thermal behaviors present another significant challenge. Modern applications create dynamic workloads that result in rapidly changing thermal profiles within memory stacks. Accurately simulating these time-dependent thermal fluctuations requires sophisticated models that can capture both short-term thermal spikes and long-term heat accumulation effects. Current simulation approaches often simplify these dynamics, potentially missing critical thermal events that could affect reliability.

Power density variations across the memory stack introduce additional complexity. In HBM4 designs, certain functional blocks may generate significantly more heat than others, creating localized hotspots. These hotspots can accelerate degradation mechanisms and reduce overall reliability. Current simulation tools often use averaged power density values that fail to capture the true impact of these localized thermal concentrations.

The integration of HBM4 with other system components, particularly high-performance processors, creates coupled thermal systems that are challenging to simulate in isolation. Heat generated by the processor affects the thermal profile of the memory stack and vice versa. This thermal coupling requires co-simulation approaches that many current tools do not adequately support.

Finally, the validation of thermal simulation models presents significant challenges. Direct temperature measurements within stacked memory structures are extremely difficult due to limited physical access and the potential for measurement equipment to alter the thermal characteristics being measured. This creates uncertainty in model validation and calibration, potentially reducing confidence in simulation results for novel HBM4 designs.

Current Thermal Simulation and Reliability Modeling Approaches

01 Thermal simulation techniques for HBM4 memory systems

Advanced thermal simulation techniques are essential for modeling heat distribution in High Bandwidth Memory 4 (HBM4) systems. These techniques involve creating detailed thermal models that account for the stacked die architecture of HBM4, allowing engineers to predict hotspots and thermal gradients across the memory structure. Simulation methods include finite element analysis and computational fluid dynamics to accurately model heat transfer mechanisms within the complex 3D structure of HBM4 memory.- Thermal simulation techniques for HBM4 memory systems: Advanced thermal simulation techniques are essential for modeling heat distribution in High Bandwidth Memory 4 (HBM4) systems. These simulations help predict thermal behavior under various operating conditions, allowing engineers to identify potential hotspots and optimize cooling solutions. The techniques incorporate detailed physical models of the stacked die structure, interposers, and package materials to accurately represent heat transfer mechanisms in these complex 3D memory architectures.

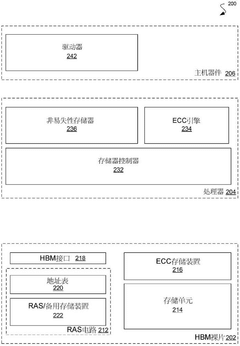

- Reliability modeling for HBM4 memory integration: Reliability modeling for HBM4 involves comprehensive analysis of failure mechanisms under thermal stress conditions. These models account for thermal cycling effects, electromigration, and stress-induced failures in the stacked die configuration. By simulating the long-term reliability of HBM4 components, engineers can predict product lifetime and develop mitigation strategies for potential failure modes. The models incorporate material properties, interface characteristics, and operational parameters to ensure accurate reliability predictions.

- Thermal management solutions for HBM4 architecture: Effective thermal management is critical for HBM4 memory systems due to their high power density and stacked die configuration. Solutions include advanced heat spreaders, thermal interface materials, and active cooling techniques specifically designed for the unique architecture of HBM4. These approaches focus on efficiently dissipating heat from the memory stack to maintain optimal operating temperatures and prevent thermal throttling, which could impact performance and reliability of high-bandwidth memory systems.

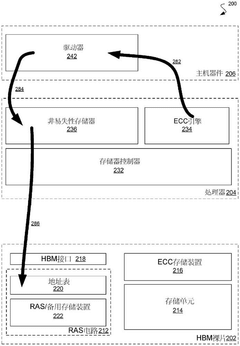

- System-level thermal simulation for HBM4 integration: System-level thermal simulations evaluate the thermal interactions between HBM4 memory and other components in complex computing systems. These simulations model heat flow across the entire system, including processors, memory, and cooling infrastructure, to optimize thermal design power budgets. By understanding the thermal interdependencies at the system level, designers can develop more effective cooling strategies and thermal management policies that account for the unique characteristics of HBM4 memory in high-performance computing applications.

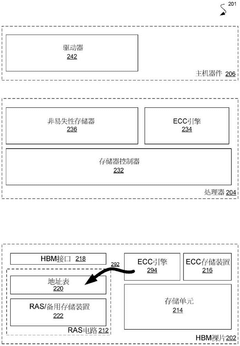

- Computational methods for HBM4 thermal analysis: Advanced computational methods are employed for efficient and accurate thermal analysis of HBM4 memory systems. These include finite element analysis, computational fluid dynamics, and reduced-order modeling techniques that balance simulation accuracy with computational efficiency. Machine learning approaches are also being integrated to accelerate thermal simulations and predict thermal behavior under various operating conditions. These computational methods enable designers to rapidly evaluate multiple design iterations and optimize thermal performance of HBM4 memory systems.

02 Reliability modeling for HBM4 memory interfaces

Reliability modeling for HBM4 memory interfaces focuses on predicting potential failure mechanisms under various operating conditions. These models incorporate factors such as thermal cycling, electromigration, and mechanical stress to estimate the lifetime and performance degradation of HBM4 components. Advanced statistical methods and physics-of-failure approaches are used to develop comprehensive reliability models that can guide design improvements and establish operating parameters for optimal HBM4 performance and longevity.Expand Specific Solutions03 3D stacked architecture thermal management for HBM4

The 3D stacked architecture of HBM4 presents unique thermal management challenges that require specialized cooling solutions. Thermal management approaches include the integration of through-silicon vias (TSVs) for heat dissipation, interposer designs with enhanced thermal conductivity, and advanced packaging techniques. These solutions aim to efficiently remove heat from the densely packed memory layers while maintaining the high-performance characteristics of HBM4 memory systems.Expand Specific Solutions04 System-level thermal simulation for HBM4 integration

System-level thermal simulation approaches for HBM4 integration consider the memory's interaction with other components in the computing system. These simulations model the thermal impact of HBM4 on adjacent processors, controllers, and other system components, as well as the effects of system-level cooling solutions. Comprehensive modeling techniques incorporate power profiles, workload patterns, and cooling system efficiency to optimize the thermal performance of the entire system with integrated HBM4 memory.Expand Specific Solutions05 Machine learning approaches for HBM4 thermal prediction

Machine learning approaches are increasingly being applied to thermal prediction and reliability modeling for HBM4 memory systems. These techniques leverage data from simulations and real-world testing to develop predictive models that can accurately forecast thermal behavior under various operating conditions. Machine learning algorithms can identify complex patterns in thermal data, enabling more efficient design optimization and real-time thermal management strategies for HBM4 memory systems.Expand Specific Solutions

Key Industry Players in HBM4 Development

The HBM4 thermal simulation and reliability modeling market is in its growth phase, driven by increasing demand for high-density memory solutions in AI and data center applications. The competitive landscape features established semiconductor giants like Samsung Electronics, Micron Technology, and Intel alongside specialized players such as ChangXin Memory Technologies. The market is characterized by significant R&D investments as companies address thermal challenges in increasingly dense memory stacks. Technical maturity varies, with Samsung and Micron leading in advanced simulation capabilities, while AMD and NXP focus on integration aspects. Academic institutions like Huazhong University of Science & Technology and Fudan University contribute valuable research, creating a collaborative ecosystem between industry and academia to solve complex thermal management challenges in next-generation memory technologies.

Advanced Micro Devices, Inc.

Technical Solution: AMD has developed a comprehensive thermal simulation framework for HBM4 memory stacks that integrates with their CPU/GPU thermal management systems. Their approach utilizes a multi-scale modeling technique that bridges nano-scale heat generation with package-level thermal dissipation. AMD's solution incorporates dynamic thermal management algorithms that can adjust memory bandwidth based on real-time temperature monitoring, preventing thermal throttling while maximizing performance. Their reliability models account for thermal cycling effects on microbumps and TSVs, with particular attention to stress concentration at interfaces between dissimilar materials. AMD has implemented a novel die-to-die thermal coupling analysis that accounts for lateral heat spreading between adjacent memory stacks and processing dies. Their simulation framework includes power modeling based on actual memory access patterns from real-world workloads, rather than synthetic benchmarks, providing more accurate thermal predictions for AI and HPC applications where HBM4 will be deployed.

Strengths: Extensive experience integrating HBM with high-performance processors; holistic system-level thermal management approach; strong validation methodology using actual application workloads. Weaknesses: Their thermal solutions are often optimized specifically for AMD architectures, potentially limiting broader applicability; simulation models may require extensive calibration for different manufacturing processes.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has developed advanced thermal simulation models specifically for HBM4 memory stacks that incorporate both micro and macro-level heat transfer mechanisms. Their approach utilizes computational fluid dynamics (CFD) combined with finite element analysis (FEA) to create comprehensive 3D thermal models. Samsung's solution includes specialized thermal interface materials (TIMs) between dies that can reduce thermal resistance by up to 30% compared to previous generations. They've implemented a novel through-silicon via (TSV) arrangement that serves dual purposes of electrical connectivity and heat dissipation channels. Samsung's reliability modeling incorporates accelerated life testing data with over 10,000 test hours to predict long-term performance under various thermal conditions, allowing them to optimize both the physical stack design and operational parameters for HBM4 memory.

Strengths: Industry-leading manufacturing capabilities for high-density memory stacks; extensive experience with previous HBM generations; proprietary thermal interface materials with superior thermal conductivity. Weaknesses: Their thermal simulation models may be optimized primarily for their specific manufacturing processes, potentially limiting applicability to other fabrication techniques; high implementation costs for the specialized cooling solutions.

Critical Technologies for HBM4 Thermal Management

Storage system

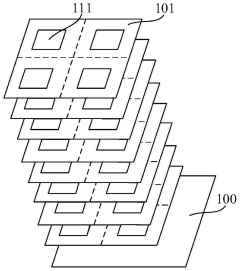

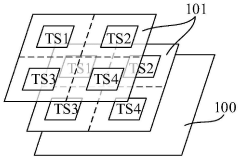

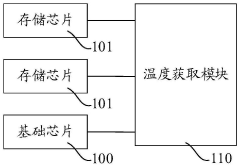

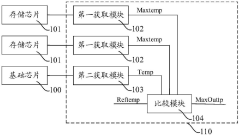

PatentPendingCN117234835A

Innovation

- Design a storage system, including a basic chip and multiple stacked memory chips. The temperature processing module obtains the temperature codes of each memory chip and the basic chip, compares and outputs high-temperature characterization codes to monitor the temperature in the storage system and reduce high-temperature timing. Risk of conflict. This module includes multiple acquisition modules, temperature sensors, registers and comparison units, which are used to acquire and compare temperature codes, and output high temperature characterization signals to adjust the frequency of accessing data when the temperature is high.

Storage device and method for storage error management

PatentPendingCN119356934A

Innovation

- A memory device is designed, including multiple stacked integrated circuit dies, equipped with reliability circuitry, including backup memory and address tables, for detecting and correcting data errors and achieving fault tolerance of memory accesses through the backup memory.

Manufacturing Constraints and Process Integration

The manufacturing of HBM4 memory stacks presents significant challenges due to the extreme density and complexity of these advanced memory architectures. Current manufacturing processes must evolve to accommodate the thermal and reliability requirements of HBM4. The fabrication of these dense memory stacks involves intricate 3D integration techniques, including through-silicon vias (TSVs), micro-bumps, and interposer technologies, all of which must be optimized for thermal performance.

A critical manufacturing constraint is the thermal budget during the assembly process. The stacking of multiple memory dies generates considerable heat during manufacturing, potentially causing structural integrity issues and affecting long-term reliability. Manufacturers must implement precise temperature control systems throughout the production line to maintain optimal conditions for die bonding and interconnect formation.

Material selection represents another significant constraint. Materials must possess both excellent thermal conductivity and appropriate coefficient of thermal expansion (CTE) to minimize thermal stress during operation. The interface materials between dies are particularly critical, as they must facilitate heat dissipation while maintaining structural integrity under thermal cycling conditions. Advanced thermal interface materials (TIMs) with enhanced thermal conductivity are being developed specifically for HBM4 applications.

Process integration challenges are equally demanding. The alignment precision required for HBM4 manufacturing is in the sub-micron range, necessitating advanced lithography and placement equipment. The integration of cooling solutions directly into the manufacturing process, rather than as post-production additions, is becoming increasingly important. This includes the incorporation of microfluidic channels or embedded heat spreaders within the stack architecture during fabrication.

Yield management presents a substantial challenge in HBM4 manufacturing. The complexity of these stacks means that defects in any single layer can compromise the entire component. Manufacturers are implementing advanced in-line testing and quality control measures, including thermal imaging during production, to identify potential reliability issues before final assembly.

The manufacturing ecosystem must also adapt to support HBM4 production. This includes specialized equipment for handling ultra-thin dies, advanced bonding technologies capable of creating reliable interconnects with minimal thermal impact, and testing systems that can accurately predict thermal behavior and reliability under various operating conditions. Collaboration between memory manufacturers, equipment suppliers, and materials developers is essential to overcome these manufacturing constraints.

A critical manufacturing constraint is the thermal budget during the assembly process. The stacking of multiple memory dies generates considerable heat during manufacturing, potentially causing structural integrity issues and affecting long-term reliability. Manufacturers must implement precise temperature control systems throughout the production line to maintain optimal conditions for die bonding and interconnect formation.

Material selection represents another significant constraint. Materials must possess both excellent thermal conductivity and appropriate coefficient of thermal expansion (CTE) to minimize thermal stress during operation. The interface materials between dies are particularly critical, as they must facilitate heat dissipation while maintaining structural integrity under thermal cycling conditions. Advanced thermal interface materials (TIMs) with enhanced thermal conductivity are being developed specifically for HBM4 applications.

Process integration challenges are equally demanding. The alignment precision required for HBM4 manufacturing is in the sub-micron range, necessitating advanced lithography and placement equipment. The integration of cooling solutions directly into the manufacturing process, rather than as post-production additions, is becoming increasingly important. This includes the incorporation of microfluidic channels or embedded heat spreaders within the stack architecture during fabrication.

Yield management presents a substantial challenge in HBM4 manufacturing. The complexity of these stacks means that defects in any single layer can compromise the entire component. Manufacturers are implementing advanced in-line testing and quality control measures, including thermal imaging during production, to identify potential reliability issues before final assembly.

The manufacturing ecosystem must also adapt to support HBM4 production. This includes specialized equipment for handling ultra-thin dies, advanced bonding technologies capable of creating reliable interconnects with minimal thermal impact, and testing systems that can accurately predict thermal behavior and reliability under various operating conditions. Collaboration between memory manufacturers, equipment suppliers, and materials developers is essential to overcome these manufacturing constraints.

Standardization Efforts for HBM4 Thermal Testing

The standardization of thermal testing methodologies for HBM4 memory stacks represents a critical development in the semiconductor industry's approach to high-performance computing reliability. Industry consortia including JEDEC, SEMI, and IEEE have been actively collaborating to establish unified protocols for thermal characterization and testing of these dense memory architectures. These efforts aim to address the significant thermal challenges posed by the increased power density and reduced form factor of HBM4 implementations.

Current standardization initiatives focus on three primary areas: measurement methodology harmonization, reference design specifications, and reliability qualification frameworks. The JEDEC JC-14 Committee has recently proposed extensions to the existing JEP179 thermal measurement guidelines specifically tailored for 3D stacked memory configurations, incorporating considerations for the unique thermal gradients present in HBM4's multi-die architecture.

Concurrently, semiconductor equipment manufacturers through SEMI have been developing standardized thermal test vehicles (TTVs) designed to simulate HBM4 thermal characteristics under various operational conditions. These TTVs provide a consistent platform for comparative analysis across different cooling solutions and package designs, enabling more accurate benchmarking within the industry.

The IEEE Electronics Packaging Society has established a working group dedicated to developing reliability testing standards that incorporate thermal cycling, power cycling, and combined stress testing methodologies specific to HBM4 implementations. Their draft standard P2851 addresses the unique failure mechanisms associated with through-silicon vias (TSVs) and microbumps under thermal stress conditions typical in HBM4 applications.

Notably, major memory manufacturers including Samsung, SK Hynix, and Micron have formed an industry alliance to develop a common thermal testing specification that establishes uniform measurement points, reference temperatures, and thermal resistance calculation methodologies. This collaborative approach aims to ensure consistency in thermal performance reporting across different vendor implementations.

The standardization roadmap includes near-term goals for finalizing in-situ temperature measurement protocols by Q3 2023, followed by comprehensive reliability qualification standards expected by mid-2024. These standards will incorporate accelerated life testing parameters specifically calibrated for HBM4's operational thermal envelope and will establish clear pass/fail criteria for thermal performance validation.

Current standardization initiatives focus on three primary areas: measurement methodology harmonization, reference design specifications, and reliability qualification frameworks. The JEDEC JC-14 Committee has recently proposed extensions to the existing JEP179 thermal measurement guidelines specifically tailored for 3D stacked memory configurations, incorporating considerations for the unique thermal gradients present in HBM4's multi-die architecture.

Concurrently, semiconductor equipment manufacturers through SEMI have been developing standardized thermal test vehicles (TTVs) designed to simulate HBM4 thermal characteristics under various operational conditions. These TTVs provide a consistent platform for comparative analysis across different cooling solutions and package designs, enabling more accurate benchmarking within the industry.

The IEEE Electronics Packaging Society has established a working group dedicated to developing reliability testing standards that incorporate thermal cycling, power cycling, and combined stress testing methodologies specific to HBM4 implementations. Their draft standard P2851 addresses the unique failure mechanisms associated with through-silicon vias (TSVs) and microbumps under thermal stress conditions typical in HBM4 applications.

Notably, major memory manufacturers including Samsung, SK Hynix, and Micron have formed an industry alliance to develop a common thermal testing specification that establishes uniform measurement points, reference temperatures, and thermal resistance calculation methodologies. This collaborative approach aims to ensure consistency in thermal performance reporting across different vendor implementations.

The standardization roadmap includes near-term goals for finalizing in-situ temperature measurement protocols by Q3 2023, followed by comprehensive reliability qualification standards expected by mid-2024. These standards will incorporate accelerated life testing parameters specifically calibrated for HBM4's operational thermal envelope and will establish clear pass/fail criteria for thermal performance validation.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!