HBM4 Lifecycle Management: Revision Control And Compatibility

SEP 12, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

HBM4 Technology Evolution and Objectives

High-Bandwidth Memory (HBM) technology has evolved significantly since its inception, with HBM4 representing the latest advancement in this critical memory architecture. The evolution of HBM technology has been driven by increasing demands for higher bandwidth, greater capacity, improved power efficiency, and enhanced reliability in data-intensive applications such as artificial intelligence, high-performance computing, and graphics processing.

The journey began with the first-generation HBM in 2013, followed by HBM2 in 2016, which doubled the bandwidth. HBM2E emerged in 2018 with further improvements, and HBM3 in 2021 brought substantial performance gains. Now, HBM4 stands as the culmination of this evolutionary path, designed to address the exponential growth in data processing requirements across multiple industries.

HBM4 aims to achieve unprecedented memory bandwidth exceeding 1.2 TB/s per stack, representing a significant leap from HBM3's capabilities. This advancement is crucial for supporting next-generation AI training models, which have grown from billions to trillions of parameters, demanding exponentially more memory bandwidth and capacity.

A key objective for HBM4 technology is establishing robust lifecycle management protocols, particularly in revision control and compatibility frameworks. As HBM implementations become more complex and widespread across diverse applications, maintaining backward compatibility while enabling forward innovation presents a significant technical challenge.

The technology targets improved thermal management capabilities, addressing one of the primary limitations in previous HBM generations. By enhancing heat dissipation efficiency, HBM4 aims to maintain optimal performance under intensive workloads without thermal throttling.

Another critical objective is standardizing the integration process with various computing platforms. This includes developing consistent interfaces and protocols that facilitate seamless adoption across different hardware ecosystems, reducing implementation barriers and accelerating market penetration.

HBM4 also focuses on enhancing reliability through advanced error detection and correction mechanisms. As memory requirements scale up, maintaining data integrity becomes increasingly challenging, necessitating more sophisticated approaches to error management.

The technology evolution path includes significant manufacturing improvements aimed at increasing yield rates and reducing production costs. These advancements are essential for broader market adoption, as current HBM solutions remain relatively expensive compared to traditional memory technologies.

Looking forward, HBM4 development objectives include establishing clear specifications for future revisions and updates, ensuring that lifecycle management becomes an integral part of the technology's architecture rather than an afterthought.

The journey began with the first-generation HBM in 2013, followed by HBM2 in 2016, which doubled the bandwidth. HBM2E emerged in 2018 with further improvements, and HBM3 in 2021 brought substantial performance gains. Now, HBM4 stands as the culmination of this evolutionary path, designed to address the exponential growth in data processing requirements across multiple industries.

HBM4 aims to achieve unprecedented memory bandwidth exceeding 1.2 TB/s per stack, representing a significant leap from HBM3's capabilities. This advancement is crucial for supporting next-generation AI training models, which have grown from billions to trillions of parameters, demanding exponentially more memory bandwidth and capacity.

A key objective for HBM4 technology is establishing robust lifecycle management protocols, particularly in revision control and compatibility frameworks. As HBM implementations become more complex and widespread across diverse applications, maintaining backward compatibility while enabling forward innovation presents a significant technical challenge.

The technology targets improved thermal management capabilities, addressing one of the primary limitations in previous HBM generations. By enhancing heat dissipation efficiency, HBM4 aims to maintain optimal performance under intensive workloads without thermal throttling.

Another critical objective is standardizing the integration process with various computing platforms. This includes developing consistent interfaces and protocols that facilitate seamless adoption across different hardware ecosystems, reducing implementation barriers and accelerating market penetration.

HBM4 also focuses on enhancing reliability through advanced error detection and correction mechanisms. As memory requirements scale up, maintaining data integrity becomes increasingly challenging, necessitating more sophisticated approaches to error management.

The technology evolution path includes significant manufacturing improvements aimed at increasing yield rates and reducing production costs. These advancements are essential for broader market adoption, as current HBM solutions remain relatively expensive compared to traditional memory technologies.

Looking forward, HBM4 development objectives include establishing clear specifications for future revisions and updates, ensuring that lifecycle management becomes an integral part of the technology's architecture rather than an afterthought.

Market Demand Analysis for HBM4 Memory Solutions

The global market for High Bandwidth Memory (HBM) solutions is experiencing unprecedented growth, driven primarily by the explosive expansion of artificial intelligence (AI) and machine learning (ML) applications. As these technologies continue to evolve and demand increasingly complex computational capabilities, the need for high-performance memory solutions has become critical. HBM4, as the next generation of high-bandwidth memory technology, is positioned to address these escalating requirements.

Current market projections indicate that the HBM market is expected to grow at a compound annual growth rate (CAGR) of over 30% through 2028, with particular acceleration in data center, high-performance computing (HPC), and AI training sectors. This growth trajectory is significantly steeper than previous generations of memory technologies, reflecting the intensifying demand for computational power across industries.

The primary market drivers for HBM4 adoption include the increasing complexity of AI models, which have grown from billions to trillions of parameters in just a few years. This exponential growth in model size necessitates memory solutions that can provide both higher bandwidth and larger capacity while maintaining energy efficiency. Additionally, the proliferation of real-time AI applications in edge computing environments is creating demand for more compact yet powerful memory solutions.

Enterprise data centers represent the largest market segment for HBM4, as organizations increasingly deploy AI infrastructure to process vast amounts of data. Cloud service providers are particularly aggressive in adopting cutting-edge memory technologies to maintain competitive advantages in offering AI-as-a-Service platforms. The hyperscaler market alone is projected to account for approximately 40% of HBM4 demand in the initial years following release.

Beyond AI applications, HBM4 is seeing growing interest from the scientific computing community, particularly in fields such as climate modeling, genomics, and quantum physics simulation. These applications require processing enormous datasets with minimal latency, making HBM4's performance characteristics especially valuable.

From a geographical perspective, North America and East Asia continue to dominate the market demand for advanced memory solutions, with emerging interest from European research institutions and technology companies. The concentration of semiconductor manufacturing capabilities in East Asia, particularly Taiwan and South Korea, also influences regional adoption patterns and supply chain dynamics.

Customer surveys indicate that lifecycle management capabilities, including revision control and backward compatibility, rank among the top five concerns for potential HBM4 adopters. This reflects the significant investments organizations make in memory-intensive infrastructure and their need to protect these investments through manageable upgrade paths and extended support lifecycles.

Current market projections indicate that the HBM market is expected to grow at a compound annual growth rate (CAGR) of over 30% through 2028, with particular acceleration in data center, high-performance computing (HPC), and AI training sectors. This growth trajectory is significantly steeper than previous generations of memory technologies, reflecting the intensifying demand for computational power across industries.

The primary market drivers for HBM4 adoption include the increasing complexity of AI models, which have grown from billions to trillions of parameters in just a few years. This exponential growth in model size necessitates memory solutions that can provide both higher bandwidth and larger capacity while maintaining energy efficiency. Additionally, the proliferation of real-time AI applications in edge computing environments is creating demand for more compact yet powerful memory solutions.

Enterprise data centers represent the largest market segment for HBM4, as organizations increasingly deploy AI infrastructure to process vast amounts of data. Cloud service providers are particularly aggressive in adopting cutting-edge memory technologies to maintain competitive advantages in offering AI-as-a-Service platforms. The hyperscaler market alone is projected to account for approximately 40% of HBM4 demand in the initial years following release.

Beyond AI applications, HBM4 is seeing growing interest from the scientific computing community, particularly in fields such as climate modeling, genomics, and quantum physics simulation. These applications require processing enormous datasets with minimal latency, making HBM4's performance characteristics especially valuable.

From a geographical perspective, North America and East Asia continue to dominate the market demand for advanced memory solutions, with emerging interest from European research institutions and technology companies. The concentration of semiconductor manufacturing capabilities in East Asia, particularly Taiwan and South Korea, also influences regional adoption patterns and supply chain dynamics.

Customer surveys indicate that lifecycle management capabilities, including revision control and backward compatibility, rank among the top five concerns for potential HBM4 adopters. This reflects the significant investments organizations make in memory-intensive infrastructure and their need to protect these investments through manageable upgrade paths and extended support lifecycles.

HBM4 Technical Challenges and Constraints

The development of HBM4 (High Bandwidth Memory 4) faces several significant technical challenges and constraints that must be addressed to ensure successful implementation and market adoption. One of the primary challenges is the thermal management of these high-density memory stacks. As HBM4 increases in capacity and performance compared to previous generations, the heat generated during operation intensifies substantially, requiring advanced cooling solutions that can effectively dissipate heat without compromising the compact form factor that makes HBM attractive.

Signal integrity presents another critical challenge, particularly as data rates continue to climb. The high-speed interfaces in HBM4 must maintain clean signal transmission across increasingly complex interconnects, with potential for signal degradation, crosstalk, and electromagnetic interference becoming more pronounced. Engineers must develop sophisticated signal conditioning techniques and improved materials to mitigate these issues.

Power delivery and management represent significant constraints in HBM4 design. The memory must deliver unprecedented bandwidth while maintaining reasonable power consumption profiles. This requires innovations in power distribution networks, voltage regulation, and dynamic power management capabilities that can adjust performance based on workload demands.

Manufacturing complexity also poses substantial challenges. The 3D stacking process for HBM4 involves intricate through-silicon via (TSV) technology and micro-bump connections that demand extremely precise alignment and bonding. Yield rates for these complex structures directly impact production costs and market viability.

Testing and validation procedures become increasingly difficult with each new HBM generation. The dense integration and high pin count make comprehensive testing challenging, requiring new methodologies and equipment to ensure reliability and performance consistency across manufactured units.

Interoperability with various host systems presents another constraint. HBM4 must function seamlessly with different processor architectures, system designs, and software environments, necessitating robust standardization efforts and compatibility testing.

Cost considerations remain a persistent constraint. The advanced manufacturing processes, specialized materials, and complex integration requirements contribute to higher production costs compared to conventional memory technologies. Finding the balance between performance improvements and cost-effectiveness is crucial for market adoption.

Finally, reliability and longevity concerns must be addressed. The dense integration and advanced packaging techniques introduce new potential failure modes that must be thoroughly understood and mitigated to ensure HBM4 can meet enterprise-grade reliability requirements across diverse operating conditions and throughout its expected service life.

Signal integrity presents another critical challenge, particularly as data rates continue to climb. The high-speed interfaces in HBM4 must maintain clean signal transmission across increasingly complex interconnects, with potential for signal degradation, crosstalk, and electromagnetic interference becoming more pronounced. Engineers must develop sophisticated signal conditioning techniques and improved materials to mitigate these issues.

Power delivery and management represent significant constraints in HBM4 design. The memory must deliver unprecedented bandwidth while maintaining reasonable power consumption profiles. This requires innovations in power distribution networks, voltage regulation, and dynamic power management capabilities that can adjust performance based on workload demands.

Manufacturing complexity also poses substantial challenges. The 3D stacking process for HBM4 involves intricate through-silicon via (TSV) technology and micro-bump connections that demand extremely precise alignment and bonding. Yield rates for these complex structures directly impact production costs and market viability.

Testing and validation procedures become increasingly difficult with each new HBM generation. The dense integration and high pin count make comprehensive testing challenging, requiring new methodologies and equipment to ensure reliability and performance consistency across manufactured units.

Interoperability with various host systems presents another constraint. HBM4 must function seamlessly with different processor architectures, system designs, and software environments, necessitating robust standardization efforts and compatibility testing.

Cost considerations remain a persistent constraint. The advanced manufacturing processes, specialized materials, and complex integration requirements contribute to higher production costs compared to conventional memory technologies. Finding the balance between performance improvements and cost-effectiveness is crucial for market adoption.

Finally, reliability and longevity concerns must be addressed. The dense integration and advanced packaging techniques introduce new potential failure modes that must be thoroughly understood and mitigated to ensure HBM4 can meet enterprise-grade reliability requirements across diverse operating conditions and throughout its expected service life.

Current HBM4 Revision Control Methodologies

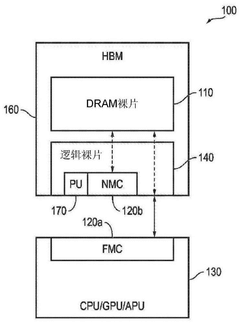

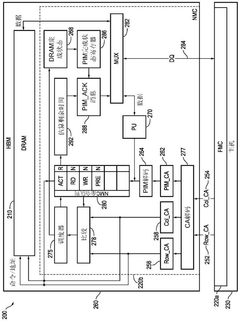

01 HBM4 Memory Architecture and Configuration Management

High Bandwidth Memory 4 (HBM4) architecture involves specific configuration management techniques to ensure optimal performance. This includes memory stack arrangements, interface protocols, and bandwidth optimization methods. The architecture supports revision control through configurable parameters that can be adjusted based on system requirements. These configurations can be stored and managed to maintain compatibility across different versions of HBM4 implementations.- HBM4 version control and compatibility management: High Bandwidth Memory 4 (HBM4) requires robust version control systems to manage compatibility between different iterations and implementations. These systems track changes, ensure backward compatibility with previous HBM versions, and maintain documentation of modifications. Version control frameworks help manage the complex memory architecture specifications across different hardware generations while ensuring interoperability between components from various manufacturers.

- Memory interface standardization for HBM4: Standardization of memory interfaces is crucial for HBM4 compatibility across different platforms. This involves creating uniform protocols for communication between HBM4 modules and host systems, establishing consistent electrical specifications, and defining standard physical connections. These standardized interfaces ensure that HBM4 memory can be integrated into various computing environments while maintaining performance characteristics and functional compatibility.

- HBM4 configuration management and testing: Configuration management systems for HBM4 memory ensure proper initialization, operation, and testing across different hardware environments. These systems include automated testing frameworks to verify compatibility, tools for managing memory timing parameters, and methods for detecting and resolving configuration conflicts. Proper configuration management is essential for maintaining stability and performance when integrating HBM4 into complex computing systems.

- HBM4 firmware and software update mechanisms: Firmware and software update mechanisms for HBM4 memory systems enable the deployment of performance improvements, bug fixes, and compatibility enhancements without hardware replacement. These mechanisms include secure update protocols, rollback capabilities for failed updates, and version verification systems. Proper update management ensures that HBM4 memory can adapt to evolving system requirements while maintaining compatibility with existing hardware and software environments.

- HBM4 cross-platform integration and interoperability: Cross-platform integration solutions for HBM4 memory address compatibility challenges across different computing architectures and operating systems. These solutions include abstraction layers that hide hardware-specific details, translation mechanisms for memory addressing schemes, and adaptive interfaces that adjust to different host capabilities. Such integration approaches ensure that HBM4 memory can function effectively across diverse computing environments while maintaining consistent performance characteristics.

02 Version Control Systems for HBM4 Firmware

Specialized version control systems are implemented for managing HBM4 firmware updates and revisions. These systems track changes to memory controller firmware, ensuring backward compatibility with previous versions while enabling new features. The version control mechanisms include metadata tagging, revision history tracking, and compatibility matrices that define which firmware versions work with specific hardware implementations of HBM4 technology.Expand Specific Solutions03 HBM4 Compatibility Layer Implementation

A compatibility layer is implemented to ensure HBM4 works with various host systems and previous memory generations. This layer includes protocol translation, timing adjustments, and signal integrity management to maintain interoperability. The compatibility layer can be dynamically configured to accommodate different system requirements and hardware configurations, allowing HBM4 to function in diverse computing environments while maintaining performance advantages.Expand Specific Solutions04 Power Management and Thermal Control for HBM4

Advanced power management and thermal control mechanisms are essential for HBM4 revision control. These systems monitor and adjust power consumption based on workload demands and thermal conditions, ensuring stable operation across different revisions. The power management framework includes dynamic voltage and frequency scaling, selective bank activation, and thermal throttling techniques that can be updated through firmware to improve compatibility with new system requirements.Expand Specific Solutions05 Testing and Validation Frameworks for HBM4 Revisions

Comprehensive testing and validation frameworks are developed to ensure HBM4 revisions meet performance and compatibility requirements. These frameworks include automated test suites, compliance verification tools, and performance benchmarking methodologies. The validation process covers interface compatibility, timing parameters, error handling, and stress testing under various operating conditions to ensure reliable operation across different implementations and revisions of HBM4 technology.Expand Specific Solutions

Key Industry Players in HBM4 Ecosystem

The HBM4 Lifecycle Management market is currently in its early growth phase, characterized by increasing adoption as high-performance computing demands escalate. The market size is projected to expand significantly with the global memory market, driven by AI, data centers, and high-performance computing applications. From a technical maturity perspective, major players are at varying stages of development. Samsung Electronics leads with advanced HBM4 implementations, while IBM, Inspur, and ZTE are making significant investments in compatible infrastructure. Chinese companies like BYD and China Mobile are focusing on integration capabilities, while Western corporations such as Volkswagen, BMW, and SAP are exploring applications in automotive and enterprise systems. The competitive landscape shows a clear division between semiconductor manufacturers, system integrators, and end-users, with cross-industry collaboration becoming increasingly important for standardization and compatibility assurance.

International Business Machines Corp.

Technical Solution: IBM has developed a sophisticated HBM4 lifecycle management framework called "Memory Revision Abstraction Layer" (MRAL) that creates a virtualization layer between applications and physical HBM4 implementations. This abstraction layer translates memory access patterns to be compatible across different HBM4 revisions, enabling seamless upgrades without application modifications. IBM's approach incorporates AI-driven predictive maintenance that analyzes memory performance patterns to identify potential compatibility issues before they impact system stability. Their solution includes a comprehensive metadata tagging system that maintains detailed revision information for each memory module, enabling automated compatibility checks during system initialization. IBM has also implemented a "graceful degradation" protocol that allows systems to continue operating with reduced performance rather than failing completely when encountering revision incompatibilities. Additionally, their enterprise-focused HBM4 management tools provide detailed analytics on memory utilization patterns across different revisions to optimize workload placement.

Strengths: IBM's enterprise-grade approach provides robust solutions for mission-critical systems where memory reliability and compatibility are paramount. Their AI-driven predictive capabilities offer proactive management of potential revision conflicts. Weaknesses: The complexity of IBM's solution may introduce additional overhead that impacts performance in latency-sensitive applications, and implementation requires significant expertise.

Cisco Technology, Inc.

Technical Solution: Cisco has developed an integrated HBM4 lifecycle management solution specifically designed for networking infrastructure. Their approach centers on a "Network Memory Fabric" architecture that abstracts physical HBM4 implementations behind a consistent API, allowing network functions to operate seamlessly across different memory revisions. Cisco's solution includes automated compatibility testing that verifies new HBM4 revisions against existing network applications before deployment. They've implemented a distributed memory management system that can dynamically allocate workloads to appropriate HBM4 modules based on revision capabilities, ensuring optimal performance while maintaining compatibility. Cisco's approach also features a comprehensive telemetry framework that continuously monitors memory performance metrics across different HBM4 revisions, providing early warning of potential compatibility issues. Their solution incorporates memory traffic shaping algorithms that can adapt to the specific characteristics of different HBM4 revisions, optimizing bandwidth utilization while ensuring consistent application performance.

Strengths: Cisco's networking-specific approach provides highly optimized solutions for data center and telecommunications environments where memory performance directly impacts network throughput. Their extensive experience with high-performance networking equipment informs practical compatibility solutions. Weaknesses: Their focus on networking applications may limit the applicability of their solutions to general-purpose computing environments with different memory access patterns.

Critical Patents and Standards for HBM4 Compatibility

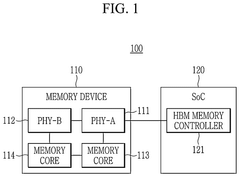

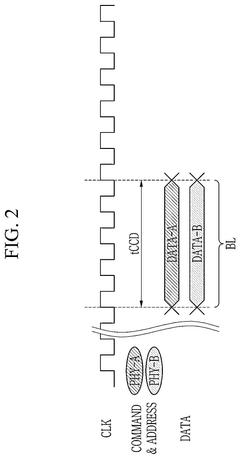

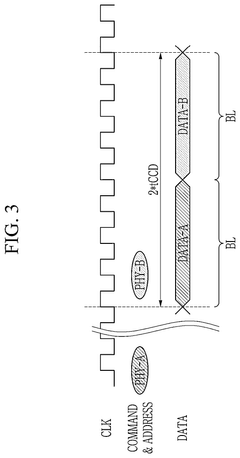

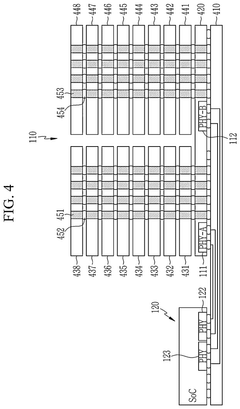

Method to select phys and a configuration of the data path in a multi PHY dram

PatentPendingUS20240362178A1

Innovation

- The implementation of memory devices with multiple physical interfaces and a setting circuit that allows selective connection to either one or multiple interfaces, enabling compatibility with both HBM3 and HBM4 standards by dynamically adjusting the interface used for connection with external devices.

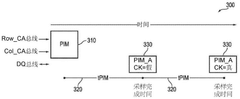

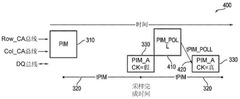

Method for coordinating memory commands and high bandwidth memory system

PatentActiveCN109299024B

Innovation

- By establishing a configuration contract between the host memory controller and the coordinated memory controller, the coordinated memory controller schedules the coordinated memory controller command based on the host memory controller command to ensure coordination of the common memory bank usage of the memory command.

Supply Chain Considerations for HBM4 Implementation

The implementation of HBM4 technology presents significant supply chain considerations that organizations must address to ensure successful deployment. The complex nature of HBM4 manufacturing requires a robust and resilient supply chain ecosystem. Currently, only a limited number of manufacturers possess the capability to produce HBM4 components, creating potential bottlenecks in the supply chain. Key suppliers include Samsung, SK Hynix, and Micron, with manufacturing facilities primarily concentrated in East Asia, particularly South Korea and Taiwan.

This geographical concentration introduces notable supply chain vulnerabilities, including geopolitical risks, natural disaster exposure, and potential trade restrictions. The COVID-19 pandemic has further highlighted these vulnerabilities, demonstrating how disruptions in one region can significantly impact global availability of advanced memory technologies.

HBM4 production involves intricate manufacturing processes requiring specialized equipment and materials. The supply chain for these critical components spans multiple tiers of suppliers, from silicon wafer producers to advanced packaging facilities. The complexity of the manufacturing process, combined with high quality requirements, necessitates close collaboration between memory manufacturers, logic chip producers, and packaging specialists.

Lead times for HBM4 components are expected to be substantial, potentially extending to 20-26 weeks under normal conditions and longer during supply constraints. Organizations implementing HBM4 technology must develop strategic inventory management approaches and establish long-term supplier relationships to mitigate these challenges.

Cost considerations represent another critical aspect of HBM4 supply chain management. The advanced manufacturing processes and materials required for HBM4 production contribute to higher component costs compared to previous memory technologies. Organizations should conduct comprehensive total cost of ownership analyses that account for not only acquisition costs but also potential supply chain disruption expenses.

Sustainability considerations are increasingly important in HBM4 supply chain management. The manufacturing process involves significant energy consumption and specialized materials, raising environmental concerns. Forward-thinking organizations are working with suppliers to implement more sustainable manufacturing practices and establish recycling programs for end-of-life components.

To address these supply chain challenges, organizations should develop multi-sourcing strategies where possible, establish strategic supplier partnerships, implement robust inventory management practices, and develop contingency plans for potential disruptions. Regular supply chain risk assessments and continuous monitoring of market conditions will be essential for successful HBM4 implementation.

This geographical concentration introduces notable supply chain vulnerabilities, including geopolitical risks, natural disaster exposure, and potential trade restrictions. The COVID-19 pandemic has further highlighted these vulnerabilities, demonstrating how disruptions in one region can significantly impact global availability of advanced memory technologies.

HBM4 production involves intricate manufacturing processes requiring specialized equipment and materials. The supply chain for these critical components spans multiple tiers of suppliers, from silicon wafer producers to advanced packaging facilities. The complexity of the manufacturing process, combined with high quality requirements, necessitates close collaboration between memory manufacturers, logic chip producers, and packaging specialists.

Lead times for HBM4 components are expected to be substantial, potentially extending to 20-26 weeks under normal conditions and longer during supply constraints. Organizations implementing HBM4 technology must develop strategic inventory management approaches and establish long-term supplier relationships to mitigate these challenges.

Cost considerations represent another critical aspect of HBM4 supply chain management. The advanced manufacturing processes and materials required for HBM4 production contribute to higher component costs compared to previous memory technologies. Organizations should conduct comprehensive total cost of ownership analyses that account for not only acquisition costs but also potential supply chain disruption expenses.

Sustainability considerations are increasingly important in HBM4 supply chain management. The manufacturing process involves significant energy consumption and specialized materials, raising environmental concerns. Forward-thinking organizations are working with suppliers to implement more sustainable manufacturing practices and establish recycling programs for end-of-life components.

To address these supply chain challenges, organizations should develop multi-sourcing strategies where possible, establish strategic supplier partnerships, implement robust inventory management practices, and develop contingency plans for potential disruptions. Regular supply chain risk assessments and continuous monitoring of market conditions will be essential for successful HBM4 implementation.

Risk Mitigation Strategies for HBM4 Version Transitions

To effectively manage the risks associated with HBM4 version transitions, organizations must implement comprehensive strategies that address both technical and operational challenges. The primary approach involves establishing a robust version compatibility matrix that clearly documents the interoperability between different HBM4 revisions and associated hardware components. This matrix should be continuously updated as new versions are released, providing system architects and engineers with reliable reference information for integration decisions.

Implementing phased transition plans represents another critical strategy, allowing organizations to gradually migrate from older to newer HBM4 versions while maintaining system stability. These plans typically include overlapping support periods where both versions are maintained simultaneously, enabling thorough validation before complete transition. Organizations should allocate sufficient resources for extensive compatibility testing during these transition phases to identify potential issues before they impact production systems.

Supply chain diversification serves as an essential risk mitigation measure, reducing dependency on single vendors for HBM4 components. By establishing relationships with multiple suppliers who support different HBM4 versions, organizations can ensure continuity even if particular versions face availability challenges. This approach requires careful vendor qualification processes and ongoing relationship management to maintain quality standards across the supply base.

Architectural abstraction layers provide technical insulation against version-specific dependencies. By implementing hardware abstraction layers (HALs) and memory controllers with configurable interfaces, systems can accommodate different HBM4 versions with minimal redesign. These abstraction mechanisms should be designed with sufficient flexibility to adapt to the evolving HBM4 specification while maintaining backward compatibility where possible.

Comprehensive documentation and knowledge management systems are equally important for preserving institutional knowledge about version-specific behaviors and workarounds. Organizations should maintain detailed records of integration experiences, known issues, and compatibility solutions for each HBM4 version. This documentation becomes particularly valuable during future transitions and when onboarding new team members.

Finally, establishing a dedicated cross-functional transition team with representatives from hardware engineering, software development, supply chain, and quality assurance ensures coordinated management of version transitions. This team should develop contingency plans for potential compatibility issues, including fallback options and temporary workarounds that can be implemented if critical problems emerge during transitions.

Implementing phased transition plans represents another critical strategy, allowing organizations to gradually migrate from older to newer HBM4 versions while maintaining system stability. These plans typically include overlapping support periods where both versions are maintained simultaneously, enabling thorough validation before complete transition. Organizations should allocate sufficient resources for extensive compatibility testing during these transition phases to identify potential issues before they impact production systems.

Supply chain diversification serves as an essential risk mitigation measure, reducing dependency on single vendors for HBM4 components. By establishing relationships with multiple suppliers who support different HBM4 versions, organizations can ensure continuity even if particular versions face availability challenges. This approach requires careful vendor qualification processes and ongoing relationship management to maintain quality standards across the supply base.

Architectural abstraction layers provide technical insulation against version-specific dependencies. By implementing hardware abstraction layers (HALs) and memory controllers with configurable interfaces, systems can accommodate different HBM4 versions with minimal redesign. These abstraction mechanisms should be designed with sufficient flexibility to adapt to the evolving HBM4 specification while maintaining backward compatibility where possible.

Comprehensive documentation and knowledge management systems are equally important for preserving institutional knowledge about version-specific behaviors and workarounds. Organizations should maintain detailed records of integration experiences, known issues, and compatibility solutions for each HBM4 version. This documentation becomes particularly valuable during future transitions and when onboarding new team members.

Finally, establishing a dedicated cross-functional transition team with representatives from hardware engineering, software development, supply chain, and quality assurance ensures coordinated management of version transitions. This team should develop contingency plans for potential compatibility issues, including fallback options and temporary workarounds that can be implemented if critical problems emerge during transitions.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!