How HBM4 Handles Power Delivery In Multi-Die Packages?

SEP 12, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

HBM4 Power Delivery Evolution and Objectives

High Bandwidth Memory (HBM) technology has evolved significantly since its introduction, with each generation addressing previous limitations while enhancing performance capabilities. HBM4, the latest iteration in this evolution, represents a substantial advancement in power delivery architecture specifically designed for multi-die packages. The development trajectory from HBM1 through HBM4 demonstrates a consistent focus on improving power efficiency while simultaneously increasing bandwidth and capacity.

The primary objective of HBM4's power delivery system is to maintain stable voltage levels across multiple stacked dies while managing thermal constraints in increasingly dense computing environments. This challenge has become more pronounced as artificial intelligence and high-performance computing applications demand greater memory bandwidth with lower latency, placing unprecedented stress on power delivery networks.

HBM4 aims to achieve a 50% improvement in power efficiency compared to HBM3, targeting operations below 1.1V while delivering bandwidth exceeding 8GB/s per pin. This ambitious goal requires fundamental rethinking of power distribution architecture within the memory stack and across the interposer connecting to the host processor.

Historical power delivery approaches in previous HBM generations relied heavily on through-silicon vias (TSVs) for vertical power distribution. However, as stack heights increased and die counts multiplied, voltage droop and power integrity issues became limiting factors. HBM4 addresses these challenges through a combination of advanced power delivery network (PDN) design and novel materials integration.

The evolution toward HBM4 has been driven by several key objectives: reducing power consumption per bit transferred, minimizing voltage fluctuations during high-bandwidth operations, enabling more efficient thermal dissipation, and supporting higher stack configurations without compromising signal integrity. These objectives align with broader industry trends toward more energy-efficient computing solutions.

Another critical goal for HBM4's power delivery system is compatibility with emerging chiplet architectures, where multiple processing elements and memory subsystems must share power resources efficiently. This requires sophisticated power management capabilities that can dynamically allocate power based on workload demands across heterogeneous die configurations.

The technical roadmap for HBM4 power delivery also emphasizes reliability improvements, targeting a 10x reduction in soft error rates compared to previous generations while maintaining operational stability under variable thermal conditions. This reliability enhancement is particularly crucial for mission-critical applications in data centers and high-performance computing environments.

The primary objective of HBM4's power delivery system is to maintain stable voltage levels across multiple stacked dies while managing thermal constraints in increasingly dense computing environments. This challenge has become more pronounced as artificial intelligence and high-performance computing applications demand greater memory bandwidth with lower latency, placing unprecedented stress on power delivery networks.

HBM4 aims to achieve a 50% improvement in power efficiency compared to HBM3, targeting operations below 1.1V while delivering bandwidth exceeding 8GB/s per pin. This ambitious goal requires fundamental rethinking of power distribution architecture within the memory stack and across the interposer connecting to the host processor.

Historical power delivery approaches in previous HBM generations relied heavily on through-silicon vias (TSVs) for vertical power distribution. However, as stack heights increased and die counts multiplied, voltage droop and power integrity issues became limiting factors. HBM4 addresses these challenges through a combination of advanced power delivery network (PDN) design and novel materials integration.

The evolution toward HBM4 has been driven by several key objectives: reducing power consumption per bit transferred, minimizing voltage fluctuations during high-bandwidth operations, enabling more efficient thermal dissipation, and supporting higher stack configurations without compromising signal integrity. These objectives align with broader industry trends toward more energy-efficient computing solutions.

Another critical goal for HBM4's power delivery system is compatibility with emerging chiplet architectures, where multiple processing elements and memory subsystems must share power resources efficiently. This requires sophisticated power management capabilities that can dynamically allocate power based on workload demands across heterogeneous die configurations.

The technical roadmap for HBM4 power delivery also emphasizes reliability improvements, targeting a 10x reduction in soft error rates compared to previous generations while maintaining operational stability under variable thermal conditions. This reliability enhancement is particularly crucial for mission-critical applications in data centers and high-performance computing environments.

Market Demand for Advanced Memory Solutions

The demand for advanced memory solutions has been experiencing unprecedented growth, driven primarily by the rapid expansion of data-intensive applications across multiple sectors. High Bandwidth Memory (HBM) technology, particularly the upcoming HBM4 standard, is positioned at the forefront of addressing these escalating requirements. Market research indicates that the global high-bandwidth memory market is projected to grow significantly through 2030, with compound annual growth rates exceeding 20% in some segments.

Data centers represent the largest market segment driving HBM adoption, as they face mounting pressure to process vast amounts of information for AI training, inference, and high-performance computing workloads. The explosion of large language models and generative AI applications has created memory bandwidth bottlenecks that traditional DRAM solutions cannot adequately address. These applications require not only massive memory capacity but also significantly higher bandwidth and improved power efficiency.

The automotive and edge computing sectors are emerging as substantial growth areas for advanced memory solutions. As vehicles incorporate more autonomous driving features and edge devices handle increasingly complex AI workloads locally, the demand for high-performance, energy-efficient memory has intensified. These applications are particularly sensitive to power delivery challenges in multi-die packages, making HBM4's power innovations especially relevant.

Telecommunications and 5G/6G infrastructure development represent another critical market driver. Network equipment manufacturers require memory solutions that can handle the increased data throughput while maintaining strict power envelopes. The ability of HBM4 to deliver improved power efficiency while increasing bandwidth makes it particularly attractive for these applications.

Consumer electronics, particularly high-end gaming, professional workstations, and mobile devices, constitute a growing market segment for advanced memory solutions. As consumers demand more sophisticated experiences and capabilities from their devices, manufacturers are exploring memory technologies that can deliver performance without compromising battery life or thermal management.

Market analysis reveals that customers across these segments are increasingly prioritizing total cost of ownership over initial acquisition costs. The superior power efficiency of HBM4 translates directly into reduced operational expenses through lower cooling requirements and energy consumption, making it an economically attractive option despite potentially higher upfront costs.

The geographical distribution of demand shows particular strength in North America and East Asia, with Europe following closely. This distribution aligns with the locations of major semiconductor manufacturers, AI research centers, and cloud service providers, suggesting a correlation between advanced technology ecosystems and demand for cutting-edge memory solutions.

Data centers represent the largest market segment driving HBM adoption, as they face mounting pressure to process vast amounts of information for AI training, inference, and high-performance computing workloads. The explosion of large language models and generative AI applications has created memory bandwidth bottlenecks that traditional DRAM solutions cannot adequately address. These applications require not only massive memory capacity but also significantly higher bandwidth and improved power efficiency.

The automotive and edge computing sectors are emerging as substantial growth areas for advanced memory solutions. As vehicles incorporate more autonomous driving features and edge devices handle increasingly complex AI workloads locally, the demand for high-performance, energy-efficient memory has intensified. These applications are particularly sensitive to power delivery challenges in multi-die packages, making HBM4's power innovations especially relevant.

Telecommunications and 5G/6G infrastructure development represent another critical market driver. Network equipment manufacturers require memory solutions that can handle the increased data throughput while maintaining strict power envelopes. The ability of HBM4 to deliver improved power efficiency while increasing bandwidth makes it particularly attractive for these applications.

Consumer electronics, particularly high-end gaming, professional workstations, and mobile devices, constitute a growing market segment for advanced memory solutions. As consumers demand more sophisticated experiences and capabilities from their devices, manufacturers are exploring memory technologies that can deliver performance without compromising battery life or thermal management.

Market analysis reveals that customers across these segments are increasingly prioritizing total cost of ownership over initial acquisition costs. The superior power efficiency of HBM4 translates directly into reduced operational expenses through lower cooling requirements and energy consumption, making it an economically attractive option despite potentially higher upfront costs.

The geographical distribution of demand shows particular strength in North America and East Asia, with Europe following closely. This distribution aligns with the locations of major semiconductor manufacturers, AI research centers, and cloud service providers, suggesting a correlation between advanced technology ecosystems and demand for cutting-edge memory solutions.

Current Challenges in Multi-Die Power Distribution

Multi-die packaging technologies have introduced unprecedented challenges in power distribution networks (PDNs). As HBM4 memory stacks integrate more layers with higher bandwidth requirements, power delivery has become a critical bottleneck that threatens overall system performance and reliability. The current power distribution architecture faces several significant limitations that must be addressed for successful HBM4 implementation.

The primary challenge lies in managing the increasing power density within confined spaces. With HBM4 targeting bandwidths exceeding 8TB/s, the power consumption per stack is projected to increase by 30-40% compared to HBM3E, while maintaining similar form factors. This creates thermal hotspots and voltage delivery issues that can compromise signal integrity and reduce memory performance.

Impedance management presents another major hurdle. As operating frequencies increase to support higher bandwidths, the impedance characteristics of power delivery networks become more critical. Current solutions struggle to maintain low impedance paths across the entire frequency spectrum relevant to HBM4 operation, resulting in power supply noise that can trigger timing violations and data errors.

The silicon interposer, which serves as the foundation for HBM integration, faces significant constraints in power delivery capability. Traditional interposer designs utilize relatively thin metal layers with limited current-carrying capacity. As HBM4 power requirements escalate, these interposers approach their physical limitations, creating bottlenecks that restrict overall system performance.

Voltage droop during high-bandwidth memory operations has emerged as a particularly challenging issue. When multiple HBM4 stacks operate simultaneously at peak performance, the resulting current transients can cause significant voltage fluctuations that exceed acceptable margins. Current decoupling capacitor implementations lack sufficient capacity to mitigate these effects adequately.

Power efficiency concerns have also become paramount. The energy cost per bit transferred continues to be a critical metric for data center applications. Current power distribution architectures for HBM implementations show diminishing returns in efficiency as bandwidth increases, threatening to make HBM4 economically unviable for certain applications without significant improvements.

Manufacturing complexity adds another dimension to these challenges. The integration of advanced power delivery solutions often requires additional processing steps, specialized materials, or novel interconnect technologies that may reduce yield and increase production costs. Finding solutions that balance performance requirements with manufacturing feasibility remains difficult.

Lastly, reliability concerns have intensified with each HBM generation. Electromigration risks increase with higher current densities, while thermal cycling can accelerate interconnect degradation. The current approaches to power distribution lack robust solutions to ensure the long-term reliability necessary for enterprise and high-performance computing applications where HBM4 is targeted.

The primary challenge lies in managing the increasing power density within confined spaces. With HBM4 targeting bandwidths exceeding 8TB/s, the power consumption per stack is projected to increase by 30-40% compared to HBM3E, while maintaining similar form factors. This creates thermal hotspots and voltage delivery issues that can compromise signal integrity and reduce memory performance.

Impedance management presents another major hurdle. As operating frequencies increase to support higher bandwidths, the impedance characteristics of power delivery networks become more critical. Current solutions struggle to maintain low impedance paths across the entire frequency spectrum relevant to HBM4 operation, resulting in power supply noise that can trigger timing violations and data errors.

The silicon interposer, which serves as the foundation for HBM integration, faces significant constraints in power delivery capability. Traditional interposer designs utilize relatively thin metal layers with limited current-carrying capacity. As HBM4 power requirements escalate, these interposers approach their physical limitations, creating bottlenecks that restrict overall system performance.

Voltage droop during high-bandwidth memory operations has emerged as a particularly challenging issue. When multiple HBM4 stacks operate simultaneously at peak performance, the resulting current transients can cause significant voltage fluctuations that exceed acceptable margins. Current decoupling capacitor implementations lack sufficient capacity to mitigate these effects adequately.

Power efficiency concerns have also become paramount. The energy cost per bit transferred continues to be a critical metric for data center applications. Current power distribution architectures for HBM implementations show diminishing returns in efficiency as bandwidth increases, threatening to make HBM4 economically unviable for certain applications without significant improvements.

Manufacturing complexity adds another dimension to these challenges. The integration of advanced power delivery solutions often requires additional processing steps, specialized materials, or novel interconnect technologies that may reduce yield and increase production costs. Finding solutions that balance performance requirements with manufacturing feasibility remains difficult.

Lastly, reliability concerns have intensified with each HBM generation. Electromigration risks increase with higher current densities, while thermal cycling can accelerate interconnect degradation. The current approaches to power distribution lack robust solutions to ensure the long-term reliability necessary for enterprise and high-performance computing applications where HBM4 is targeted.

Power Delivery Network Solutions for HBM4

01 Power delivery network design for HBM4

High Bandwidth Memory 4 (HBM4) requires specialized power delivery network designs to handle its high performance requirements. These designs include optimized voltage regulation modules, power planes, and decoupling capacitors to ensure stable power supply under high-speed data transfer conditions. Advanced power delivery architectures help minimize power loss and voltage droop while supporting the increased bandwidth and reduced latency of HBM4 memory systems.- Power delivery network architecture for HBM4: High Bandwidth Memory 4 (HBM4) requires specialized power delivery network architectures to support its high performance demands. These architectures include optimized power planes, dedicated voltage regulators, and efficient power distribution systems that minimize power loss while delivering stable voltage across the memory stack. The design incorporates advanced power management circuits that can respond quickly to changing power requirements during different memory operations.

- Thermal management solutions for HBM4 power systems: Effective thermal management is critical for HBM4 power delivery systems due to the high power density and heat generation. Solutions include integrated heat spreaders, advanced cooling techniques, and thermal-aware power routing that helps dissipate heat efficiently from the memory stack. These thermal management approaches ensure stable operation under high bandwidth conditions while preventing performance degradation due to thermal throttling.

- Power efficiency optimization techniques for HBM4: Various techniques are employed to optimize power efficiency in HBM4 implementations, including dynamic voltage and frequency scaling, power gating for inactive memory banks, and intelligent power state management. These approaches reduce overall power consumption while maintaining high bandwidth capabilities. Advanced power controllers monitor and adjust power delivery based on workload requirements, ensuring optimal performance per watt.

- Integration of HBM4 power delivery with host systems: HBM4 power delivery systems must be carefully integrated with host processors or GPUs to ensure proper operation. This includes coordinated power sequencing, shared power regulation schemes, and communication protocols between the memory and host power management systems. The integration addresses challenges related to different voltage domains, power budgeting across components, and system-level power optimization strategies.

- Signal integrity in HBM4 power delivery systems: Maintaining signal integrity is crucial for reliable HBM4 operation, requiring specialized power delivery designs that minimize noise and interference. These designs incorporate decoupling capacitors, controlled impedance power paths, and isolation techniques to prevent power supply noise from affecting high-speed data signals. Advanced power integrity analysis ensures clean power delivery across the entire memory stack, supporting the high data rates required for HBM4 operation.

02 Thermal management solutions for HBM4 power systems

Effective thermal management is critical for HBM4 memory systems due to their high power density. Solutions include integrated heat spreaders, advanced cooling techniques, and thermal interface materials specifically designed for stacked memory architectures. These thermal management approaches help dissipate heat generated during high-bandwidth operations, preventing performance degradation and ensuring reliable operation of HBM4 memory under various workloads.Expand Specific Solutions03 Power-efficient HBM4 interface technologies

Interface technologies for HBM4 focus on power efficiency while maintaining high data transfer rates. These include advanced signaling techniques, optimized I/O buffers, and power-aware communication protocols. By reducing power consumption at the interface level, these technologies help balance the performance demands of HBM4 with power constraints, enabling more efficient operation in data-intensive applications like AI and high-performance computing.Expand Specific Solutions04 Dynamic power management for HBM4 systems

Dynamic power management techniques for HBM4 memory include adaptive voltage scaling, frequency adjustment, and power gating for inactive memory regions. These approaches allow HBM4 systems to optimize power consumption based on workload requirements, reducing energy usage during periods of lower activity while ensuring full performance when needed. Advanced power controllers monitor and adjust power delivery in real-time to maintain system stability and efficiency.Expand Specific Solutions05 System-level integration of HBM4 power delivery

System-level integration approaches for HBM4 power delivery focus on coordinating power requirements across the entire computing platform. These solutions include power domain partitioning, integrated voltage regulators, and power management ICs specifically designed for high-bandwidth memory systems. By considering the entire system architecture, these approaches optimize power delivery to HBM4 while managing interactions with other components like processors and accelerators.Expand Specific Solutions

Key Players in HBM4 Memory Ecosystem

The HBM4 power delivery landscape in multi-die packages is evolving rapidly, with the market currently in a growth phase as data center and AI applications drive demand. The global HBM market is projected to expand significantly, reaching multi-billion dollar valuations by 2028. From a technical maturity perspective, industry leaders Samsung, SK hynix, and Micron are at the forefront with production-ready solutions, while Intel, AMD, and TSMC are advancing integration capabilities. Chinese players like ChangXin Memory and Huawei are investing heavily to close the technology gap. Google and other hyperscalers are driving requirements as major consumers. The competitive dynamics center around balancing increased bandwidth demands with thermal management challenges in increasingly dense computing environments.

Micron Technology, Inc.

Technical Solution: Micron's approach to HBM4 power delivery in multi-die packages centers on their Hybrid Memory Cube architecture evolution. They've developed a sophisticated power delivery network that incorporates distributed power delivery TSVs with optimized placement to minimize IR drop across the memory stack. Micron's solution features a segmented power distribution system where each die in the stack receives independently regulated power, allowing for fine-grained power management. Their HBM4 implementation includes integrated voltage regulators in the logic die that work in concert with advanced power gating techniques to reduce static power consumption during idle periods. Micron has also implemented adaptive impedance matching in their TSV design to maintain signal integrity while optimizing power delivery paths, resulting in improved power efficiency across varying workloads.

Strengths: Segmented power distribution enables fine-grained power management; advanced power gating techniques significantly reduce idle power consumption. Weaknesses: More complex control logic required for independent die power management; potential for increased latency due to power state transitions.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung's HBM4 power delivery solution employs a sophisticated hierarchical power distribution network specifically designed for multi-die packages. Their approach utilizes a combination of advanced TSV technology and innovative substrate design to address the power challenges in high-bandwidth memory stacks. Samsung has developed proprietary microbump arrays with dedicated power/ground configurations that minimize impedance and reduce power loss. Their HBM4 implementation features an intelligent power management system that dynamically adjusts voltage levels based on memory access patterns and thermal conditions. Samsung has also pioneered the use of silicon interposers with embedded capacitors that serve as localized power reservoirs, reducing voltage fluctuations during high-current transients. This comprehensive approach enables their HBM4 solution to deliver exceptional performance while maintaining strict power constraints.

Strengths: Advanced silicon interposer technology with embedded passive components improves power stability; dynamic voltage/frequency scaling capabilities optimize power consumption. Weaknesses: Higher manufacturing complexity compared to previous HBM generations; requires specialized testing procedures to validate power integrity across the stack.

Critical Patents in Multi-Die Power Management

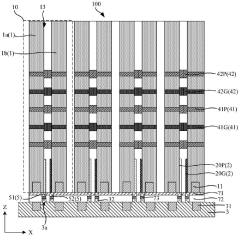

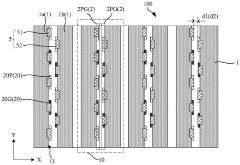

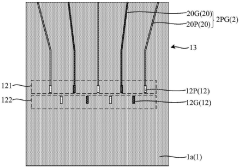

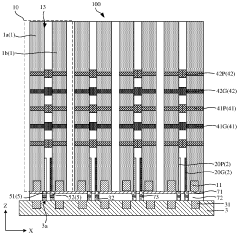

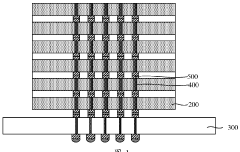

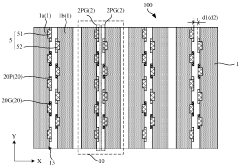

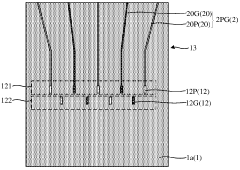

Semiconductor structure, manufacturing method of semiconductor structure and semiconductor device

PatentPendingCN117677207A

Innovation

- By stacking multiple memory chips in a parallel direction on the upper surface of the logic chip, and leading out power supply signal lines within the memory chip, a wired power supply method is used to electrically connect the power supply wiring layer to the power supply port to achieve unified communication delay and improve power supply stability. sex.

Semiconductor structure, manufacturing method for semiconductor structure, and semiconductor device

PatentWO2024031774A1

Innovation

- Multiple memory chips are stacked in parallel on the upper surface of the logic chip. Wired power supply is realized through the electrical connection between the power supply wiring layer and the power supply signal line. The power supply is connected to the power supply port through welding bumps to simplify the power supply path to improve stability.

Thermal Management Strategies for HBM4

Thermal management represents a critical challenge for HBM4 implementation in multi-die packages, particularly as power densities continue to increase with each generation. HBM4 memory stacks generate significant heat during operation, with thermal output potentially exceeding 15W per stack under high-bandwidth scenarios. This heat concentration, combined with the proximity to other high-performance components in the package, creates thermal management complexities that require innovative solutions.

The primary thermal management strategies for HBM4 involve both passive and active cooling techniques. Passive solutions include advanced thermal interface materials (TIMs) with conductivity values exceeding 20 W/m·K, which significantly improve heat transfer between the HBM4 stacks and heat dissipation components. Silicon interposers with integrated micro-fluidic channels represent another promising approach, allowing coolant circulation directly beneath the HBM4 stacks to efficiently extract heat at its source.

Active cooling solutions for HBM4 include vapor chamber technologies that utilize phase-change principles to rapidly transport heat away from memory stacks. These chambers can be integrated directly into the package substrate, providing thermal conductivity values up to 10 times higher than traditional solid materials. Additionally, advanced cold plate designs with micro-fin structures increase surface area for heat exchange while maintaining minimal z-height requirements.

Thermal sensing and dynamic power management also play crucial roles in HBM4 thermal control. Distributed temperature sensors embedded throughout the memory stack provide real-time thermal data, enabling dynamic frequency and voltage scaling to maintain optimal operating temperatures. These sensors typically offer precision within ±0.5°C and response times under 10ms, allowing for rapid thermal management adjustments.

Computational fluid dynamics (CFD) modeling has become essential for HBM4 thermal design, enabling engineers to simulate and optimize airflow patterns and heat distribution before physical prototyping. These simulations account for various operating conditions and can predict thermal bottlenecks with accuracy approaching 95% compared to physical measurements.

Industry leaders have developed proprietary thermal solutions specifically for HBM4 implementations. These include Samsung's "Heat Spreader Integration" technology, which embeds copper heat spreaders between DRAM layers, and SK Hynix's "Thermal Bridge Architecture" that creates dedicated thermal pathways through the memory stack. These innovations have demonstrated temperature reductions of 15-20°C compared to previous generation solutions.

The primary thermal management strategies for HBM4 involve both passive and active cooling techniques. Passive solutions include advanced thermal interface materials (TIMs) with conductivity values exceeding 20 W/m·K, which significantly improve heat transfer between the HBM4 stacks and heat dissipation components. Silicon interposers with integrated micro-fluidic channels represent another promising approach, allowing coolant circulation directly beneath the HBM4 stacks to efficiently extract heat at its source.

Active cooling solutions for HBM4 include vapor chamber technologies that utilize phase-change principles to rapidly transport heat away from memory stacks. These chambers can be integrated directly into the package substrate, providing thermal conductivity values up to 10 times higher than traditional solid materials. Additionally, advanced cold plate designs with micro-fin structures increase surface area for heat exchange while maintaining minimal z-height requirements.

Thermal sensing and dynamic power management also play crucial roles in HBM4 thermal control. Distributed temperature sensors embedded throughout the memory stack provide real-time thermal data, enabling dynamic frequency and voltage scaling to maintain optimal operating temperatures. These sensors typically offer precision within ±0.5°C and response times under 10ms, allowing for rapid thermal management adjustments.

Computational fluid dynamics (CFD) modeling has become essential for HBM4 thermal design, enabling engineers to simulate and optimize airflow patterns and heat distribution before physical prototyping. These simulations account for various operating conditions and can predict thermal bottlenecks with accuracy approaching 95% compared to physical measurements.

Industry leaders have developed proprietary thermal solutions specifically for HBM4 implementations. These include Samsung's "Heat Spreader Integration" technology, which embeds copper heat spreaders between DRAM layers, and SK Hynix's "Thermal Bridge Architecture" that creates dedicated thermal pathways through the memory stack. These innovations have demonstrated temperature reductions of 15-20°C compared to previous generation solutions.

Integration Standards and Interoperability

The integration of HBM4 into multi-die packages requires adherence to established standards and protocols to ensure seamless interoperability across different components and systems. JEDEC, as the primary standardization body for memory technologies, has developed comprehensive specifications for HBM4 that address power delivery challenges while maintaining compatibility with existing systems.

HBM4 implements the standardized 2.5D and 3D integration approaches, utilizing silicon interposers and through-silicon vias (TSVs) that conform to industry-wide specifications. These standards ensure that HBM4 memory can be effectively integrated with various processing units from different manufacturers while maintaining consistent power delivery characteristics. The standardized base die design in HBM4 incorporates power management circuitry that adheres to common voltage regulation specifications, facilitating integration with diverse SoCs and accelerators.

Interoperability between HBM4 and other components is enhanced through standardized power management interfaces that support dynamic voltage and frequency scaling (DVFS) protocols. These interfaces enable coordinated power management across heterogeneous die components, allowing system-level power optimization while maintaining data integrity. The implementation of standardized power states and transitions ensures that HBM4 can respond appropriately to system-level power management commands without compromising performance or reliability.

The Common Electrical Interface (CEI) standards have been incorporated into HBM4 design, providing well-defined electrical specifications for signal integrity and power delivery across die boundaries. This standardization is crucial for maintaining reliable communication between HBM4 memory stacks and processing elements, particularly under varying power conditions in complex multi-die packages.

HBM4 also supports industry-standard thermal management protocols, enabling coordinated thermal monitoring and mitigation strategies across heterogeneous die components. The standardized thermal sensors and reporting mechanisms allow system-level thermal management solutions to incorporate HBM4's thermal characteristics into holistic cooling strategies, preventing localized hotspots that could compromise power delivery integrity.

Furthermore, HBM4 implements standardized testing and validation methodologies specifically designed for multi-die packages, ensuring that power delivery networks maintain their integrity across manufacturing variations. These methodologies include standardized power integrity tests that verify the robustness of power delivery under various operating conditions, contributing to overall system reliability and performance consistency across different implementations.

HBM4 implements the standardized 2.5D and 3D integration approaches, utilizing silicon interposers and through-silicon vias (TSVs) that conform to industry-wide specifications. These standards ensure that HBM4 memory can be effectively integrated with various processing units from different manufacturers while maintaining consistent power delivery characteristics. The standardized base die design in HBM4 incorporates power management circuitry that adheres to common voltage regulation specifications, facilitating integration with diverse SoCs and accelerators.

Interoperability between HBM4 and other components is enhanced through standardized power management interfaces that support dynamic voltage and frequency scaling (DVFS) protocols. These interfaces enable coordinated power management across heterogeneous die components, allowing system-level power optimization while maintaining data integrity. The implementation of standardized power states and transitions ensures that HBM4 can respond appropriately to system-level power management commands without compromising performance or reliability.

The Common Electrical Interface (CEI) standards have been incorporated into HBM4 design, providing well-defined electrical specifications for signal integrity and power delivery across die boundaries. This standardization is crucial for maintaining reliable communication between HBM4 memory stacks and processing elements, particularly under varying power conditions in complex multi-die packages.

HBM4 also supports industry-standard thermal management protocols, enabling coordinated thermal monitoring and mitigation strategies across heterogeneous die components. The standardized thermal sensors and reporting mechanisms allow system-level thermal management solutions to incorporate HBM4's thermal characteristics into holistic cooling strategies, preventing localized hotspots that could compromise power delivery integrity.

Furthermore, HBM4 implements standardized testing and validation methodologies specifically designed for multi-die packages, ensuring that power delivery networks maintain their integrity across manufacturing variations. These methodologies include standardized power integrity tests that verify the robustness of power delivery under various operating conditions, contributing to overall system reliability and performance consistency across different implementations.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!