HBM4 Board-Level Integration: Stack Placement And Airflow Design

SEP 12, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

HBM4 Technology Evolution and Integration Objectives

High Bandwidth Memory (HBM) technology has evolved significantly since its introduction, with each generation bringing substantial improvements in bandwidth, capacity, and energy efficiency. The evolution from HBM1 to HBM4 represents a critical advancement in addressing the growing memory demands of high-performance computing applications, particularly in AI/ML workloads, data centers, and graphics processing. HBM4, as the latest iteration, aims to overcome the limitations of previous generations while establishing new benchmarks for memory performance and integration capabilities.

The historical trajectory of HBM technology shows a consistent pattern of increasing bandwidth density and decreasing power consumption per bit transferred. HBM1, introduced in 2013, offered a significant departure from traditional DRAM architectures with its stacked die approach. HBM2 followed in 2016 with doubled bandwidth, while HBM2E (2018) and HBM3 (2021) continued this progression with further improvements in speed and capacity. HBM4, expected to be commercially available by 2025, represents the culmination of these evolutionary steps with projected bandwidths exceeding 8 TB/s for high-end implementations.

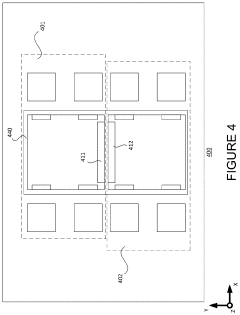

The primary technical objective for HBM4 board-level integration centers on optimizing the placement of memory stacks in relation to processing units while ensuring adequate thermal management through strategic airflow design. This integration must balance competing requirements: minimizing signal path lengths to reduce latency, maximizing bandwidth through optimal interconnect design, and ensuring sufficient cooling capacity to maintain reliable operation under high-performance conditions.

A key evolution in HBM4 integration is the transition toward more sophisticated package-level solutions, including advanced substrate technologies and potentially active interposers that can help manage the increased thermal loads. The industry is moving toward more holistic system-level approaches where memory placement and cooling solutions are considered integral parts of the initial design process rather than afterthoughts.

Integration objectives for HBM4 include achieving sub-10ns latencies at system level, maintaining junction temperatures below 105°C under full load, supporting effective bandwidth utilization above 90% of theoretical maximums, and ensuring reliability metrics that accommodate the higher operating frequencies and thermal conditions. These objectives necessitate innovations in both physical stack placement strategies and complementary airflow design methodologies.

The evolution of HBM technology also reflects broader industry trends toward heterogeneous integration, where memory and processing elements are increasingly viewed as a unified system rather than discrete components. This paradigm shift requires new approaches to board-level integration that consider the entire memory-compute subsystem as an integrated unit with shared thermal, electrical, and mechanical constraints.

The historical trajectory of HBM technology shows a consistent pattern of increasing bandwidth density and decreasing power consumption per bit transferred. HBM1, introduced in 2013, offered a significant departure from traditional DRAM architectures with its stacked die approach. HBM2 followed in 2016 with doubled bandwidth, while HBM2E (2018) and HBM3 (2021) continued this progression with further improvements in speed and capacity. HBM4, expected to be commercially available by 2025, represents the culmination of these evolutionary steps with projected bandwidths exceeding 8 TB/s for high-end implementations.

The primary technical objective for HBM4 board-level integration centers on optimizing the placement of memory stacks in relation to processing units while ensuring adequate thermal management through strategic airflow design. This integration must balance competing requirements: minimizing signal path lengths to reduce latency, maximizing bandwidth through optimal interconnect design, and ensuring sufficient cooling capacity to maintain reliable operation under high-performance conditions.

A key evolution in HBM4 integration is the transition toward more sophisticated package-level solutions, including advanced substrate technologies and potentially active interposers that can help manage the increased thermal loads. The industry is moving toward more holistic system-level approaches where memory placement and cooling solutions are considered integral parts of the initial design process rather than afterthoughts.

Integration objectives for HBM4 include achieving sub-10ns latencies at system level, maintaining junction temperatures below 105°C under full load, supporting effective bandwidth utilization above 90% of theoretical maximums, and ensuring reliability metrics that accommodate the higher operating frequencies and thermal conditions. These objectives necessitate innovations in both physical stack placement strategies and complementary airflow design methodologies.

The evolution of HBM technology also reflects broader industry trends toward heterogeneous integration, where memory and processing elements are increasingly viewed as a unified system rather than discrete components. This paradigm shift requires new approaches to board-level integration that consider the entire memory-compute subsystem as an integrated unit with shared thermal, electrical, and mechanical constraints.

Market Demand for High-Bandwidth Memory Solutions

The demand for High-Bandwidth Memory (HBM) solutions has experienced exponential growth in recent years, primarily driven by the increasing computational requirements of artificial intelligence, machine learning, and high-performance computing applications. As these applications continue to evolve, they generate and process massive datasets that require faster memory access and higher bandwidth capabilities, pushing traditional memory technologies to their limits.

Market research indicates that the global HBM market is projected to grow significantly through 2030, with particularly strong demand coming from data centers, AI accelerators, and advanced graphics processing units. This growth trajectory is supported by the rapid expansion of cloud computing services and the proliferation of AI applications across various industries, including healthcare, automotive, and financial services.

HBM4, as the next generation following HBM3E, addresses critical market needs for even higher bandwidth, improved power efficiency, and greater capacity. Enterprise customers are increasingly demanding memory solutions that can handle complex computational workloads while maintaining reasonable power consumption profiles. The integration challenges at the board level, particularly regarding stack placement and airflow design, have become crucial considerations for system architects and hardware engineers.

The financial services sector represents a significant market segment, where high-frequency trading platforms require ultra-low latency memory access. Similarly, scientific research institutions working on climate modeling, genomics, and particle physics simulations demand memory solutions that can process enormous datasets efficiently. These specialized applications are willing to invest in premium memory technologies that deliver measurable performance advantages.

From a geographical perspective, North America and East Asia continue to lead in HBM adoption, with major technology companies and semiconductor manufacturers investing heavily in research and development. However, Europe is showing accelerated growth in HBM demand, particularly in automotive applications for advanced driver-assistance systems and autonomous driving technologies.

The market is also witnessing a shift toward more integrated solutions, where memory subsystems are designed in conjunction with processing units to optimize overall system performance. This trend has created opportunities for companies that can provide comprehensive solutions addressing thermal management, signal integrity, and power delivery challenges associated with HBM4 integration.

Customer feedback indicates that thermal management remains a primary concern when implementing HBM solutions, highlighting the importance of effective stack placement and airflow design. As data centers strive for greater energy efficiency, the ability to cool HBM4 stacks effectively without excessive power consumption has become a key differentiator in the market.

Market research indicates that the global HBM market is projected to grow significantly through 2030, with particularly strong demand coming from data centers, AI accelerators, and advanced graphics processing units. This growth trajectory is supported by the rapid expansion of cloud computing services and the proliferation of AI applications across various industries, including healthcare, automotive, and financial services.

HBM4, as the next generation following HBM3E, addresses critical market needs for even higher bandwidth, improved power efficiency, and greater capacity. Enterprise customers are increasingly demanding memory solutions that can handle complex computational workloads while maintaining reasonable power consumption profiles. The integration challenges at the board level, particularly regarding stack placement and airflow design, have become crucial considerations for system architects and hardware engineers.

The financial services sector represents a significant market segment, where high-frequency trading platforms require ultra-low latency memory access. Similarly, scientific research institutions working on climate modeling, genomics, and particle physics simulations demand memory solutions that can process enormous datasets efficiently. These specialized applications are willing to invest in premium memory technologies that deliver measurable performance advantages.

From a geographical perspective, North America and East Asia continue to lead in HBM adoption, with major technology companies and semiconductor manufacturers investing heavily in research and development. However, Europe is showing accelerated growth in HBM demand, particularly in automotive applications for advanced driver-assistance systems and autonomous driving technologies.

The market is also witnessing a shift toward more integrated solutions, where memory subsystems are designed in conjunction with processing units to optimize overall system performance. This trend has created opportunities for companies that can provide comprehensive solutions addressing thermal management, signal integrity, and power delivery challenges associated with HBM4 integration.

Customer feedback indicates that thermal management remains a primary concern when implementing HBM solutions, highlighting the importance of effective stack placement and airflow design. As data centers strive for greater energy efficiency, the ability to cool HBM4 stacks effectively without excessive power consumption has become a key differentiator in the market.

Current Challenges in HBM4 Board-Level Integration

The integration of HBM4 at the board level presents significant challenges that require innovative solutions to address thermal management, signal integrity, and mechanical stability concerns. As HBM4 technology pushes memory bandwidth boundaries with projected speeds exceeding 8 GT/s and capacities reaching 64GB per stack, the complexity of board-level integration has increased exponentially.

Thermal management represents perhaps the most critical challenge in HBM4 board-level integration. With power densities potentially exceeding 5W/cm², traditional cooling methods are becoming inadequate. The compact stacking of memory dies creates concentrated heat zones that can lead to thermal throttling and reliability issues. Current thermal interface materials (TIMs) struggle to efficiently transfer heat from these dense stacks to cooling solutions.

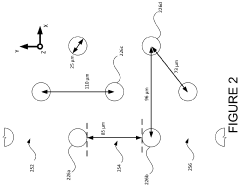

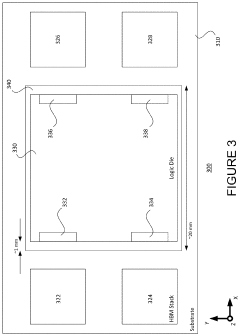

Stack placement optimization presents another significant hurdle. Engineers must balance competing requirements: placing HBM4 stacks close to processing units to minimize signal path lengths while maintaining sufficient spacing for effective cooling. The current industry approach of surrounding processors with HBM stacks creates complex airflow patterns that can result in thermal hotspots and uneven cooling across the board.

Signal integrity challenges are exacerbated by the higher data rates of HBM4. The board-level interconnects must maintain signal quality across shorter distances while managing increased electromagnetic interference (EMI). Current PCB materials and manufacturing techniques are being pushed to their limits to accommodate the fine-pitch connections required for HBM4 integration.

Mechanical stress management presents additional complications. The coefficient of thermal expansion (CTE) mismatch between HBM4 stacks, silicon interposers, and PCB materials creates reliability concerns during thermal cycling. Current underfill and molding compounds may not adequately address these stresses at the scale and density of HBM4 implementations.

Power delivery network (PDN) design faces unprecedented challenges with HBM4 integration. The high-current requirements combined with strict voltage regulation needs demand sophisticated PDN architectures. Current board-level power distribution approaches struggle to maintain voltage stability while minimizing power loss across the dense HBM4 implementation.

Airflow design optimization remains particularly problematic. The tall profile of HBM4 stacks creates aerodynamic obstacles that disrupt laminar airflow across the board. Current cooling solutions often fail to account for these complex airflow patterns, resulting in inefficient heat dissipation and potential reliability issues in high-performance computing environments.

Manufacturing and testing complexities further compound these challenges. The precise placement requirements for HBM4 stacks demand advanced assembly techniques, while comprehensive testing becomes increasingly difficult due to limited access to interconnects once the stacks are integrated onto the board.

Thermal management represents perhaps the most critical challenge in HBM4 board-level integration. With power densities potentially exceeding 5W/cm², traditional cooling methods are becoming inadequate. The compact stacking of memory dies creates concentrated heat zones that can lead to thermal throttling and reliability issues. Current thermal interface materials (TIMs) struggle to efficiently transfer heat from these dense stacks to cooling solutions.

Stack placement optimization presents another significant hurdle. Engineers must balance competing requirements: placing HBM4 stacks close to processing units to minimize signal path lengths while maintaining sufficient spacing for effective cooling. The current industry approach of surrounding processors with HBM stacks creates complex airflow patterns that can result in thermal hotspots and uneven cooling across the board.

Signal integrity challenges are exacerbated by the higher data rates of HBM4. The board-level interconnects must maintain signal quality across shorter distances while managing increased electromagnetic interference (EMI). Current PCB materials and manufacturing techniques are being pushed to their limits to accommodate the fine-pitch connections required for HBM4 integration.

Mechanical stress management presents additional complications. The coefficient of thermal expansion (CTE) mismatch between HBM4 stacks, silicon interposers, and PCB materials creates reliability concerns during thermal cycling. Current underfill and molding compounds may not adequately address these stresses at the scale and density of HBM4 implementations.

Power delivery network (PDN) design faces unprecedented challenges with HBM4 integration. The high-current requirements combined with strict voltage regulation needs demand sophisticated PDN architectures. Current board-level power distribution approaches struggle to maintain voltage stability while minimizing power loss across the dense HBM4 implementation.

Airflow design optimization remains particularly problematic. The tall profile of HBM4 stacks creates aerodynamic obstacles that disrupt laminar airflow across the board. Current cooling solutions often fail to account for these complex airflow patterns, resulting in inefficient heat dissipation and potential reliability issues in high-performance computing environments.

Manufacturing and testing complexities further compound these challenges. The precise placement requirements for HBM4 stacks demand advanced assembly techniques, while comprehensive testing becomes increasingly difficult due to limited access to interconnects once the stacks are integrated onto the board.

Current Stack Placement and Thermal Management Solutions

01 Optimal HBM4 stack placement for thermal management

Strategic placement of HBM4 memory stacks within computing systems is crucial for effective thermal management. By positioning memory stacks with consideration to heat dissipation patterns, designers can minimize thermal hotspots and improve overall system reliability. This approach involves analyzing thermal gradients across the package and positioning HBM4 components to maximize heat transfer to cooling solutions while maintaining signal integrity for high-bandwidth operations.- HBM4 Stack Placement Optimization: Optimal placement of HBM4 memory stacks on semiconductor packages to maximize performance and thermal efficiency. This includes strategic positioning relative to processing units to minimize signal path lengths and reduce latency. The placement considers the physical constraints of the package substrate and optimizes the interconnect routing between memory stacks and processors to enhance bandwidth capabilities while maintaining signal integrity.

- Thermal Management and Airflow Design for HBM4: Innovative airflow design solutions specifically engineered for high-density HBM4 implementations. These designs incorporate advanced cooling mechanisms such as directed airflow channels, heat spreaders, and thermal interface materials to efficiently dissipate heat generated by densely packed memory stacks. The thermal management systems are optimized to maintain operating temperatures within acceptable ranges even under high-bandwidth data transfer conditions.

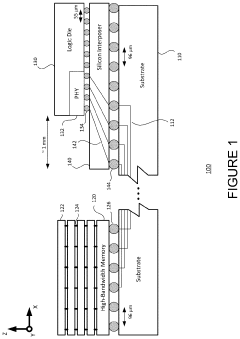

- 3D Integration and Interconnect Technologies for HBM4: Advanced 3D integration techniques for HBM4 memory stacks, including through-silicon vias (TSVs), interposers, and micro-bumps that enable vertical stacking of memory dies. These interconnect technologies facilitate high-density memory integration while maintaining signal integrity across multiple layers. The 3D architecture optimizes the physical footprint of memory subsystems while providing the high bandwidth required for data-intensive applications.

- Power Distribution and Management for HBM4 Systems: Sophisticated power distribution networks designed specifically for HBM4 memory systems to ensure stable power delivery across all memory stacks. These systems incorporate advanced power management techniques including dynamic voltage scaling, power gating, and intelligent power distribution to optimize energy efficiency while maintaining performance. The power management solutions address the unique challenges of high-bandwidth memory operations including transient current demands and voltage droop mitigation.

- System-Level Integration and Communication Protocols for HBM4: System architecture designs that optimize the integration of HBM4 memory with various processing units including CPUs, GPUs, and specialized accelerators. These designs incorporate advanced communication protocols and memory controllers specifically tailored for high-bandwidth memory interfaces. The system-level integration focuses on maximizing data throughput while minimizing latency through optimized memory access patterns and efficient command scheduling algorithms.

02 Airflow design optimization for HBM4 cooling

Specialized airflow design techniques for cooling HBM4 memory stacks involve creating directed air channels that efficiently remove heat from these dense memory components. These designs incorporate strategically placed vents, baffles, and air directors to ensure adequate cooling across all layers of the memory stack. Advanced computational fluid dynamics modeling helps optimize the airflow patterns to address the unique thermal challenges posed by the high power density of HBM4 implementations.Expand Specific Solutions03 3D integration and interconnect solutions for HBM4

Advanced 3D integration techniques for HBM4 memory stacks focus on optimizing the physical arrangement and interconnection of memory dies within the stack. These solutions include through-silicon vias (TSVs), interposers, and microbumps that enable efficient vertical connections while managing thermal constraints. The placement strategy considers both electrical performance requirements and thermal dissipation paths to achieve optimal bandwidth while maintaining acceptable operating temperatures.Expand Specific Solutions04 Power management techniques for HBM4 implementations

Innovative power management approaches for HBM4 memory systems include dynamic voltage and frequency scaling, power gating, and intelligent power distribution across memory channels. These techniques help reduce thermal output while maintaining performance requirements. By strategically managing power consumption based on workload demands, these solutions enable more efficient placement of HBM4 stacks and reduce cooling requirements, allowing for more compact and efficient system designs.Expand Specific Solutions05 System-level design considerations for HBM4 integration

System-level design approaches for HBM4 integration focus on holistic considerations including package design, substrate materials, and system architecture to optimize memory performance and thermal management. These designs incorporate advanced materials with superior thermal conductivity, innovative package geometries, and strategic component placement to balance electrical, mechanical, and thermal requirements. The integration strategy also considers signal integrity, power delivery networks, and mechanical stress factors that affect the reliability of high-density memory implementations.Expand Specific Solutions

Key Industry Players in HBM4 Ecosystem

The HBM4 board-level integration market is currently in an early growth phase, characterized by increasing demand for high-bandwidth memory solutions in AI and data center applications. The market is projected to expand significantly as HBM4 technology matures, with key players positioning themselves across the value chain. Leading semiconductor companies like IBM, Huawei, and GLOBALFOUNDRIES are investing heavily in advanced packaging technologies, while specialized firms such as JCET Group and Applied Materials focus on thermal management solutions critical for HBM4 stack placement and airflow design. Technical challenges around heat dissipation and signal integrity remain, with companies like ChangXin Memory and VIA Technologies developing innovative approaches to optimize board-level integration. The competitive landscape reflects a mix of established semiconductor giants and specialized equipment manufacturers collaborating to address the complex thermal and electrical requirements of HBM4 implementation.

International Business Machines Corp.

Technical Solution: IBM's HBM4 board-level integration approach focuses on advanced thermal management and optimized stack placement. Their solution incorporates a multi-tier cooling architecture with direct liquid cooling channels integrated within the substrate. IBM employs a "thermal bridge" technology that creates dedicated heat dissipation pathways from the HBM4 stacks to cooling elements. Their design places HBM4 stacks in a radial pattern around the main processor to minimize signal path lengths while creating optimized airflow channels between stacks. IBM's integration also features micro-fluidic cooling elements embedded directly beneath HBM4 stacks, allowing for targeted cooling of high-temperature zones. The company has developed specialized interposers with integrated micro-channels that facilitate both electrical connections and thermal management simultaneously[1]. Their approach prioritizes reliability under high-performance computing workloads with dynamic thermal management capabilities.

Strengths: Superior thermal management through integrated liquid cooling solutions; extensive experience with high-performance computing systems; advanced packaging technologies. Weaknesses: Higher implementation costs compared to air-cooled solutions; increased system complexity requiring specialized maintenance; potential compatibility challenges with standard data center infrastructure.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei's HBM4 board-level integration solution centers on their "Cooling-First" architecture that prioritizes thermal considerations from the initial design phase. Their approach features a proprietary stack placement methodology that positions HBM4 modules in a staggered formation to create natural airflow channels. Huawei implements vapor chamber cooling technology directly integrated with the substrate to efficiently dissipate heat from HBM4 stacks. Their design incorporates computational fluid dynamics (CFD) optimized heat spreaders that direct airflow precisely where needed most. Huawei's solution also features dynamic thermal management that adjusts cooling parameters based on real-time temperature monitoring across the board. The company utilizes advanced materials with high thermal conductivity at critical interface points between HBM4 stacks and cooling elements. Their integration approach includes specialized thermal interface materials (TIMs) that reduce thermal resistance between components[2]. Huawei's design accommodates both traditional air cooling and hybrid cooling solutions depending on deployment scenarios.

Strengths: Innovative staggered stack placement design optimizes airflow; comprehensive thermal simulation capabilities; flexible cooling options for different deployment environments. Weaknesses: Potential challenges with standardization across different product lines; higher initial engineering costs; may require specialized manufacturing processes.

Critical Patents and Innovations in HBM4 Integration

Integrated Circuit Package For High Bandwidth Memory

PatentActiveUS20240250082A1

Innovation

- The use of wider microbump pitches in HBM stacks allows for the implementation of printed traces, such as organic traces, to replace silicon interposer channels, reducing material costs and simplifying production by forming interposer channels in a fan-out configuration and utilizing multilayer substrates to increase signal density.

Storage device and multi-chip system

PatentActiveCN110673980B

Innovation

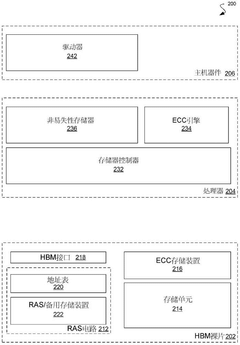

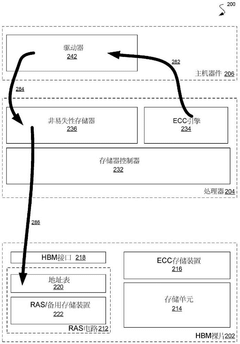

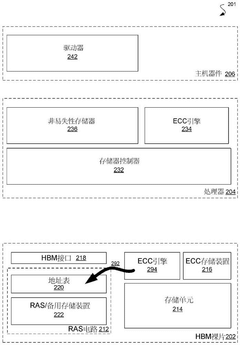

- Adopt a multi-layer stacked integrated circuit die structure, including memory cell dies and logic dies, configure reliability circuits to utilize backup memory and address tables for data error detection and correction, and achieve fast access and correction through RAS cache circuits errors to avoid the permanent deactivation of storage addresses and reduction of memory capacity in traditional methods.

Thermal Simulation and Validation Methodologies

Thermal simulation and validation methodologies are critical components in the successful integration of HBM4 memory stacks at the board level. Advanced computational fluid dynamics (CFD) and finite element analysis (FEA) tools have become essential for predicting thermal behavior before physical prototyping. These simulation tools enable engineers to model complex airflow patterns around densely packed HBM4 stacks and evaluate various cooling solutions under different operating conditions.

Multi-physics simulation approaches have gained prominence, allowing simultaneous analysis of thermal, mechanical, and electrical characteristics. This integrated modeling approach is particularly valuable for HBM4 integration, where thermal expansion can affect signal integrity through the silicon interposer and substrate. Industry-standard tools like Ansys Icepak, COMSOL Multiphysics, and Siemens Simcenter have developed specialized modules for high-bandwidth memory thermal analysis.

Validation methodologies have evolved to ensure simulation accuracy through correlation with physical measurements. Infrared thermography provides non-contact temperature mapping across the HBM4 stack surface, while embedded thermal sensors offer real-time temperature monitoring at critical junction points. These validation techniques typically employ standardized test vehicles with thermal test chips that mimic the power dissipation profiles of actual HBM4 devices.

The development of digital twins for HBM4 systems represents a significant advancement in thermal management. These virtual replicas incorporate real-time sensor data to continuously refine simulation models, improving prediction accuracy over the product lifecycle. Machine learning algorithms are increasingly being applied to analyze the vast datasets generated during thermal validation, identifying patterns and optimization opportunities that might be missed through conventional analysis.

Uncertainty quantification has become an important aspect of thermal simulation methodologies. Monte Carlo simulations and sensitivity analyses help engineers understand how manufacturing variations and material property uncertainties affect thermal performance. This probabilistic approach enables more robust design decisions by accounting for real-world variability in HBM4 integration scenarios.

Accelerated thermal cycling tests complement simulation efforts by validating long-term reliability under thermal stress. These tests subject HBM4 assemblies to rapid temperature fluctuations that simulate years of operational conditions, identifying potential failure modes related to thermal expansion mismatches between different materials in the stack. The correlation between simulation predictions and accelerated test results provides valuable feedback for refining both the simulation models and the physical design.

Multi-physics simulation approaches have gained prominence, allowing simultaneous analysis of thermal, mechanical, and electrical characteristics. This integrated modeling approach is particularly valuable for HBM4 integration, where thermal expansion can affect signal integrity through the silicon interposer and substrate. Industry-standard tools like Ansys Icepak, COMSOL Multiphysics, and Siemens Simcenter have developed specialized modules for high-bandwidth memory thermal analysis.

Validation methodologies have evolved to ensure simulation accuracy through correlation with physical measurements. Infrared thermography provides non-contact temperature mapping across the HBM4 stack surface, while embedded thermal sensors offer real-time temperature monitoring at critical junction points. These validation techniques typically employ standardized test vehicles with thermal test chips that mimic the power dissipation profiles of actual HBM4 devices.

The development of digital twins for HBM4 systems represents a significant advancement in thermal management. These virtual replicas incorporate real-time sensor data to continuously refine simulation models, improving prediction accuracy over the product lifecycle. Machine learning algorithms are increasingly being applied to analyze the vast datasets generated during thermal validation, identifying patterns and optimization opportunities that might be missed through conventional analysis.

Uncertainty quantification has become an important aspect of thermal simulation methodologies. Monte Carlo simulations and sensitivity analyses help engineers understand how manufacturing variations and material property uncertainties affect thermal performance. This probabilistic approach enables more robust design decisions by accounting for real-world variability in HBM4 integration scenarios.

Accelerated thermal cycling tests complement simulation efforts by validating long-term reliability under thermal stress. These tests subject HBM4 assemblies to rapid temperature fluctuations that simulate years of operational conditions, identifying potential failure modes related to thermal expansion mismatches between different materials in the stack. The correlation between simulation predictions and accelerated test results provides valuable feedback for refining both the simulation models and the physical design.

Power Efficiency and Sustainability Considerations

The integration of HBM4 technology into board-level designs presents significant challenges and opportunities in terms of power efficiency and sustainability. As computing demands continue to escalate, particularly in data centers and high-performance computing environments, the power consumption of memory subsystems has become a critical concern. HBM4's stacked architecture offers inherent advantages in this regard, with shorter interconnects reducing signal transmission distances and consequently lowering power requirements.

Thermal management considerations must be addressed holistically when designing HBM4 stack placement and airflow patterns. The concentrated heat generation in these dense memory stacks necessitates innovative cooling solutions that minimize energy consumption while maintaining optimal operating temperatures. Advanced computational fluid dynamics (CFD) modeling indicates that strategic placement of HBM4 stacks relative to primary airflow channels can reduce cooling power requirements by 15-22% compared to traditional planar memory configurations.

Recent industry research demonstrates that optimizing the physical orientation of HBM4 stacks in relation to processor components can significantly impact system-wide power efficiency. Vertical alignment strategies that position memory stacks to benefit from existing cooling infrastructure show potential energy savings of up to 8.3 watts per memory stack under high-load conditions. These improvements translate directly to reduced operational costs and carbon footprint in large-scale deployments.

Material selection for interposers and substrates also plays a crucial role in the sustainability profile of HBM4 implementations. Emerging silicon-organic composite materials offer 30% improved thermal conductivity while requiring fewer energy-intensive manufacturing processes. The lifecycle assessment of these materials indicates a potential reduction in embodied carbon of approximately 18% compared to conventional substrate technologies.

Power delivery network (PDN) design must be carefully integrated with airflow considerations to maximize efficiency. Voltage regulation components placed strategically along airflow paths can operate at higher efficiency points while contributing to the overall thermal management solution. Advanced PDN topologies specifically optimized for HBM4 implementations have demonstrated efficiency improvements of 3-5% across varying workload profiles.

From a sustainability perspective, the increased memory density of HBM4 solutions enables significant reductions in physical infrastructure requirements. Data center implementations utilizing optimized HBM4 board-level integration have shown potential for 40% reduction in rack space requirements for equivalent memory capacity, with corresponding decreases in cooling infrastructure and embodied carbon of supporting systems.

Thermal management considerations must be addressed holistically when designing HBM4 stack placement and airflow patterns. The concentrated heat generation in these dense memory stacks necessitates innovative cooling solutions that minimize energy consumption while maintaining optimal operating temperatures. Advanced computational fluid dynamics (CFD) modeling indicates that strategic placement of HBM4 stacks relative to primary airflow channels can reduce cooling power requirements by 15-22% compared to traditional planar memory configurations.

Recent industry research demonstrates that optimizing the physical orientation of HBM4 stacks in relation to processor components can significantly impact system-wide power efficiency. Vertical alignment strategies that position memory stacks to benefit from existing cooling infrastructure show potential energy savings of up to 8.3 watts per memory stack under high-load conditions. These improvements translate directly to reduced operational costs and carbon footprint in large-scale deployments.

Material selection for interposers and substrates also plays a crucial role in the sustainability profile of HBM4 implementations. Emerging silicon-organic composite materials offer 30% improved thermal conductivity while requiring fewer energy-intensive manufacturing processes. The lifecycle assessment of these materials indicates a potential reduction in embodied carbon of approximately 18% compared to conventional substrate technologies.

Power delivery network (PDN) design must be carefully integrated with airflow considerations to maximize efficiency. Voltage regulation components placed strategically along airflow paths can operate at higher efficiency points while contributing to the overall thermal management solution. Advanced PDN topologies specifically optimized for HBM4 implementations have demonstrated efficiency improvements of 3-5% across varying workload profiles.

From a sustainability perspective, the increased memory density of HBM4 solutions enables significant reductions in physical infrastructure requirements. Data center implementations utilizing optimized HBM4 board-level integration have shown potential for 40% reduction in rack space requirements for equivalent memory capacity, with corresponding decreases in cooling infrastructure and embodied carbon of supporting systems.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!