HBM4 Thermal Constraints: Cooling Interfaces And Heat Spreader Design

SEP 12, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

HBM4 Thermal Management Background and Objectives

High Bandwidth Memory (HBM) technology has evolved significantly since its introduction, with HBM4 representing the latest advancement in this critical memory architecture. The thermal management challenges associated with HBM4 have become increasingly complex due to the escalating power densities and performance requirements in modern computing systems. This technological progression has been driven by the growing demands of artificial intelligence, high-performance computing, and data-intensive applications that require unprecedented memory bandwidth and capacity.

The evolution of HBM technology can be traced through multiple generations, each addressing previous limitations while introducing new capabilities. From HBM1 to HBM2, HBM2E, HBM3, and now HBM4, we have witnessed substantial improvements in bandwidth, capacity, and energy efficiency. However, these advancements have consistently been accompanied by increased thermal challenges, making thermal management a critical factor in realizing the full potential of each new generation.

HBM4's stacked die architecture, while enabling remarkable memory density and bandwidth, creates significant thermal constraints due to the concentration of heat-generating components in a compact three-dimensional structure. The vertical stacking of multiple DRAM dies connected through through-silicon vias (TSVs) results in heat being trapped within the stack, with limited pathways for dissipation. This thermal bottleneck threatens to undermine the performance benefits that HBM4 technology promises.

The primary objective of HBM4 thermal management research is to develop innovative cooling interfaces and heat spreader designs that can effectively address these thermal constraints without compromising the form factor advantages or electrical performance of the memory system. This involves exploring advanced materials with superior thermal conductivity, novel geometric configurations for heat spreaders, and efficient integration methods that maintain the integrity of the memory stack while maximizing heat dissipation.

Another critical goal is to establish comprehensive thermal modeling methodologies that accurately predict temperature distributions within HBM4 stacks under various operating conditions. These models must account for the complex thermal interactions between different components, including silicon dies, microbumps, interposers, and package substrates, to enable effective thermal design optimization.

Furthermore, the research aims to identify the optimal balance between passive and active cooling solutions for different application scenarios, recognizing that the thermal management approach may need to vary based on specific performance requirements, power constraints, and environmental conditions. The ultimate objective is to develop thermal management solutions that enable HBM4 to operate at its full potential while maintaining reliability and longevity across diverse computing platforms.

The evolution of HBM technology can be traced through multiple generations, each addressing previous limitations while introducing new capabilities. From HBM1 to HBM2, HBM2E, HBM3, and now HBM4, we have witnessed substantial improvements in bandwidth, capacity, and energy efficiency. However, these advancements have consistently been accompanied by increased thermal challenges, making thermal management a critical factor in realizing the full potential of each new generation.

HBM4's stacked die architecture, while enabling remarkable memory density and bandwidth, creates significant thermal constraints due to the concentration of heat-generating components in a compact three-dimensional structure. The vertical stacking of multiple DRAM dies connected through through-silicon vias (TSVs) results in heat being trapped within the stack, with limited pathways for dissipation. This thermal bottleneck threatens to undermine the performance benefits that HBM4 technology promises.

The primary objective of HBM4 thermal management research is to develop innovative cooling interfaces and heat spreader designs that can effectively address these thermal constraints without compromising the form factor advantages or electrical performance of the memory system. This involves exploring advanced materials with superior thermal conductivity, novel geometric configurations for heat spreaders, and efficient integration methods that maintain the integrity of the memory stack while maximizing heat dissipation.

Another critical goal is to establish comprehensive thermal modeling methodologies that accurately predict temperature distributions within HBM4 stacks under various operating conditions. These models must account for the complex thermal interactions between different components, including silicon dies, microbumps, interposers, and package substrates, to enable effective thermal design optimization.

Furthermore, the research aims to identify the optimal balance between passive and active cooling solutions for different application scenarios, recognizing that the thermal management approach may need to vary based on specific performance requirements, power constraints, and environmental conditions. The ultimate objective is to develop thermal management solutions that enable HBM4 to operate at its full potential while maintaining reliability and longevity across diverse computing platforms.

Market Demand Analysis for Advanced Memory Cooling Solutions

The global market for advanced memory cooling solutions is experiencing unprecedented growth, driven primarily by the rapid evolution of High Bandwidth Memory (HBM) technologies. With the imminent arrival of HBM4, thermal management has become a critical bottleneck in system performance and reliability. Current market analysis indicates that the data center cooling market alone is projected to reach $20 billion by 2025, with HBM thermal solutions representing a significant growth segment within this space.

The demand for advanced cooling interfaces and heat spreader designs is being fueled by several converging market factors. First, artificial intelligence and machine learning workloads continue to intensify computational demands, with training models requiring exponentially more memory bandwidth. This has created a substantial market pull for HBM4 implementation despite its thermal challenges, as organizations prioritize performance gains over cooling complexities.

Enterprise data centers represent the largest market segment, accounting for approximately 45% of the demand for advanced memory cooling solutions. Cloud service providers follow closely at 32%, while high-performance computing installations contribute about 18% of market demand. The remaining 5% comes from specialized applications in telecommunications, aerospace, and defense sectors.

Geographically, North America leads the market with 38% share, followed by Asia-Pacific at 34%, which is experiencing the fastest growth rate at 24% annually. Europe accounts for 22% of the market, with emerging economies showing increasing adoption rates as they expand their digital infrastructure.

A significant market trend is the growing preference for liquid cooling solutions, which has seen a 27% year-over-year increase in adoption rates. This shift is directly related to the thermal constraints of HBM4, which generates heat densities exceeding 500W/cm², far beyond the capabilities of traditional air cooling methods.

Customer requirements are evolving rapidly, with system integrators demanding cooling solutions that can maintain HBM4 junction temperatures below 85°C while operating in increasingly dense server environments. Energy efficiency has also emerged as a critical purchasing factor, with 78% of enterprise customers citing cooling power consumption as a major consideration in their procurement decisions.

The market is also witnessing increased demand for integrated cooling solutions that address both the CPU/GPU and HBM thermal challenges simultaneously, creating opportunities for vendors who can provide holistic thermal management approaches. This trend is reflected in recent procurement patterns, where 63% of data center operators are prioritizing vendors offering comprehensive cooling ecosystems rather than component-level solutions.

The demand for advanced cooling interfaces and heat spreader designs is being fueled by several converging market factors. First, artificial intelligence and machine learning workloads continue to intensify computational demands, with training models requiring exponentially more memory bandwidth. This has created a substantial market pull for HBM4 implementation despite its thermal challenges, as organizations prioritize performance gains over cooling complexities.

Enterprise data centers represent the largest market segment, accounting for approximately 45% of the demand for advanced memory cooling solutions. Cloud service providers follow closely at 32%, while high-performance computing installations contribute about 18% of market demand. The remaining 5% comes from specialized applications in telecommunications, aerospace, and defense sectors.

Geographically, North America leads the market with 38% share, followed by Asia-Pacific at 34%, which is experiencing the fastest growth rate at 24% annually. Europe accounts for 22% of the market, with emerging economies showing increasing adoption rates as they expand their digital infrastructure.

A significant market trend is the growing preference for liquid cooling solutions, which has seen a 27% year-over-year increase in adoption rates. This shift is directly related to the thermal constraints of HBM4, which generates heat densities exceeding 500W/cm², far beyond the capabilities of traditional air cooling methods.

Customer requirements are evolving rapidly, with system integrators demanding cooling solutions that can maintain HBM4 junction temperatures below 85°C while operating in increasingly dense server environments. Energy efficiency has also emerged as a critical purchasing factor, with 78% of enterprise customers citing cooling power consumption as a major consideration in their procurement decisions.

The market is also witnessing increased demand for integrated cooling solutions that address both the CPU/GPU and HBM thermal challenges simultaneously, creating opportunities for vendors who can provide holistic thermal management approaches. This trend is reflected in recent procurement patterns, where 63% of data center operators are prioritizing vendors offering comprehensive cooling ecosystems rather than component-level solutions.

Current Thermal Constraints and Challenges in HBM4 Technology

HBM4 technology faces significant thermal challenges that have become increasingly critical as memory bandwidth demands continue to escalate. Current HBM4 implementations struggle with heat dissipation due to their high-density stacked architecture, where multiple DRAM dies are vertically integrated with through-silicon vias (TSVs). This compact design creates thermal bottlenecks that can severely impact performance, reliability, and lifespan of memory systems.

The power density in HBM4 has increased substantially compared to previous generations, with estimates suggesting power consumption reaching 15-20W per stack during peak operations. This represents approximately a 30-40% increase over HBM3E, creating unprecedented cooling challenges. The limited surface area available for heat extraction compounds this issue, as the primary heat dissipation path remains through the interposer and package substrate.

Temperature gradients within the HBM4 stack present another significant challenge. The dies positioned furthest from the heat spreader can experience temperatures 15-20°C higher than those closest to cooling solutions. These thermal gradients induce mechanical stress due to differential thermal expansion, potentially leading to reliability issues such as solder joint fatigue and delamination at interfaces.

Current cooling interfaces for HBM4 rely predominantly on thermal interface materials (TIMs) with thermal conductivities ranging from 3-8 W/mK, which are increasingly inadequate for managing the thermal loads. The interface quality between the HBM stack and heat spreader has become a critical bottleneck, with contact resistance accounting for approximately 30% of the total thermal resistance in some implementations.

Heat spreader designs currently employed with HBM4 typically utilize copper or aluminum structures with limited geometric optimization. These conventional designs struggle to distribute heat evenly across the spreader surface, resulting in hotspots that can exceed thermal specifications. The thermal resistance from junction to ambient (Rja) in current solutions ranges from 0.3 to 0.5 °C/W, which is insufficient for maintaining optimal operating temperatures under sustained workloads.

Liquid cooling solutions are being explored but face integration challenges due to the proximity of HBM4 stacks to processing units on the same package. The risk of coolant leakage and the complexity of implementing liquid cooling pathways in dense computing environments remain significant barriers to adoption.

The industry is also confronting challenges related to thermal simulation accuracy. Current modeling approaches struggle to accurately predict temperature distributions within HBM4 stacks, particularly at the microbump and TSV levels. This modeling gap hampers the development of optimized thermal solutions and necessitates conservative design approaches that may limit performance potential.

The power density in HBM4 has increased substantially compared to previous generations, with estimates suggesting power consumption reaching 15-20W per stack during peak operations. This represents approximately a 30-40% increase over HBM3E, creating unprecedented cooling challenges. The limited surface area available for heat extraction compounds this issue, as the primary heat dissipation path remains through the interposer and package substrate.

Temperature gradients within the HBM4 stack present another significant challenge. The dies positioned furthest from the heat spreader can experience temperatures 15-20°C higher than those closest to cooling solutions. These thermal gradients induce mechanical stress due to differential thermal expansion, potentially leading to reliability issues such as solder joint fatigue and delamination at interfaces.

Current cooling interfaces for HBM4 rely predominantly on thermal interface materials (TIMs) with thermal conductivities ranging from 3-8 W/mK, which are increasingly inadequate for managing the thermal loads. The interface quality between the HBM stack and heat spreader has become a critical bottleneck, with contact resistance accounting for approximately 30% of the total thermal resistance in some implementations.

Heat spreader designs currently employed with HBM4 typically utilize copper or aluminum structures with limited geometric optimization. These conventional designs struggle to distribute heat evenly across the spreader surface, resulting in hotspots that can exceed thermal specifications. The thermal resistance from junction to ambient (Rja) in current solutions ranges from 0.3 to 0.5 °C/W, which is insufficient for maintaining optimal operating temperatures under sustained workloads.

Liquid cooling solutions are being explored but face integration challenges due to the proximity of HBM4 stacks to processing units on the same package. The risk of coolant leakage and the complexity of implementing liquid cooling pathways in dense computing environments remain significant barriers to adoption.

The industry is also confronting challenges related to thermal simulation accuracy. Current modeling approaches struggle to accurately predict temperature distributions within HBM4 stacks, particularly at the microbump and TSV levels. This modeling gap hampers the development of optimized thermal solutions and necessitates conservative design approaches that may limit performance potential.

Current Cooling Interface and Heat Spreader Design Approaches

01 Thermal management solutions for HBM4

Various thermal management solutions are implemented to address the thermal constraints of HBM4 memory. These include heat spreaders, thermal interface materials, and advanced cooling systems designed specifically for high-bandwidth memory architectures. These solutions help dissipate heat efficiently from the densely packed memory stacks, preventing thermal throttling and maintaining optimal performance under high workloads.- Thermal management solutions for HBM4: Various thermal management solutions are implemented to address the thermal constraints of HBM4 memory. These include heat spreaders, thermal interface materials, and advanced cooling systems designed specifically for high-bandwidth memory architectures. These solutions help dissipate heat efficiently from the densely packed memory stacks, preventing thermal throttling and maintaining optimal performance under high workloads.

- Temperature monitoring and control systems: Temperature monitoring and control systems are integrated into HBM4 implementations to manage thermal constraints. These systems include temperature sensors, thermal management controllers, and dynamic frequency scaling mechanisms that adjust memory operations based on temperature readings. By continuously monitoring thermal conditions, these systems can prevent overheating while maximizing performance within safe thermal limits.

- 3D stacking architecture optimizations: Optimizations in the 3D stacking architecture of HBM4 help address thermal constraints. These include improved through-silicon via (TSV) designs, thermal-aware stack arrangements, and materials with better thermal conductivity. The architecture is designed to facilitate better heat dissipation pathways through the multiple layers of memory dies, reducing hotspots and improving overall thermal performance.

- Power management techniques: Advanced power management techniques are employed to reduce heat generation in HBM4 memory systems. These include dynamic voltage and frequency scaling, power gating of unused memory banks, and intelligent refresh mechanisms. By reducing power consumption during operation, these techniques directly address thermal constraints by limiting the amount of heat generated in the first place.

- System-level thermal design considerations: System-level thermal design considerations for HBM4 integration include optimized placement on the package substrate, thermal-aware floorplanning, and coordinated cooling solutions with the host processor. These approaches consider the entire computing system's thermal envelope, ensuring that HBM4 memory can operate within thermal constraints while maintaining high bandwidth and low latency connections to processing elements.

02 Temperature monitoring and control systems

Advanced temperature monitoring and control systems are employed to manage thermal constraints in HBM4 implementations. These systems include integrated temperature sensors, thermal feedback loops, and dynamic thermal management algorithms that can adjust memory operations based on temperature readings. This approach helps maintain memory performance while preventing overheating issues in high-performance computing environments.Expand Specific Solutions03 Power management techniques for thermal optimization

Power management techniques are implemented to optimize thermal performance of HBM4 memory systems. These include dynamic voltage and frequency scaling, intelligent power allocation, and workload-aware power management that reduces energy consumption during periods of lower activity. By controlling power consumption, these techniques effectively manage heat generation in HBM4 memory stacks.Expand Specific Solutions04 Structural design innovations for heat dissipation

Innovative structural designs are developed to enhance heat dissipation in HBM4 memory systems. These include specialized package designs with improved thermal pathways, optimized substrate materials with better thermal conductivity, and novel stacking arrangements that facilitate more efficient cooling. These structural innovations help address the thermal constraints inherent in the high-density memory architecture of HBM4.Expand Specific Solutions05 Integration of HBM4 with system-level thermal solutions

System-level thermal solutions are designed to integrate with HBM4 memory for comprehensive thermal management. These include coordinated cooling approaches that consider the entire computing system, liquid cooling solutions specifically designed for high-performance memory, and thermal-aware system architectures that optimize component placement for heat dissipation. This holistic approach ensures that HBM4 memory can operate within thermal constraints while maintaining system performance.Expand Specific Solutions

Key Industry Players in HBM4 and Thermal Solution Development

The HBM4 thermal constraints market is currently in an early growth phase, with increasing demand driven by AI and high-performance computing applications. Major semiconductor players like Intel, Micron Technology, and GLOBALFOUNDRIES are competing to develop advanced cooling solutions for high-bandwidth memory. IBM and Toshiba lead in thermal management innovation, with research institutions like Tsinghua University and Xi'an Jiaotong University contributing significant academic advancements. The market is characterized by collaborative efforts between semiconductor manufacturers and thermal solution providers like Laird Technologies and Henkel. Technical challenges remain in heat spreader design and cooling interfaces, with companies exploring liquid cooling, phase-change materials, and integrated thermal solutions to address the increasing power densities of next-generation HBM4 implementations.

International Business Machines Corp.

Technical Solution: IBM has pioneered a novel approach to HBM4 thermal management through their "Direct Liquid Cooling to Memory" technology. This solution directly addresses the thermal constraints of high-bandwidth memory by implementing a micro-scale cooling system that brings coolant in close proximity to the memory dies without risking electrical interference. IBM's design incorporates specialized heat spreaders with embedded microfluidic channels that are precision-manufactured to maximize cooling efficiency while maintaining the strict z-height requirements of HBM4 packages. The company has developed proprietary thermal interface materials that bridge the gap between silicon dies and cooling structures with minimal thermal resistance. IBM's solution also features a modular design that allows for cooling system maintenance without disturbing the memory-processor connections, addressing a key reliability concern in high-performance computing environments. Their approach has demonstrated the ability to maintain HBM4 operating temperatures below 85°C even under maximum computational loads.

Strengths: Direct liquid cooling approach provides exceptional thermal performance; modular design improves serviceability and system reliability. Weaknesses: Requires specialized cooling infrastructure that may not be compatible with all data center environments; higher initial implementation costs compared to conventional cooling solutions.

Intel Corp.

Technical Solution: Intel has developed advanced thermal management solutions for HBM4 memory that integrate directly with their compute platforms. Their approach includes a multi-layered cooling interface that combines micro-channel liquid cooling with advanced thermal interface materials (TIMs) specifically engineered for the high thermal density of HBM4 stacks. Intel's solution incorporates a copper-based heat spreader design with optimized geometry that maximizes surface area while maintaining structural integrity under thermal expansion. The company has implemented vapor chamber technology within their heat spreaders that allows for more uniform heat distribution across the entire HBM4 package, reducing hotspots and improving overall thermal performance. Intel's cooling solution also features an integrated temperature monitoring system that dynamically adjusts cooling parameters based on real-time thermal conditions, ensuring optimal performance while preventing thermal throttling.

Strengths: Comprehensive integration with compute platforms allows for system-level thermal optimization; advanced vapor chamber technology provides superior heat distribution. Weaknesses: Solutions are primarily optimized for Intel's own processor architectures; implementation complexity may increase manufacturing costs and potential points of failure.

Critical Thermal Interface Materials and Heat Transfer Technologies

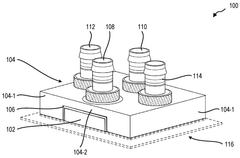

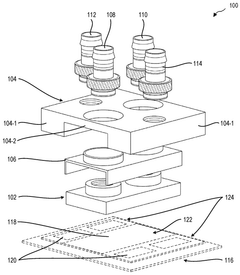

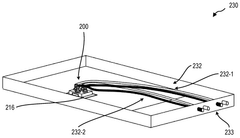

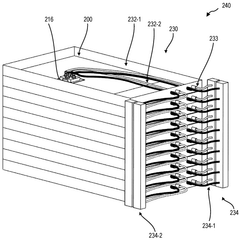

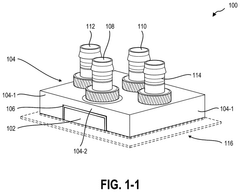

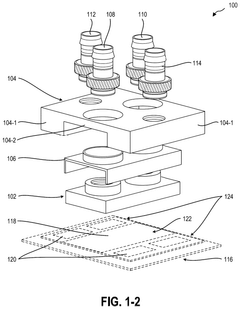

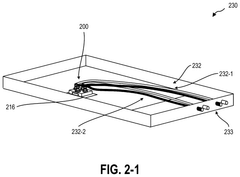

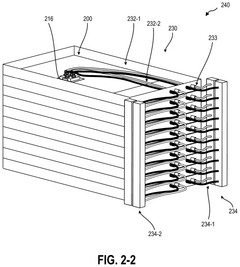

Optimized chip cooling infrastructure

PatentWO2025042547A1

Innovation

- A cold plate assembly with separate cooling structures and coolant loops for processing and memory components, where the first cooling structure provides cooling to the processing component at a higher temperature, and the second cooling structure, connected via a thermal barrier, provides cooling to the memory components at a lower temperature.

Optimized chip cooling infrastructure

PatentPendingUS20250063688A1

Innovation

- A cold plate assembly with separate cooling structures and coolant loops for different temperature sections of a computing device, where a first cooling structure provides cooling to a processing component at a higher temperature, and a second cooling structure, connected via a thermal barrier, provides cooling to memory components at a lower temperature.

Environmental Impact and Sustainability of Cooling Solutions

The environmental impact of cooling solutions for HBM4 memory has become increasingly significant as data centers and high-performance computing systems continue to expand globally. Traditional cooling methods often rely on materials and processes that contribute substantially to carbon footprints and resource depletion. The manufacturing of copper heat spreaders and aluminum heat sinks, commonly used in HBM4 thermal management, requires extensive mining operations and energy-intensive processing, resulting in considerable environmental degradation.

Water-based cooling systems, while effective for HBM4's high thermal density, present sustainability challenges related to water consumption and treatment. In regions facing water scarcity, the implementation of liquid cooling solutions may exacerbate existing resource constraints. Additionally, the chemical additives used in coolants to prevent corrosion and biological growth can introduce toxins into the environment if not properly managed at end-of-life.

The refrigerants employed in phase-change cooling systems for advanced HBM4 applications often have high global warming potential (GWP). Although modern refrigerants have reduced ozone depletion potential compared to their predecessors, their contribution to climate change remains substantial. The industry is gradually transitioning toward natural refrigerants with lower environmental impact, but adoption rates vary significantly across different markets.

Energy consumption represents another critical environmental consideration. While efficient cooling designs can reduce the operational energy requirements of HBM4 memory systems, the manufacturing energy debt and embodied carbon of sophisticated cooling solutions must be factored into sustainability assessments. Life cycle analyses indicate that advanced cooling technologies may require 3-5 years of operation before their energy savings offset their production impact.

Emerging sustainable approaches include the development of biodegradable thermal interface materials, recyclable heat spreader designs, and cooling systems optimized for eventual material recovery. Some manufacturers have begun implementing closed-loop manufacturing processes that recapture and reuse materials from decommissioned cooling systems, reducing waste and resource consumption.

The regulatory landscape surrounding cooling technologies is evolving rapidly, with increasing pressure to adopt environmentally responsible practices. The European Union's Restriction of Hazardous Substances (RoHS) and Registration, Evaluation, Authorization and Restriction of Chemicals (REACH) regulations have already impacted material selection for thermal solutions, while carbon pricing mechanisms in various regions are driving innovation toward more sustainable cooling approaches for HBM4 and other high-performance computing components.

Water-based cooling systems, while effective for HBM4's high thermal density, present sustainability challenges related to water consumption and treatment. In regions facing water scarcity, the implementation of liquid cooling solutions may exacerbate existing resource constraints. Additionally, the chemical additives used in coolants to prevent corrosion and biological growth can introduce toxins into the environment if not properly managed at end-of-life.

The refrigerants employed in phase-change cooling systems for advanced HBM4 applications often have high global warming potential (GWP). Although modern refrigerants have reduced ozone depletion potential compared to their predecessors, their contribution to climate change remains substantial. The industry is gradually transitioning toward natural refrigerants with lower environmental impact, but adoption rates vary significantly across different markets.

Energy consumption represents another critical environmental consideration. While efficient cooling designs can reduce the operational energy requirements of HBM4 memory systems, the manufacturing energy debt and embodied carbon of sophisticated cooling solutions must be factored into sustainability assessments. Life cycle analyses indicate that advanced cooling technologies may require 3-5 years of operation before their energy savings offset their production impact.

Emerging sustainable approaches include the development of biodegradable thermal interface materials, recyclable heat spreader designs, and cooling systems optimized for eventual material recovery. Some manufacturers have begun implementing closed-loop manufacturing processes that recapture and reuse materials from decommissioned cooling systems, reducing waste and resource consumption.

The regulatory landscape surrounding cooling technologies is evolving rapidly, with increasing pressure to adopt environmentally responsible practices. The European Union's Restriction of Hazardous Substances (RoHS) and Registration, Evaluation, Authorization and Restriction of Chemicals (REACH) regulations have already impacted material selection for thermal solutions, while carbon pricing mechanisms in various regions are driving innovation toward more sustainable cooling approaches for HBM4 and other high-performance computing components.

Integration Challenges with Heterogeneous Computing Systems

The integration of HBM4 memory with heterogeneous computing systems presents significant challenges that extend beyond thermal management alone. Heterogeneous computing architectures, which combine different types of processors (CPUs, GPUs, FPGAs, ASICs) with specialized memory subsystems, create complex integration scenarios that must be carefully addressed.

Physical integration constraints represent a primary challenge when incorporating HBM4 into these systems. The 3D stacked nature of HBM4 requires precise alignment with interposers or substrates, while maintaining the integrity of thousands of microbumps and through-silicon vias (TSVs). The dimensional tolerances become increasingly critical as computing systems incorporate multiple HBM stacks alongside various processing elements.

Signal integrity issues emerge as another significant concern. The high-speed interfaces between HBM4 and different computing elements must maintain signal quality across varying distances and through different materials. Cross-talk, impedance matching, and timing synchronization become particularly challenging when integrating memory with diverse processing architectures operating at different clock domains and voltage levels.

Power delivery networks face substantial complications in heterogeneous systems incorporating HBM4. The varying power requirements of different computing elements, combined with HBM4's own power profile, necessitate sophisticated power distribution architectures. Voltage droop and power integrity issues can severely impact system stability, especially during workload transitions between different computing elements accessing the shared memory resources.

Firmware and driver integration presents additional complexity. Heterogeneous systems require coordinated memory management across different processing elements, each potentially running different operating systems or firmware. Memory coherency, access prioritization, and bandwidth allocation must be carefully orchestrated to prevent conflicts and ensure optimal performance across the system.

Testing and validation methodologies become exponentially more complex in heterogeneous environments. Traditional memory testing approaches must be adapted to account for the varied access patterns and timing requirements of different computing elements. Comprehensive system-level validation must verify proper operation across all possible operating modes and transitions between computing elements.

Manufacturing scalability represents a final integration challenge. The assembly process for heterogeneous systems with HBM4 involves multiple specialized steps that must be precisely coordinated. Yield management becomes particularly difficult when integrating components with different manufacturing maturity levels and reliability characteristics.

Physical integration constraints represent a primary challenge when incorporating HBM4 into these systems. The 3D stacked nature of HBM4 requires precise alignment with interposers or substrates, while maintaining the integrity of thousands of microbumps and through-silicon vias (TSVs). The dimensional tolerances become increasingly critical as computing systems incorporate multiple HBM stacks alongside various processing elements.

Signal integrity issues emerge as another significant concern. The high-speed interfaces between HBM4 and different computing elements must maintain signal quality across varying distances and through different materials. Cross-talk, impedance matching, and timing synchronization become particularly challenging when integrating memory with diverse processing architectures operating at different clock domains and voltage levels.

Power delivery networks face substantial complications in heterogeneous systems incorporating HBM4. The varying power requirements of different computing elements, combined with HBM4's own power profile, necessitate sophisticated power distribution architectures. Voltage droop and power integrity issues can severely impact system stability, especially during workload transitions between different computing elements accessing the shared memory resources.

Firmware and driver integration presents additional complexity. Heterogeneous systems require coordinated memory management across different processing elements, each potentially running different operating systems or firmware. Memory coherency, access prioritization, and bandwidth allocation must be carefully orchestrated to prevent conflicts and ensure optimal performance across the system.

Testing and validation methodologies become exponentially more complex in heterogeneous environments. Traditional memory testing approaches must be adapted to account for the varied access patterns and timing requirements of different computing elements. Comprehensive system-level validation must verify proper operation across all possible operating modes and transitions between computing elements.

Manufacturing scalability represents a final integration challenge. The assembly process for heterogeneous systems with HBM4 involves multiple specialized steps that must be precisely coordinated. Yield management becomes particularly difficult when integrating components with different manufacturing maturity levels and reliability characteristics.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!