HBM4 Moisture Sensitivity And Reliability In High-Density Packaging

SEP 12, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

HBM4 Technology Evolution and Reliability Goals

High Bandwidth Memory (HBM) technology has evolved significantly since its inception, with HBM4 representing the latest advancement in this critical memory architecture. The evolution from HBM1 to HBM4 has been characterized by increasing bandwidth, capacity, and power efficiency to meet the growing demands of data-intensive applications such as artificial intelligence, high-performance computing, and graphics processing.

HBM1, introduced in 2013, offered a bandwidth of approximately 128 GB/s per stack with a capacity of up to 4GB. HBM2, which followed in 2016, doubled the bandwidth to around 256 GB/s per stack while increasing capacity to 8GB. HBM2E, an enhancement to HBM2, further improved performance with bandwidths reaching up to 460 GB/s per stack and capacities of up to 16GB.

HBM3, released in 2021, represented a significant leap forward with bandwidths exceeding 665 GB/s per stack and capacities reaching 24GB. Now, HBM4 aims to push these boundaries even further, with projected bandwidths of over 1 TB/s per stack and capacities potentially reaching 36GB or more, while maintaining or improving power efficiency metrics.

The technological progression of HBM has been driven by several key innovations: increasing the number of DRAM dies in each stack, enhancing the through-silicon via (TSV) density and performance, improving the interposer technology for die-to-die connections, and advancing the packaging techniques to manage thermal challenges and signal integrity.

As HBM4 technology advances, reliability goals have become increasingly stringent, particularly regarding moisture sensitivity. The high-density packaging of HBM4, with its complex 3D stacking architecture and numerous interconnects, creates unique challenges for moisture management. Moisture ingress can lead to various failure mechanisms including delamination, interfacial cracking, and electrochemical migration, all of which can compromise the integrity and performance of the memory system.

The reliability targets for HBM4 include achieving Moisture Sensitivity Level (MSL) ratings that allow for practical manufacturing and assembly processes while ensuring long-term operational stability. Industry standards typically aim for MSL 3 or better, which requires the components to withstand exposure to ambient conditions for up to 168 hours before assembly without degradation.

Additionally, HBM4 reliability goals encompass thermal cycling resilience, as the disparate coefficient of thermal expansion (CTE) between materials in the stack can induce mechanical stress during temperature fluctuations. Electromigration resistance is another critical reliability target, particularly as current densities increase with higher bandwidth requirements.

HBM1, introduced in 2013, offered a bandwidth of approximately 128 GB/s per stack with a capacity of up to 4GB. HBM2, which followed in 2016, doubled the bandwidth to around 256 GB/s per stack while increasing capacity to 8GB. HBM2E, an enhancement to HBM2, further improved performance with bandwidths reaching up to 460 GB/s per stack and capacities of up to 16GB.

HBM3, released in 2021, represented a significant leap forward with bandwidths exceeding 665 GB/s per stack and capacities reaching 24GB. Now, HBM4 aims to push these boundaries even further, with projected bandwidths of over 1 TB/s per stack and capacities potentially reaching 36GB or more, while maintaining or improving power efficiency metrics.

The technological progression of HBM has been driven by several key innovations: increasing the number of DRAM dies in each stack, enhancing the through-silicon via (TSV) density and performance, improving the interposer technology for die-to-die connections, and advancing the packaging techniques to manage thermal challenges and signal integrity.

As HBM4 technology advances, reliability goals have become increasingly stringent, particularly regarding moisture sensitivity. The high-density packaging of HBM4, with its complex 3D stacking architecture and numerous interconnects, creates unique challenges for moisture management. Moisture ingress can lead to various failure mechanisms including delamination, interfacial cracking, and electrochemical migration, all of which can compromise the integrity and performance of the memory system.

The reliability targets for HBM4 include achieving Moisture Sensitivity Level (MSL) ratings that allow for practical manufacturing and assembly processes while ensuring long-term operational stability. Industry standards typically aim for MSL 3 or better, which requires the components to withstand exposure to ambient conditions for up to 168 hours before assembly without degradation.

Additionally, HBM4 reliability goals encompass thermal cycling resilience, as the disparate coefficient of thermal expansion (CTE) between materials in the stack can induce mechanical stress during temperature fluctuations. Electromigration resistance is another critical reliability target, particularly as current densities increase with higher bandwidth requirements.

Market Demand for High-Density Memory Solutions

The global demand for high-density memory solutions has experienced unprecedented growth in recent years, primarily driven by the rapid expansion of data-intensive applications across multiple sectors. Artificial Intelligence (AI) and Machine Learning (ML) workloads have emerged as significant drivers, requiring massive parallel processing capabilities and high-bandwidth memory access to handle complex neural network training and inference operations. Industry reports indicate that AI training models have grown from millions to trillions of parameters within just a few years, creating exponential demand for memory bandwidth and capacity.

Cloud computing and data center operations represent another substantial market segment pushing the boundaries of memory technology. With the global data sphere projected to reach 175 zettabytes by 2025, data centers require increasingly dense memory solutions to process, store, and analyze this information efficiently. High Bandwidth Memory (HBM) technologies, particularly the upcoming HBM4 standard, are positioned as critical components to address these computational bottlenecks.

The high-performance computing (HPC) sector continues to demand advanced memory solutions for scientific research, weather forecasting, genomic sequencing, and complex simulations. These applications require not only high bandwidth but also exceptional reliability under intensive computational loads, making moisture-resistant packaging a critical factor in their deployment environments.

Consumer electronics, particularly high-end graphics processing and gaming applications, represent a growing market segment for high-density memory. The gaming industry's push toward 8K resolution, ray tracing, and virtual reality experiences has created substantial demand for memory solutions that can deliver both capacity and speed while maintaining thermal efficiency.

Automotive and industrial applications are emerging as significant growth areas for high-density memory solutions. Advanced driver-assistance systems (ADAS), autonomous vehicles, and industrial automation require robust memory components that can withstand harsh environmental conditions while delivering reliable performance. The moisture sensitivity concerns in HBM4 packaging are particularly relevant in these sectors, where operating environments may include temperature extremes and varying humidity levels.

Market analysis reveals that customers across these segments increasingly prioritize not just performance metrics but also reliability and longevity. The total cost of ownership calculations now routinely factor in failure rates and replacement costs, making moisture resistance in high-density packaging a competitive differentiator rather than merely a technical specification.

The geographical distribution of demand shows particular concentration in regions with advanced semiconductor manufacturing and AI research hubs, including North America, East Asia, and parts of Europe. However, as edge computing applications proliferate globally, the demand for reliable high-density memory solutions is becoming increasingly distributed across diverse environmental conditions.

Cloud computing and data center operations represent another substantial market segment pushing the boundaries of memory technology. With the global data sphere projected to reach 175 zettabytes by 2025, data centers require increasingly dense memory solutions to process, store, and analyze this information efficiently. High Bandwidth Memory (HBM) technologies, particularly the upcoming HBM4 standard, are positioned as critical components to address these computational bottlenecks.

The high-performance computing (HPC) sector continues to demand advanced memory solutions for scientific research, weather forecasting, genomic sequencing, and complex simulations. These applications require not only high bandwidth but also exceptional reliability under intensive computational loads, making moisture-resistant packaging a critical factor in their deployment environments.

Consumer electronics, particularly high-end graphics processing and gaming applications, represent a growing market segment for high-density memory. The gaming industry's push toward 8K resolution, ray tracing, and virtual reality experiences has created substantial demand for memory solutions that can deliver both capacity and speed while maintaining thermal efficiency.

Automotive and industrial applications are emerging as significant growth areas for high-density memory solutions. Advanced driver-assistance systems (ADAS), autonomous vehicles, and industrial automation require robust memory components that can withstand harsh environmental conditions while delivering reliable performance. The moisture sensitivity concerns in HBM4 packaging are particularly relevant in these sectors, where operating environments may include temperature extremes and varying humidity levels.

Market analysis reveals that customers across these segments increasingly prioritize not just performance metrics but also reliability and longevity. The total cost of ownership calculations now routinely factor in failure rates and replacement costs, making moisture resistance in high-density packaging a competitive differentiator rather than merely a technical specification.

The geographical distribution of demand shows particular concentration in regions with advanced semiconductor manufacturing and AI research hubs, including North America, East Asia, and parts of Europe. However, as edge computing applications proliferate globally, the demand for reliable high-density memory solutions is becoming increasingly distributed across diverse environmental conditions.

Current Challenges in HBM4 Moisture Sensitivity

HBM4 technology faces significant moisture sensitivity challenges that threaten its reliability in high-density packaging applications. The primary concern stems from the increasingly complex 3D stacking architecture with thinner silicon, more TSVs (Through-Silicon Vias), and finer interconnects. These structural characteristics make HBM4 particularly vulnerable to moisture ingress, which can lead to various failure mechanisms including delamination, popcorn cracking, and interfacial adhesion degradation.

Moisture absorption occurs primarily during assembly, testing, and storage processes, with critical exposure points during reflow soldering when temperatures reach 260°C. At these elevated temperatures, trapped moisture vaporizes rapidly, creating internal pressure that can compromise package integrity. The problem is exacerbated by HBM4's larger die size and increased layer count compared to previous generations, providing more potential pathways for moisture penetration.

Current industry standards for moisture sensitivity levels (MSL) are proving inadequate for HBM4 technology. While most high-performance computing components typically require MSL 3 handling (168-hour floor life at 30°C/60% RH), HBM4 packages often demonstrate characteristics requiring more stringent MSL 2 or even MSL 1 classifications, significantly complicating manufacturing logistics and increasing costs.

Material interface challenges represent another critical concern. The coefficient of thermal expansion (CTE) mismatch between different materials in the HBM4 stack creates mechanical stress during temperature cycling. When combined with moisture presence, this stress accelerates delamination at material interfaces, particularly between the silicon die, underfill materials, and substrate layers. Recent reliability studies have shown interface delamination rates increasing by 35-40% in high-humidity environments compared to controlled dry conditions.

The microbump connections in HBM4, which have been reduced to sub-10μm pitch, present unique moisture-related failure mechanisms. Moisture-induced corrosion and electrochemical migration between these closely spaced interconnects can create electrical shorts or opens. The reduced spacing between microbumps accelerates ion migration in the presence of moisture and electrical bias, with mean-time-to-failure (MTTF) decreasing exponentially as humidity levels increase.

Testing methodologies for moisture sensitivity also present significant challenges. Traditional JEDEC standards for moisture sensitivity assessment were developed for conventional packaging technologies and do not adequately address the unique characteristics of HBM4's 3D architecture. The industry lacks standardized test protocols specifically designed to evaluate moisture effects on high-density memory stacks with multiple die layers and thousands of interconnects.

Finally, there are substantial challenges in developing effective moisture barrier coatings and materials for HBM4. Current conformal coating technologies struggle to provide uniform coverage across the complex topography of HBM4 packages, leaving vulnerable areas exposed to moisture ingress. The need for materials that combine excellent moisture resistance with appropriate thermal and electrical properties remains a significant technical hurdle.

Moisture absorption occurs primarily during assembly, testing, and storage processes, with critical exposure points during reflow soldering when temperatures reach 260°C. At these elevated temperatures, trapped moisture vaporizes rapidly, creating internal pressure that can compromise package integrity. The problem is exacerbated by HBM4's larger die size and increased layer count compared to previous generations, providing more potential pathways for moisture penetration.

Current industry standards for moisture sensitivity levels (MSL) are proving inadequate for HBM4 technology. While most high-performance computing components typically require MSL 3 handling (168-hour floor life at 30°C/60% RH), HBM4 packages often demonstrate characteristics requiring more stringent MSL 2 or even MSL 1 classifications, significantly complicating manufacturing logistics and increasing costs.

Material interface challenges represent another critical concern. The coefficient of thermal expansion (CTE) mismatch between different materials in the HBM4 stack creates mechanical stress during temperature cycling. When combined with moisture presence, this stress accelerates delamination at material interfaces, particularly between the silicon die, underfill materials, and substrate layers. Recent reliability studies have shown interface delamination rates increasing by 35-40% in high-humidity environments compared to controlled dry conditions.

The microbump connections in HBM4, which have been reduced to sub-10μm pitch, present unique moisture-related failure mechanisms. Moisture-induced corrosion and electrochemical migration between these closely spaced interconnects can create electrical shorts or opens. The reduced spacing between microbumps accelerates ion migration in the presence of moisture and electrical bias, with mean-time-to-failure (MTTF) decreasing exponentially as humidity levels increase.

Testing methodologies for moisture sensitivity also present significant challenges. Traditional JEDEC standards for moisture sensitivity assessment were developed for conventional packaging technologies and do not adequately address the unique characteristics of HBM4's 3D architecture. The industry lacks standardized test protocols specifically designed to evaluate moisture effects on high-density memory stacks with multiple die layers and thousands of interconnects.

Finally, there are substantial challenges in developing effective moisture barrier coatings and materials for HBM4. Current conformal coating technologies struggle to provide uniform coverage across the complex topography of HBM4 packages, leaving vulnerable areas exposed to moisture ingress. The need for materials that combine excellent moisture resistance with appropriate thermal and electrical properties remains a significant technical hurdle.

Existing Moisture Protection Solutions for HBM4

01 Moisture protection mechanisms for HBM4

High Bandwidth Memory 4 (HBM4) requires specific moisture protection mechanisms to ensure reliability. These include specialized packaging techniques, moisture barrier layers, and hermetic sealing methods that prevent moisture ingress. Advanced encapsulation materials are used to create a protective barrier around the memory stack, while desiccant materials may be incorporated within the package to absorb any residual moisture. These protection mechanisms are critical for maintaining the long-term reliability of HBM4 components, especially in environments with varying humidity levels.- Moisture protection mechanisms for HBM4: High Bandwidth Memory 4 (HBM4) requires specific moisture protection mechanisms to ensure reliability. These include specialized packaging techniques, moisture barrier layers, and hermetic sealing methods that prevent moisture ingress. Advanced encapsulation materials are used to create a protective barrier around the memory stack, while desiccant materials may be incorporated within the package to absorb any residual moisture. These protection mechanisms are critical for maintaining the long-term reliability of HBM4 components, especially in environments with varying humidity levels.

- Reliability testing methods for HBM4: Specialized reliability testing methods are employed to evaluate the moisture sensitivity and overall reliability of HBM4 memory. These include accelerated stress tests, temperature cycling, humidity testing, and bias-temperature-humidity stress tests. Testing protocols often follow industry standards for moisture sensitivity levels (MSL) classification, with HBM4 typically requiring more stringent testing due to its complex 3D stacked structure. Advanced analytical techniques are used to detect potential failure modes related to moisture ingress, including interface delamination, corrosion, and electrical parameter shifts.

- Thermal management solutions for HBM4 reliability: Thermal management is crucial for HBM4 reliability as it directly impacts moisture-related failure mechanisms. Advanced thermal solutions include integrated heat spreaders, thermal interface materials with low moisture absorption properties, and cooling systems designed specifically for high-density memory stacks. Proper thermal management prevents condensation cycles that could introduce moisture into the package. Additionally, thermal design considerations help maintain stable operating temperatures across the memory stack, reducing thermal expansion stresses that could compromise moisture barriers or create paths for moisture ingress.

- Interface materials and bonding techniques for moisture resistance: Specialized interface materials and bonding techniques are employed in HBM4 to enhance moisture resistance. These include advanced underfill materials with low moisture absorption rates, moisture-resistant adhesives for die stacking, and specialized interposer materials that prevent moisture migration between layers. Bonding techniques such as hybrid bonding and enhanced microbump technologies create more robust connections that resist moisture-induced degradation. The selection of these materials and techniques is critical for maintaining the integrity of the complex 3D structure of HBM4 memory in varying environmental conditions.

- Storage and handling protocols for HBM4: Specific storage and handling protocols are essential for maintaining HBM4 reliability. These include controlled environment requirements for manufacturing, transportation, and storage facilities with specified humidity levels and temperature ranges. Vacuum-sealed moisture barrier bags with humidity indicator cards are commonly used for shipping and storage. Strict floor-life management practices must be followed once packages are removed from protective packaging. Automated handling systems are designed to minimize human contact and exposure to ambient conditions. These protocols are critical for preventing moisture absorption before the HBM4 components are assembled into final products.

02 Reliability testing methods for HBM4

Specialized reliability testing methods have been developed for HBM4 to evaluate its performance under various environmental conditions. These include temperature cycling tests, humidity tests, and accelerated life testing to simulate long-term use. High-temperature operating life (HTOL) tests and temperature-humidity-bias (THB) tests are commonly employed to assess the moisture sensitivity and reliability of HBM4 components. These testing protocols help identify potential failure mechanisms and ensure that HBM4 meets industry reliability standards before deployment in critical applications.Expand Specific Solutions03 Thermal management solutions for HBM4 reliability

Effective thermal management is crucial for HBM4 reliability, as excessive heat can exacerbate moisture-related issues. Advanced cooling solutions, including integrated heat spreaders, thermal interface materials, and liquid cooling systems, are employed to maintain optimal operating temperatures. These thermal management approaches help prevent moisture condensation within the memory stack and reduce thermal stress that could lead to delamination or other moisture-related failures. By controlling the thermal environment, the overall reliability and moisture resistance of HBM4 components can be significantly improved.Expand Specific Solutions04 Moisture sensitivity level (MSL) classification for HBM4

HBM4 components are classified according to standardized moisture sensitivity levels (MSL) that indicate their susceptibility to moisture-induced damage during reflow soldering. The MSL classification determines the specific handling, storage, and processing requirements for HBM4 to prevent moisture absorption. Advanced packaging technologies and materials are employed to achieve lower MSL ratings, which allow for longer floor life and less stringent handling requirements. Proper MSL classification and adherence to the corresponding handling procedures are essential for preventing moisture-related failures in HBM4 components.Expand Specific Solutions05 Interface design for improved HBM4 reliability

The design of interfaces between HBM4 memory stacks and substrates plays a critical role in moisture resistance and overall reliability. Advanced interface materials and connection technologies, such as through-silicon vias (TSVs) and microbumps, are engineered to minimize moisture penetration pathways. Specialized underfill materials are used to seal the interfaces and provide mechanical support while preventing moisture ingress. These interface design considerations help maintain signal integrity under varying environmental conditions and contribute significantly to the long-term reliability of HBM4 memory systems in high-performance computing applications.Expand Specific Solutions

Key Players in High-Bandwidth Memory Ecosystem

The HBM4 moisture sensitivity and reliability landscape in high-density packaging is currently in a transitional growth phase, with the market expanding rapidly as advanced computing applications drive demand. The technology is approaching maturity but still faces significant challenges in moisture management and reliability assurance. Academic institutions like Zhejiang University and Wuhan University of Technology are conducting fundamental research, while industrial players demonstrate varying levels of technological readiness. Companies such as W.L. Gore & Associates and Resonac Corp. lead with advanced moisture barrier solutions, while semiconductor packaging specialists like FUJIFILM Corp. and Taiyo Holdings focus on reliability enhancements. Material science innovators including ExxonMobil Chemical Patents and Evonik Operations are developing specialized polymers to address moisture-related failures in these increasingly dense and complex packaging environments.

Dow Global Technologies LLC

Technical Solution: Dow Global Technologies has developed a revolutionary moisture protection system specifically for HBM4 applications called HydroshieldX. This technology utilizes a multi-component approach featuring their advanced silicone-based polymers with engineered porosity at the molecular level. The system creates an effective moisture barrier while maintaining the thermal conductivity necessary for high-performance computing applications. Dow's solution incorporates proprietary coupling agents that form chemical bonds at material interfaces, eliminating potential moisture pathways that typically occur at these junctions. Their materials demonstrate exceptional stability at temperatures exceeding 300°C, making them suitable for lead-free reflow processes. Testing has shown moisture absorption rates below 0.05% after 1000 hours of HAST (Highly Accelerated Stress Test) conditions, representing a 70% improvement over previous generation materials. The company has also developed specialized application techniques that ensure uniform coverage of complex 3D structures typical in HBM4 packages, addressing one of the key challenges in high-density packaging reliability.

Strengths: Exceptional moisture resistance combined with high thermal conductivity; excellent adhesion properties reducing interfacial delamination; proven long-term reliability under accelerated testing conditions. Weaknesses: Requires specialized application equipment; higher initial material costs; potential for increased processing time during manufacturing.

Resonac Corp.

Technical Solution: Resonac Corporation (formerly Showa Denko) has developed advanced moisture barrier films specifically designed for HBM4 high-density packaging applications. Their technology employs a multi-layer composite structure with alternating inorganic and organic layers that significantly reduces water vapor transmission rates to below 10^-3 g/m²/day. The company's proprietary plasma-enhanced chemical vapor deposition (PECVD) process creates ultra-thin silicon nitride and silicon oxide barrier layers with exceptional uniformity, while their specialized polymer interlayers provide flexibility and stress relief. This combination effectively prevents moisture ingress into sensitive HBM4 components during reflow soldering processes, where temperatures can exceed 260°C. Resonac has also implemented nano-scale surface treatments that enhance adhesion between different material interfaces, reducing delamination risks that could create moisture pathways.

Strengths: Superior moisture barrier properties with industry-leading water vapor transmission rates; excellent thermal stability during reflow processes; compatibility with existing manufacturing equipment. Weaknesses: Higher production costs compared to conventional materials; requires specialized deposition equipment; potential for increased package thickness affecting overall form factor.

Critical Patents in HBM4 Reliability Enhancement

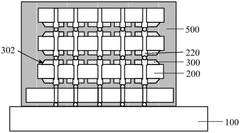

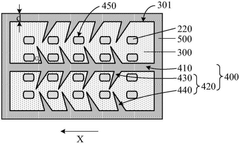

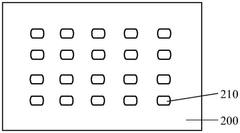

Packaging structure and packaging method

PatentPendingCN120076343A

Innovation

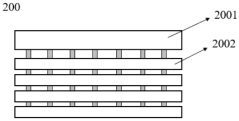

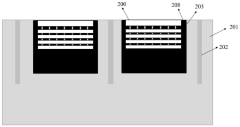

- A packaging structure and method are adopted, wherein a protective layer is formed on the upper and lower surfaces of a plurality of chips stacked longitudinally on the substrate, the flow guide groove is located in the protective layer, the main flow guide groove penetrates the protective layer in the direction of the mold flow, and the support flow guide groove is arranged on the side of the main flow guide groove along the direction of the mold flow, and extends in the direction of the mold flow, forming a larger filling window for plastic sealing material to fill.

Packaging structure of high-bandwidth memory and forming method thereof

PatentPendingCN117750785A

Innovation

- Using a chip stack structure in a silicon substrate, electrical connections are made through conductive through-silicon vias and interconnect structures, and the cavity is filled with plastic encapsulation material to reduce the risk of warpage, while releasing stress by thinning the silicon substrate and plastic encapsulation material. Improve the flatness and heat dissipation effect of the package.

Thermal Management Considerations for HBM4

Thermal management represents a critical challenge in the implementation of HBM4 technology, particularly when considering moisture sensitivity and reliability concerns in high-density packaging environments. As HBM4 continues to push the boundaries of memory bandwidth and density, the thermal characteristics of these packages become increasingly complex and demanding.

The stacked die architecture of HBM4 creates significant thermal challenges due to the concentration of heat-generating components in a confined space. With multiple DRAM dies stacked vertically and connected through thousands of through-silicon vias (TSVs), heat dissipation pathways are limited and thermal gradients can become pronounced. These thermal gradients may exacerbate moisture-related reliability issues, as temperature fluctuations can accelerate moisture migration within the package.

Industry data indicates that HBM4 packages can generate thermal densities exceeding 1 W/mm², significantly higher than previous generations. This increased thermal load necessitates sophisticated cooling solutions that must balance thermal performance with form factor constraints and system-level integration requirements.

The interplay between thermal cycling and moisture sensitivity presents a particular challenge for HBM4 reliability. As packages undergo temperature fluctuations during normal operation, the resulting expansion and contraction can create pathways for moisture ingress. This moisture can subsequently lead to various failure mechanisms, including interfacial delamination, popcorn cracking, and corrosion of interconnects.

Advanced thermal management solutions for HBM4 must address both steady-state and transient thermal conditions. These include enhanced thermal interface materials (TIMs) with thermal conductivities exceeding 5 W/m·K, integrated vapor chambers, and microchannel liquid cooling systems. The selection of appropriate solutions depends on specific application requirements, including power profiles, ambient conditions, and reliability targets.

Computational fluid dynamics (CFD) modeling has become essential in predicting the thermal behavior of HBM4 packages. These simulations must account for the complex geometry of stacked dies, interposers, and substrate materials, as well as the anisotropic thermal conductivity of various package components. Accurate thermal modeling enables designers to identify potential hotspots and optimize cooling strategies accordingly.

Recent research indicates that dynamic thermal management techniques, including adaptive power throttling and workload distribution, can significantly improve the reliability of HBM4 systems. By maintaining more consistent temperature profiles, these approaches reduce the thermal cycling that contributes to moisture-related failure mechanisms.

The stacked die architecture of HBM4 creates significant thermal challenges due to the concentration of heat-generating components in a confined space. With multiple DRAM dies stacked vertically and connected through thousands of through-silicon vias (TSVs), heat dissipation pathways are limited and thermal gradients can become pronounced. These thermal gradients may exacerbate moisture-related reliability issues, as temperature fluctuations can accelerate moisture migration within the package.

Industry data indicates that HBM4 packages can generate thermal densities exceeding 1 W/mm², significantly higher than previous generations. This increased thermal load necessitates sophisticated cooling solutions that must balance thermal performance with form factor constraints and system-level integration requirements.

The interplay between thermal cycling and moisture sensitivity presents a particular challenge for HBM4 reliability. As packages undergo temperature fluctuations during normal operation, the resulting expansion and contraction can create pathways for moisture ingress. This moisture can subsequently lead to various failure mechanisms, including interfacial delamination, popcorn cracking, and corrosion of interconnects.

Advanced thermal management solutions for HBM4 must address both steady-state and transient thermal conditions. These include enhanced thermal interface materials (TIMs) with thermal conductivities exceeding 5 W/m·K, integrated vapor chambers, and microchannel liquid cooling systems. The selection of appropriate solutions depends on specific application requirements, including power profiles, ambient conditions, and reliability targets.

Computational fluid dynamics (CFD) modeling has become essential in predicting the thermal behavior of HBM4 packages. These simulations must account for the complex geometry of stacked dies, interposers, and substrate materials, as well as the anisotropic thermal conductivity of various package components. Accurate thermal modeling enables designers to identify potential hotspots and optimize cooling strategies accordingly.

Recent research indicates that dynamic thermal management techniques, including adaptive power throttling and workload distribution, can significantly improve the reliability of HBM4 systems. By maintaining more consistent temperature profiles, these approaches reduce the thermal cycling that contributes to moisture-related failure mechanisms.

Industry Standards and Testing Protocols for HBM4

The industry standards for HBM4 moisture sensitivity and reliability testing are primarily governed by JEDEC, IPC, and other international standardization bodies. JEDEC's J-STD-020 serves as the cornerstone standard for moisture sensitivity classification of non-hermetic solid-state surface mount devices, providing critical guidelines for HBM4 packaging. This standard defines eight moisture sensitivity levels (MSL), with HBM4 typically requiring MSL 3 or higher due to its complex structure and fine pitch interconnects.

Testing protocols for HBM4 reliability include Temperature Cycling Test (TCT) according to JEDEC JESD22-A104, which evaluates the package's ability to withstand thermal stress through repeated temperature cycling between -40°C and 125°C. The High Temperature Storage Life (HTSL) test, following JEDEC JESD22-A103, assesses long-term reliability under elevated temperature conditions, typically at 150°C for 1000 hours.

Moisture sensitivity testing for HBM4 follows the JEDEC J-STD-033 protocol, which outlines procedures for handling, packing, shipping, and use of moisture/reflow sensitive surface mount devices. The test sequence involves preconditioning (baking), moisture absorption under controlled humidity conditions, and multiple reflow cycles to simulate manufacturing processes.

The IPC/JEDEC J-STD-020E standard specifically addresses the classification of non-hermetic solid-state surface mount devices, providing detailed procedures for moisture sensitivity characterization. For HBM4, with its silicon interposer and microbumps, specialized testing parameters are often required, including extended preconditioning times and modified reflow profiles.

Highly Accelerated Stress Test (HAST) and Pressure Cooker Test (PCT), following JEDEC JESD22-A110 and JESD22-A102 respectively, are employed to evaluate package resistance to moisture penetration under extreme conditions. These tests are particularly critical for HBM4 due to its increased susceptibility to moisture-induced failures at interface layers.

The Electromigration test (JEDEC JESD61A) evaluates the reliability of interconnects under electrical stress, while the Thermal Shock test (JEDEC JESD22-A106) assesses the package's resistance to sudden temperature changes. For HBM4's unique structure, modified test conditions are often implemented to address the specific failure mechanisms associated with high-density packaging.

Recent updates to these standards have begun to incorporate specific provisions for advanced packaging technologies like HBM4, acknowledging the unique challenges posed by 3D stacking, silicon interposers, and microbump interconnections. Industry consortia such as SEMI and the Heterogeneous Integration Roadmap (HIR) team are actively working to develop specialized testing protocols that better address the reliability concerns specific to high-bandwidth memory interfaces.

Testing protocols for HBM4 reliability include Temperature Cycling Test (TCT) according to JEDEC JESD22-A104, which evaluates the package's ability to withstand thermal stress through repeated temperature cycling between -40°C and 125°C. The High Temperature Storage Life (HTSL) test, following JEDEC JESD22-A103, assesses long-term reliability under elevated temperature conditions, typically at 150°C for 1000 hours.

Moisture sensitivity testing for HBM4 follows the JEDEC J-STD-033 protocol, which outlines procedures for handling, packing, shipping, and use of moisture/reflow sensitive surface mount devices. The test sequence involves preconditioning (baking), moisture absorption under controlled humidity conditions, and multiple reflow cycles to simulate manufacturing processes.

The IPC/JEDEC J-STD-020E standard specifically addresses the classification of non-hermetic solid-state surface mount devices, providing detailed procedures for moisture sensitivity characterization. For HBM4, with its silicon interposer and microbumps, specialized testing parameters are often required, including extended preconditioning times and modified reflow profiles.

Highly Accelerated Stress Test (HAST) and Pressure Cooker Test (PCT), following JEDEC JESD22-A110 and JESD22-A102 respectively, are employed to evaluate package resistance to moisture penetration under extreme conditions. These tests are particularly critical for HBM4 due to its increased susceptibility to moisture-induced failures at interface layers.

The Electromigration test (JEDEC JESD61A) evaluates the reliability of interconnects under electrical stress, while the Thermal Shock test (JEDEC JESD22-A106) assesses the package's resistance to sudden temperature changes. For HBM4's unique structure, modified test conditions are often implemented to address the specific failure mechanisms associated with high-density packaging.

Recent updates to these standards have begun to incorporate specific provisions for advanced packaging technologies like HBM4, acknowledging the unique challenges posed by 3D stacking, silicon interposers, and microbump interconnections. Industry consortia such as SEMI and the Heterogeneous Integration Roadmap (HIR) team are actively working to develop specialized testing protocols that better address the reliability concerns specific to high-bandwidth memory interfaces.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!