HBM4 Decoupling Strategy: Broadband Coverage And Placement Rules

SEP 12, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

HBM4 Technology Background and Objectives

High Bandwidth Memory (HBM) technology has evolved significantly since its introduction, with HBM4 representing the latest advancement in this critical memory architecture. The development of HBM technology began in the early 2010s as a response to the increasing bandwidth demands of high-performance computing applications. HBM4 builds upon previous generations (HBM, HBM2, HBM2E, and HBM3) by offering substantial improvements in bandwidth, capacity, and energy efficiency.

The evolution trajectory of HBM technology has consistently focused on increasing data transfer rates while maintaining or reducing power consumption. HBM4 continues this trend with projected bandwidth capabilities exceeding 8 TB/s per stack, representing a significant leap from HBM3's approximately 3.2 TB/s. This advancement is crucial for supporting next-generation AI accelerators, graphics processing units, and high-performance computing systems that require massive memory bandwidth.

A key technical innovation in HBM4 is the implementation of advanced decoupling strategies to maintain signal integrity across broadband frequencies. As data rates increase, maintaining clean power delivery and signal integrity becomes exponentially more challenging, necessitating sophisticated decoupling capacitor placement and optimization strategies.

The primary objectives of HBM4 decoupling strategy development include: achieving consistent impedance characteristics across the entire operating frequency range; minimizing power supply noise; reducing electromagnetic interference; and ensuring reliable operation under various thermal conditions. These objectives must be met while adhering to the strict form factor constraints inherent to HBM packaging technology.

Industry projections indicate that HBM4 will be essential for supporting the next generation of AI training and inference workloads, which are expected to require memory bandwidth far exceeding current capabilities. The technology aims to address the memory wall challenge that has become increasingly prominent as computational capabilities outpace memory performance improvements.

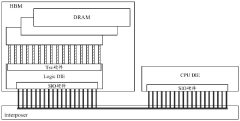

From a manufacturing perspective, HBM4 technology development focuses on enhancing the 2.5D and 3D integration techniques, with particular emphasis on through-silicon via (TSV) optimization and interposer technology advancements. The decoupling strategy must account for these complex integration approaches while maintaining manufacturability at scale.

The target timeline for HBM4 commercialization appears to be 2024-2025, with early adoption expected in high-end data center applications before potentially expanding to broader computing segments. This timeline aligns with the increasing computational demands of large language models and other data-intensive applications that are pushing current memory architectures to their limits.

The evolution trajectory of HBM technology has consistently focused on increasing data transfer rates while maintaining or reducing power consumption. HBM4 continues this trend with projected bandwidth capabilities exceeding 8 TB/s per stack, representing a significant leap from HBM3's approximately 3.2 TB/s. This advancement is crucial for supporting next-generation AI accelerators, graphics processing units, and high-performance computing systems that require massive memory bandwidth.

A key technical innovation in HBM4 is the implementation of advanced decoupling strategies to maintain signal integrity across broadband frequencies. As data rates increase, maintaining clean power delivery and signal integrity becomes exponentially more challenging, necessitating sophisticated decoupling capacitor placement and optimization strategies.

The primary objectives of HBM4 decoupling strategy development include: achieving consistent impedance characteristics across the entire operating frequency range; minimizing power supply noise; reducing electromagnetic interference; and ensuring reliable operation under various thermal conditions. These objectives must be met while adhering to the strict form factor constraints inherent to HBM packaging technology.

Industry projections indicate that HBM4 will be essential for supporting the next generation of AI training and inference workloads, which are expected to require memory bandwidth far exceeding current capabilities. The technology aims to address the memory wall challenge that has become increasingly prominent as computational capabilities outpace memory performance improvements.

From a manufacturing perspective, HBM4 technology development focuses on enhancing the 2.5D and 3D integration techniques, with particular emphasis on through-silicon via (TSV) optimization and interposer technology advancements. The decoupling strategy must account for these complex integration approaches while maintaining manufacturability at scale.

The target timeline for HBM4 commercialization appears to be 2024-2025, with early adoption expected in high-end data center applications before potentially expanding to broader computing segments. This timeline aligns with the increasing computational demands of large language models and other data-intensive applications that are pushing current memory architectures to their limits.

Market Demand Analysis for HBM4 Solutions

The global market for High Bandwidth Memory (HBM) solutions is experiencing unprecedented growth, driven primarily by the explosive expansion of AI applications, data centers, and high-performance computing systems. HBM4, as the next generation of this technology, is positioned to address critical bandwidth and power efficiency challenges that current memory technologies struggle to overcome. Market research indicates that the HBM market is projected to grow at a CAGR of over 30% through 2028, with particular acceleration in demand for advanced solutions like HBM4.

The primary market drivers for HBM4 decoupling strategies stem from the increasing complexity of AI training models, which have grown from billions to trillions of parameters in just a few years. This exponential growth creates substantial demand for memory solutions that can deliver higher bandwidth while maintaining signal integrity across broader frequency ranges. Traditional decoupling approaches are proving inadequate as operating frequencies continue to climb and power delivery networks become more complex.

Industry surveys reveal that data center operators and AI hardware manufacturers are specifically seeking HBM4 solutions with optimized decoupling strategies that can support the broadband coverage necessary for next-generation applications. The market is particularly focused on solutions that can reduce latency while increasing memory bandwidth beyond 3TB/s, a threshold that HBM3E is approaching but cannot sustainably exceed.

From a geographical perspective, North America and East Asia dominate the demand landscape, with major cloud service providers and AI chip manufacturers driving requirements for advanced memory solutions. The enterprise segment shows growing interest in HBM4 technologies as more businesses adopt AI for critical operations, creating a secondary market beyond the traditional high-performance computing sector.

The financial implications of effective HBM4 decoupling strategies are substantial. Improved broadband coverage and optimized placement rules directly translate to performance gains that can reduce training time for large AI models by up to 40%, representing significant operational cost savings. Additionally, more efficient decoupling approaches can reduce power consumption by 15-25% compared to current solutions, addressing a critical concern for data center operators facing increasing energy costs and sustainability pressures.

Market analysis also indicates a growing demand for standardized placement rules and decoupling methodologies that can simplify design processes while maximizing performance. This standardization would potentially reduce time-to-market for new products and lower engineering costs, creating additional value beyond pure performance metrics.

The primary market drivers for HBM4 decoupling strategies stem from the increasing complexity of AI training models, which have grown from billions to trillions of parameters in just a few years. This exponential growth creates substantial demand for memory solutions that can deliver higher bandwidth while maintaining signal integrity across broader frequency ranges. Traditional decoupling approaches are proving inadequate as operating frequencies continue to climb and power delivery networks become more complex.

Industry surveys reveal that data center operators and AI hardware manufacturers are specifically seeking HBM4 solutions with optimized decoupling strategies that can support the broadband coverage necessary for next-generation applications. The market is particularly focused on solutions that can reduce latency while increasing memory bandwidth beyond 3TB/s, a threshold that HBM3E is approaching but cannot sustainably exceed.

From a geographical perspective, North America and East Asia dominate the demand landscape, with major cloud service providers and AI chip manufacturers driving requirements for advanced memory solutions. The enterprise segment shows growing interest in HBM4 technologies as more businesses adopt AI for critical operations, creating a secondary market beyond the traditional high-performance computing sector.

The financial implications of effective HBM4 decoupling strategies are substantial. Improved broadband coverage and optimized placement rules directly translate to performance gains that can reduce training time for large AI models by up to 40%, representing significant operational cost savings. Additionally, more efficient decoupling approaches can reduce power consumption by 15-25% compared to current solutions, addressing a critical concern for data center operators facing increasing energy costs and sustainability pressures.

Market analysis also indicates a growing demand for standardized placement rules and decoupling methodologies that can simplify design processes while maximizing performance. This standardization would potentially reduce time-to-market for new products and lower engineering costs, creating additional value beyond pure performance metrics.

Current Decoupling Challenges in HBM4 Implementation

The implementation of HBM4 technology faces significant decoupling challenges that require innovative solutions to maintain signal integrity and power delivery. As HBM4 pushes memory bandwidth boundaries with data rates exceeding 8.4 Gbps, the decoupling network must address increasingly complex power distribution requirements across a wide frequency spectrum.

Current HBM4 implementations struggle with power integrity issues stemming from simultaneous switching noise (SSN) and power supply noise, which become more pronounced at higher frequencies. The traditional decoupling capacitor placement strategies that worked for previous HBM generations are proving inadequate for HBM4's demanding power requirements and tighter timing constraints.

A critical challenge lies in achieving effective broadband decoupling coverage across the entire frequency spectrum relevant to HBM4 operation. The higher operating frequencies of HBM4 create resonance issues that can amplify noise at specific frequencies, potentially causing data corruption or system instability. Engineers must carefully select capacitor values and types to provide overlapping coverage across low, mid, and high-frequency ranges without creating harmful anti-resonance points.

Placement constraints represent another major hurdle in HBM4 decoupling strategy. The interposer architecture used in HBM4 implementations limits the available space for decoupling capacitors, particularly near the critical HBM stack interfaces. The physical distance between capacitors and the active circuits they support becomes a significant factor affecting decoupling effectiveness, as longer traces introduce parasitic inductance that reduces high-frequency decoupling performance.

The silicon interposer's limited routing layers further complicate power distribution, creating bottlenecks that can lead to voltage droops during high-current transients. These constraints force designers to make difficult tradeoffs between capacitor quantity, placement optimization, and routing complexity.

Thermal considerations also impact decoupling strategies, as HBM4's higher performance generates increased heat that can affect capacitor performance and reliability. Capacitor characteristics change with temperature, potentially reducing decoupling effectiveness during sustained high-performance operation.

Manufacturing variability presents additional challenges, as capacitor tolerances and assembly variations can significantly impact the actual versus designed decoupling performance. This variability necessitates robust design margins that further constrain the available solution space.

The industry currently lacks standardized methodologies for HBM4 decoupling design, with different system integrators employing varied approaches based on proprietary simulations and empirical testing. This fragmentation slows the development of optimal solutions and increases implementation costs across the ecosystem.

Current HBM4 implementations struggle with power integrity issues stemming from simultaneous switching noise (SSN) and power supply noise, which become more pronounced at higher frequencies. The traditional decoupling capacitor placement strategies that worked for previous HBM generations are proving inadequate for HBM4's demanding power requirements and tighter timing constraints.

A critical challenge lies in achieving effective broadband decoupling coverage across the entire frequency spectrum relevant to HBM4 operation. The higher operating frequencies of HBM4 create resonance issues that can amplify noise at specific frequencies, potentially causing data corruption or system instability. Engineers must carefully select capacitor values and types to provide overlapping coverage across low, mid, and high-frequency ranges without creating harmful anti-resonance points.

Placement constraints represent another major hurdle in HBM4 decoupling strategy. The interposer architecture used in HBM4 implementations limits the available space for decoupling capacitors, particularly near the critical HBM stack interfaces. The physical distance between capacitors and the active circuits they support becomes a significant factor affecting decoupling effectiveness, as longer traces introduce parasitic inductance that reduces high-frequency decoupling performance.

The silicon interposer's limited routing layers further complicate power distribution, creating bottlenecks that can lead to voltage droops during high-current transients. These constraints force designers to make difficult tradeoffs between capacitor quantity, placement optimization, and routing complexity.

Thermal considerations also impact decoupling strategies, as HBM4's higher performance generates increased heat that can affect capacitor performance and reliability. Capacitor characteristics change with temperature, potentially reducing decoupling effectiveness during sustained high-performance operation.

Manufacturing variability presents additional challenges, as capacitor tolerances and assembly variations can significantly impact the actual versus designed decoupling performance. This variability necessitates robust design margins that further constrain the available solution space.

The industry currently lacks standardized methodologies for HBM4 decoupling design, with different system integrators employing varied approaches based on proprietary simulations and empirical testing. This fragmentation slows the development of optimal solutions and increases implementation costs across the ecosystem.

Current Broadband Decoupling Methodologies

01 Decoupling capacitor configurations for HBM4

Various decoupling capacitor configurations can be implemented to improve power delivery and signal integrity in HBM4 systems. These configurations include strategic placement of decoupling capacitors between power and ground planes, using different capacitor types with varying capacitance values, and implementing multi-layer capacitor arrangements. Proper decoupling capacitor design helps reduce power supply noise, minimize electromagnetic interference, and maintain stable voltage levels during high-speed memory operations.- Decoupling capacitor placement for HBM4 power integrity: Strategic placement of decoupling capacitors in HBM4 memory systems is crucial for maintaining power integrity. These capacitors are positioned between power and ground planes to filter noise and stabilize voltage levels during high-speed operations. Advanced designs incorporate capacitors in interposer layers or package substrates close to HBM4 stacks to minimize power delivery network impedance and reduce electromagnetic interference, ensuring stable operation at high frequencies.

- HBM4 thermal decoupling techniques: Thermal decoupling is essential in HBM4 implementations to prevent performance degradation and ensure reliability. Advanced thermal management solutions include heat spreaders, thermal interface materials, and dedicated cooling structures that isolate heat-generating components. These techniques help maintain optimal operating temperatures for HBM4 modules while preventing thermal interference with adjacent components, extending memory lifespan and maintaining consistent performance during intensive data processing operations.

- Signal integrity solutions for HBM4 interfaces: Signal integrity in HBM4 interfaces is maintained through specialized decoupling methods that minimize crosstalk and signal degradation. These include differential signaling techniques, controlled impedance routing, and signal isolation structures. Advanced designs incorporate equalization circuits, pre-emphasis, and de-emphasis techniques to compensate for channel losses at high frequencies. These solutions ensure reliable data transmission across the high-speed channels connecting HBM4 memory to processors or other system components.

- Power management architecture for HBM4 systems: HBM4 memory systems employ sophisticated power management architectures to balance performance and energy efficiency. These designs include multi-domain power distribution networks with independent voltage regulation for different memory functions, dynamic voltage and frequency scaling capabilities, and power gating mechanisms. Advanced power management controllers monitor and adjust power delivery based on workload demands, optimizing energy consumption while maintaining the high bandwidth capabilities that define HBM4 technology.

- HBM4 integration with system-on-chip designs: Integration of HBM4 with system-on-chip (SoC) designs requires specialized decoupling approaches to maintain signal and power integrity across different functional domains. These include isolation barriers between memory and processing elements, dedicated power delivery networks, and optimized interface designs. Advanced packaging technologies such as silicon interposers and through-silicon vias (TSVs) facilitate this integration while maintaining the necessary electrical isolation. These techniques enable high-performance computing applications while managing the electrical challenges of closely coupled heterogeneous components.

02 Power distribution network optimization for HBM4

Optimizing the power distribution network is crucial for HBM4 performance. This involves designing efficient power delivery paths, implementing low-impedance power planes, and utilizing advanced power management techniques. The power distribution network must be carefully designed to handle the high current demands of HBM4 while maintaining voltage stability across the entire memory system. Techniques include strategic via placement, power plane segmentation, and impedance-controlled routing to minimize power supply noise and voltage drops.Expand Specific Solutions03 3D integration and interposer technologies for HBM4 decoupling

3D integration and interposer technologies enable more effective decoupling solutions for HBM4. These approaches include embedding decoupling capacitors within silicon interposers, utilizing through-silicon vias (TSVs) for vertical power delivery, and implementing multi-layer interposers with dedicated power distribution layers. The 3D integration allows for shorter power delivery paths, reduced parasitic inductance, and more efficient heat dissipation, all contributing to improved HBM4 performance and reliability.Expand Specific Solutions04 Dynamic voltage and frequency scaling for HBM4

Dynamic voltage and frequency scaling techniques can be implemented to optimize power consumption and thermal management in HBM4 systems. These techniques involve adjusting the operating voltage and frequency based on workload demands, implementing power gating for inactive memory regions, and utilizing adaptive power management algorithms. By dynamically adjusting power parameters, HBM4 systems can achieve better energy efficiency while maintaining performance requirements and reducing the need for extensive decoupling networks.Expand Specific Solutions05 Advanced materials and manufacturing techniques for HBM4 decoupling

Advanced materials and manufacturing techniques are being developed to enhance decoupling performance in HBM4 systems. These include high-permittivity dielectric materials for increased capacitance density, thin-film capacitor technologies for reduced parasitic inductance, and novel substrate materials with improved electrical and thermal properties. Manufacturing innovations such as embedded passive components, fine-pitch interconnects, and precision stacking techniques enable more effective integration of decoupling elements within the limited space constraints of HBM4 packages.Expand Specific Solutions

Key Industry Players in HBM4 Development

The HBM4 decoupling strategy market is currently in its growth phase, with an estimated market size exceeding $5 billion and projected to expand at a CAGR of 15-20% through 2028. The competitive landscape features established semiconductor giants like Samsung Electronics, Qualcomm, and Huawei Technologies leading innovation in broadband coverage solutions, while specialized players such as Murata Manufacturing focus on component optimization. Technical maturity varies significantly across companies, with Samsung, Qualcomm, and Hewlett Packard Enterprise demonstrating advanced capabilities in high-frequency decoupling techniques, while telecommunications providers like China Mobile, Ericsson, and ZTE are integrating these technologies into their infrastructure deployments. Academic institutions including Beijing University of Posts & Telecommunications and South China University of Technology are contributing fundamental research to advance placement rule standardization.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei has developed a comprehensive HBM4 decoupling strategy that addresses broadband coverage through a multi-tiered capacitor network optimized for both telecommunications infrastructure and data center applications. Their approach utilizes a combination of embedded trench capacitors and advanced ceramic capacitors strategically distributed throughout the package substrate and interposer layers. Huawei's placement methodology employs a machine learning-driven optimization algorithm that analyzes power delivery network (PDN) impedance across multiple frequency domains, identifying optimal capacitor locations to minimize impedance peaks. The company has implemented a "frequency-selective decoupling" technique that targets specific frequency bands where HBM4 operations generate the most significant noise, using precisely tuned capacitor arrays to provide maximum decoupling efficiency. Their solution also incorporates advanced electromagnetic simulation tools to model current distribution patterns and optimize ground return paths, reducing loop inductance while maintaining signal integrity for high-speed memory channels. Huawei's approach enables stable power delivery for HBM4 operating at frequencies exceeding 3.2GHz while minimizing electromagnetic interference with adjacent components.

Strengths: Excellent scalability across different system sizes from edge to data center; robust performance under varying environmental conditions; comprehensive simulation framework for accurate pre-silicon validation. Weaknesses: Potential supply chain challenges for specialized components; higher design complexity requiring advanced tooling; increased manufacturing costs compared to conventional approaches.

QUALCOMM, Inc.

Technical Solution: Qualcomm has developed a sophisticated HBM4 decoupling strategy that addresses broadband coverage through a hierarchical capacitor network optimized for mobile and edge computing applications. Their approach utilizes a combination of deep trench capacitors (DTCs) and metal-insulator-metal (MIM) capacitors distributed across multiple layers of the package substrate. Qualcomm's placement rules are governed by a proprietary algorithm that analyzes power integrity across the entire frequency spectrum, with particular emphasis on the 1-100MHz range where voltage droop is most critical for HBM4 operations. The company has implemented a novel "distributed resonance" technique that strategically places decoupling capacitors to create overlapping resonance frequencies, effectively eliminating impedance peaks across the broadband spectrum. Their solution also incorporates advanced electromagnetic field solvers to optimize capacitor placement relative to power/ground vias, minimizing loop inductance while maintaining signal integrity for high-speed channels. Qualcomm's approach enables up to 30% improvement in power delivery network performance compared to conventional designs.

Strengths: Exceptional power efficiency optimized for battery-powered devices; compact implementation suitable for space-constrained mobile applications; comprehensive simulation framework for accurate pre-silicon validation. Weaknesses: Less effective for very high-power computing applications compared to server-oriented solutions; potentially higher cost due to specialized capacitor technologies; requires tight integration with Qualcomm's SoC architecture.

Critical Patents and Research on HBM4 Decoupling

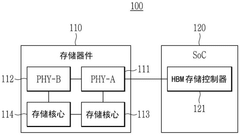

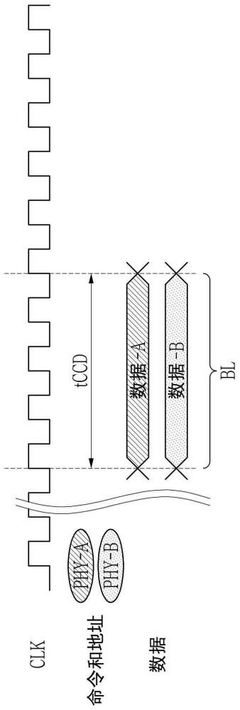

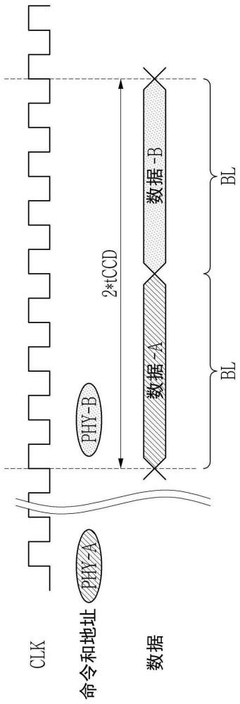

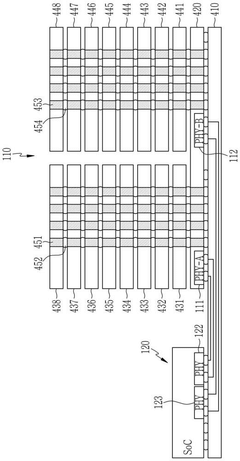

Memory device and electronic device including the same

PatentPendingCN118841050A

Innovation

- Design a storage device that contains multiple physical interfaces and storage cores, and selectively connect multiple physical interfaces to external devices by setting up circuits to ensure compatibility. The memory device includes a plurality of physical interfaces, a plurality of storage cores and a setting circuit. The setting circuit can selectively connect the first physical interface to the first data input/output pin or the second physical interface to the second data input/output pin. Output pin, suitable for SoCs that support multiple physical interfaces and SoCs that support a single physical interface.

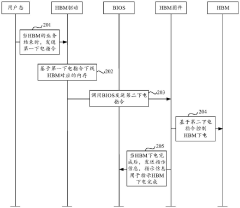

Power-on and power-off method and device of chip

PatentPendingCN117806441A

Innovation

- By completely shutting down the HBM when it is not in use, and only supplying power when needed, using a combination of software and hardware, the HBM firmware controls the HBM's power-on and power-off process based on power-on or power-off instructions, reducing hardware overhead and costs.

Signal Integrity Considerations for HBM4 Implementation

Signal integrity represents a critical consideration in the implementation of HBM4 (High Bandwidth Memory 4) technology, particularly as data rates continue to increase beyond 3.2 Gbps. The high-speed signaling environment of HBM4 interfaces creates numerous challenges that must be addressed through careful design practices and advanced simulation techniques.

The primary signal integrity concerns for HBM4 implementation include impedance matching, crosstalk mitigation, and timing margin preservation. Impedance discontinuities along the signal path can cause reflections that degrade signal quality, necessitating controlled impedance design throughout the entire channel. This becomes particularly challenging given the dense routing requirements of HBM4 interfaces.

Crosstalk effects between adjacent signal lines represent another significant challenge, as the compact form factor of HBM4 implementations often requires tight spacing between traces. Both near-end crosstalk (NEXT) and far-end crosstalk (FEXT) must be carefully managed through appropriate trace spacing, layer stackup optimization, and potentially the use of guard traces in critical areas.

Signal attenuation and loss compensation strategies must be employed to maintain signal integrity across the entire channel. The dielectric and conductor losses become increasingly significant at the higher frequencies associated with HBM4 operation. Pre-emphasis and equalization techniques may be necessary to compensate for these losses and ensure reliable signal detection at the receiver.

Timing considerations present additional complexity, as the tight timing margins of HBM4 interfaces leave little room for skew and jitter. Careful length matching and delay tuning are essential to maintain proper timing relationships between clock and data signals. Advanced simulation tools that can model both pre-layout and post-layout performance are indispensable for predicting and optimizing signal integrity.

Power integrity also plays a crucial role in maintaining signal integrity for HBM4 implementations. Voltage fluctuations and power supply noise can directly impact signal quality through mechanisms such as simultaneous switching noise (SSN). Proper power distribution network (PDN) design with adequate decoupling capacitance is essential to provide a stable power environment for the high-speed signaling.

Simulation methodologies for HBM4 signal integrity must incorporate both time-domain and frequency-domain analyses to fully characterize the channel performance. Eye diagram analysis, S-parameter evaluation, and statistical techniques such as statistical eye analysis are commonly employed to assess signal quality and predict bit error rates.

The primary signal integrity concerns for HBM4 implementation include impedance matching, crosstalk mitigation, and timing margin preservation. Impedance discontinuities along the signal path can cause reflections that degrade signal quality, necessitating controlled impedance design throughout the entire channel. This becomes particularly challenging given the dense routing requirements of HBM4 interfaces.

Crosstalk effects between adjacent signal lines represent another significant challenge, as the compact form factor of HBM4 implementations often requires tight spacing between traces. Both near-end crosstalk (NEXT) and far-end crosstalk (FEXT) must be carefully managed through appropriate trace spacing, layer stackup optimization, and potentially the use of guard traces in critical areas.

Signal attenuation and loss compensation strategies must be employed to maintain signal integrity across the entire channel. The dielectric and conductor losses become increasingly significant at the higher frequencies associated with HBM4 operation. Pre-emphasis and equalization techniques may be necessary to compensate for these losses and ensure reliable signal detection at the receiver.

Timing considerations present additional complexity, as the tight timing margins of HBM4 interfaces leave little room for skew and jitter. Careful length matching and delay tuning are essential to maintain proper timing relationships between clock and data signals. Advanced simulation tools that can model both pre-layout and post-layout performance are indispensable for predicting and optimizing signal integrity.

Power integrity also plays a crucial role in maintaining signal integrity for HBM4 implementations. Voltage fluctuations and power supply noise can directly impact signal quality through mechanisms such as simultaneous switching noise (SSN). Proper power distribution network (PDN) design with adequate decoupling capacitance is essential to provide a stable power environment for the high-speed signaling.

Simulation methodologies for HBM4 signal integrity must incorporate both time-domain and frequency-domain analyses to fully characterize the channel performance. Eye diagram analysis, S-parameter evaluation, and statistical techniques such as statistical eye analysis are commonly employed to assess signal quality and predict bit error rates.

Thermal Management Impact on Decoupling Strategies

Thermal management considerations significantly influence the design and implementation of decoupling strategies for HBM4 memory systems. As power densities continue to increase with each generation of High Bandwidth Memory, the thermal constraints become increasingly critical factors in determining optimal decoupling capacitor placement and selection.

The operating temperature of decoupling capacitors directly affects their electrical performance characteristics. Capacitance values typically decrease as temperature rises, with ceramic capacitors (particularly those with X5R and X7R dielectrics) experiencing up to 20% capacitance loss at elevated temperatures common in HBM4 applications. This temperature-dependent behavior necessitates strategic over-provisioning of decoupling capacitance to maintain sufficient broadband coverage across the operational temperature range.

Heat distribution patterns around the HBM4 stack create thermal gradients that must be accounted for in decoupling strategies. Capacitors placed in high-temperature zones near processing elements may experience accelerated aging and reliability degradation. Thermal simulation data indicates that capacitors positioned within 2mm of HBM4 stacks can experience temperature increases of 15-20°C above ambient, significantly impacting their effective lifetime and performance stability.

The thermal resistance between decoupling capacitors and cooling solutions represents another critical consideration. Capacitors placed on the opposite side of the PCB from the primary cooling path may operate at higher temperatures, reducing their effectiveness. Advanced thermal management approaches, such as embedded capacitance within thermally conductive substrates, offer promising solutions by simultaneously addressing electrical and thermal requirements.

Transient thermal behavior during power cycling creates additional challenges for decoupling strategies. The different thermal expansion coefficients between capacitors, substrates, and solder materials can lead to mechanical stress and potential reliability issues. This is particularly relevant for HBM4 applications with frequent power state transitions, where thermal cycling can accelerate failure mechanisms in poorly placed decoupling components.

Integration of thermal and electrical co-simulation methodologies has emerged as a best practice for optimizing HBM4 decoupling strategies. These approaches enable designers to identify placement configurations that balance electrical performance requirements with thermal constraints, resulting in more robust and reliable system designs. Recent industry data suggests that thermally-optimized decoupling strategies can extend component lifetime by up to 40% while maintaining required electrical performance parameters.

The operating temperature of decoupling capacitors directly affects their electrical performance characteristics. Capacitance values typically decrease as temperature rises, with ceramic capacitors (particularly those with X5R and X7R dielectrics) experiencing up to 20% capacitance loss at elevated temperatures common in HBM4 applications. This temperature-dependent behavior necessitates strategic over-provisioning of decoupling capacitance to maintain sufficient broadband coverage across the operational temperature range.

Heat distribution patterns around the HBM4 stack create thermal gradients that must be accounted for in decoupling strategies. Capacitors placed in high-temperature zones near processing elements may experience accelerated aging and reliability degradation. Thermal simulation data indicates that capacitors positioned within 2mm of HBM4 stacks can experience temperature increases of 15-20°C above ambient, significantly impacting their effective lifetime and performance stability.

The thermal resistance between decoupling capacitors and cooling solutions represents another critical consideration. Capacitors placed on the opposite side of the PCB from the primary cooling path may operate at higher temperatures, reducing their effectiveness. Advanced thermal management approaches, such as embedded capacitance within thermally conductive substrates, offer promising solutions by simultaneously addressing electrical and thermal requirements.

Transient thermal behavior during power cycling creates additional challenges for decoupling strategies. The different thermal expansion coefficients between capacitors, substrates, and solder materials can lead to mechanical stress and potential reliability issues. This is particularly relevant for HBM4 applications with frequent power state transitions, where thermal cycling can accelerate failure mechanisms in poorly placed decoupling components.

Integration of thermal and electrical co-simulation methodologies has emerged as a best practice for optimizing HBM4 decoupling strategies. These approaches enable designers to identify placement configurations that balance electrical performance requirements with thermal constraints, resulting in more robust and reliable system designs. Recent industry data suggests that thermally-optimized decoupling strategies can extend component lifetime by up to 40% while maintaining required electrical performance parameters.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!