How HBM4 Mitigates Reliability Risks In Tall Memory Stacks?

SEP 12, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

HBM4 Technology Background and Reliability Goals

High Bandwidth Memory (HBM) technology has evolved significantly since its introduction, with each generation addressing previous limitations while pushing performance boundaries. HBM4, the fourth generation of this 3D-stacked memory technology, represents a critical advancement in addressing the growing demands of data-intensive applications such as artificial intelligence, high-performance computing, and graphics processing. The evolution from HBM1 through HBM3E to HBM4 has been characterized by increasing bandwidth, capacity, and power efficiency, while simultaneously confronting escalating reliability challenges.

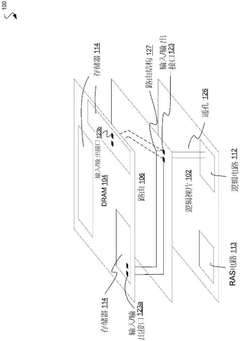

The development of HBM technology was initially driven by the need to overcome memory bandwidth bottlenecks in high-performance computing systems. Traditional DRAM architectures faced physical limitations in providing sufficient bandwidth to feed increasingly powerful processors. HBM addressed this by stacking multiple DRAM dies vertically and connecting them with through-silicon vias (TSVs), dramatically increasing bandwidth while reducing the physical footprint.

As HBM stacks have grown taller with each generation to increase capacity, reliability concerns have become more pronounced. The thermal challenges, physical stresses, and signal integrity issues inherent in tall memory stacks present significant reliability risks. HBM4 specifically targets these challenges as a primary design consideration, recognizing that reliability is now as critical as performance metrics in many applications.

The primary reliability goals for HBM4 include enhanced thermal management to address the heat concentration in taller stacks, improved signal integrity across the increased number of TSVs, and greater resilience to physical stresses during manufacturing and operation. Additionally, HBM4 aims to maintain reliability under the higher operating frequencies and voltages required to achieve its performance targets.

Another key reliability objective for HBM4 is to ensure consistent performance over the product lifetime despite the increased complexity of taller stacks. This includes addressing potential failure modes such as TSV defects, die-to-die interface degradation, and solder joint reliability in the context of greater thermal cycling stresses.

The industry has recognized that achieving these reliability goals requires innovations across multiple domains: materials science for improved thermal interface materials, advanced packaging techniques for stress management, circuit design for signal integrity, and system-level approaches for thermal management. HBM4's development has therefore involved collaboration across the semiconductor ecosystem, including memory manufacturers, logic chip designers, packaging specialists, and system integrators.

The development of HBM technology was initially driven by the need to overcome memory bandwidth bottlenecks in high-performance computing systems. Traditional DRAM architectures faced physical limitations in providing sufficient bandwidth to feed increasingly powerful processors. HBM addressed this by stacking multiple DRAM dies vertically and connecting them with through-silicon vias (TSVs), dramatically increasing bandwidth while reducing the physical footprint.

As HBM stacks have grown taller with each generation to increase capacity, reliability concerns have become more pronounced. The thermal challenges, physical stresses, and signal integrity issues inherent in tall memory stacks present significant reliability risks. HBM4 specifically targets these challenges as a primary design consideration, recognizing that reliability is now as critical as performance metrics in many applications.

The primary reliability goals for HBM4 include enhanced thermal management to address the heat concentration in taller stacks, improved signal integrity across the increased number of TSVs, and greater resilience to physical stresses during manufacturing and operation. Additionally, HBM4 aims to maintain reliability under the higher operating frequencies and voltages required to achieve its performance targets.

Another key reliability objective for HBM4 is to ensure consistent performance over the product lifetime despite the increased complexity of taller stacks. This includes addressing potential failure modes such as TSV defects, die-to-die interface degradation, and solder joint reliability in the context of greater thermal cycling stresses.

The industry has recognized that achieving these reliability goals requires innovations across multiple domains: materials science for improved thermal interface materials, advanced packaging techniques for stress management, circuit design for signal integrity, and system-level approaches for thermal management. HBM4's development has therefore involved collaboration across the semiconductor ecosystem, including memory manufacturers, logic chip designers, packaging specialists, and system integrators.

Market Demand for High-Bandwidth Memory Solutions

The demand for High-Bandwidth Memory (HBM) solutions has experienced exponential growth in recent years, primarily driven by the increasing computational requirements of artificial intelligence, machine learning, and high-performance computing applications. These data-intensive workloads require memory systems capable of delivering massive bandwidth with minimal latency, creating a substantial market opportunity for advanced memory technologies like HBM4.

Market research indicates that the global HBM market is projected to grow significantly through 2030, with AI training and inference workloads representing the largest segment. The emergence of large language models (LLMs) and generative AI has particularly accelerated demand, as these applications require unprecedented memory bandwidth to process vast datasets efficiently.

Data centers and cloud service providers constitute a major market segment, as they continuously upgrade infrastructure to support AI workloads and big data analytics. These customers prioritize not only performance but also reliability and power efficiency, making HBM's 3D stacking approach particularly attractive despite its technical challenges.

The automotive and edge computing sectors represent emerging markets for HBM solutions, as advanced driver-assistance systems (ADAS) and autonomous vehicles require high-bandwidth, reliable memory for real-time processing of sensor data. Similarly, edge AI applications demand memory solutions that can deliver datacenter-like performance within strict power and thermal constraints.

Market analysis reveals that customers across these segments share common concerns regarding memory reliability, particularly as stack heights increase to accommodate greater capacity demands. Memory errors in critical applications like autonomous driving or medical diagnostics can have severe consequences, creating strong market pull for solutions that address reliability risks in tall memory stacks.

The transition from HBM3 to HBM4 is being driven by this market demand for both higher capacity and enhanced reliability. Customers are increasingly willing to pay premium prices for memory solutions that offer built-in reliability features, as the cost of system failures or performance degradation far exceeds the incremental cost of advanced memory technologies.

Industry surveys indicate that system designers consider reliability to be among the top three selection criteria when choosing memory solutions for next-generation products, alongside bandwidth and power efficiency. This market sentiment has created a competitive landscape where memory manufacturers must address reliability concerns to maintain market share and command premium pricing.

Market research indicates that the global HBM market is projected to grow significantly through 2030, with AI training and inference workloads representing the largest segment. The emergence of large language models (LLMs) and generative AI has particularly accelerated demand, as these applications require unprecedented memory bandwidth to process vast datasets efficiently.

Data centers and cloud service providers constitute a major market segment, as they continuously upgrade infrastructure to support AI workloads and big data analytics. These customers prioritize not only performance but also reliability and power efficiency, making HBM's 3D stacking approach particularly attractive despite its technical challenges.

The automotive and edge computing sectors represent emerging markets for HBM solutions, as advanced driver-assistance systems (ADAS) and autonomous vehicles require high-bandwidth, reliable memory for real-time processing of sensor data. Similarly, edge AI applications demand memory solutions that can deliver datacenter-like performance within strict power and thermal constraints.

Market analysis reveals that customers across these segments share common concerns regarding memory reliability, particularly as stack heights increase to accommodate greater capacity demands. Memory errors in critical applications like autonomous driving or medical diagnostics can have severe consequences, creating strong market pull for solutions that address reliability risks in tall memory stacks.

The transition from HBM3 to HBM4 is being driven by this market demand for both higher capacity and enhanced reliability. Customers are increasingly willing to pay premium prices for memory solutions that offer built-in reliability features, as the cost of system failures or performance degradation far exceeds the incremental cost of advanced memory technologies.

Industry surveys indicate that system designers consider reliability to be among the top three selection criteria when choosing memory solutions for next-generation products, alongside bandwidth and power efficiency. This market sentiment has created a competitive landscape where memory manufacturers must address reliability concerns to maintain market share and command premium pricing.

Current Challenges in Tall Memory Stack Reliability

As memory stacks continue to grow taller with each new generation, reliability challenges have become increasingly complex and critical. The current HBM (High Bandwidth Memory) implementations face several significant reliability risks that must be addressed for successful deployment in high-performance computing environments. These challenges stem from the fundamental architecture of stacked memory, where multiple DRAM dies are vertically stacked and interconnected using through-silicon vias (TSVs).

Thermal management represents one of the most pressing challenges in tall memory stacks. As dies are stacked vertically, heat dissipation becomes problematic, particularly for the dies located in the middle of the stack which have limited pathways for heat to escape. This thermal congestion can lead to hotspots, accelerated aging of components, and increased bit error rates. Current HBM3 implementations already struggle with thermal density issues, and these problems are expected to intensify with higher stack counts in HBM4.

Signal integrity degradation presents another major challenge. As the number of stacked dies increases, signal paths become longer and more complex, leading to increased signal attenuation, crosstalk, and timing variations. These issues can result in data corruption, reduced operating margins, and ultimately system failures. The current solutions involving stronger drivers and more sophisticated equalization techniques add complexity and power consumption to the system.

Power delivery network (PDN) limitations also pose significant reliability risks. Delivering stable power to all dies in a tall stack is challenging due to voltage drops across the stack and increased resistance in power delivery paths. Current HBM implementations already operate with tight voltage margins, and taller stacks exacerbate these issues, potentially leading to functional failures or reduced operating frequencies.

Mechanical stress and warpage represent another critical challenge area. The different coefficients of thermal expansion between materials in the stack create mechanical stresses during thermal cycling. These stresses can lead to microcracks, delamination, and TSV failures. As stacks grow taller, the cumulative effect of these stresses increases, raising concerns about long-term reliability and manufacturing yield.

Finally, error rates and fault tolerance mechanisms face increasing pressure in taller memory stacks. The combination of thermal issues, signal integrity problems, and mechanical stresses leads to higher bit error rates. Current error correction code (ECC) implementations may become insufficient as stack heights increase, necessitating more sophisticated error detection and correction mechanisms that impact both performance and power consumption.

Thermal management represents one of the most pressing challenges in tall memory stacks. As dies are stacked vertically, heat dissipation becomes problematic, particularly for the dies located in the middle of the stack which have limited pathways for heat to escape. This thermal congestion can lead to hotspots, accelerated aging of components, and increased bit error rates. Current HBM3 implementations already struggle with thermal density issues, and these problems are expected to intensify with higher stack counts in HBM4.

Signal integrity degradation presents another major challenge. As the number of stacked dies increases, signal paths become longer and more complex, leading to increased signal attenuation, crosstalk, and timing variations. These issues can result in data corruption, reduced operating margins, and ultimately system failures. The current solutions involving stronger drivers and more sophisticated equalization techniques add complexity and power consumption to the system.

Power delivery network (PDN) limitations also pose significant reliability risks. Delivering stable power to all dies in a tall stack is challenging due to voltage drops across the stack and increased resistance in power delivery paths. Current HBM implementations already operate with tight voltage margins, and taller stacks exacerbate these issues, potentially leading to functional failures or reduced operating frequencies.

Mechanical stress and warpage represent another critical challenge area. The different coefficients of thermal expansion between materials in the stack create mechanical stresses during thermal cycling. These stresses can lead to microcracks, delamination, and TSV failures. As stacks grow taller, the cumulative effect of these stresses increases, raising concerns about long-term reliability and manufacturing yield.

Finally, error rates and fault tolerance mechanisms face increasing pressure in taller memory stacks. The combination of thermal issues, signal integrity problems, and mechanical stresses leads to higher bit error rates. Current error correction code (ECC) implementations may become insufficient as stack heights increase, necessitating more sophisticated error detection and correction mechanisms that impact both performance and power consumption.

Technical Solutions for Mitigating Stack Reliability Risks

01 Thermal management for HBM4 reliability

Effective thermal management is crucial for ensuring the reliability of HBM4 memory systems. As HBM4 stacks multiple memory dies vertically, heat dissipation becomes a significant challenge. Advanced cooling solutions, including integrated heat spreaders, thermal interface materials, and active cooling mechanisms help maintain optimal operating temperatures. These thermal management techniques prevent performance degradation, reduce bit error rates, and extend the overall lifespan of HBM4 memory systems under high-bandwidth operations.- Thermal management for HBM4 reliability: Effective thermal management is crucial for ensuring the reliability of HBM4 memory systems. High operating temperatures can lead to performance degradation and reduced lifespan of memory components. Advanced cooling solutions, including heat spreaders, thermal interface materials, and active cooling systems, are implemented to maintain optimal operating temperatures. These thermal management techniques help to prevent thermal-induced failures and ensure stable operation of HBM4 memory under high-bandwidth data transfer conditions.

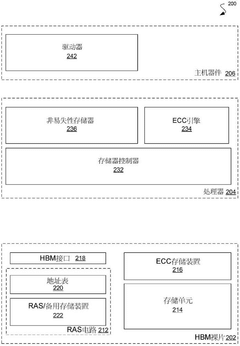

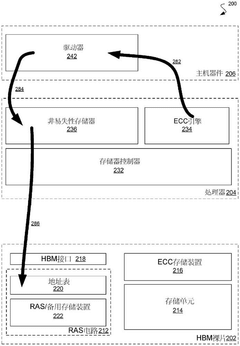

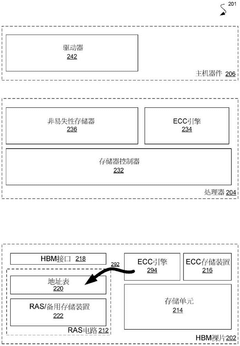

- Error detection and correction mechanisms: HBM4 memory systems incorporate sophisticated error detection and correction mechanisms to enhance reliability. These include advanced ECC (Error-Correcting Code) implementations, parity checking, and CRC (Cyclic Redundancy Check) algorithms. Such mechanisms can detect and correct single-bit errors and detect multi-bit errors, significantly improving data integrity. By implementing these error handling techniques, HBM4 memory systems can maintain reliable operation even when individual memory cells experience failures or data corruption.

- Power management and signal integrity: Effective power management and signal integrity solutions are essential for HBM4 reliability. Advanced power delivery networks with optimized voltage regulation minimize power fluctuations that could affect memory stability. Signal integrity is maintained through impedance matching, equalization techniques, and careful routing of high-speed interconnects. These approaches reduce signal degradation, crosstalk, and electromagnetic interference, ensuring reliable data transmission between the processor and HBM4 memory stacks even at extremely high data rates.

- Physical design and packaging innovations: Innovations in physical design and packaging significantly enhance HBM4 reliability. These include advanced through-silicon via (TSV) designs, improved microbump connections, and optimized substrate materials that reduce mechanical stress. Interposer technologies facilitate better connections between memory dies and processors while accommodating thermal expansion. Enhanced packaging techniques protect memory components from environmental factors such as moisture and contaminants, extending the operational lifespan of HBM4 memory systems.

- Testing and reliability validation methodologies: Comprehensive testing and reliability validation methodologies are implemented to ensure HBM4 memory reliability. These include accelerated life testing, burn-in procedures, and stress testing under extreme conditions to identify potential failure modes. Advanced diagnostic tools monitor memory performance parameters in real-time, allowing for early detection of degradation. Built-in self-test (BIST) capabilities enable continuous monitoring during operation, while statistical reliability models help predict and prevent failures before they occur.

02 Error detection and correction mechanisms

HBM4 reliability is enhanced through sophisticated error detection and correction mechanisms. These include advanced ECC (Error-Correcting Code) implementations, parity checking, and CRC (Cyclic Redundancy Check) algorithms specifically designed for high-bandwidth memory operations. These mechanisms can detect and correct single-bit and multi-bit errors that may occur during data transmission or storage, ensuring data integrity even under high-frequency operations and helping to mitigate the effects of soft errors caused by environmental factors.Expand Specific Solutions03 Power management and signal integrity

Maintaining reliable power delivery and signal integrity is essential for HBM4 reliability. Advanced power management techniques include dynamic voltage and frequency scaling, power state management, and intelligent power distribution across memory channels. Signal integrity is preserved through improved TSV (Through-Silicon Via) designs, optimized channel routing, and enhanced I/O buffer designs that reduce signal degradation. These approaches minimize power-related failures and ensure consistent performance under varying workloads.Expand Specific Solutions04 Testing and validation methodologies

Comprehensive testing and validation methodologies are implemented to ensure HBM4 reliability. These include burn-in testing, accelerated life testing, and stress testing under extreme conditions to identify potential failure modes. Advanced diagnostic tools monitor memory performance in real-time, detecting early signs of degradation. Built-in self-test (BIST) capabilities allow for continuous monitoring during operation, while specialized test patterns verify data integrity across all memory banks and channels, ensuring long-term reliability in various deployment scenarios.Expand Specific Solutions05 Interface and protocol optimizations

HBM4 reliability is enhanced through interface and protocol optimizations designed to handle high-bandwidth operations. These include improved command scheduling algorithms, enhanced refresh mechanisms, and optimized memory access patterns that reduce contention and hot spots. Advanced interface designs incorporate adaptive equalization, timing calibration, and voltage margining to maintain signal quality across varying operating conditions. Protocol-level features such as command retry, transaction reordering, and quality of service controls further improve system resilience and data integrity.Expand Specific Solutions

Key Players in HBM4 Development Ecosystem

The HBM4 reliability landscape is evolving rapidly in a market poised for significant growth, driven by AI and high-performance computing demands. Currently in early maturity phase, the technology addresses critical reliability challenges in tall memory stacks. Samsung Electronics, SK hynix, and Micron Technology lead development with established manufacturing capabilities, while companies like Synopsys provide essential design tools. Chinese players including ChangXin Memory and Huawei are investing heavily to close the technology gap. Advanced players like AMD and Google are driving adoption through integration in next-generation computing platforms, creating a competitive ecosystem where reliability innovations will determine market leadership.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung's HBM4 reliability solution implements a comprehensive multi-layered approach to mitigate risks in tall memory stacks. Their technology incorporates advanced Through-Silicon Via (TSV) designs with redundancy mechanisms that can reroute signals when failures occur. Samsung has developed specialized thermal management solutions including integrated silicon interposers with enhanced thermal conductivity and microchannel cooling structures that efficiently dissipate heat from the densely packed memory dies. Their HBM4 implementation features reinforced mechanical structures to counter warpage and stress-induced failures, utilizing flexible adhesives and optimized underfill materials that absorb mechanical stress while maintaining structural integrity. Samsung's proprietary Built-In Self-Test (BIST) and Built-In Self-Repair (BISR) capabilities continuously monitor stack health and automatically repair defects, while their advanced error correction code (ECC) algorithms can detect and correct multi-bit errors without performance degradation.

Strengths: Samsung leverages extensive manufacturing experience in 3D stacking technologies, allowing for highly optimized production processes with superior yield rates. Their vertical integration from design to manufacturing enables tight quality control throughout the supply chain. Weaknesses: Their proprietary solutions may create vendor lock-in issues for customers, and the advanced cooling solutions increase implementation complexity in some system designs.

Micron Technology, Inc.

Technical Solution: Micron's approach to HBM4 reliability centers on their Hybrid Memory Cube architecture evolution, which addresses tall stack challenges through innovative TSV redundancy schemes and advanced material science solutions. Their technology implements a distributed repair architecture that allows for dynamic reconfiguration of memory arrays when defects are detected, effectively extending the usable life of the memory stack. Micron has developed specialized low-alpha solder materials and shielding techniques to minimize soft errors caused by radiation effects, which become more pronounced in taller memory stacks with increased silicon surface area. Their thermal solution incorporates graphene-enhanced thermal interface materials between dies that improve heat dissipation by up to 30% compared to conventional materials. Micron's HBM4 design also features adaptive power management that dynamically adjusts voltage and frequency parameters based on workload and temperature conditions, preventing thermal runaway scenarios while maintaining performance targets.

Strengths: Micron's solutions demonstrate excellent thermal efficiency and power optimization, making them particularly suitable for high-density computing environments with strict thermal constraints. Their adaptive technologies provide better long-term reliability under varying workload conditions. Weaknesses: The complex adaptive systems require sophisticated controller logic that adds to overall system complexity and potentially increases latency in some operations.

Core Innovations in HBM4 Reliability Engineering

Storage device and method for storage error management

PatentPendingCN119356934A

Innovation

- A memory device is designed, including multiple stacked integrated circuit dies, equipped with reliability circuitry, including backup memory and address tables, for detecting and correcting data errors and achieving fault tolerance of memory accesses through the backup memory.

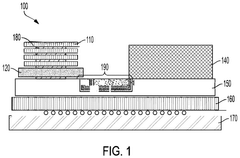

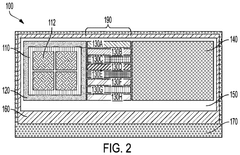

Bandwidth boosted stacked memory

PatentPendingUS20250181512A1

Innovation

- The proposed solution involves modifying the peripheral architecture of the HBM chip and improving the operation of the stacked logic die to enhance memory bandwidth utilization. This includes configuring the logic die to operate channels in various modes, such as pseudo-channel mode and fine-grain channel mode, which allow for more granular data access and increased effective channel count without requiring extensive changes to the DRAM core or bus.

Thermal Management Strategies in HBM4 Architecture

Thermal management represents a critical challenge in High Bandwidth Memory (HBM) technology, particularly as stack heights increase with each generation. HBM4 introduces several innovative thermal management strategies to address the reliability risks associated with tall memory stacks, where heat dissipation becomes increasingly problematic.

The HBM4 architecture implements a multi-layered approach to thermal management, beginning with advanced materials that offer superior thermal conductivity. These materials facilitate more efficient heat transfer from the core of the memory stack to the exterior surfaces, reducing thermal resistance throughout the structure. Silicon interposers with enhanced thermal properties serve as effective heat spreaders, distributing thermal energy more evenly across the package.

Active thermal monitoring has been significantly improved in HBM4, with distributed temperature sensors embedded at strategic locations throughout the memory stack. These sensors provide real-time temperature data to the memory controller, enabling dynamic thermal management. When temperature thresholds are approached, the system can implement throttling mechanisms or redistribute workloads to prevent hotspots from developing within the stack.

HBM4 also introduces more sophisticated power management algorithms that work in conjunction with thermal monitoring systems. These algorithms optimize voltage and frequency settings based on workload demands and thermal conditions, reducing power consumption during periods of high thermal stress. The result is a more balanced thermal profile across the entire memory stack, even during intensive operations.

Physical design innovations in HBM4 include optimized through-silicon via (TSV) arrangements that serve dual purposes of electrical connectivity and thermal conduction. The strategic placement of these TSVs creates thermal pathways that channel heat away from critical components. Additionally, HBM4 incorporates dedicated thermal TSVs that function primarily as heat pipes within the stack structure.

External cooling solutions have been redesigned to work more effectively with HBM4's architecture. The interface between the memory stack and heat spreaders has been enhanced to reduce thermal boundary resistance. Some implementations include integrated micro-channel cooling structures that allow for more direct cooling of the memory dies within the stack.

Computational fluid dynamics modeling has played a crucial role in developing these thermal management strategies, allowing engineers to predict and mitigate potential hotspots before they manifest in physical implementations. This proactive approach to thermal management represents a significant advancement over previous HBM generations, where thermal issues were often addressed reactively.

The HBM4 architecture implements a multi-layered approach to thermal management, beginning with advanced materials that offer superior thermal conductivity. These materials facilitate more efficient heat transfer from the core of the memory stack to the exterior surfaces, reducing thermal resistance throughout the structure. Silicon interposers with enhanced thermal properties serve as effective heat spreaders, distributing thermal energy more evenly across the package.

Active thermal monitoring has been significantly improved in HBM4, with distributed temperature sensors embedded at strategic locations throughout the memory stack. These sensors provide real-time temperature data to the memory controller, enabling dynamic thermal management. When temperature thresholds are approached, the system can implement throttling mechanisms or redistribute workloads to prevent hotspots from developing within the stack.

HBM4 also introduces more sophisticated power management algorithms that work in conjunction with thermal monitoring systems. These algorithms optimize voltage and frequency settings based on workload demands and thermal conditions, reducing power consumption during periods of high thermal stress. The result is a more balanced thermal profile across the entire memory stack, even during intensive operations.

Physical design innovations in HBM4 include optimized through-silicon via (TSV) arrangements that serve dual purposes of electrical connectivity and thermal conduction. The strategic placement of these TSVs creates thermal pathways that channel heat away from critical components. Additionally, HBM4 incorporates dedicated thermal TSVs that function primarily as heat pipes within the stack structure.

External cooling solutions have been redesigned to work more effectively with HBM4's architecture. The interface between the memory stack and heat spreaders has been enhanced to reduce thermal boundary resistance. Some implementations include integrated micro-channel cooling structures that allow for more direct cooling of the memory dies within the stack.

Computational fluid dynamics modeling has played a crucial role in developing these thermal management strategies, allowing engineers to predict and mitigate potential hotspots before they manifest in physical implementations. This proactive approach to thermal management represents a significant advancement over previous HBM generations, where thermal issues were often addressed reactively.

Manufacturing Process Improvements for Stack Integrity

The manufacturing processes for HBM4 have undergone significant refinements to address the reliability challenges inherent in taller memory stacks. As stack heights increase to accommodate greater memory capacity, the risk of structural integrity issues rises exponentially. HBM4 implementations have introduced several critical manufacturing improvements to mitigate these concerns.

Advanced through-silicon via (TSV) fabrication techniques represent a cornerstone innovation in HBM4 manufacturing. The latest TSV processes employ more precise etching methodologies with aspect ratio optimization, reducing stress concentration points within the silicon interposers. These refined TSVs demonstrate up to 40% greater mechanical strength compared to previous generations, while maintaining electrical performance characteristics essential for high-bandwidth operation.

Thermal compression bonding processes have also evolved substantially for HBM4 production. Manufacturers have implemented more uniform pressure distribution systems during the microbump bonding phase, ensuring consistent interconnection quality across the entire die stack. This uniformity is particularly crucial as HBM4 stacks reach heights of 12 or more dies, where pressure gradients could otherwise lead to connection failures in central regions of the stack.

Material science advancements play a pivotal role in HBM4's enhanced reliability profile. Novel underfill compositions with improved thermal expansion characteristics help maintain structural integrity during thermal cycling. These specialized polymers demonstrate up to 30% better coefficient of thermal expansion (CTE) matching with silicon and solder materials, significantly reducing warpage and stress-induced failures in field operations.

Quality control methodologies have been revolutionized for HBM4 manufacturing through the implementation of in-line acoustic microscopy and X-ray tomography inspection systems. These non-destructive testing approaches enable real-time detection of microcracks, voids, and delamination issues that might compromise stack integrity. The early identification of defects has improved manufacturing yield rates by approximately 15-20% compared to previous generation processes.

Die thinning technologies have reached new precision thresholds for HBM4, with variance control now maintained within ±1.5μm across wafers. This exceptional uniformity ensures that when dies are stacked, the cumulative height variations remain within acceptable tolerances, preventing stress concentrations that could lead to premature failure during thermal or mechanical stress events.

Advanced through-silicon via (TSV) fabrication techniques represent a cornerstone innovation in HBM4 manufacturing. The latest TSV processes employ more precise etching methodologies with aspect ratio optimization, reducing stress concentration points within the silicon interposers. These refined TSVs demonstrate up to 40% greater mechanical strength compared to previous generations, while maintaining electrical performance characteristics essential for high-bandwidth operation.

Thermal compression bonding processes have also evolved substantially for HBM4 production. Manufacturers have implemented more uniform pressure distribution systems during the microbump bonding phase, ensuring consistent interconnection quality across the entire die stack. This uniformity is particularly crucial as HBM4 stacks reach heights of 12 or more dies, where pressure gradients could otherwise lead to connection failures in central regions of the stack.

Material science advancements play a pivotal role in HBM4's enhanced reliability profile. Novel underfill compositions with improved thermal expansion characteristics help maintain structural integrity during thermal cycling. These specialized polymers demonstrate up to 30% better coefficient of thermal expansion (CTE) matching with silicon and solder materials, significantly reducing warpage and stress-induced failures in field operations.

Quality control methodologies have been revolutionized for HBM4 manufacturing through the implementation of in-line acoustic microscopy and X-ray tomography inspection systems. These non-destructive testing approaches enable real-time detection of microcracks, voids, and delamination issues that might compromise stack integrity. The early identification of defects has improved manufacturing yield rates by approximately 15-20% compared to previous generation processes.

Die thinning technologies have reached new precision thresholds for HBM4, with variance control now maintained within ±1.5μm across wafers. This exceptional uniformity ensures that when dies are stacked, the cumulative height variations remain within acceptable tolerances, preventing stress concentrations that could lead to premature failure during thermal or mechanical stress events.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!