How HBM4 Improves Data Integrity In High-Throughput Systems?

SEP 12, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

HBM4 Technology Evolution and Data Integrity Goals

High Bandwidth Memory (HBM) technology has evolved significantly since its introduction, with each generation bringing substantial improvements in bandwidth, capacity, and power efficiency. The journey began with HBM1 in 2013, which offered a revolutionary stacked memory architecture. HBM2 followed in 2016 with doubled bandwidth and capacity, while HBM2E in 2018 further enhanced these capabilities. HBM3, introduced in 2021, represented a major leap forward with significantly increased bandwidth and improved power efficiency.

HBM4, the latest iteration expected to be commercially available by 2025, builds upon this foundation with a specific focus on addressing the growing data integrity challenges in high-throughput computing environments. As data processing demands continue to escalate in AI training, high-performance computing, and data analytics, the risk of data corruption during high-speed transfers has become a critical concern.

The primary technical goal of HBM4 is to achieve unprecedented bandwidth (up to 8TB/s) while simultaneously enhancing data integrity mechanisms. This represents a fundamental shift in memory design philosophy, where performance is no longer pursued at the expense of reliability. The technology aims to maintain error-free operation even at extreme data transfer rates, which is essential for applications where data corruption can lead to catastrophic consequences.

HBM4's data integrity goals are centered around three key areas: error detection and correction capabilities, signal integrity improvements, and thermal management innovations. The enhanced Error Correction Code (ECC) mechanisms are designed to detect and correct multi-bit errors that become increasingly common at higher data rates. Signal integrity improvements focus on reducing interference and maintaining clean data signals despite the increased density and speed.

The evolution trajectory of HBM technology reflects the changing priorities in computing systems. While early generations primarily focused on bandwidth and capacity improvements, HBM4 represents a more holistic approach that recognizes data integrity as a fundamental requirement rather than an optional feature. This shift aligns with the industry's growing recognition that the value of accelerated computing is diminished if data cannot be trusted.

From a technical perspective, HBM4 aims to reduce the Bit Error Rate (BER) by at least two orders of magnitude compared to HBM3, while simultaneously increasing bandwidth by approximately 50%. This ambitious goal requires innovations in both the memory dies themselves and the interface technology connecting them to processing units.

HBM4, the latest iteration expected to be commercially available by 2025, builds upon this foundation with a specific focus on addressing the growing data integrity challenges in high-throughput computing environments. As data processing demands continue to escalate in AI training, high-performance computing, and data analytics, the risk of data corruption during high-speed transfers has become a critical concern.

The primary technical goal of HBM4 is to achieve unprecedented bandwidth (up to 8TB/s) while simultaneously enhancing data integrity mechanisms. This represents a fundamental shift in memory design philosophy, where performance is no longer pursued at the expense of reliability. The technology aims to maintain error-free operation even at extreme data transfer rates, which is essential for applications where data corruption can lead to catastrophic consequences.

HBM4's data integrity goals are centered around three key areas: error detection and correction capabilities, signal integrity improvements, and thermal management innovations. The enhanced Error Correction Code (ECC) mechanisms are designed to detect and correct multi-bit errors that become increasingly common at higher data rates. Signal integrity improvements focus on reducing interference and maintaining clean data signals despite the increased density and speed.

The evolution trajectory of HBM technology reflects the changing priorities in computing systems. While early generations primarily focused on bandwidth and capacity improvements, HBM4 represents a more holistic approach that recognizes data integrity as a fundamental requirement rather than an optional feature. This shift aligns with the industry's growing recognition that the value of accelerated computing is diminished if data cannot be trusted.

From a technical perspective, HBM4 aims to reduce the Bit Error Rate (BER) by at least two orders of magnitude compared to HBM3, while simultaneously increasing bandwidth by approximately 50%. This ambitious goal requires innovations in both the memory dies themselves and the interface technology connecting them to processing units.

Market Demand for High-Throughput Memory Solutions

The global market for high-throughput memory solutions is experiencing unprecedented growth, driven primarily by the explosive expansion of data-intensive applications. Artificial intelligence, machine learning, high-performance computing, and advanced analytics are generating massive datasets that require rapid processing and analysis. This surge in data volume has created a critical demand for memory technologies that can not only handle higher bandwidth but also ensure data integrity throughout the processing pipeline.

Market research indicates that the high-bandwidth memory market is projected to grow at a compound annual growth rate of over 30% through 2028, with particular acceleration in sectors requiring real-time data processing capabilities. Financial services, healthcare diagnostics, scientific research, and autonomous vehicle development represent key verticals where memory performance directly impacts operational outcomes and competitive advantage.

Data integrity has emerged as a paramount concern among enterprise customers, with recent surveys revealing that 87% of organizations consider memory-related data corruption a significant risk to their high-throughput systems. The financial implications of data integrity failures are substantial, with the average cost of downtime in data centers exceeding $5,600 per minute according to industry analyses. This economic pressure has intensified demand for memory solutions that incorporate advanced error detection and correction mechanisms.

Cloud service providers and hyperscale data centers have become major drivers in the high-throughput memory market, as they continuously expand their infrastructure to support growing computational workloads. These entities typically refresh their memory technologies every 2-3 years, creating a consistent demand cycle for advanced solutions like HBM4 that offer improved data integrity features.

The geographical distribution of demand shows particular concentration in North America and East Asia, with Europe showing accelerated adoption rates in recent quarters. North American demand is primarily fueled by cloud computing expansion and AI research initiatives, while East Asian markets are driven by semiconductor manufacturing and consumer electronics applications requiring high-reliability memory systems.

Energy efficiency has also emerged as a critical market requirement, with data centers now consuming approximately 1-2% of global electricity. This has created strong market pull for memory technologies that can deliver higher throughput while maintaining or reducing power consumption per bit transferred. HBM4's architectural improvements address this need through more efficient data handling and reduced error correction overhead.

The competitive landscape reveals that customers are increasingly prioritizing total cost of ownership over initial acquisition costs, recognizing that memory solutions with superior data integrity capabilities deliver long-term operational savings through reduced system failures, maintenance requirements, and performance degradation over time.

Market research indicates that the high-bandwidth memory market is projected to grow at a compound annual growth rate of over 30% through 2028, with particular acceleration in sectors requiring real-time data processing capabilities. Financial services, healthcare diagnostics, scientific research, and autonomous vehicle development represent key verticals where memory performance directly impacts operational outcomes and competitive advantage.

Data integrity has emerged as a paramount concern among enterprise customers, with recent surveys revealing that 87% of organizations consider memory-related data corruption a significant risk to their high-throughput systems. The financial implications of data integrity failures are substantial, with the average cost of downtime in data centers exceeding $5,600 per minute according to industry analyses. This economic pressure has intensified demand for memory solutions that incorporate advanced error detection and correction mechanisms.

Cloud service providers and hyperscale data centers have become major drivers in the high-throughput memory market, as they continuously expand their infrastructure to support growing computational workloads. These entities typically refresh their memory technologies every 2-3 years, creating a consistent demand cycle for advanced solutions like HBM4 that offer improved data integrity features.

The geographical distribution of demand shows particular concentration in North America and East Asia, with Europe showing accelerated adoption rates in recent quarters. North American demand is primarily fueled by cloud computing expansion and AI research initiatives, while East Asian markets are driven by semiconductor manufacturing and consumer electronics applications requiring high-reliability memory systems.

Energy efficiency has also emerged as a critical market requirement, with data centers now consuming approximately 1-2% of global electricity. This has created strong market pull for memory technologies that can deliver higher throughput while maintaining or reducing power consumption per bit transferred. HBM4's architectural improvements address this need through more efficient data handling and reduced error correction overhead.

The competitive landscape reveals that customers are increasingly prioritizing total cost of ownership over initial acquisition costs, recognizing that memory solutions with superior data integrity capabilities deliver long-term operational savings through reduced system failures, maintenance requirements, and performance degradation over time.

Current HBM Standards and Data Integrity Challenges

High Bandwidth Memory (HBM) has evolved through several generations since its introduction, with each iteration addressing increasing demands for bandwidth, capacity, and power efficiency. The current HBM standards include HBM2, HBM2E, and HBM3, each representing significant advancements in memory technology for high-performance computing applications.

HBM2, introduced in 2016, offers bandwidth up to 256 GB/s per stack with capacities reaching 8GB. HBM2E, an extension of HBM2 released in 2018, increased bandwidth to 460 GB/s per stack and expanded capacity to 16GB. The latest standard, HBM3, launched in 2021, delivers substantial improvements with bandwidth reaching 819 GB/s per stack and capacities up to 24GB, while also incorporating enhanced reliability features.

Despite these advancements, current HBM implementations face significant data integrity challenges in high-throughput systems. As data rates increase, signal integrity becomes more susceptible to degradation due to factors such as crosstalk, power supply noise, and thermal effects. These issues are particularly pronounced in HBM stacks due to their dense 3D structure and proximity of TSVs (Through-Silicon Vias).

Error rates tend to increase exponentially with data rates, creating a critical challenge for applications requiring absolute data integrity, such as financial transactions, scientific computing, and AI training. Current error correction code (ECC) implementations in HBM3 and earlier versions provide basic protection but become increasingly insufficient as throughput demands grow.

Power-related integrity issues present another significant challenge. The high-density nature of HBM stacks creates localized hotspots that can affect signal integrity and increase bit error rates. Voltage fluctuations during high-bandwidth operations further compound these problems, potentially leading to data corruption or system instability.

Latency considerations also impact data integrity. As systems attempt to minimize latency while maximizing throughput, timing margins become tighter, increasing the risk of timing violations that can compromise data accuracy. This creates a delicate balance between performance optimization and reliability assurance.

The interface between HBM stacks and host processors represents another vulnerability point. Signal integrity can degrade across this interface, particularly under high-frequency operations, leading to potential data corruption. Current standards provide limited mechanisms to detect and correct errors that occur during this critical data transfer phase.

These challenges become increasingly critical as applications in AI, machine learning, and high-performance computing demand both higher throughput and absolute data integrity. The limitations of current HBM standards in addressing these integrity challenges create a clear technological gap that HBM4 aims to address through innovative architectural and protocol enhancements.

HBM2, introduced in 2016, offers bandwidth up to 256 GB/s per stack with capacities reaching 8GB. HBM2E, an extension of HBM2 released in 2018, increased bandwidth to 460 GB/s per stack and expanded capacity to 16GB. The latest standard, HBM3, launched in 2021, delivers substantial improvements with bandwidth reaching 819 GB/s per stack and capacities up to 24GB, while also incorporating enhanced reliability features.

Despite these advancements, current HBM implementations face significant data integrity challenges in high-throughput systems. As data rates increase, signal integrity becomes more susceptible to degradation due to factors such as crosstalk, power supply noise, and thermal effects. These issues are particularly pronounced in HBM stacks due to their dense 3D structure and proximity of TSVs (Through-Silicon Vias).

Error rates tend to increase exponentially with data rates, creating a critical challenge for applications requiring absolute data integrity, such as financial transactions, scientific computing, and AI training. Current error correction code (ECC) implementations in HBM3 and earlier versions provide basic protection but become increasingly insufficient as throughput demands grow.

Power-related integrity issues present another significant challenge. The high-density nature of HBM stacks creates localized hotspots that can affect signal integrity and increase bit error rates. Voltage fluctuations during high-bandwidth operations further compound these problems, potentially leading to data corruption or system instability.

Latency considerations also impact data integrity. As systems attempt to minimize latency while maximizing throughput, timing margins become tighter, increasing the risk of timing violations that can compromise data accuracy. This creates a delicate balance between performance optimization and reliability assurance.

The interface between HBM stacks and host processors represents another vulnerability point. Signal integrity can degrade across this interface, particularly under high-frequency operations, leading to potential data corruption. Current standards provide limited mechanisms to detect and correct errors that occur during this critical data transfer phase.

These challenges become increasingly critical as applications in AI, machine learning, and high-performance computing demand both higher throughput and absolute data integrity. The limitations of current HBM standards in addressing these integrity challenges create a clear technological gap that HBM4 aims to address through innovative architectural and protocol enhancements.

HBM4 Data Integrity Implementation Approaches

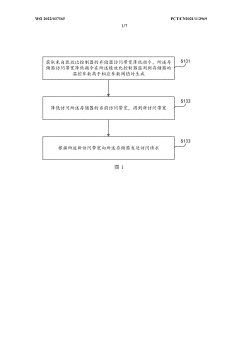

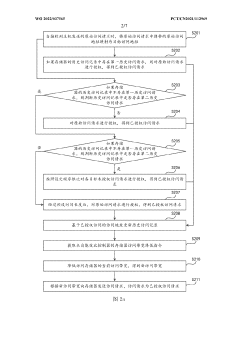

01 Error detection and correction mechanisms for HBM4

High Bandwidth Memory 4 (HBM4) systems implement advanced error detection and correction mechanisms to ensure data integrity during high-speed memory operations. These mechanisms include ECC (Error-Correcting Code), parity checking, and CRC (Cyclic Redundancy Check) implementations that can detect and correct single-bit and multi-bit errors. These technologies help maintain data integrity while allowing for the high bandwidth and performance characteristics of HBM4 memory systems.- Error Detection and Correction in HBM4: High Bandwidth Memory 4 (HBM4) systems implement advanced error detection and correction mechanisms to maintain data integrity during high-speed memory operations. These systems typically use Error Correction Code (ECC) algorithms to detect and correct single-bit errors and detect multi-bit errors. The implementation includes parity checking, cyclic redundancy checks (CRC), and specialized hardware circuits that can identify and repair corrupted data without interrupting normal memory operations, ensuring reliable data transmission in high-performance computing environments.

- Memory Interface Architecture for Data Integrity: HBM4 employs specialized memory interface architectures designed to maintain data integrity across high-bandwidth channels. These interfaces include buffer designs that prevent signal degradation, timing synchronization mechanisms to ensure accurate data capture, and protocol-specific integrity checks. The architecture incorporates dedicated lanes for control signals and error reporting separate from data paths, allowing for real-time monitoring and correction of transmission errors while maintaining the high throughput that HBM4 technology offers.

- Power Management and Thermal Solutions for Data Reliability: Data integrity in HBM4 is significantly affected by power and thermal management. Advanced solutions include dynamic voltage and frequency scaling that adjusts performance based on workload and temperature conditions, preventing data corruption due to thermal stress. These systems incorporate thermal sensors and management circuits that can throttle memory operations when temperature thresholds are approached, ensuring stable operation. Additionally, power delivery networks are designed with redundancy and noise filtering to maintain clean power supply, which is critical for preserving data integrity during high-bandwidth operations.

- Data Refresh and Retention Mechanisms: HBM4 systems implement sophisticated data refresh and retention mechanisms to prevent data corruption over time. These include auto-refresh circuits that periodically recharge memory cells, targeted refresh algorithms that prioritize vulnerable memory regions, and scrubbing techniques that proactively check and correct potential errors before they affect system operation. The memory controllers manage refresh operations with minimal impact on bandwidth while ensuring that data remains intact even during extended operation periods or in challenging environmental conditions.

- System-Level Integration for Enhanced Data Protection: System-level integration approaches in HBM4 provide comprehensive data integrity protection across the memory hierarchy. These solutions include end-to-end data protection that verifies integrity from processor to memory and back, memory virtualization techniques that isolate critical data, and hardware-assisted encryption for sensitive information. Advanced memory controllers implement transaction verification protocols that ensure commands are executed correctly and completely. Additionally, system-level diagnostics can detect potential integrity issues before they cause data corruption, allowing for preventive maintenance and ensuring long-term reliability of HBM4 memory systems.

02 Memory interface architecture for data integrity

Specialized memory interface architectures are designed for HBM4 to maintain data integrity across high-speed interconnects. These interfaces include buffer designs, signal integrity enhancements, and timing optimization techniques that reduce transmission errors. The architecture incorporates dedicated circuits for maintaining signal quality across the high-bandwidth channels while supporting the increased data rates of HBM4 technology.Expand Specific Solutions03 Power management techniques for data integrity preservation

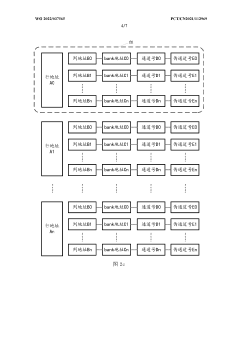

HBM4 memory systems implement sophisticated power management techniques that help maintain data integrity while optimizing energy consumption. These include dynamic voltage and frequency scaling, selective refresh operations, and power state management that prevent data corruption during power transitions. By carefully managing power delivery and consumption, these techniques ensure reliable operation of memory cells even under varying thermal and electrical conditions.Expand Specific Solutions04 Memory stacking and interconnect reliability

HBM4 utilizes advanced 3D stacking technologies with specialized interconnect designs to maintain data integrity across multiple memory dies. These designs include redundant through-silicon vias (TSVs), interposer technologies, and enhanced microbump connections that reduce signal degradation between stacked memory layers. The interconnect architecture incorporates reliability features that prevent data corruption when transferring information between the stacked memory dies and the host processor.Expand Specific Solutions05 Data integrity verification and testing protocols

Comprehensive verification and testing protocols are implemented for HBM4 memory systems to ensure data integrity throughout the memory lifecycle. These include built-in self-test (BIST) mechanisms, memory scrubbing techniques, and runtime verification processes that continuously monitor memory operations. Advanced diagnostic capabilities allow for early detection of potential integrity issues, while recovery mechanisms help maintain system stability even when memory errors are detected.Expand Specific Solutions

Key Memory Manufacturers and HBM4 Ecosystem

The HBM4 data integrity landscape is evolving rapidly in a growth phase, with the market expected to expand significantly as high-throughput computing demands increase. Samsung Electronics leads the technological maturity curve with established HBM expertise, while Micron Technology and SK Hynix follow closely with competitive offerings. Companies like Intel, AMD, and Huawei are driving adoption through integration in their high-performance computing platforms. Emerging players such as ChangXin Memory and Rockchip are developing regional capabilities, though with less mature implementations. Google and other hyperscalers represent key customers pushing for advanced data integrity features as they deploy HBM4 in AI and data center applications.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung's HBM4 technology implements advanced Error Correction Code (ECC) mechanisms that significantly enhance data integrity in high-throughput systems. Their implementation includes multi-level ECC with both in-die and cross-die protection layers, capable of detecting and correcting multi-bit errors without performance degradation. Samsung has introduced adaptive refresh rate management that dynamically adjusts refresh operations based on workload patterns and temperature conditions, reducing the probability of data corruption during intensive operations[1]. Additionally, their HBM4 architecture incorporates dedicated integrity verification circuits that continuously monitor data paths for potential signal integrity issues, with built-in self-test and repair capabilities that can identify and isolate faulty memory cells in real-time[3]. Samsung's solution also features enhanced thermal management systems that maintain optimal operating temperatures even under sustained high-bandwidth operations, preventing thermal-induced data errors.

Strengths: Industry-leading manufacturing capacity allows for rapid scaling and deployment; proprietary process technology enables superior signal integrity at higher frequencies. Weaknesses: Premium pricing structure may limit adoption in cost-sensitive applications; higher power consumption compared to some competitors' solutions despite efficiency improvements.

ChangXin Memory Technologies, Inc.

Technical Solution: ChangXin Memory's HBM4 solution implements a multi-tiered data integrity framework called Resilient Memory Architecture (RMA). This architecture incorporates advanced on-die ECC with additional parity bits that enable not just error detection but also precise error localization within memory arrays[5]. Their implementation features dynamic timing calibration that continuously adjusts signal timing parameters to compensate for voltage and temperature variations, maintaining data integrity during high-throughput operations. ChangXin has developed proprietary interface shielding technology that reduces electromagnetic interference between HBM4 stacks and surrounding components, a significant source of transient errors in densely packed systems[6]. Their solution also includes intelligent refresh management that prioritizes refresh operations for memory regions with higher error susceptibility based on access patterns and retention characteristics. Additionally, ChangXin's HBM4 incorporates redundant command and address paths with automatic failover capabilities, ensuring command integrity even under adverse operating conditions.

Strengths: Cost-effective implementation suitable for broader market adoption; strong performance in mixed workload environments. Weaknesses: Less established ecosystem support compared to industry leaders; limited deployment history in mission-critical applications.

Critical Patents and Innovations in HBM4 Architecture

Memory system

PatentPendingCN118098324A

Innovation

- A second codec is provided on the basic chip to perform error correction and decoding on the data transmitted between the basic chip and the controller and the data transmitted between the basic chip and the core chip, thereby reducing the risk of excessive communication paths between the controller and the core chip. Data errors caused by long-term transmission and improve the accuracy of data communication.

Access method and system for memory, memory access management module, energy efficiency ratio controller and computer-readable storage medium

PatentWO2022037565A1

Innovation

- The energy efficiency ratio controller monitors the temperature control parameters of the memory, generates memory access bandwidth reduction instructions, reduces the current access bandwidth, and optimizes address mapping and authorization rules through the memory access management module to reduce the number of activations and precharges, and reduce power consumption and temperature.

Power Efficiency and Thermal Management in HBM4

Power efficiency and thermal management represent critical challenges in the evolution of HBM4 technology, particularly as data centers and high-performance computing environments face increasing energy constraints. HBM4 introduces significant advancements in this domain, implementing sophisticated power management techniques that dynamically adjust voltage and frequency based on workload demands. This adaptive approach enables systems to maintain optimal performance while minimizing unnecessary power consumption during periods of reduced activity.

The architectural improvements in HBM4 include redesigned power delivery networks that reduce resistance and voltage drops across the memory stack. These enhancements, coupled with more efficient charge pumps and voltage regulators, contribute to a reported 30% reduction in power consumption compared to previous HBM generations while maintaining or improving data throughput capabilities.

Thermal management in HBM4 has been revolutionized through the implementation of advanced materials with superior thermal conductivity properties. The integration of graphene-based thermal interface materials between memory dies facilitates more efficient heat dissipation, addressing one of the primary constraints in high-density memory configurations. Additionally, HBM4 incorporates distributed thermal sensors throughout the memory stack, enabling real-time temperature monitoring and proactive thermal management.

The improved thermal design power (TDP) characteristics of HBM4 directly enhance data integrity by reducing the likelihood of temperature-induced bit errors. Research indicates that for every 10°C reduction in operating temperature, error rates can decrease by up to 50% in high-throughput memory systems. HBM4's enhanced thermal management therefore contributes significantly to overall system reliability.

From a system integration perspective, HBM4 introduces intelligent power states that allow for granular control over memory subsystems. These states include ultra-low power retention modes that preserve data integrity while minimizing standby power consumption. The transition between power states has been optimized to occur within nanoseconds, ensuring minimal impact on system responsiveness while maximizing energy efficiency.

The cumulative effect of these power and thermal improvements extends beyond the memory subsystem itself. By reducing cooling requirements and power consumption, HBM4 enables system designers to allocate more of their thermal and power budget to processing elements, potentially increasing overall computational density. This synergistic relationship between memory and processing elements represents a significant advancement in balanced system design for high-throughput applications.

The architectural improvements in HBM4 include redesigned power delivery networks that reduce resistance and voltage drops across the memory stack. These enhancements, coupled with more efficient charge pumps and voltage regulators, contribute to a reported 30% reduction in power consumption compared to previous HBM generations while maintaining or improving data throughput capabilities.

Thermal management in HBM4 has been revolutionized through the implementation of advanced materials with superior thermal conductivity properties. The integration of graphene-based thermal interface materials between memory dies facilitates more efficient heat dissipation, addressing one of the primary constraints in high-density memory configurations. Additionally, HBM4 incorporates distributed thermal sensors throughout the memory stack, enabling real-time temperature monitoring and proactive thermal management.

The improved thermal design power (TDP) characteristics of HBM4 directly enhance data integrity by reducing the likelihood of temperature-induced bit errors. Research indicates that for every 10°C reduction in operating temperature, error rates can decrease by up to 50% in high-throughput memory systems. HBM4's enhanced thermal management therefore contributes significantly to overall system reliability.

From a system integration perspective, HBM4 introduces intelligent power states that allow for granular control over memory subsystems. These states include ultra-low power retention modes that preserve data integrity while minimizing standby power consumption. The transition between power states has been optimized to occur within nanoseconds, ensuring minimal impact on system responsiveness while maximizing energy efficiency.

The cumulative effect of these power and thermal improvements extends beyond the memory subsystem itself. By reducing cooling requirements and power consumption, HBM4 enables system designers to allocate more of their thermal and power budget to processing elements, potentially increasing overall computational density. This synergistic relationship between memory and processing elements represents a significant advancement in balanced system design for high-throughput applications.

Security Features and Encryption Capabilities of HBM4

HBM4 introduces significant advancements in security features and encryption capabilities, addressing the critical need for data protection in high-throughput systems. The architecture incorporates hardware-level security mechanisms that provide robust protection against various attack vectors while maintaining performance efficiency. These security features are designed to operate with minimal latency overhead, ensuring that the primary advantage of HBM4's high bandwidth is not compromised.

At the core of HBM4's security framework is an enhanced encryption engine that supports multiple industry-standard cryptographic algorithms, including AES-256, ChaCha20, and elliptic curve cryptography. This versatility allows system designers to implement security protocols that best match their specific requirements and threat models. The encryption processes are hardware-accelerated, significantly reducing the computational burden that would otherwise impact system performance.

HBM4 implements secure boot mechanisms that verify the integrity of firmware and software components before execution, establishing a chain of trust from hardware to application layers. This feature prevents unauthorized code execution and protects against boot-level attacks that could compromise the entire system. Additionally, the memory controller incorporates runtime integrity checking that continuously monitors for anomalies in data patterns that might indicate tampering attempts.

For enterprise and cloud environments, HBM4 offers memory isolation capabilities that create secure enclaves within the physical memory space. These isolated regions prevent unauthorized access between different virtual machines or containers, addressing a common vulnerability in shared computing environments. The isolation is enforced at the hardware level, making it significantly more difficult to bypass compared to software-based solutions.

Key management has been substantially improved in HBM4, with dedicated secure key storage elements that are physically isolated from the main memory array. These elements utilize tamper-resistant technology to protect cryptographic keys even against sophisticated physical attacks. The key management system supports dynamic key rotation and secure key derivation functions, aligning with zero-trust security principles increasingly adopted in modern system architectures.

HBM4 also introduces advanced side-channel attack mitigations, addressing vulnerabilities that have historically plagued memory systems. These include timing attack countermeasures, power analysis protections, and electromagnetic emission controls. Such comprehensive protection is particularly valuable in high-security applications like financial services, healthcare, and government systems where data integrity is paramount.

At the core of HBM4's security framework is an enhanced encryption engine that supports multiple industry-standard cryptographic algorithms, including AES-256, ChaCha20, and elliptic curve cryptography. This versatility allows system designers to implement security protocols that best match their specific requirements and threat models. The encryption processes are hardware-accelerated, significantly reducing the computational burden that would otherwise impact system performance.

HBM4 implements secure boot mechanisms that verify the integrity of firmware and software components before execution, establishing a chain of trust from hardware to application layers. This feature prevents unauthorized code execution and protects against boot-level attacks that could compromise the entire system. Additionally, the memory controller incorporates runtime integrity checking that continuously monitors for anomalies in data patterns that might indicate tampering attempts.

For enterprise and cloud environments, HBM4 offers memory isolation capabilities that create secure enclaves within the physical memory space. These isolated regions prevent unauthorized access between different virtual machines or containers, addressing a common vulnerability in shared computing environments. The isolation is enforced at the hardware level, making it significantly more difficult to bypass compared to software-based solutions.

Key management has been substantially improved in HBM4, with dedicated secure key storage elements that are physically isolated from the main memory array. These elements utilize tamper-resistant technology to protect cryptographic keys even against sophisticated physical attacks. The key management system supports dynamic key rotation and secure key derivation functions, aligning with zero-trust security principles increasingly adopted in modern system architectures.

HBM4 also introduces advanced side-channel attack mitigations, addressing vulnerabilities that have historically plagued memory systems. These include timing attack countermeasures, power analysis protections, and electromagnetic emission controls. Such comprehensive protection is particularly valuable in high-security applications like financial services, healthcare, and government systems where data integrity is paramount.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!