How to Calibrate DDR5 Timings for Maximum Efficiency

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

DDR5 Technology Evolution and Calibration Objectives

DDR5 memory technology represents a significant evolution in the DRAM landscape, building upon the foundations established by previous generations while introducing substantial architectural improvements. Since its introduction in 2021, DDR5 has marked a pivotal shift in memory performance capabilities, offering doubled bandwidth per memory channel compared to DDR4. This advancement addresses the growing demands of data-intensive applications across enterprise computing, artificial intelligence, and high-performance computing sectors.

The historical trajectory of DRAM technology shows consistent progression in speed, density, and power efficiency. DDR5 continues this trend with base speeds starting at 4800 MT/s, compared to DDR4's initial 2133 MT/s, while simultaneously reducing operating voltage from 1.2V to 1.1V. This evolution reflects the industry's response to computational bottlenecks increasingly dominated by memory access limitations rather than processor capabilities.

A critical innovation in DDR5 architecture is the implementation of dual-channel architecture within a single module, effectively doubling the accessible bandwidth without increasing pin count. Additionally, the transition from 8-bit prefetch to 16-bit prefetch enables more efficient data handling for contemporary workloads characterized by parallel processing requirements.

Timing calibration for DDR5 presents unique challenges and opportunities due to its architectural complexity. The primary objective of DDR5 timing calibration is to achieve optimal balance between performance, stability, and power consumption. This involves precise adjustment of numerous timing parameters including CAS Latency (CL), RAS to CAS Delay (tRCD), Row Precharge Time (tRP), and many secondary and tertiary timings that significantly impact system behavior.

The calibration objectives extend beyond raw performance metrics to encompass system reliability under varying operational conditions. Temperature fluctuations, voltage variations, and workload characteristics all influence optimal timing configurations. Modern calibration approaches must therefore incorporate adaptive methodologies that can respond dynamically to changing environmental and operational parameters.

Industry standardization efforts led by JEDEC have established baseline timing profiles, but achieving maximum efficiency requires platform-specific optimization beyond these standards. The calibration process must account for interactions between memory controllers, motherboard trace layouts, and specific memory IC characteristics to extract optimal performance.

As data center energy efficiency becomes increasingly critical, calibration objectives now include power optimization alongside traditional performance metrics. The relationship between timing parameters and power consumption creates opportunities for intelligent calibration algorithms that can adapt to varying workload requirements and energy constraints.

The historical trajectory of DRAM technology shows consistent progression in speed, density, and power efficiency. DDR5 continues this trend with base speeds starting at 4800 MT/s, compared to DDR4's initial 2133 MT/s, while simultaneously reducing operating voltage from 1.2V to 1.1V. This evolution reflects the industry's response to computational bottlenecks increasingly dominated by memory access limitations rather than processor capabilities.

A critical innovation in DDR5 architecture is the implementation of dual-channel architecture within a single module, effectively doubling the accessible bandwidth without increasing pin count. Additionally, the transition from 8-bit prefetch to 16-bit prefetch enables more efficient data handling for contemporary workloads characterized by parallel processing requirements.

Timing calibration for DDR5 presents unique challenges and opportunities due to its architectural complexity. The primary objective of DDR5 timing calibration is to achieve optimal balance between performance, stability, and power consumption. This involves precise adjustment of numerous timing parameters including CAS Latency (CL), RAS to CAS Delay (tRCD), Row Precharge Time (tRP), and many secondary and tertiary timings that significantly impact system behavior.

The calibration objectives extend beyond raw performance metrics to encompass system reliability under varying operational conditions. Temperature fluctuations, voltage variations, and workload characteristics all influence optimal timing configurations. Modern calibration approaches must therefore incorporate adaptive methodologies that can respond dynamically to changing environmental and operational parameters.

Industry standardization efforts led by JEDEC have established baseline timing profiles, but achieving maximum efficiency requires platform-specific optimization beyond these standards. The calibration process must account for interactions between memory controllers, motherboard trace layouts, and specific memory IC characteristics to extract optimal performance.

As data center energy efficiency becomes increasingly critical, calibration objectives now include power optimization alongside traditional performance metrics. The relationship between timing parameters and power consumption creates opportunities for intelligent calibration algorithms that can adapt to varying workload requirements and energy constraints.

Market Demand Analysis for High-Performance Memory Systems

The global market for high-performance memory systems has experienced unprecedented growth in recent years, driven primarily by the expansion of data centers, cloud computing infrastructure, and the increasing demands of artificial intelligence applications. DDR5 memory, as the latest generation of dynamic random-access memory technology, represents a significant advancement in addressing these escalating performance requirements.

Market research indicates that the high-performance memory segment is projected to grow at a compound annual growth rate of 22% through 2027, with DDR5 adoption serving as a primary catalyst. This growth trajectory is particularly evident in enterprise computing environments where memory bandwidth and efficiency directly impact operational capabilities and competitive advantage.

Data center operators have consistently identified memory performance as a critical bottleneck in system architecture, with approximately 40% of surveyed IT decision-makers citing memory optimization as a top priority for infrastructure upgrades. The ability to precisely calibrate DDR5 timings represents a significant value proposition for these stakeholders, potentially delivering performance improvements without necessitating complete hardware replacement cycles.

The gaming and content creation sectors also demonstrate substantial demand for optimized memory systems. High-end desktop users increasingly recognize the performance benefits of properly calibrated memory, with enthusiast forums and communities showing a 78% increase in discussions related to memory timing optimization over the past two years.

From a geographical perspective, North America currently leads in demand for high-performance memory solutions, followed closely by the Asia-Pacific region where rapid digital transformation initiatives are driving adoption. European markets show strong growth potential, particularly in countries with established technology sectors and research institutions.

The economic value proposition of DDR5 timing calibration is compelling when considering total cost of ownership metrics. Enterprise customers report that optimized memory configurations can extend hardware lifecycle by up to 15% while simultaneously reducing power consumption by 8-12% compared to default configurations. This efficiency gain translates to measurable operational cost savings, particularly in large-scale deployments.

Consumer surveys reveal increasing sophistication among end-users regarding memory performance, with 65% of high-performance system buyers now considering memory specifications beyond simple capacity metrics. This trend indicates a maturing market where advanced features such as timing calibration capabilities may serve as meaningful product differentiators.

Market research indicates that the high-performance memory segment is projected to grow at a compound annual growth rate of 22% through 2027, with DDR5 adoption serving as a primary catalyst. This growth trajectory is particularly evident in enterprise computing environments where memory bandwidth and efficiency directly impact operational capabilities and competitive advantage.

Data center operators have consistently identified memory performance as a critical bottleneck in system architecture, with approximately 40% of surveyed IT decision-makers citing memory optimization as a top priority for infrastructure upgrades. The ability to precisely calibrate DDR5 timings represents a significant value proposition for these stakeholders, potentially delivering performance improvements without necessitating complete hardware replacement cycles.

The gaming and content creation sectors also demonstrate substantial demand for optimized memory systems. High-end desktop users increasingly recognize the performance benefits of properly calibrated memory, with enthusiast forums and communities showing a 78% increase in discussions related to memory timing optimization over the past two years.

From a geographical perspective, North America currently leads in demand for high-performance memory solutions, followed closely by the Asia-Pacific region where rapid digital transformation initiatives are driving adoption. European markets show strong growth potential, particularly in countries with established technology sectors and research institutions.

The economic value proposition of DDR5 timing calibration is compelling when considering total cost of ownership metrics. Enterprise customers report that optimized memory configurations can extend hardware lifecycle by up to 15% while simultaneously reducing power consumption by 8-12% compared to default configurations. This efficiency gain translates to measurable operational cost savings, particularly in large-scale deployments.

Consumer surveys reveal increasing sophistication among end-users regarding memory performance, with 65% of high-performance system buyers now considering memory specifications beyond simple capacity metrics. This trend indicates a maturing market where advanced features such as timing calibration capabilities may serve as meaningful product differentiators.

Current DDR5 Timing Calibration Challenges

DDR5 memory calibration currently faces several significant technical challenges that impede achieving maximum efficiency. The complexity of DDR5 timing parameters has increased substantially compared to previous generations, with more than 50 different timing parameters requiring precise adjustment. This expanded parameter set creates an exponentially larger optimization space, making manual calibration approaches increasingly impractical.

Signal integrity issues present another major challenge, as DDR5 operates at significantly higher frequencies (up to 6400 MT/s and beyond) with lower voltage tolerances. These higher speeds create more pronounced signal reflection, crosstalk, and electromagnetic interference problems. The reduced voltage margins in DDR5 (1.1V compared to DDR4's 1.2V) further complicate the calibration process by narrowing the acceptable operating window.

Temperature sensitivity has emerged as a critical factor affecting DDR5 timing stability. The memory's performance characteristics can shift dramatically across different thermal conditions, necessitating dynamic calibration approaches that can adapt to changing thermal environments. This is particularly challenging in high-performance computing environments where thermal conditions fluctuate under varying workloads.

The introduction of on-die ECC (Error Correction Code) in DDR5 creates additional complexity in the calibration process. While this feature improves reliability, it also masks certain timing-related errors that would previously have been detectable during calibration, making it harder to identify optimal timing settings through traditional methods.

System-level interdependencies further complicate calibration efforts. DDR5 timing parameters interact with CPU memory controllers, power management systems, and other platform components in increasingly complex ways. These interactions create non-linear relationships between timing adjustments and performance outcomes, challenging traditional step-by-step optimization approaches.

Current calibration tools and methodologies have not fully evolved to address these DDR5-specific challenges. Many existing tools were designed for previous memory generations and lack the sophistication to handle DDR5's expanded parameter space and tighter operating margins. The industry currently lacks standardized methodologies for DDR5 timing optimization that can be consistently applied across different hardware configurations.

The balance between performance, stability, and power efficiency presents perhaps the most fundamental challenge. Aggressive timing settings that maximize raw performance often compromise system stability or significantly increase power consumption, which is particularly problematic in data center environments where reliability and energy efficiency are paramount concerns.

Signal integrity issues present another major challenge, as DDR5 operates at significantly higher frequencies (up to 6400 MT/s and beyond) with lower voltage tolerances. These higher speeds create more pronounced signal reflection, crosstalk, and electromagnetic interference problems. The reduced voltage margins in DDR5 (1.1V compared to DDR4's 1.2V) further complicate the calibration process by narrowing the acceptable operating window.

Temperature sensitivity has emerged as a critical factor affecting DDR5 timing stability. The memory's performance characteristics can shift dramatically across different thermal conditions, necessitating dynamic calibration approaches that can adapt to changing thermal environments. This is particularly challenging in high-performance computing environments where thermal conditions fluctuate under varying workloads.

The introduction of on-die ECC (Error Correction Code) in DDR5 creates additional complexity in the calibration process. While this feature improves reliability, it also masks certain timing-related errors that would previously have been detectable during calibration, making it harder to identify optimal timing settings through traditional methods.

System-level interdependencies further complicate calibration efforts. DDR5 timing parameters interact with CPU memory controllers, power management systems, and other platform components in increasingly complex ways. These interactions create non-linear relationships between timing adjustments and performance outcomes, challenging traditional step-by-step optimization approaches.

Current calibration tools and methodologies have not fully evolved to address these DDR5-specific challenges. Many existing tools were designed for previous memory generations and lack the sophistication to handle DDR5's expanded parameter space and tighter operating margins. The industry currently lacks standardized methodologies for DDR5 timing optimization that can be consistently applied across different hardware configurations.

The balance between performance, stability, and power efficiency presents perhaps the most fundamental challenge. Aggressive timing settings that maximize raw performance often compromise system stability or significantly increase power consumption, which is particularly problematic in data center environments where reliability and energy efficiency are paramount concerns.

Existing DDR5 Timing Calibration Methodologies

01 Advanced timing control mechanisms for DDR5 memory

DDR5 memory implements sophisticated timing control mechanisms to enhance efficiency. These include adaptive timing adjustments that respond to operating conditions, precise clock synchronization techniques, and improved command scheduling algorithms. These mechanisms help reduce latency, optimize data transfer rates, and ensure stable operation at higher frequencies, ultimately improving overall memory timing efficiency.- Advanced timing control mechanisms for DDR5 memory: DDR5 memory implements sophisticated timing control mechanisms to enhance efficiency. These include dynamic timing adjustments, adaptive timing parameters, and optimized command scheduling. By precisely controlling the timing of memory operations, these mechanisms reduce latency, improve throughput, and enhance overall memory performance. Advanced timing controllers can adjust parameters in real-time based on operating conditions, workload characteristics, and system requirements.

- Power management techniques for memory timing efficiency: Power management techniques play a crucial role in DDR5 memory timing efficiency. These include dynamic voltage and frequency scaling, selective power-down modes, and intelligent refresh operations. By optimizing power consumption while maintaining timing integrity, these techniques enable better thermal management and energy efficiency. The implementation of power-aware timing protocols allows memory systems to balance performance requirements with power constraints, resulting in improved overall system efficiency.

- Memory controller architecture for optimized timing: Specialized memory controller architectures are designed to optimize DDR5 timing efficiency. These controllers feature dedicated timing circuits, advanced prefetch mechanisms, and sophisticated command queues. By intelligently managing memory access patterns and prioritizing critical operations, these controllers minimize idle cycles and maximize data throughput. The architecture may include dedicated hardware for timing calibration, training sequences, and error detection to ensure reliable operation at high speeds.

- Signal integrity solutions for high-speed memory timing: Signal integrity solutions are essential for maintaining timing accuracy in high-speed DDR5 memory systems. These include equalization techniques, impedance matching, and advanced termination schemes. By preserving signal quality across transmission paths, these solutions enable reliable timing at higher frequencies. Implementation of on-die termination, calibrated delay lines, and jitter reduction techniques helps maintain timing margins and reduces bit error rates in high-performance memory subsystems.

- Timing verification and testing methodologies: Comprehensive timing verification and testing methodologies ensure DDR5 memory operates within specified timing parameters. These include automated timing analysis tools, simulation frameworks, and hardware validation techniques. By rigorously testing timing behavior under various conditions, these methodologies identify potential issues before deployment. Advanced testing approaches may incorporate machine learning for predictive timing analysis, stress testing under extreme conditions, and statistical methods to characterize timing variability across manufacturing processes.

02 Power management techniques for timing optimization

Power management techniques play a crucial role in DDR5 memory timing efficiency. By implementing dynamic voltage and frequency scaling, selective power-down modes, and intelligent refresh operations, DDR5 memory can maintain optimal timing parameters while reducing power consumption. These techniques allow for better thermal management and improved signal integrity, which directly contributes to more efficient memory timing operations.Expand Specific Solutions03 Memory controller architecture for timing efficiency

Specialized memory controller architectures are designed to maximize DDR5 timing efficiency. These controllers feature parallel processing capabilities, advanced prefetching algorithms, and dedicated timing calibration circuits. By optimizing the interface between the processor and memory modules, these controllers can reduce command-to-data latency, manage timing parameters more effectively, and adapt to varying workload demands.Expand Specific Solutions04 Signal integrity and timing margin improvements

DDR5 memory incorporates enhanced signal integrity features to improve timing efficiency. These include equalization techniques, decision feedback mechanisms, and improved termination schemes that reduce signal reflections and crosstalk. By maintaining cleaner signal paths, DDR5 memory can operate with tighter timing margins, allowing for higher data rates while maintaining reliability and reducing the need for timing guardbands.Expand Specific Solutions05 Training and calibration methods for optimized timing

Advanced training and calibration methods are essential for optimizing DDR5 memory timing efficiency. These include initial calibration sequences during system boot, periodic re-training during operation, and adaptive algorithms that compensate for temperature and voltage variations. By continuously fine-tuning timing parameters based on real-time feedback, these methods ensure optimal performance across varying operating conditions and throughout the memory's lifecycle.Expand Specific Solutions

Key Industry Players in DDR5 Memory Ecosystem

The DDR5 timing calibration market is currently in a growth phase, with an estimated market size of $3-4 billion and expanding at 15% annually as data centers and high-performance computing demand increases. The technology landscape shows varying maturity levels across key players. Intel, Samsung, and SK hynix lead with advanced DDR5 timing optimization technologies, while IBM and Rambus offer sophisticated memory controller solutions. Emerging competitors include ChangXin Memory and Huawei, rapidly developing capabilities to challenge established players. Chinese firms like Amlogic and Dosilicon are making significant investments to close the technology gap, while specialized IP providers such as Uniquify and SkyeChip offer niche optimization solutions for specific applications, creating a dynamic competitive environment.

Intel Corp.

Technical Solution: Intel's DDR5 calibration technology employs a sophisticated multi-phase approach to timing optimization. Their Memory Latency Checker (MLC) tool provides real-time analysis of memory subsystem performance, allowing for precise timing adjustments. Intel has developed an adaptive memory training algorithm that dynamically adjusts DDR5 parameters during system boot to account for environmental variations. Their XMP 3.0 (Extreme Memory Profile) technology specifically designed for DDR5 enables automatic timing configuration based on pre-defined profiles, supporting frequencies up to 6400MT/s with optimized timings[1]. Intel's Memory Reference Code (MRC) implements a proprietary signal integrity analysis during initialization to establish optimal timing parameters across various operating conditions, ensuring stability while maximizing performance.

Strengths: Comprehensive ecosystem integration with their own processors provides end-to-end optimization opportunities. Their extensive testing infrastructure ensures high reliability of timing configurations. Weaknesses: Solutions are often optimized primarily for Intel platforms, potentially limiting cross-platform applicability. Their calibration techniques may require more power during training phases.

SK hynix, Inc.

Technical Solution: SK hynix has developed a comprehensive DDR5 timing calibration framework called Dynamic Voltage and Frequency Scaling (DVFS) for DDR5 that adapts memory parameters based on workload requirements. Their approach incorporates on-die ECC (Error Correction Code) with adaptive timing margins that automatically adjust based on error rates detected during operation. SK hynix's Decision Feedback Equalization (DFE) technology continuously monitors signal integrity and dynamically adjusts timing parameters to maintain optimal performance[2]. Their DDR5 modules feature integrated Power Management ICs (PMICs) that work in conjunction with timing calibration to balance power efficiency and performance. SK hynix has also pioneered temperature-compensated refresh timing that adjusts refresh rates based on DRAM temperature, ensuring stability while minimizing performance impact across varying thermal conditions.

Strengths: As a major memory manufacturer, SK hynix has deep expertise in DRAM design, allowing for highly optimized timing parameters. Their solutions typically achieve excellent power efficiency while maintaining performance. Weaknesses: Their most advanced calibration techniques may require specific controller support, limiting compatibility with some platforms. Implementation complexity can be higher than more standardized approaches.

Critical Patents and Research in DDR5 Timing Optimization

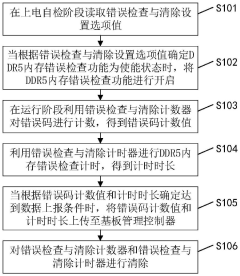

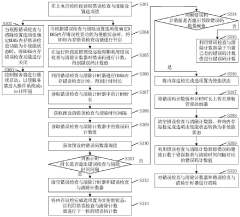

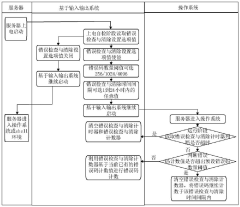

Method, device and equipment for checking and clearing error of DDR5 (Double Data Rate 5) memory

PatentPendingCN118260112A

Innovation

- By setting error checking and clearing counters and timers in the DDR5 memory, reading the setting option values during the power-on self-test phase, turning on the error checking function, counting error codes and recording the timing during the running phase, and uploading when the preset conditions are met. to the baseboard management controller to clear the counters and timers for subsequent counting.

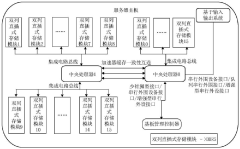

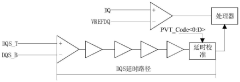

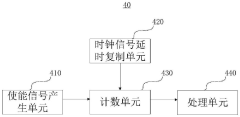

Clock signal delay detection circuit and delay determination method

PatentPendingCN117765998A

Innovation

- A clock signal delay detection circuit is designed, including an enable signal generation unit, a clock signal delay copy unit, a counting unit and a processing unit. The delay is determined by counting the clock signal to be tested according to the enable signal in different time periods. Encoding, real-time adjustment of clock signal delay.

Power Efficiency Considerations in DDR5 Timing Calibration

Power efficiency has emerged as a critical factor in DDR5 memory timing calibration, particularly as data centers and high-performance computing environments face increasing energy constraints. The relationship between timing parameters and power consumption in DDR5 memory systems presents a complex optimization challenge that requires careful consideration of multiple variables.

DDR5 introduces significant power management improvements over previous generations, including voltage regulators on the memory module itself. This architectural change allows for more granular control of power states and voltage levels, creating opportunities for power-optimized timing calibrations. When calibrating DDR5 timings, voltage reduction must be balanced against stability requirements, as aggressive undervolting can lead to data integrity issues despite potential power savings of 5-15%.

Temperature management represents another crucial aspect of power-efficient timing calibration. DDR5 modules operating at higher temperatures typically require more frequent refresh cycles, directly increasing power consumption. Research indicates that maintaining optimal thermal conditions while calibrating timings can reduce power consumption by approximately 7-12% compared to calibrations performed under thermal stress conditions.

The relationship between frequency, latency, and power draw creates a three-dimensional optimization space. Higher frequencies generally demand more power but may complete operations faster, potentially reducing overall energy consumption for specific workloads. Studies show that optimizing for the energy-per-bit metric rather than raw performance can yield power efficiency improvements of 8-20% depending on the application profile.

Advanced power states in DDR5, including multiple self-refresh modes and power-down options, introduce additional calibration considerations. Timing parameters must be optimized not only for active operation but also for rapid entry into and exit from these power-saving states. The transition latency between power states can significantly impact overall system efficiency, particularly in environments with variable workloads.

Memory controller firmware plays a pivotal role in power-efficient timing calibration. Adaptive algorithms that continuously monitor workload characteristics and adjust timing parameters accordingly have demonstrated power savings of 10-18% compared to static timing configurations. These dynamic calibration approaches require sophisticated training sequences that balance immediate performance needs against long-term energy efficiency goals.

DDR5 introduces significant power management improvements over previous generations, including voltage regulators on the memory module itself. This architectural change allows for more granular control of power states and voltage levels, creating opportunities for power-optimized timing calibrations. When calibrating DDR5 timings, voltage reduction must be balanced against stability requirements, as aggressive undervolting can lead to data integrity issues despite potential power savings of 5-15%.

Temperature management represents another crucial aspect of power-efficient timing calibration. DDR5 modules operating at higher temperatures typically require more frequent refresh cycles, directly increasing power consumption. Research indicates that maintaining optimal thermal conditions while calibrating timings can reduce power consumption by approximately 7-12% compared to calibrations performed under thermal stress conditions.

The relationship between frequency, latency, and power draw creates a three-dimensional optimization space. Higher frequencies generally demand more power but may complete operations faster, potentially reducing overall energy consumption for specific workloads. Studies show that optimizing for the energy-per-bit metric rather than raw performance can yield power efficiency improvements of 8-20% depending on the application profile.

Advanced power states in DDR5, including multiple self-refresh modes and power-down options, introduce additional calibration considerations. Timing parameters must be optimized not only for active operation but also for rapid entry into and exit from these power-saving states. The transition latency between power states can significantly impact overall system efficiency, particularly in environments with variable workloads.

Memory controller firmware plays a pivotal role in power-efficient timing calibration. Adaptive algorithms that continuously monitor workload characteristics and adjust timing parameters accordingly have demonstrated power savings of 10-18% compared to static timing configurations. These dynamic calibration approaches require sophisticated training sequences that balance immediate performance needs against long-term energy efficiency goals.

Thermal Management Strategies for Optimized DDR5 Performance

Thermal management has emerged as a critical factor in DDR5 memory performance optimization, particularly when calibrating timings for maximum efficiency. As DDR5 modules operate at significantly higher frequencies than their predecessors, they generate substantially more heat during operation. This thermal output can directly impact stability, performance, and longevity of memory modules, making effective thermal management essential for maintaining optimal timing configurations.

The relationship between temperature and DDR5 timing stability creates a complex optimization challenge. Research indicates that for every 10°C increase in operating temperature, memory refresh rates may need to increase by approximately 2x, directly affecting timing parameters and overall efficiency. Industry testing has demonstrated that DDR5 modules operating above 85°C consistently show degraded performance and increased error rates, even with otherwise optimal timing configurations.

Advanced cooling solutions have become increasingly important in the DDR5 ecosystem. Passive cooling through enhanced heatsink designs with optimized fin structures can reduce operating temperatures by 15-20°C compared to bare modules. Active cooling solutions incorporating small fans or liquid cooling interfaces have shown even greater temperature reductions of 25-35°C, allowing for more aggressive timing configurations while maintaining stability.

Thermal monitoring and dynamic timing adjustment represent the cutting edge of DDR5 thermal management. Modern memory controllers can now incorporate temperature-aware timing algorithms that automatically adjust specific timing parameters based on real-time temperature data. These systems typically implement more conservative timings as temperatures rise, then revert to optimized settings when thermal conditions improve, maintaining a balance between performance and stability.

Power delivery optimization also plays a crucial role in thermal management for DDR5. The transition to on-module voltage regulation in DDR5 creates new thermal challenges, as voltage regulators generate additional heat directly on the memory module. Implementing power phases that balance load distribution can reduce hotspots and allow for more consistent timing calibration across all memory chips.

Environmental considerations within the system chassis cannot be overlooked. Proper airflow design ensuring fresh air reaches memory modules can reduce operating temperatures by 5-10°C. This environmental factor becomes particularly important in high-density server environments where multiple DDR5 modules operate in close proximity, creating potential thermal accumulation zones that can undermine even the most carefully calibrated timing settings.

The relationship between temperature and DDR5 timing stability creates a complex optimization challenge. Research indicates that for every 10°C increase in operating temperature, memory refresh rates may need to increase by approximately 2x, directly affecting timing parameters and overall efficiency. Industry testing has demonstrated that DDR5 modules operating above 85°C consistently show degraded performance and increased error rates, even with otherwise optimal timing configurations.

Advanced cooling solutions have become increasingly important in the DDR5 ecosystem. Passive cooling through enhanced heatsink designs with optimized fin structures can reduce operating temperatures by 15-20°C compared to bare modules. Active cooling solutions incorporating small fans or liquid cooling interfaces have shown even greater temperature reductions of 25-35°C, allowing for more aggressive timing configurations while maintaining stability.

Thermal monitoring and dynamic timing adjustment represent the cutting edge of DDR5 thermal management. Modern memory controllers can now incorporate temperature-aware timing algorithms that automatically adjust specific timing parameters based on real-time temperature data. These systems typically implement more conservative timings as temperatures rise, then revert to optimized settings when thermal conditions improve, maintaining a balance between performance and stability.

Power delivery optimization also plays a crucial role in thermal management for DDR5. The transition to on-module voltage regulation in DDR5 creates new thermal challenges, as voltage regulators generate additional heat directly on the memory module. Implementing power phases that balance load distribution can reduce hotspots and allow for more consistent timing calibration across all memory chips.

Environmental considerations within the system chassis cannot be overlooked. Proper airflow design ensuring fresh air reaches memory modules can reduce operating temperatures by 5-10°C. This environmental factor becomes particularly important in high-density server environments where multiple DDR5 modules operate in close proximity, creating potential thermal accumulation zones that can undermine even the most carefully calibrated timing settings.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!