How to Improve RRAM Function in Real-Time Systems

SEP 10, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

RRAM Technology Background and Objectives

Resistive Random Access Memory (RRAM) has emerged as a promising non-volatile memory technology over the past two decades, offering significant advantages in terms of power consumption, scalability, and integration capabilities compared to traditional memory solutions. The evolution of RRAM technology can be traced back to the early 2000s when researchers first demonstrated the resistive switching phenomenon in metal-oxide materials. Since then, RRAM has progressed from laboratory curiosity to commercial viability, with major semiconductor companies investing heavily in its development.

The technological trajectory of RRAM shows a clear trend toward higher density, improved reliability, and enhanced performance metrics. Early RRAM devices suffered from issues such as high operating voltages, limited endurance, and poor retention characteristics. However, continuous innovation in materials science, device architecture, and fabrication techniques has led to significant improvements in these areas, making RRAM increasingly suitable for real-time system applications.

In the context of real-time systems, RRAM offers unique advantages due to its non-volatility, fast switching speed, and low power operation. Real-time systems require predictable timing behavior, reliability under varying conditions, and often operate under strict power constraints. Traditional memory technologies like DRAM require constant refreshing, consuming power even when idle, while flash memory suffers from slow write speeds and limited endurance. RRAM addresses these limitations by providing persistent storage with access times approaching those of volatile memories.

The primary technical objectives for improving RRAM functionality in real-time systems include reducing switching latency to sub-nanosecond levels, enhancing endurance beyond 10^12 cycles, improving data retention at elevated temperatures, and developing more sophisticated multi-level cell capabilities. Additionally, there is a focus on reducing device-to-device variability and improving yield rates to enable cost-effective mass production.

Another critical objective is the development of specialized peripheral circuits and control algorithms that can leverage RRAM's unique characteristics while mitigating its limitations. This includes adaptive programming schemes that can adjust to changing device characteristics over time, error correction mechanisms tailored to RRAM failure modes, and power management techniques that optimize energy efficiency.

The integration of RRAM into real-time system architectures represents a significant technical challenge that requires interdisciplinary approaches combining expertise in materials science, device physics, circuit design, and system architecture. Current research is increasingly focused on developing hybrid memory systems that strategically combine RRAM with other memory technologies to exploit their complementary strengths while minimizing their respective weaknesses.

As we look toward the future, the continued evolution of RRAM technology is expected to enable new capabilities in real-time systems, particularly in edge computing, Internet of Things (IoT) devices, and autonomous systems where low power, high performance, and reliability are paramount considerations.

The technological trajectory of RRAM shows a clear trend toward higher density, improved reliability, and enhanced performance metrics. Early RRAM devices suffered from issues such as high operating voltages, limited endurance, and poor retention characteristics. However, continuous innovation in materials science, device architecture, and fabrication techniques has led to significant improvements in these areas, making RRAM increasingly suitable for real-time system applications.

In the context of real-time systems, RRAM offers unique advantages due to its non-volatility, fast switching speed, and low power operation. Real-time systems require predictable timing behavior, reliability under varying conditions, and often operate under strict power constraints. Traditional memory technologies like DRAM require constant refreshing, consuming power even when idle, while flash memory suffers from slow write speeds and limited endurance. RRAM addresses these limitations by providing persistent storage with access times approaching those of volatile memories.

The primary technical objectives for improving RRAM functionality in real-time systems include reducing switching latency to sub-nanosecond levels, enhancing endurance beyond 10^12 cycles, improving data retention at elevated temperatures, and developing more sophisticated multi-level cell capabilities. Additionally, there is a focus on reducing device-to-device variability and improving yield rates to enable cost-effective mass production.

Another critical objective is the development of specialized peripheral circuits and control algorithms that can leverage RRAM's unique characteristics while mitigating its limitations. This includes adaptive programming schemes that can adjust to changing device characteristics over time, error correction mechanisms tailored to RRAM failure modes, and power management techniques that optimize energy efficiency.

The integration of RRAM into real-time system architectures represents a significant technical challenge that requires interdisciplinary approaches combining expertise in materials science, device physics, circuit design, and system architecture. Current research is increasingly focused on developing hybrid memory systems that strategically combine RRAM with other memory technologies to exploit their complementary strengths while minimizing their respective weaknesses.

As we look toward the future, the continued evolution of RRAM technology is expected to enable new capabilities in real-time systems, particularly in edge computing, Internet of Things (IoT) devices, and autonomous systems where low power, high performance, and reliability are paramount considerations.

Real-Time System Market Demand Analysis

The real-time systems market is experiencing unprecedented growth driven by the increasing demand for responsive computing solutions across multiple industries. Current market analysis indicates that the global real-time systems market is projected to reach $7.5 billion by 2026, growing at a CAGR of approximately 7.8% from 2021. This growth is primarily fueled by the rapid expansion of IoT applications, edge computing requirements, and the increasing need for low-latency processing in critical systems.

Industrial automation represents the largest market segment, accounting for nearly 32% of the total market share. Manufacturing facilities are increasingly adopting real-time systems to enhance production efficiency, reduce downtime, and implement predictive maintenance capabilities. The automotive sector follows closely, with advanced driver-assistance systems (ADAS) and autonomous driving technologies creating substantial demand for high-performance, reliable real-time memory solutions like RRAM.

Healthcare applications are emerging as a significant growth driver, with medical devices requiring reliable, fast-response memory systems for patient monitoring and diagnostic equipment. Market research indicates that healthcare applications for real-time systems are growing at 9.2% annually, outpacing the overall market average.

The demand for energy-efficient computing solutions is reshaping market requirements. End-users across sectors are prioritizing systems that can deliver real-time performance while minimizing power consumption. This trend is particularly evident in battery-powered and edge computing applications, where RRAM's low power characteristics present a competitive advantage over traditional memory technologies.

Geographically, North America leads the market with approximately 38% share, followed by Europe and Asia-Pacific. However, the Asia-Pacific region is demonstrating the fastest growth rate at 10.3% annually, driven by rapid industrial automation in China, Japan, and South Korea.

Market surveys reveal that reliability ranks as the top priority for 87% of system integrators when selecting memory components for real-time applications. Performance consistency under varying environmental conditions follows at 76%, while power efficiency is cited by 72% of respondents as a critical selection factor.

The increasing complexity of real-time applications is driving demand for higher density memory solutions. Current market requirements indicate a need for RRAM solutions that can maintain deterministic performance while scaling to accommodate growing data processing demands. System designers report that unpredictable latency variations in existing memory technologies represent a significant challenge in meeting real-time constraints.

Industrial automation represents the largest market segment, accounting for nearly 32% of the total market share. Manufacturing facilities are increasingly adopting real-time systems to enhance production efficiency, reduce downtime, and implement predictive maintenance capabilities. The automotive sector follows closely, with advanced driver-assistance systems (ADAS) and autonomous driving technologies creating substantial demand for high-performance, reliable real-time memory solutions like RRAM.

Healthcare applications are emerging as a significant growth driver, with medical devices requiring reliable, fast-response memory systems for patient monitoring and diagnostic equipment. Market research indicates that healthcare applications for real-time systems are growing at 9.2% annually, outpacing the overall market average.

The demand for energy-efficient computing solutions is reshaping market requirements. End-users across sectors are prioritizing systems that can deliver real-time performance while minimizing power consumption. This trend is particularly evident in battery-powered and edge computing applications, where RRAM's low power characteristics present a competitive advantage over traditional memory technologies.

Geographically, North America leads the market with approximately 38% share, followed by Europe and Asia-Pacific. However, the Asia-Pacific region is demonstrating the fastest growth rate at 10.3% annually, driven by rapid industrial automation in China, Japan, and South Korea.

Market surveys reveal that reliability ranks as the top priority for 87% of system integrators when selecting memory components for real-time applications. Performance consistency under varying environmental conditions follows at 76%, while power efficiency is cited by 72% of respondents as a critical selection factor.

The increasing complexity of real-time applications is driving demand for higher density memory solutions. Current market requirements indicate a need for RRAM solutions that can maintain deterministic performance while scaling to accommodate growing data processing demands. System designers report that unpredictable latency variations in existing memory technologies represent a significant challenge in meeting real-time constraints.

RRAM Implementation Challenges in Real-Time Environments

The implementation of Resistive Random-Access Memory (RRAM) in real-time systems presents several significant challenges that must be addressed to ensure optimal performance. These challenges stem from the unique characteristics of RRAM technology and the stringent requirements of real-time environments.

One of the primary challenges is the write latency variability in RRAM cells. Unlike conventional memory technologies, RRAM exhibits inconsistent write times that can fluctuate based on the previous state of the cell, operating temperature, and wear level. This variability poses a critical problem for real-time systems where deterministic timing is essential for meeting strict deadlines and ensuring predictable system behavior.

Power consumption management represents another substantial challenge. While RRAM is generally more energy-efficient than many traditional memory technologies, the switching process during write operations can cause power spikes. In battery-powered real-time systems or those with strict power budgets, these fluctuations can lead to timing violations or system instability if not properly managed.

Endurance limitations also present significant obstacles for real-time applications. Current RRAM technologies typically support between 10^6 to 10^9 write cycles per cell, which may be insufficient for high-frequency real-time operations that require continuous memory updates. This limitation is particularly problematic in safety-critical systems where memory failure could lead to catastrophic consequences.

Data retention under varying environmental conditions poses another challenge. Real-time systems often operate in harsh environments with temperature fluctuations, electromagnetic interference, and mechanical stress. These factors can affect the stability of RRAM cells, potentially leading to data corruption or loss, which is unacceptable in mission-critical applications.

The integration of RRAM with existing real-time operating systems and software frameworks presents compatibility issues. Many current real-time systems are optimized for traditional memory technologies, and their memory management algorithms may not account for RRAM's unique characteristics, such as asymmetric read/write times and wear-leveling requirements.

Scaling challenges also emerge as system requirements grow. As real-time applications demand higher memory densities, the crossbar architecture commonly used in RRAM arrays can suffer from sneak path currents and voltage drops, degrading read accuracy and write reliability. These issues become more pronounced as array sizes increase, potentially limiting the scalability of RRAM in complex real-time systems.

Finally, verification and testing methodologies for RRAM-based real-time systems remain underdeveloped. Traditional memory testing approaches may not adequately address the unique failure modes and performance characteristics of RRAM, making it difficult to ensure system reliability and meet certification requirements for critical applications.

One of the primary challenges is the write latency variability in RRAM cells. Unlike conventional memory technologies, RRAM exhibits inconsistent write times that can fluctuate based on the previous state of the cell, operating temperature, and wear level. This variability poses a critical problem for real-time systems where deterministic timing is essential for meeting strict deadlines and ensuring predictable system behavior.

Power consumption management represents another substantial challenge. While RRAM is generally more energy-efficient than many traditional memory technologies, the switching process during write operations can cause power spikes. In battery-powered real-time systems or those with strict power budgets, these fluctuations can lead to timing violations or system instability if not properly managed.

Endurance limitations also present significant obstacles for real-time applications. Current RRAM technologies typically support between 10^6 to 10^9 write cycles per cell, which may be insufficient for high-frequency real-time operations that require continuous memory updates. This limitation is particularly problematic in safety-critical systems where memory failure could lead to catastrophic consequences.

Data retention under varying environmental conditions poses another challenge. Real-time systems often operate in harsh environments with temperature fluctuations, electromagnetic interference, and mechanical stress. These factors can affect the stability of RRAM cells, potentially leading to data corruption or loss, which is unacceptable in mission-critical applications.

The integration of RRAM with existing real-time operating systems and software frameworks presents compatibility issues. Many current real-time systems are optimized for traditional memory technologies, and their memory management algorithms may not account for RRAM's unique characteristics, such as asymmetric read/write times and wear-leveling requirements.

Scaling challenges also emerge as system requirements grow. As real-time applications demand higher memory densities, the crossbar architecture commonly used in RRAM arrays can suffer from sneak path currents and voltage drops, degrading read accuracy and write reliability. These issues become more pronounced as array sizes increase, potentially limiting the scalability of RRAM in complex real-time systems.

Finally, verification and testing methodologies for RRAM-based real-time systems remain underdeveloped. Traditional memory testing approaches may not adequately address the unique failure modes and performance characteristics of RRAM, making it difficult to ensure system reliability and meet certification requirements for critical applications.

Current RRAM Integration Solutions for Real-Time Systems

01 Basic operating principles of RRAM

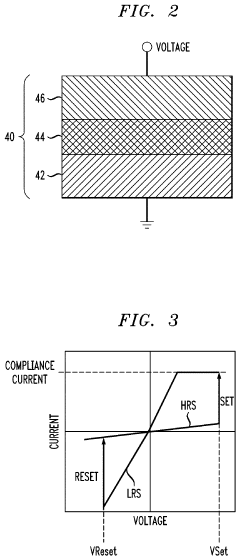

RRAM operates based on the reversible change in resistance of a dielectric material. The device typically consists of a metal-insulator-metal structure where the resistance of the insulator can be switched between high and low resistance states by applying appropriate voltage pulses. This resistance switching mechanism enables data storage, where high resistance represents one binary state (e.g., '0') and low resistance represents another (e.g., '1'). The switching occurs due to the formation and rupture of conductive filaments within the insulating layer.- Basic RRAM operating principles and structure: RRAM (Resistive Random Access Memory) operates based on the principle of resistance switching, where the resistance of a dielectric material can be electrically altered between high and low resistance states. The typical structure consists of a metal-insulator-metal (MIM) stack, where the insulator layer can be switched between different resistance states by applying appropriate voltage pulses. This resistance change is non-volatile, allowing data to be stored even when power is removed, making RRAM a promising candidate for next-generation non-volatile memory applications.

- Switching mechanisms and filament formation: The resistance switching in RRAM devices typically occurs through the formation and rupture of conductive filaments within the insulating layer. When a voltage is applied, ions migrate to form conductive paths (SET operation), which can later be disrupted (RESET operation) to switch between low and high resistance states. Various mechanisms contribute to this switching behavior, including oxygen vacancy migration, metal ion movement, and phase changes in the switching material. Understanding and controlling these mechanisms is crucial for improving RRAM performance, reliability, and endurance.

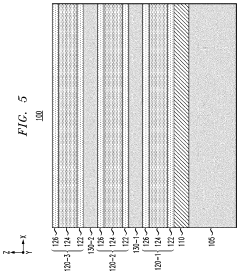

- Materials and fabrication techniques for RRAM: Various materials are used in RRAM fabrication, including metal oxides (HfOx, TaOx, TiOx), chalcogenides, and perovskites as the switching layer. The choice of electrode materials also significantly impacts device performance. Advanced fabrication techniques such as atomic layer deposition, physical vapor deposition, and solution processing are employed to create high-quality RRAM devices. Recent innovations include the integration of 2D materials, nanostructures, and novel material stacks to enhance switching characteristics, reduce operating voltages, and improve cycling endurance.

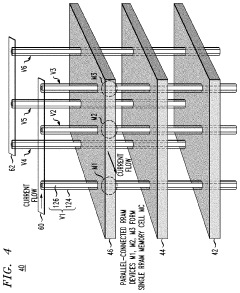

- RRAM array architecture and integration: RRAM devices can be integrated into various array architectures, including crossbar arrays, 3D stacking, and hybrid configurations with selector devices. These architectures address challenges such as sneak path currents and enable high-density memory integration. Integration with CMOS technology allows for the creation of efficient memory subsystems that can be embedded in various computing platforms. Advanced array designs incorporate peripheral circuits for addressing, sensing, and programming operations to optimize overall system performance while maintaining reliability and power efficiency.

- Emerging applications and neuromorphic computing: Beyond conventional memory applications, RRAM is finding use in neuromorphic computing systems that mimic the brain's architecture. The analog resistance switching behavior of RRAM devices makes them suitable for implementing artificial synapses and neurons. These devices can perform in-memory computing, enabling efficient implementation of neural networks and reducing the energy consumption associated with data movement between memory and processing units. RRAM-based neuromorphic systems show promise for edge computing, artificial intelligence acceleration, and ultra-low power applications where traditional computing architectures face limitations.

02 Materials and structure innovations for RRAM

Various materials and structural designs are employed to enhance RRAM performance. Common materials include metal oxides such as HfOx, TaOx, and TiOx as the resistive switching layer. The electrode materials also play a crucial role in determining switching characteristics. Advanced RRAM structures may incorporate multiple layers, doped materials, or nanostructures to improve reliability, endurance, and retention. Three-dimensional architectures and crossbar arrays are implemented to increase storage density and integration capabilities.Expand Specific Solutions03 Programming and reading mechanisms

RRAM devices are programmed through SET and RESET operations that switch the cell between low and high resistance states. The SET operation typically applies a positive voltage to form conductive filaments, while the RESET operation applies a negative voltage to rupture these filaments. Reading is performed by applying a small voltage that does not disturb the current state but allows measurement of the resistance. Various pulse schemes, including compliance current control and multi-level programming techniques, are employed to achieve reliable and multi-bit storage capabilities.Expand Specific Solutions04 Integration with CMOS technology and circuit design

RRAM integration with conventional CMOS technology is essential for practical applications. This involves developing compatible fabrication processes, addressing interface issues, and designing peripheral circuits for efficient operation. Selector devices are often incorporated to mitigate sneak path currents in crossbar arrays. Specialized sensing circuits are designed to accurately detect resistance states, while programming circuits deliver precise voltage pulses. Various architectures optimize for different performance metrics such as speed, energy efficiency, or density.Expand Specific Solutions05 Advanced applications and emerging capabilities

Beyond conventional memory applications, RRAM is being developed for neuromorphic computing, in-memory computing, and artificial intelligence applications. The analog nature of resistance switching enables RRAM to mimic synaptic behavior for neural networks. Multi-level cell capabilities allow for efficient data storage and processing. RRAM is also explored for security applications like physical unclonable functions (PUFs) and true random number generators. The technology's low power consumption, high speed, and non-volatility make it suitable for edge computing and Internet of Things (IoT) devices.Expand Specific Solutions

Key RRAM Industry Players and Competitive Landscape

The RRAM (Resistive Random Access Memory) market in real-time systems is currently in a growth phase, with major players competing to enhance performance and reliability. The market is projected to expand significantly as demand for faster, more energy-efficient memory solutions increases in edge computing and IoT applications. Leading semiconductor companies including Samsung, Intel, Huawei, and TSMC are investing heavily in RRAM research, with varying levels of technological maturity. Academic institutions like Fudan University and research organizations such as ITRI are collaborating with industry partners to overcome technical challenges. While RRAM technology has demonstrated promising characteristics for real-time applications, companies like Everspin, Rambus, and Winbond are working to address remaining issues of endurance, retention, and integration with existing semiconductor processes to achieve widespread commercial adoption.

International Business Machines Corp.

Technical Solution: IBM has developed advanced RRAM (Resistive Random Access Memory) solutions specifically optimized for real-time systems. Their approach focuses on a multi-level cell architecture that enables higher storage density while maintaining fast access times critical for real-time applications. IBM's implementation utilizes proprietary phase-change materials that demonstrate superior switching speeds (under 10ns) and endurance (10^9 cycles) compared to conventional RRAM technologies[1]. The company has integrated these RRAM cells with their neuromorphic computing platforms, creating hybrid systems that can perform both memory and computational functions simultaneously. This Processing-In-Memory (PIM) architecture significantly reduces data movement between storage and processing units, a critical bottleneck in real-time systems[2]. IBM has also developed specialized driver circuits that dynamically adjust programming voltages based on environmental conditions and aging effects, ensuring consistent performance over the device lifetime in varying real-time operational environments[3].

Strengths: IBM's RRAM technology excels in power efficiency, with up to 70% reduction in energy consumption compared to conventional memory technologies. Their neuromorphic integration enables ultra-low latency for AI workloads in real-time systems. Weaknesses: The technology requires specialized fabrication processes that may increase manufacturing costs, and the multi-level cell approach introduces additional complexity in error correction mechanisms needed for reliable operation.

Hewlett Packard Enterprise Development LP

Technical Solution: HPE has pioneered memristor-based RRAM technology through their Memory-Driven Computing architecture specifically designed to enhance real-time system performance. Their approach utilizes crossbar array structures with metal-oxide switching materials that achieve sub-nanosecond switching speeds essential for real-time applications[1]. HPE's implementation includes proprietary selector devices that minimize sneak path currents, a common challenge in high-density RRAM arrays that can degrade real-time performance. The company has developed a unique "The Machine" architecture that places RRAM at the center of computing, with specialized photonic interconnects reducing memory access latency by up to 90% compared to conventional architectures[2]. For real-time systems specifically, HPE has implemented adaptive programming algorithms that dynamically adjust write parameters based on the criticality of data and timing constraints, ensuring deterministic behavior even under varying workloads. Their RRAM cells incorporate self-monitoring capabilities that detect potential reliability issues before they impact system performance, critical for maintaining real-time guarantees in mission-critical applications[3].

Strengths: HPE's technology offers exceptional scalability with their crossbar architecture allowing for extremely high memory densities while maintaining real-time performance characteristics. Their photonic interconnect technology provides ultra-low latency access to RRAM arrays. Weaknesses: The technology currently has higher manufacturing costs compared to conventional memory technologies, and the complex programming algorithms require additional controller overhead that may impact system simplicity.

Critical RRAM Performance Enhancement Technologies

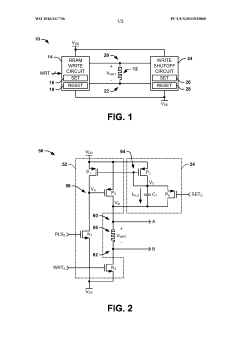

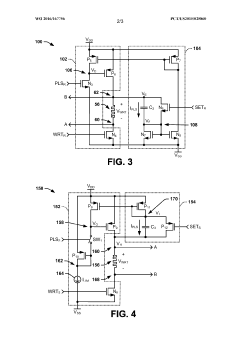

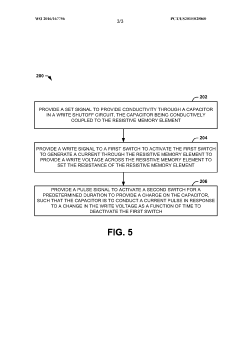

Resistive random access memory (RRAM) system

PatentWO2016167756A1

Innovation

- The RRAM system incorporates a write shutoff circuit that monitors the change in write voltage over time and immediately deactivates the write operation upon detecting a rapid change in resistance, using capacitors and switches to terminate the write stimulus efficiently.

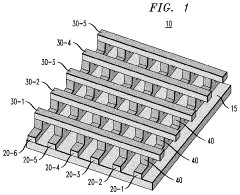

Resistive random-access memory array with reduced switching resistance variability

PatentInactiveUS10957742B2

Innovation

- The fabrication of RRAM memory cells with multiple parallel-connected resistive memory devices, where each cell comprises a group of RRAM devices sharing a common horizontal electrode layer, effectively averaging the switching resistances to minimize variability and noise.

Power Efficiency Considerations for RRAM in Real-Time Systems

Power consumption represents a critical factor in the deployment of RRAM (Resistive Random-Access Memory) within real-time systems, particularly for applications with strict energy constraints. RRAM inherently offers lower power consumption compared to traditional memory technologies like DRAM and flash memory, with static power requirements typically 10-100 times lower. However, significant optimization opportunities remain unexplored for real-time system implementations.

Dynamic power management techniques specifically tailored for RRAM can substantially improve energy efficiency. Adaptive voltage scaling methods that adjust operating voltage based on real-time system demands show promise, with research indicating potential energy savings of 30-45% without compromising performance reliability. These techniques must carefully balance power reduction against the need for consistent performance in time-critical applications.

Write operations in RRAM consume significantly more power than read operations, creating an opportunity for asymmetric optimization. Implementing write buffers and intelligent write scheduling algorithms can reduce peak power demands by distributing write operations across time windows when system resources are less constrained. Recent studies demonstrate that such approaches can reduce write-related power consumption by up to 40% while maintaining real-time guarantees.

Thermal management presents another crucial consideration, as RRAM power efficiency degrades under elevated temperatures. Implementing thermal-aware placement strategies and dynamic frequency scaling in response to temperature fluctuations can maintain optimal power efficiency. Experimental data suggests that proper thermal management can prevent up to 25% of power efficiency degradation that would otherwise occur under high-temperature conditions.

Multi-level cell (MLC) RRAM configurations offer increased storage density but introduce power efficiency challenges. While MLC designs can theoretically double or quadruple storage capacity within the same physical footprint, they typically require more precise (and power-hungry) read/write circuits. Hybrid approaches that selectively employ MLC configurations for less time-critical data while using single-level cells for performance-critical operations show promise for optimizing the power-performance tradeoff.

Standby power reduction techniques, including partial array power-gating and retention-aware refresh strategies, can significantly reduce energy consumption during idle periods without compromising data integrity or wake-up responsiveness. These approaches are particularly valuable for real-time systems with intermittent activity patterns, potentially reducing overall system energy consumption by 15-30% in typical usage scenarios.

Dynamic power management techniques specifically tailored for RRAM can substantially improve energy efficiency. Adaptive voltage scaling methods that adjust operating voltage based on real-time system demands show promise, with research indicating potential energy savings of 30-45% without compromising performance reliability. These techniques must carefully balance power reduction against the need for consistent performance in time-critical applications.

Write operations in RRAM consume significantly more power than read operations, creating an opportunity for asymmetric optimization. Implementing write buffers and intelligent write scheduling algorithms can reduce peak power demands by distributing write operations across time windows when system resources are less constrained. Recent studies demonstrate that such approaches can reduce write-related power consumption by up to 40% while maintaining real-time guarantees.

Thermal management presents another crucial consideration, as RRAM power efficiency degrades under elevated temperatures. Implementing thermal-aware placement strategies and dynamic frequency scaling in response to temperature fluctuations can maintain optimal power efficiency. Experimental data suggests that proper thermal management can prevent up to 25% of power efficiency degradation that would otherwise occur under high-temperature conditions.

Multi-level cell (MLC) RRAM configurations offer increased storage density but introduce power efficiency challenges. While MLC designs can theoretically double or quadruple storage capacity within the same physical footprint, they typically require more precise (and power-hungry) read/write circuits. Hybrid approaches that selectively employ MLC configurations for less time-critical data while using single-level cells for performance-critical operations show promise for optimizing the power-performance tradeoff.

Standby power reduction techniques, including partial array power-gating and retention-aware refresh strategies, can significantly reduce energy consumption during idle periods without compromising data integrity or wake-up responsiveness. These approaches are particularly valuable for real-time systems with intermittent activity patterns, potentially reducing overall system energy consumption by 15-30% in typical usage scenarios.

Reliability and Endurance Testing Methodologies

Reliability and endurance testing methodologies for RRAM devices in real-time systems require systematic approaches to ensure consistent performance under varying operational conditions. These methodologies can be categorized into accelerated lifetime testing, in-situ monitoring techniques, and statistical reliability modeling.

Accelerated lifetime testing involves subjecting RRAM cells to stress conditions exceeding normal operational parameters to induce early failures. This includes voltage stress tests where devices are operated at elevated voltages (typically 1.2-1.5x nominal voltage) while monitoring resistance changes. Temperature-accelerated testing, conducted at elevated temperatures (85-125°C), helps identify thermal degradation mechanisms. Pulse endurance testing, involving the application of millions to billions of programming cycles at accelerated rates, evaluates write endurance limitations.

In-situ monitoring techniques provide real-time assessment of RRAM reliability during operation. Resistance drift monitoring tracks gradual changes in high and low resistance states over time, offering early warning of potential device degradation. Current compliance monitoring ensures programming currents remain within specified limits to prevent premature breakdown. Error rate tracking systems continuously monitor bit error rates during read operations, enabling dynamic adjustment of error correction strategies.

Statistical reliability modeling employs mathematical frameworks to predict RRAM failure rates and lifetime. Weibull distribution analysis characterizes failure patterns across device populations, while Monte Carlo simulations model variability in device parameters. Mean Time Between Failures (MTBF) calculations provide quantitative reliability metrics essential for real-time system design.

Industry-standard test protocols have emerged to standardize reliability assessment. JEDEC JESD47 guidelines for stress-testing semiconductor devices have been adapted for RRAM evaluation. The JEDEC JESD22-A108 standard for temperature cycling tests helps assess thermal reliability. Custom test protocols specific to RRAM technology focus on resistance state stability and retention characteristics.

Environmental testing methodologies evaluate RRAM performance under extreme conditions relevant to real-time applications. These include humidity testing (85% RH, 85°C), mechanical shock and vibration testing, and radiation hardness testing particularly important for aerospace and military applications where single-event upsets must be mitigated.

The integration of these testing methodologies into automated test equipment (ATE) platforms enables high-throughput reliability screening during manufacturing, ensuring only devices meeting stringent reliability criteria are deployed in critical real-time systems.

Accelerated lifetime testing involves subjecting RRAM cells to stress conditions exceeding normal operational parameters to induce early failures. This includes voltage stress tests where devices are operated at elevated voltages (typically 1.2-1.5x nominal voltage) while monitoring resistance changes. Temperature-accelerated testing, conducted at elevated temperatures (85-125°C), helps identify thermal degradation mechanisms. Pulse endurance testing, involving the application of millions to billions of programming cycles at accelerated rates, evaluates write endurance limitations.

In-situ monitoring techniques provide real-time assessment of RRAM reliability during operation. Resistance drift monitoring tracks gradual changes in high and low resistance states over time, offering early warning of potential device degradation. Current compliance monitoring ensures programming currents remain within specified limits to prevent premature breakdown. Error rate tracking systems continuously monitor bit error rates during read operations, enabling dynamic adjustment of error correction strategies.

Statistical reliability modeling employs mathematical frameworks to predict RRAM failure rates and lifetime. Weibull distribution analysis characterizes failure patterns across device populations, while Monte Carlo simulations model variability in device parameters. Mean Time Between Failures (MTBF) calculations provide quantitative reliability metrics essential for real-time system design.

Industry-standard test protocols have emerged to standardize reliability assessment. JEDEC JESD47 guidelines for stress-testing semiconductor devices have been adapted for RRAM evaluation. The JEDEC JESD22-A108 standard for temperature cycling tests helps assess thermal reliability. Custom test protocols specific to RRAM technology focus on resistance state stability and retention characteristics.

Environmental testing methodologies evaluate RRAM performance under extreme conditions relevant to real-time applications. These include humidity testing (85% RH, 85°C), mechanical shock and vibration testing, and radiation hardness testing particularly important for aerospace and military applications where single-event upsets must be mitigated.

The integration of these testing methodologies into automated test equipment (ATE) platforms enables high-throughput reliability screening during manufacturing, ensuring only devices meeting stringent reliability criteria are deployed in critical real-time systems.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!