RRAM Evaluation in Integrated System Designs

SEP 10, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

RRAM Technology Evolution and Objectives

Resistive Random-Access Memory (RRAM) has emerged as a promising non-volatile memory technology over the past two decades, evolving from theoretical concepts to practical implementations in various integrated systems. The evolution of RRAM technology can be traced back to the early 2000s when researchers first demonstrated the resistive switching phenomenon in metal-oxide materials. Since then, significant advancements have been made in understanding the underlying mechanisms, improving device performance, and exploring potential applications.

The fundamental operating principle of RRAM relies on the formation and rupture of conductive filaments within a dielectric layer, allowing for reversible switching between high and low resistance states. This simple yet effective mechanism has positioned RRAM as a potential successor to conventional memory technologies such as NAND flash and DRAM, particularly in applications requiring high density, low power consumption, and non-volatility.

The technological trajectory of RRAM has been characterized by continuous improvements in several key performance metrics. Endurance capabilities have increased from early demonstrations of 10^5 cycles to recent achievements exceeding 10^12 cycles. Similarly, retention times have extended from hours to years, while switching speeds have improved from microseconds to nanoseconds. These advancements have been facilitated by innovations in materials science, device architecture, and fabrication techniques.

Material exploration has been a critical aspect of RRAM evolution, progressing from simple binary oxides like TiO2 and HfO2 to more complex compounds and heterostructures. Device architectures have also diversified, including crossbar arrays, 3D stacking, and hybrid configurations that combine RRAM with conventional CMOS technology. These developments have expanded the potential application space for RRAM beyond simple storage to include neuromorphic computing, in-memory processing, and security applications.

The primary objectives of current RRAM research and development efforts are multifaceted. From a performance perspective, researchers aim to further enhance endurance, reduce variability, and improve reliability under diverse operating conditions. From an integration standpoint, the focus is on developing scalable fabrication processes compatible with existing semiconductor manufacturing infrastructure and addressing challenges related to sneak path currents in high-density arrays.

Looking forward, the strategic goals for RRAM technology include establishing it as a viable solution for storage class memory, which bridges the performance gap between DRAM and NAND flash. Additionally, there is growing interest in leveraging RRAM's analog switching characteristics for neuromorphic computing applications, potentially enabling more efficient implementation of artificial neural networks. The ultimate objective is to position RRAM as a versatile memory technology that can be tailored to meet the diverse requirements of next-generation computing systems, from edge devices to data centers.

The fundamental operating principle of RRAM relies on the formation and rupture of conductive filaments within a dielectric layer, allowing for reversible switching between high and low resistance states. This simple yet effective mechanism has positioned RRAM as a potential successor to conventional memory technologies such as NAND flash and DRAM, particularly in applications requiring high density, low power consumption, and non-volatility.

The technological trajectory of RRAM has been characterized by continuous improvements in several key performance metrics. Endurance capabilities have increased from early demonstrations of 10^5 cycles to recent achievements exceeding 10^12 cycles. Similarly, retention times have extended from hours to years, while switching speeds have improved from microseconds to nanoseconds. These advancements have been facilitated by innovations in materials science, device architecture, and fabrication techniques.

Material exploration has been a critical aspect of RRAM evolution, progressing from simple binary oxides like TiO2 and HfO2 to more complex compounds and heterostructures. Device architectures have also diversified, including crossbar arrays, 3D stacking, and hybrid configurations that combine RRAM with conventional CMOS technology. These developments have expanded the potential application space for RRAM beyond simple storage to include neuromorphic computing, in-memory processing, and security applications.

The primary objectives of current RRAM research and development efforts are multifaceted. From a performance perspective, researchers aim to further enhance endurance, reduce variability, and improve reliability under diverse operating conditions. From an integration standpoint, the focus is on developing scalable fabrication processes compatible with existing semiconductor manufacturing infrastructure and addressing challenges related to sneak path currents in high-density arrays.

Looking forward, the strategic goals for RRAM technology include establishing it as a viable solution for storage class memory, which bridges the performance gap between DRAM and NAND flash. Additionally, there is growing interest in leveraging RRAM's analog switching characteristics for neuromorphic computing applications, potentially enabling more efficient implementation of artificial neural networks. The ultimate objective is to position RRAM as a versatile memory technology that can be tailored to meet the diverse requirements of next-generation computing systems, from edge devices to data centers.

Market Analysis for RRAM-Based Systems

The RRAM (Resistive Random Access Memory) market is experiencing significant growth as integrated system designs increasingly demand high-performance, energy-efficient memory solutions. Current market valuations place the global RRAM sector at approximately $310 million in 2023, with projections indicating a compound annual growth rate (CAGR) of 16.2% through 2030, potentially reaching $1.1 billion by the end of the decade.

The demand for RRAM-based systems is primarily driven by emerging applications in edge computing, Internet of Things (IoT), artificial intelligence, and neuromorphic computing. These sectors require memory solutions that can deliver high-density storage, low power consumption, and fast read/write speeds - characteristics that RRAM technology inherently provides.

In the consumer electronics segment, RRAM is gaining traction for mobile devices, wearables, and smart home systems where power efficiency and form factor are critical considerations. Market research indicates that this segment currently accounts for 38% of RRAM applications, with an expected increase to 45% by 2027 as miniaturization trends continue.

The enterprise computing sector represents another substantial market opportunity, with data centers increasingly exploring RRAM solutions to address the growing demands of big data processing and real-time analytics. This segment currently comprises 27% of the RRAM market, with particular interest in hybrid memory systems that leverage RRAM alongside traditional DRAM and NAND flash technologies.

Automotive and industrial applications are emerging as high-growth segments for RRAM technology, particularly for advanced driver-assistance systems (ADAS) and industrial automation. These applications benefit from RRAM's radiation hardness and temperature stability, with market share in these sectors expected to grow from 15% to 23% over the next five years.

Geographically, Asia-Pacific dominates the RRAM market with 52% share, followed by North America (28%) and Europe (16%). China and Taiwan are particularly significant manufacturing hubs, while research and development activities are concentrated in the United States, Japan, and South Korea.

Market challenges include competition from alternative emerging memory technologies such as MRAM, PCM, and FeRAM, as well as the established infrastructure supporting traditional memory solutions. Price sensitivity remains a barrier to widespread adoption, with current RRAM solutions commanding a premium of 30-40% over conventional alternatives, though this gap is expected to narrow as manufacturing scales.

The demand for RRAM-based systems is primarily driven by emerging applications in edge computing, Internet of Things (IoT), artificial intelligence, and neuromorphic computing. These sectors require memory solutions that can deliver high-density storage, low power consumption, and fast read/write speeds - characteristics that RRAM technology inherently provides.

In the consumer electronics segment, RRAM is gaining traction for mobile devices, wearables, and smart home systems where power efficiency and form factor are critical considerations. Market research indicates that this segment currently accounts for 38% of RRAM applications, with an expected increase to 45% by 2027 as miniaturization trends continue.

The enterprise computing sector represents another substantial market opportunity, with data centers increasingly exploring RRAM solutions to address the growing demands of big data processing and real-time analytics. This segment currently comprises 27% of the RRAM market, with particular interest in hybrid memory systems that leverage RRAM alongside traditional DRAM and NAND flash technologies.

Automotive and industrial applications are emerging as high-growth segments for RRAM technology, particularly for advanced driver-assistance systems (ADAS) and industrial automation. These applications benefit from RRAM's radiation hardness and temperature stability, with market share in these sectors expected to grow from 15% to 23% over the next five years.

Geographically, Asia-Pacific dominates the RRAM market with 52% share, followed by North America (28%) and Europe (16%). China and Taiwan are particularly significant manufacturing hubs, while research and development activities are concentrated in the United States, Japan, and South Korea.

Market challenges include competition from alternative emerging memory technologies such as MRAM, PCM, and FeRAM, as well as the established infrastructure supporting traditional memory solutions. Price sensitivity remains a barrier to widespread adoption, with current RRAM solutions commanding a premium of 30-40% over conventional alternatives, though this gap is expected to narrow as manufacturing scales.

RRAM Integration Challenges and Limitations

Despite the promising attributes of RRAM technology, significant integration challenges persist when implementing these devices into practical system designs. The non-linear switching behavior of RRAM cells presents a fundamental obstacle, as it introduces variability in resistance states that can compromise reliability in large-scale arrays. This variability manifests as cycle-to-cycle and device-to-device inconsistencies, making it difficult to establish stable read and write thresholds across an integrated memory system.

Material interface issues constitute another critical limitation, particularly at advanced technology nodes. The complex interaction between the switching layer and electrode materials can lead to undesired diffusion effects and degradation of the switching mechanism over time. These material compatibility challenges are exacerbated when RRAM cells are integrated with CMOS logic, as thermal budgets and process contamination concerns must be carefully managed.

Scaling limitations represent a significant barrier to RRAM adoption in high-density applications. While individual RRAM cells can theoretically scale to dimensions below 10nm, parasitic effects become increasingly dominant at these scales. Sneak path currents in crossbar arrays and increased resistance variability at smaller dimensions compromise the read margin and overall system performance. Additionally, the high programming currents required by many RRAM implementations create design constraints for peripheral circuitry.

The endurance characteristics of RRAM devices remain insufficient for certain applications, particularly those requiring frequent write operations. Current RRAM technologies typically demonstrate endurance in the range of 10^6 to 10^9 cycles, which falls short of DRAM and SRAM capabilities. This limitation restricts RRAM's applicability in write-intensive workloads and necessitates complex wear-leveling algorithms in integrated systems.

Power consumption during write operations presents another significant challenge. The high voltage requirements for reliable switching operations translate to substantial energy expenditure, particularly in dense arrays. This power constraint complicates the integration of RRAM into energy-efficient system designs and mobile applications where power budgets are strictly limited.

Retention characteristics under various operating conditions also pose integration difficulties. While RRAM offers non-volatility, the stability of resistance states can degrade under elevated temperatures or when subjected to read disturb effects. System designers must implement error correction mechanisms and refresh schemes to maintain data integrity, adding complexity to the overall architecture.

The lack of standardized design and fabrication methodologies further impedes widespread RRAM integration. Unlike established memory technologies with mature design ecosystems, RRAM implementation requires specialized expertise and custom design approaches. This absence of standardization increases development costs and extends time-to-market for RRAM-based systems.

Material interface issues constitute another critical limitation, particularly at advanced technology nodes. The complex interaction between the switching layer and electrode materials can lead to undesired diffusion effects and degradation of the switching mechanism over time. These material compatibility challenges are exacerbated when RRAM cells are integrated with CMOS logic, as thermal budgets and process contamination concerns must be carefully managed.

Scaling limitations represent a significant barrier to RRAM adoption in high-density applications. While individual RRAM cells can theoretically scale to dimensions below 10nm, parasitic effects become increasingly dominant at these scales. Sneak path currents in crossbar arrays and increased resistance variability at smaller dimensions compromise the read margin and overall system performance. Additionally, the high programming currents required by many RRAM implementations create design constraints for peripheral circuitry.

The endurance characteristics of RRAM devices remain insufficient for certain applications, particularly those requiring frequent write operations. Current RRAM technologies typically demonstrate endurance in the range of 10^6 to 10^9 cycles, which falls short of DRAM and SRAM capabilities. This limitation restricts RRAM's applicability in write-intensive workloads and necessitates complex wear-leveling algorithms in integrated systems.

Power consumption during write operations presents another significant challenge. The high voltage requirements for reliable switching operations translate to substantial energy expenditure, particularly in dense arrays. This power constraint complicates the integration of RRAM into energy-efficient system designs and mobile applications where power budgets are strictly limited.

Retention characteristics under various operating conditions also pose integration difficulties. While RRAM offers non-volatility, the stability of resistance states can degrade under elevated temperatures or when subjected to read disturb effects. System designers must implement error correction mechanisms and refresh schemes to maintain data integrity, adding complexity to the overall architecture.

The lack of standardized design and fabrication methodologies further impedes widespread RRAM integration. Unlike established memory technologies with mature design ecosystems, RRAM implementation requires specialized expertise and custom design approaches. This absence of standardization increases development costs and extends time-to-market for RRAM-based systems.

Current RRAM Integration Methodologies

01 Performance metrics and evaluation methods for RRAM

Various metrics and methods are used to evaluate RRAM performance, including endurance testing, retention time measurement, switching speed analysis, and power consumption assessment. These evaluations help determine the reliability and efficiency of RRAM devices under different operating conditions. Performance evaluation typically involves measuring parameters such as read/write speeds, data retention capabilities, and resistance ratio between high and low resistance states.- Performance metrics and evaluation methods for RRAM: Various metrics and methods are used to evaluate RRAM performance, including endurance testing, retention time measurement, switching speed analysis, and power consumption assessment. These evaluations help determine the reliability and efficiency of RRAM devices under different operating conditions. Performance evaluation typically involves measuring parameters such as read/write speeds, data retention capabilities, and resistance ratio between high and low resistance states.

- Material composition impact on RRAM performance: The choice of materials used in RRAM fabrication significantly affects device performance. Different metal oxides, electrode materials, and doping elements can enhance switching characteristics, improve endurance, and increase retention time. Material engineering approaches focus on optimizing the resistive switching layer composition to achieve better uniformity, stability, and reliability in RRAM devices.

- RRAM array architecture and performance optimization: The design and architecture of RRAM arrays significantly impact overall memory performance. Cross-point arrays, 3D stacking, and selector device integration are approaches used to enhance density and reduce interference between cells. Performance optimization techniques include addressing sneak path currents, implementing efficient sensing schemes, and developing novel array configurations that maximize read/write speeds while minimizing power consumption.

- Simulation and modeling techniques for RRAM performance prediction: Computational models and simulation techniques are employed to predict and analyze RRAM performance before physical fabrication. These include physics-based models that simulate resistive switching mechanisms, circuit-level simulations for array performance, and reliability models that predict device lifetime. Advanced modeling approaches incorporate machine learning algorithms to optimize device parameters and predict performance under various operating conditions.

- Novel testing methodologies and characterization techniques: Innovative testing methodologies have been developed specifically for RRAM performance evaluation, including pulse-based testing protocols, accelerated aging tests, and in-situ characterization techniques. These approaches enable comprehensive assessment of switching dynamics, variability analysis, and failure mode identification. Advanced characterization techniques utilize specialized equipment to analyze the physical and electrical properties of RRAM devices at the nanoscale level.

02 Material composition impact on RRAM performance

The choice of materials used in RRAM fabrication significantly affects device performance. Different oxide materials, electrode compositions, and interface engineering approaches can enhance switching characteristics, improve endurance, and increase retention time. Research focuses on optimizing material stacks to achieve better performance metrics while maintaining compatibility with existing semiconductor manufacturing processes.Expand Specific Solutions03 RRAM array architecture and circuit design

The architecture of RRAM arrays and associated circuit designs play crucial roles in overall memory performance. Cross-point arrays, 3D stacking configurations, and selector device integration affect parameters such as access speed, density, and power efficiency. Circuit designs for sensing, programming, and addressing impact read/write reliability and help mitigate issues like sneak path currents that can degrade performance in high-density arrays.Expand Specific Solutions04 Reliability and endurance enhancement techniques

Various techniques are employed to enhance RRAM reliability and endurance, including pulse engineering, adaptive programming schemes, and error correction methods. These approaches aim to mitigate issues such as resistance drift, variability between cells, and performance degradation over multiple switching cycles. Implementing proper verification algorithms and compensation techniques helps maintain consistent performance throughout the device lifetime.Expand Specific Solutions05 Integration and scaling challenges for RRAM technology

As RRAM technology scales down to smaller nodes, various challenges emerge that affect performance evaluation. These include process variation management, thermal stability concerns, and integration with CMOS technology. Evaluation methods must account for these scaling effects, particularly how they impact uniformity across large arrays, retention characteristics at elevated temperatures, and overall yield. Advanced characterization techniques help identify and address these integration challenges.Expand Specific Solutions

Leading RRAM Technology Companies and Research Institutions

The RRAM (Resistive Random Access Memory) evaluation in integrated system designs market is currently in a growth phase, with major semiconductor players actively developing this technology. The global RRAM market is projected to expand significantly due to its advantages in power efficiency and storage density. Leading companies like Intel, Samsung Electronics, and TSMC are investing heavily in RRAM research, while specialized firms such as CrossBar are focusing exclusively on RRAM innovations. Academic institutions including the Institute of Microelectronics of Chinese Academy of Sciences and The University of Hong Kong are contributing to technological advancements. The technology is approaching commercial maturity with companies like Micron Technology and IBM developing integration solutions for practical applications, though challenges in manufacturing consistency and long-term reliability remain to be fully resolved.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC has developed advanced RRAM integration solutions within their semiconductor manufacturing processes. Their approach focuses on embedding RRAM cells into their standard CMOS logic processes, particularly in their 28nm and 22nm technology nodes. TSMC's RRAM technology features a hafnium oxide-based resistive switching layer that demonstrates excellent endurance (>10^6 cycles) and retention (>10 years at 85°C)[1]. They've optimized the integration of RRAM with their backend-of-line (BEOL) processes, allowing for 3D stacking capabilities that increase memory density without expanding chip footprint. TSMC has also developed specialized peripheral circuitry to address the variability challenges in RRAM operation, implementing adaptive programming schemes that adjust pulse conditions based on cell characteristics[3]. Their technology roadmap includes scaling RRAM to sub-20nm nodes while maintaining reliability metrics.

Strengths: Industry-leading manufacturing capabilities allow for high-yield RRAM production; advanced process integration expertise enables seamless CMOS-RRAM integration. Weaknesses: Their solution requires specialized manufacturing equipment and processes that may increase production costs; RRAM technology still faces challenges in terms of cell-to-cell variability compared to conventional memory technologies.

Intel Corp.

Technical Solution: Intel has developed a sophisticated 3D XPoint™ technology (though technically not pure RRAM, it shares many characteristics) and has more recently been researching true RRAM solutions for next-generation memory hierarchies. Their approach focuses on integrating RRAM as an intermediate layer between DRAM and storage in their compute platforms. Intel's RRAM technology utilizes a metal-oxide switching layer with proprietary electrode materials that enable high endurance (>10^7 cycles) while maintaining data retention[7]. Their integration strategy leverages Intel's advanced packaging technologies, particularly Embedded Multi-die Interconnect Bridge (EMIB) and Foveros 3D stacking, to place RRAM dies in close proximity to processing cores, minimizing latency for data access. Intel has also developed specialized memory controllers and instruction set extensions that allow their processors to efficiently utilize RRAM's unique characteristics, such as byte-addressability combined with non-volatility[8].

Strengths: Vertical integration from memory technology to processor architecture allows for optimized system-level performance; extensive manufacturing capabilities enable rapid scaling once technology is mature. Weaknesses: Intel's primary focus on processor technology may limit resources dedicated to RRAM development; their solutions tend to be proprietary rather than industry-standard.

Key RRAM Patents and Technical Innovations

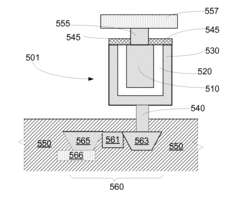

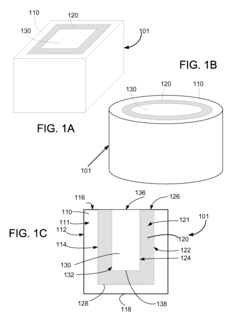

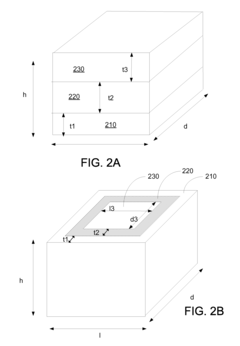

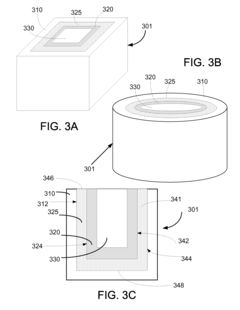

Structures for resistive random access memory cells

PatentActiveUS7791925B2

Innovation

- The RRAM cell design features a trench structure with a first electrode, a resistive layer, and a second electrode, where the resistive layer is nested inside the first electrode, and the second electrode is nested inside the resistive layer, increasing the contact area between the electrodes and the resistive layer, thereby enhancing the cell's functionality.

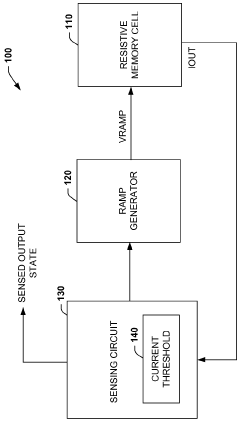

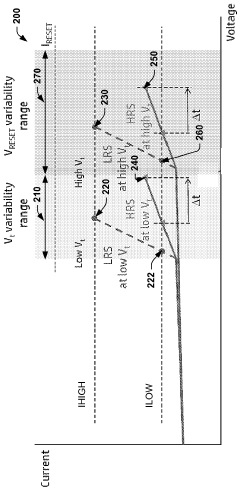

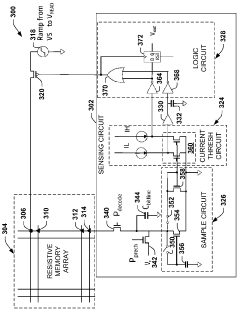

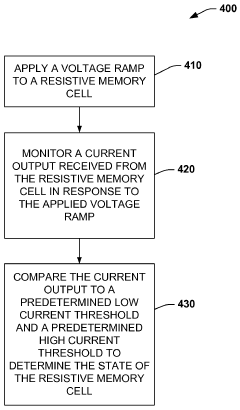

Sensing circuit for resistive memory

PatentWO2016068980A1

Innovation

- A sensing circuit that applies a varying read voltage at a predetermined rate, using a ramp signal to compare the output current relative to thresholds, allowing for the determination of memory cell states by measuring the time elapsed to reach current thresholds, thereby improving read margin and tolerance to process variations.

RRAM Reliability and Endurance Assessment

Reliability and endurance remain critical challenges for RRAM integration into commercial systems. Current RRAM devices typically demonstrate endurance capabilities ranging from 10^6 to 10^9 switching cycles, which falls short of the requirements for certain high-intensity applications such as cache memory that demands 10^12 to 10^15 cycles. This limitation stems primarily from the gradual degradation of the switching material during repeated SET and RESET operations.

The reliability assessment of RRAM devices involves comprehensive characterization across multiple parameters. Retention testing reveals that most RRAM technologies can maintain stored data for periods exceeding 10 years at temperatures up to 85°C, though this performance degrades significantly at higher temperatures. Variability in switching parameters represents another crucial reliability concern, with cycle-to-cycle and device-to-device variations affecting both the SET and RESET processes.

Environmental factors significantly impact RRAM reliability metrics. Temperature fluctuations can alter resistance states and switching thresholds, with elevated temperatures accelerating failure mechanisms. Radiation effects, particularly relevant for aerospace and nuclear applications, can induce temporary or permanent changes in resistance states through ionization events or displacement damage.

Advanced characterization techniques have been developed to assess RRAM reliability more accurately. Pulsed measurements enable precise evaluation of switching dynamics under conditions that mimic actual operation. Accelerated lifetime testing, conducted at elevated temperatures or voltages, helps predict long-term performance while reducing test duration. Statistical analysis methods have evolved to better quantify and model the inherent variability in RRAM performance.

Recent engineering approaches have yielded substantial improvements in RRAM reliability. Doping the switching material with select elements has demonstrated enhanced endurance by stabilizing the conductive filament formation. Optimized pulse schemes, including carefully controlled voltage ramps and verify operations, have reduced stress on the device during switching. Multi-layer structures incorporating buffer layers between the switching material and electrodes have shown promise in mitigating electrode degradation effects.

Standardized reliability assessment protocols are emerging within the industry, though consensus remains limited. The JEDEC JC-14.2 committee has proposed preliminary guidelines for non-volatile memory reliability testing that include RRAM-specific considerations. However, the diversity of RRAM materials and architectures necessitates customized reliability evaluation frameworks tailored to specific implementation contexts.

The reliability assessment of RRAM devices involves comprehensive characterization across multiple parameters. Retention testing reveals that most RRAM technologies can maintain stored data for periods exceeding 10 years at temperatures up to 85°C, though this performance degrades significantly at higher temperatures. Variability in switching parameters represents another crucial reliability concern, with cycle-to-cycle and device-to-device variations affecting both the SET and RESET processes.

Environmental factors significantly impact RRAM reliability metrics. Temperature fluctuations can alter resistance states and switching thresholds, with elevated temperatures accelerating failure mechanisms. Radiation effects, particularly relevant for aerospace and nuclear applications, can induce temporary or permanent changes in resistance states through ionization events or displacement damage.

Advanced characterization techniques have been developed to assess RRAM reliability more accurately. Pulsed measurements enable precise evaluation of switching dynamics under conditions that mimic actual operation. Accelerated lifetime testing, conducted at elevated temperatures or voltages, helps predict long-term performance while reducing test duration. Statistical analysis methods have evolved to better quantify and model the inherent variability in RRAM performance.

Recent engineering approaches have yielded substantial improvements in RRAM reliability. Doping the switching material with select elements has demonstrated enhanced endurance by stabilizing the conductive filament formation. Optimized pulse schemes, including carefully controlled voltage ramps and verify operations, have reduced stress on the device during switching. Multi-layer structures incorporating buffer layers between the switching material and electrodes have shown promise in mitigating electrode degradation effects.

Standardized reliability assessment protocols are emerging within the industry, though consensus remains limited. The JEDEC JC-14.2 committee has proposed preliminary guidelines for non-volatile memory reliability testing that include RRAM-specific considerations. However, the diversity of RRAM materials and architectures necessitates customized reliability evaluation frameworks tailored to specific implementation contexts.

Energy Efficiency Considerations for RRAM Systems

Energy efficiency has emerged as a critical factor in the evaluation and implementation of RRAM (Resistive Random Access Memory) systems within integrated designs. The non-volatile nature of RRAM offers inherent advantages in static power consumption, as it maintains stored data without requiring constant power refresh cycles that plague conventional DRAM technologies. This fundamental characteristic positions RRAM as a promising candidate for energy-efficient computing paradigms.

When evaluating RRAM from an energy perspective, the read and write operations present distinct energy profiles that must be carefully considered. Write operations typically consume significantly more energy than read operations, with programming currents ranging from microamperes to milliamperes depending on the specific RRAM technology. This asymmetry necessitates specialized circuit designs and access patterns to optimize overall system energy efficiency.

The switching mechanism of RRAM cells directly impacts energy consumption. Filamentary-based RRAM technologies exhibit different energy requirements compared to interface-type switching mechanisms. Recent advancements in material engineering have reduced the forming voltage requirements, thereby decreasing the initial energy investment needed to prepare RRAM cells for operation.

Peripheral circuitry surrounding RRAM arrays contributes substantially to the overall energy budget. Sense amplifiers, write drivers, and address decoders must be designed with energy efficiency as a primary consideration. The integration of low-power circuit techniques such as voltage scaling, power gating, and adaptive biasing has demonstrated energy reductions of 30-50% in recent RRAM implementations without compromising performance metrics.

System-level energy optimizations for RRAM include intelligent data mapping strategies that minimize write operations to frequently accessed memory locations. Wear-leveling algorithms, originally developed for flash memory, have been adapted for RRAM systems to distribute write operations evenly across the memory array, extending device lifetime while maintaining energy efficiency over the system lifespan.

The crossbar architecture commonly employed in RRAM arrays presents unique energy challenges related to sneak path currents. These parasitic current paths can significantly increase energy consumption during read operations. Selector devices integrated with memory elements in 1S1R (one selector, one resistor) configurations have proven effective in mitigating these issues, with recent selector technologies demonstrating sub-nanoampere leakage currents.

Temperature sensitivity represents another critical factor affecting RRAM energy efficiency. Operating temperature influences both the resistance states and switching characteristics of RRAM cells. Adaptive biasing schemes that adjust operating parameters based on temperature conditions have shown promise in maintaining consistent energy profiles across varying environmental conditions.

When evaluating RRAM from an energy perspective, the read and write operations present distinct energy profiles that must be carefully considered. Write operations typically consume significantly more energy than read operations, with programming currents ranging from microamperes to milliamperes depending on the specific RRAM technology. This asymmetry necessitates specialized circuit designs and access patterns to optimize overall system energy efficiency.

The switching mechanism of RRAM cells directly impacts energy consumption. Filamentary-based RRAM technologies exhibit different energy requirements compared to interface-type switching mechanisms. Recent advancements in material engineering have reduced the forming voltage requirements, thereby decreasing the initial energy investment needed to prepare RRAM cells for operation.

Peripheral circuitry surrounding RRAM arrays contributes substantially to the overall energy budget. Sense amplifiers, write drivers, and address decoders must be designed with energy efficiency as a primary consideration. The integration of low-power circuit techniques such as voltage scaling, power gating, and adaptive biasing has demonstrated energy reductions of 30-50% in recent RRAM implementations without compromising performance metrics.

System-level energy optimizations for RRAM include intelligent data mapping strategies that minimize write operations to frequently accessed memory locations. Wear-leveling algorithms, originally developed for flash memory, have been adapted for RRAM systems to distribute write operations evenly across the memory array, extending device lifetime while maintaining energy efficiency over the system lifespan.

The crossbar architecture commonly employed in RRAM arrays presents unique energy challenges related to sneak path currents. These parasitic current paths can significantly increase energy consumption during read operations. Selector devices integrated with memory elements in 1S1R (one selector, one resistor) configurations have proven effective in mitigating these issues, with recent selector technologies demonstrating sub-nanoampere leakage currents.

Temperature sensitivity represents another critical factor affecting RRAM energy efficiency. Operating temperature influences both the resistance states and switching characteristics of RRAM cells. Adaptive biasing schemes that adjust operating parameters based on temperature conditions have shown promise in maintaining consistent energy profiles across varying environmental conditions.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!