How to verify and debug neuromorphic hardware systems.

SEP 3, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Neuromorphic Hardware Verification Background and Objectives

Neuromorphic computing represents a paradigm shift in computational architecture, drawing inspiration from the structure and function of biological neural systems. This field has evolved significantly since the pioneering work of Carver Mead in the late 1980s, who first proposed the concept of using analog circuits to mimic neurobiological architectures. The trajectory of neuromorphic hardware development has accelerated dramatically in the past decade, driven by the limitations of traditional von Neumann architectures in handling complex cognitive tasks and the increasing demand for energy-efficient computing solutions.

The verification and debugging of neuromorphic hardware systems present unique challenges that distinguish them from conventional digital systems. Unlike traditional computing architectures with deterministic behavior, neuromorphic systems often incorporate stochastic elements, analog components, and massively parallel processing units that operate asynchronously. These characteristics necessitate specialized verification methodologies that can accommodate the inherent variability and complexity of brain-inspired computing.

Current technological trends in neuromorphic hardware verification include the development of multi-level testing frameworks that span from individual synaptic components to system-level functionality. The field is witnessing a convergence of verification techniques borrowed from mixed-signal circuit design, parallel computing, and machine learning validation approaches, adapted to address the specific requirements of neuromorphic architectures.

The primary objectives of neuromorphic hardware verification encompass ensuring functional correctness, performance optimization, and reliability assessment. Functional verification aims to confirm that the implemented neural networks behave as intended, accurately processing information and learning from data. Performance verification focuses on evaluating metrics such as energy efficiency, processing speed, and scalability. Reliability verification addresses the system's robustness against manufacturing variations, environmental factors, and degradation over time.

Looking forward, the evolution of neuromorphic hardware verification is expected to follow several key trajectories. These include the development of standardized benchmarks specifically designed for neuromorphic systems, automated verification tools that can handle the complexity of large-scale neural networks, and hybrid approaches that combine formal verification methods with simulation-based testing. Additionally, there is growing interest in creating verification methodologies that can assess the biological plausibility of neuromorphic implementations, ensuring they faithfully capture the essential computational principles of biological neural systems.

The ultimate goal of advancing neuromorphic hardware verification techniques is to enable the widespread adoption of these brain-inspired computing systems across various application domains, from edge computing and autonomous systems to scientific simulation and artificial intelligence.

The verification and debugging of neuromorphic hardware systems present unique challenges that distinguish them from conventional digital systems. Unlike traditional computing architectures with deterministic behavior, neuromorphic systems often incorporate stochastic elements, analog components, and massively parallel processing units that operate asynchronously. These characteristics necessitate specialized verification methodologies that can accommodate the inherent variability and complexity of brain-inspired computing.

Current technological trends in neuromorphic hardware verification include the development of multi-level testing frameworks that span from individual synaptic components to system-level functionality. The field is witnessing a convergence of verification techniques borrowed from mixed-signal circuit design, parallel computing, and machine learning validation approaches, adapted to address the specific requirements of neuromorphic architectures.

The primary objectives of neuromorphic hardware verification encompass ensuring functional correctness, performance optimization, and reliability assessment. Functional verification aims to confirm that the implemented neural networks behave as intended, accurately processing information and learning from data. Performance verification focuses on evaluating metrics such as energy efficiency, processing speed, and scalability. Reliability verification addresses the system's robustness against manufacturing variations, environmental factors, and degradation over time.

Looking forward, the evolution of neuromorphic hardware verification is expected to follow several key trajectories. These include the development of standardized benchmarks specifically designed for neuromorphic systems, automated verification tools that can handle the complexity of large-scale neural networks, and hybrid approaches that combine formal verification methods with simulation-based testing. Additionally, there is growing interest in creating verification methodologies that can assess the biological plausibility of neuromorphic implementations, ensuring they faithfully capture the essential computational principles of biological neural systems.

The ultimate goal of advancing neuromorphic hardware verification techniques is to enable the widespread adoption of these brain-inspired computing systems across various application domains, from edge computing and autonomous systems to scientific simulation and artificial intelligence.

Market Analysis for Neuromorphic Computing Systems

The neuromorphic computing market is experiencing significant growth, driven by increasing demand for AI applications and the limitations of traditional computing architectures. Current market valuations place the global neuromorphic computing sector at approximately $3.2 billion in 2023, with projections indicating a compound annual growth rate (CAGR) of 24.7% through 2030, potentially reaching $19.8 billion by the end of the decade.

The market demand for neuromorphic hardware systems stems primarily from five key sectors. First, autonomous vehicles require real-time processing capabilities with minimal power consumption, making neuromorphic systems particularly attractive. Second, healthcare applications, including brain-computer interfaces and medical imaging analysis, benefit from the pattern recognition capabilities inherent in neuromorphic designs.

Third, the IoT ecosystem represents a substantial market opportunity, with edge computing devices requiring energy-efficient processing solutions that neuromorphic systems can provide. Fourth, defense and aerospace industries are investing heavily in neuromorphic technologies for applications ranging from drone navigation to signal intelligence. Fifth, scientific research institutions continue to drive demand for specialized neuromorphic hardware for computational neuroscience and AI research.

Regional analysis reveals North America currently dominates the market with approximately 42% share, followed by Europe at 28% and Asia-Pacific at 24%. However, the Asia-Pacific region is expected to witness the fastest growth rate over the next five years due to increasing investments in AI technologies by countries like China, Japan, and South Korea.

Customer requirements analysis indicates three primary market needs driving neuromorphic hardware adoption: power efficiency (systems that consume 100-1000x less energy than conventional computing architectures), real-time processing capabilities (sub-millisecond response times for time-critical applications), and adaptive learning abilities (systems that can modify their behavior based on new inputs without complete reprogramming).

Market barriers include high development costs, lack of standardized verification and debugging tools, limited software ecosystem support, and competition from alternative computing paradigms such as quantum computing and specialized AI accelerators. The verification and debugging challenges specifically represent a significant market opportunity, as current solutions are largely proprietary and fragmented.

Industry surveys indicate that 78% of potential enterprise adopters cite verification and debugging limitations as a major concern when considering neuromorphic computing implementations. This highlights the critical need for advanced verification methodologies and debugging tools to accelerate market adoption and expand commercial applications beyond current niche deployments.

The market demand for neuromorphic hardware systems stems primarily from five key sectors. First, autonomous vehicles require real-time processing capabilities with minimal power consumption, making neuromorphic systems particularly attractive. Second, healthcare applications, including brain-computer interfaces and medical imaging analysis, benefit from the pattern recognition capabilities inherent in neuromorphic designs.

Third, the IoT ecosystem represents a substantial market opportunity, with edge computing devices requiring energy-efficient processing solutions that neuromorphic systems can provide. Fourth, defense and aerospace industries are investing heavily in neuromorphic technologies for applications ranging from drone navigation to signal intelligence. Fifth, scientific research institutions continue to drive demand for specialized neuromorphic hardware for computational neuroscience and AI research.

Regional analysis reveals North America currently dominates the market with approximately 42% share, followed by Europe at 28% and Asia-Pacific at 24%. However, the Asia-Pacific region is expected to witness the fastest growth rate over the next five years due to increasing investments in AI technologies by countries like China, Japan, and South Korea.

Customer requirements analysis indicates three primary market needs driving neuromorphic hardware adoption: power efficiency (systems that consume 100-1000x less energy than conventional computing architectures), real-time processing capabilities (sub-millisecond response times for time-critical applications), and adaptive learning abilities (systems that can modify their behavior based on new inputs without complete reprogramming).

Market barriers include high development costs, lack of standardized verification and debugging tools, limited software ecosystem support, and competition from alternative computing paradigms such as quantum computing and specialized AI accelerators. The verification and debugging challenges specifically represent a significant market opportunity, as current solutions are largely proprietary and fragmented.

Industry surveys indicate that 78% of potential enterprise adopters cite verification and debugging limitations as a major concern when considering neuromorphic computing implementations. This highlights the critical need for advanced verification methodologies and debugging tools to accelerate market adoption and expand commercial applications beyond current niche deployments.

Current Challenges in Neuromorphic Hardware Debugging

Neuromorphic hardware systems present unique verification and debugging challenges that differ significantly from traditional computing architectures. The fundamental complexity stems from their brain-inspired design principles, which incorporate massive parallelism, event-driven processing, and analog components that exhibit inherent variability. These characteristics make conventional debugging methodologies largely ineffective.

One primary challenge is the lack of standardized verification frameworks specifically designed for neuromorphic systems. While traditional hardware relies on established verification methodologies like Universal Verification Methodology (UVM), neuromorphic hardware operates on fundamentally different principles that require specialized approaches. The industry has yet to converge on standardized testing protocols that can adequately address the unique behaviors of spiking neural networks implemented in hardware.

The temporal dynamics of neuromorphic systems pose another significant obstacle. Unlike conventional synchronous digital systems, neuromorphic hardware often processes information through asynchronous spike events occurring across distributed networks. This temporal complexity makes it difficult to trace execution paths or reproduce specific behaviors consistently, as timing variations can significantly impact system functionality.

Observability presents a formidable challenge due to the massive scale and distributed nature of neuromorphic architectures. Modern neuromorphic chips may contain millions of neurons and billions of synapses, making comprehensive monitoring of internal states practically impossible without introducing significant overhead that alters the system's behavior. The limited number of I/O pins further restricts direct access to internal components.

The analog nature of many neuromorphic implementations introduces variability that complicates verification. Process variations, temperature fluctuations, and noise can cause unpredictable behaviors that are difficult to model accurately in simulation environments. This creates a significant gap between simulation results and actual hardware performance, making it challenging to identify whether discrepancies represent design flaws or expected variations.

Cross-layer debugging complexity arises from the interdependence between hardware, firmware, and software layers in neuromorphic systems. Issues may originate at any layer or from interactions between layers, requiring comprehensive debugging tools that can correlate events across the entire stack. Current tools typically specialize in either hardware or software debugging, lacking the integrated capabilities needed for neuromorphic systems.

The absence of mature debugging tools specifically designed for neuromorphic hardware represents perhaps the most pressing challenge. Existing tools lack the capability to visualize spiking activity, track information flow through complex neural networks, or identify anomalous behaviors in these non-deterministic systems. This tooling gap significantly impedes development cycles and limits the broader adoption of neuromorphic computing technologies.

One primary challenge is the lack of standardized verification frameworks specifically designed for neuromorphic systems. While traditional hardware relies on established verification methodologies like Universal Verification Methodology (UVM), neuromorphic hardware operates on fundamentally different principles that require specialized approaches. The industry has yet to converge on standardized testing protocols that can adequately address the unique behaviors of spiking neural networks implemented in hardware.

The temporal dynamics of neuromorphic systems pose another significant obstacle. Unlike conventional synchronous digital systems, neuromorphic hardware often processes information through asynchronous spike events occurring across distributed networks. This temporal complexity makes it difficult to trace execution paths or reproduce specific behaviors consistently, as timing variations can significantly impact system functionality.

Observability presents a formidable challenge due to the massive scale and distributed nature of neuromorphic architectures. Modern neuromorphic chips may contain millions of neurons and billions of synapses, making comprehensive monitoring of internal states practically impossible without introducing significant overhead that alters the system's behavior. The limited number of I/O pins further restricts direct access to internal components.

The analog nature of many neuromorphic implementations introduces variability that complicates verification. Process variations, temperature fluctuations, and noise can cause unpredictable behaviors that are difficult to model accurately in simulation environments. This creates a significant gap between simulation results and actual hardware performance, making it challenging to identify whether discrepancies represent design flaws or expected variations.

Cross-layer debugging complexity arises from the interdependence between hardware, firmware, and software layers in neuromorphic systems. Issues may originate at any layer or from interactions between layers, requiring comprehensive debugging tools that can correlate events across the entire stack. Current tools typically specialize in either hardware or software debugging, lacking the integrated capabilities needed for neuromorphic systems.

The absence of mature debugging tools specifically designed for neuromorphic hardware represents perhaps the most pressing challenge. Existing tools lack the capability to visualize spiking activity, track information flow through complex neural networks, or identify anomalous behaviors in these non-deterministic systems. This tooling gap significantly impedes development cycles and limits the broader adoption of neuromorphic computing technologies.

Existing Verification and Debugging Methodologies

01 Simulation-based verification for neuromorphic systems

Simulation-based approaches are used to verify neuromorphic hardware systems before physical implementation. These methods involve creating virtual models of the neuromorphic architecture to test functionality, performance, and identify potential issues. Advanced simulation techniques can emulate neural network behavior, test various input scenarios, and validate the system's response against expected outcomes, significantly reducing debugging time and development costs.- Simulation and emulation techniques for neuromorphic hardware: Simulation and emulation techniques are essential for verifying neuromorphic hardware systems before physical implementation. These techniques allow developers to model neural networks, test functionality, and identify potential issues in a controlled environment. Advanced simulation tools can emulate the behavior of neuromorphic circuits, providing insights into performance characteristics and helping to debug design flaws before fabrication.

- Hardware-specific debugging tools for neuromorphic systems: Specialized debugging tools designed specifically for neuromorphic hardware provide capabilities to monitor neural network operations, trace signal pathways, and identify anomalies in system behavior. These tools often include features for visualizing network activity, analyzing timing issues, and isolating faults in neuromorphic circuits. They enable developers to efficiently troubleshoot complex neuromorphic architectures and ensure proper functionality.

- Verification methodologies for neural network hardware: Comprehensive verification methodologies for neuromorphic systems involve systematic approaches to validate hardware implementations against design specifications. These methodologies include formal verification techniques, test pattern generation, and coverage analysis specifically adapted for neural network architectures. They ensure that neuromorphic hardware correctly implements intended algorithms and maintains accuracy across various operational conditions.

- Runtime monitoring and diagnostic systems: Runtime monitoring systems for neuromorphic hardware provide continuous observation of operational parameters and performance metrics during execution. These systems can detect anomalies, collect diagnostic information, and enable real-time debugging of neural network operations. Advanced implementations include self-diagnostic capabilities that can identify and potentially correct issues without interrupting system operation.

- Integration testing frameworks for neuromorphic systems: Integration testing frameworks enable verification of neuromorphic hardware components working together as a complete system. These frameworks facilitate testing of interfaces between neural processing units, memory systems, and conventional computing elements. They help identify integration issues such as timing problems, resource conflicts, and communication bottlenecks that might not be apparent when testing individual components in isolation.

02 Hardware-specific debugging tools for neuromorphic systems

Specialized debugging tools are developed specifically for neuromorphic hardware architectures. These tools provide capabilities to monitor neural spike activities, analyze synaptic weight changes, and trace signal propagation through the neuromorphic circuits. They often include visualization interfaces that represent complex neural activities in an interpretable format, allowing engineers to identify anomalies in the neuromorphic processing pipeline.Expand Specific Solutions03 Fault detection and diagnosis in neuromorphic hardware

Methods for detecting and diagnosing faults in neuromorphic computing systems involve monitoring circuit behavior, identifying anomalies, and localizing defects. These approaches use techniques such as built-in self-test mechanisms, error detection codes, and comparative analysis between expected and actual outputs. Advanced fault diagnosis systems can differentiate between permanent hardware failures and temporary computational errors, enabling appropriate remediation strategies.Expand Specific Solutions04 Verification methodologies for neural network hardware implementations

Comprehensive verification methodologies are developed specifically for neural network hardware implementations. These methodologies include formal verification techniques, coverage-driven verification, and assertion-based verification to ensure the correctness of the neuromorphic hardware. They typically involve creating test scenarios that exercise various operational modes of the neural network hardware, verifying both functional correctness and performance requirements.Expand Specific Solutions05 Runtime monitoring and adaptive debugging for neuromorphic systems

Runtime monitoring systems provide continuous observation of neuromorphic hardware during operation, enabling real-time debugging capabilities. These systems collect performance metrics, detect anomalous behavior, and can trigger adaptive responses to maintain system integrity. Advanced implementations include self-correction mechanisms that can reconfigure neural pathways or adjust parameters to compensate for detected issues, ensuring robust operation even in the presence of hardware variations or degradation.Expand Specific Solutions

Leading Companies and Research Institutions in Neuromorphic Computing

The neuromorphic hardware verification and debugging market is in an early growth phase, characterized by increasing adoption but still evolving technical standards. Market size is expanding as neuromorphic computing gains traction in AI applications, with projections showing significant growth potential. Regarding technical maturity, industry leaders like IBM, Intel, and Samsung are advancing verification methodologies, while specialized players such as Cadence Design Systems and Synopsys are developing dedicated tools. Academic institutions including Tianjin University and NAIST are contributing fundamental research. Companies like ARM and Imagination Technologies are focusing on hardware-software co-verification approaches, while GlobalFoundries and Socionext are addressing manufacturing verification challenges. The ecosystem remains fragmented with diverse approaches to neuromorphic system validation.

International Business Machines Corp.

Technical Solution: IBM has developed comprehensive verification and debugging frameworks for their TrueNorth and subsequent neuromorphic systems. Their approach combines hardware-specific test benches with specialized software tools that enable real-time monitoring of spiking neural networks. IBM's verification methodology includes a multi-level testing strategy: from individual neuron behavior validation to full-system functional verification. They employ Hardware Description Language (HDL) simulations alongside custom-built verification environments that can inject controlled spike patterns and analyze responses. For debugging, IBM has created specialized probe points within their neuromorphic architecture that allow non-intrusive monitoring of internal states without disrupting normal operation[1]. Their Compass simulator provides a software environment that can accurately model hardware behavior, enabling pre-silicon verification and post-silicon validation through comparative analysis[3]. IBM also utilizes formal verification methods to mathematically prove the correctness of critical neuromorphic components before physical implementation.

Strengths: IBM's approach offers comprehensive coverage from component to system level with strong mathematical foundations. Their tools provide excellent visibility into internal states without performance degradation. Weaknesses: The verification infrastructure requires significant computational resources and specialized expertise. The debugging tools are highly customized to IBM's specific neuromorphic architecture, limiting transferability to other platforms.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has developed a neuromorphic verification framework that integrates hardware-in-the-loop testing with advanced simulation environments. Their approach focuses on bridging the gap between conventional CMOS verification methodologies and the unique challenges of neuromorphic systems. Samsung's verification strategy employs a hierarchical methodology starting with unit-level verification of neuromorphic building blocks (neurons, synapses) and progressing to system-level validation. They have created specialized test vectors that can exercise the stochastic and temporal aspects of neuromorphic computation. For debugging, Samsung has implemented a hybrid approach combining traditional logic analyzers with custom-built spike monitoring tools that can capture and visualize neural activity across their hardware[2]. Their platform includes fault injection capabilities to test resilience and error recovery mechanisms specific to neuromorphic architectures. Samsung has also developed power analysis tools that can correlate neural activity with energy consumption patterns, enabling optimization of neuromorphic designs for mobile and edge applications[4].

Strengths: Samsung's verification approach effectively leverages their extensive semiconductor manufacturing expertise while addressing neuromorphic-specific challenges. Their tools excel at power/performance analysis crucial for commercial deployment. Weaknesses: Their methodology is heavily oriented toward manufacturing yield and reliability testing rather than algorithmic correctness. The debugging infrastructure has limited support for temporal analysis of complex spike timing-dependent behaviors.

Key Innovations in Neuromorphic Testing Technologies

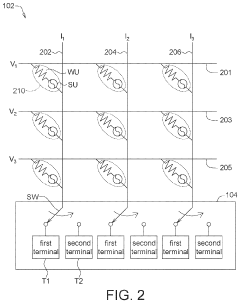

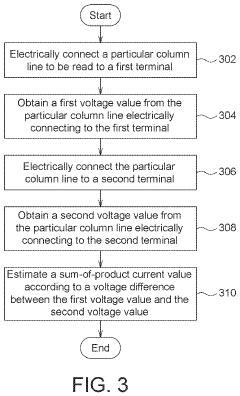

Neuromorphic computing system and current estimation method using the same

PatentActiveUS11062197B2

Innovation

- Each output channel of the synapse array is electrically connected to a first terminal or a second terminal in a switchable manner, allowing only limited or no current to flow, with the sum-of-product current estimated based on the voltage difference between these terminals, reducing energy dissipation.

Systems and methods for detonation control in spark ignition engines using analog neuromorphic computing hardware

PatentActiveUS11885271B2

Innovation

- Analog neuromorphic circuits that model trained neural networks, using operational amplifiers and resistors, allowing for low power consumption, improved parallelism, and noise resilience, enabling efficient hardware realization of neural networks for edge applications.

Standardization Efforts in Neuromorphic System Testing

The standardization of testing methodologies for neuromorphic hardware systems has emerged as a critical need in the rapidly evolving field of brain-inspired computing. Currently, the neuromorphic hardware ecosystem suffers from fragmentation in testing approaches, making it difficult to compare performance across different platforms and validate system functionality against design specifications.

Several international organizations have begun addressing this challenge through collaborative standardization efforts. The IEEE Neuromorphic Computing Standards Working Group, established in 2018, has been developing a comprehensive framework for benchmarking neuromorphic systems, focusing on metrics that capture both computational efficiency and biological fidelity. Their P2788 standard specifically addresses test methodologies for spike-based neuromorphic systems, providing guidelines for measuring power consumption, processing speed, and learning capabilities.

In parallel, the International Neuromorphic Systems Testing Consortium (INSTC) has been working to establish reference datasets and validation protocols specifically designed for neuromorphic hardware. These datasets include standardized spike patterns derived from biological recordings, synthetic test cases with known solutions, and application-specific benchmarks that evaluate performance on real-world tasks such as pattern recognition and anomaly detection.

The European Neuromorphic Computing Initiative (ENCI) has contributed significantly by developing the Neuromorphic Hardware Verification Framework (NHVF), which provides a unified approach to functional verification. This framework includes formal verification methods adapted for neuromorphic architectures, simulation-based testing protocols, and hardware-in-the-loop validation techniques that can identify discrepancies between theoretical models and physical implementations.

Industry leaders including IBM, Intel, and BrainChip have also joined forces to establish the Neuromorphic Industry Testing Alliance (NITA), which focuses on practical aspects of system verification. NITA has published testing guidelines that address manufacturing variability, reliability under different operating conditions, and integration testing for neuromorphic components within larger computing systems.

Academic institutions have contributed to standardization through open-source testing platforms like NeuroBench and SpikeVerify, which provide reproducible testing environments and automated verification tools. These platforms implement many of the emerging standards and allow researchers to validate their hardware designs against community-accepted benchmarks.

Despite this progress, significant challenges remain in standardizing neuromorphic testing. The diversity of neuromorphic architectures—ranging from digital CMOS implementations to analog, memristive, and photonic systems—requires flexible testing frameworks that can accommodate fundamentally different computing paradigms while still enabling meaningful comparisons.

Several international organizations have begun addressing this challenge through collaborative standardization efforts. The IEEE Neuromorphic Computing Standards Working Group, established in 2018, has been developing a comprehensive framework for benchmarking neuromorphic systems, focusing on metrics that capture both computational efficiency and biological fidelity. Their P2788 standard specifically addresses test methodologies for spike-based neuromorphic systems, providing guidelines for measuring power consumption, processing speed, and learning capabilities.

In parallel, the International Neuromorphic Systems Testing Consortium (INSTC) has been working to establish reference datasets and validation protocols specifically designed for neuromorphic hardware. These datasets include standardized spike patterns derived from biological recordings, synthetic test cases with known solutions, and application-specific benchmarks that evaluate performance on real-world tasks such as pattern recognition and anomaly detection.

The European Neuromorphic Computing Initiative (ENCI) has contributed significantly by developing the Neuromorphic Hardware Verification Framework (NHVF), which provides a unified approach to functional verification. This framework includes formal verification methods adapted for neuromorphic architectures, simulation-based testing protocols, and hardware-in-the-loop validation techniques that can identify discrepancies between theoretical models and physical implementations.

Industry leaders including IBM, Intel, and BrainChip have also joined forces to establish the Neuromorphic Industry Testing Alliance (NITA), which focuses on practical aspects of system verification. NITA has published testing guidelines that address manufacturing variability, reliability under different operating conditions, and integration testing for neuromorphic components within larger computing systems.

Academic institutions have contributed to standardization through open-source testing platforms like NeuroBench and SpikeVerify, which provide reproducible testing environments and automated verification tools. These platforms implement many of the emerging standards and allow researchers to validate their hardware designs against community-accepted benchmarks.

Despite this progress, significant challenges remain in standardizing neuromorphic testing. The diversity of neuromorphic architectures—ranging from digital CMOS implementations to analog, memristive, and photonic systems—requires flexible testing frameworks that can accommodate fundamentally different computing paradigms while still enabling meaningful comparisons.

Performance Metrics and Benchmarking Frameworks

Evaluating neuromorphic hardware systems requires specialized performance metrics and benchmarking frameworks that differ significantly from traditional computing architectures. These systems, which mimic neural structures of the brain, demand evaluation approaches that can capture their unique characteristics such as spike-based processing, event-driven computation, and temporal dynamics.

Standard metrics for neuromorphic hardware include energy efficiency (typically measured in joules per synaptic operation), throughput (operations per second), latency (response time for spike propagation), and area efficiency (computational density). More specialized metrics focus on spike timing precision, dynamic range of neural responses, and noise tolerance—all critical for brain-inspired computing systems.

The SNN (Spiking Neural Network) community has developed several benchmarking suites specifically designed for neuromorphic hardware. Notable examples include N-MNIST and NTIDIGITS for spike-based pattern recognition, and more complex benchmarks like Spiking HeartNet for biomedical applications. These benchmarks provide standardized workloads that enable fair comparison across different neuromorphic implementations.

Hardware-in-the-loop testing frameworks have emerged as essential tools for neuromorphic verification. These frameworks integrate real-time data acquisition with neuromorphic processing elements, allowing engineers to validate system behavior under realistic operating conditions. Examples include the Neurorobotics Platform and SpiNNaker software stack, which provide comprehensive environments for testing neuromorphic systems in closed-loop scenarios.

Cross-platform benchmarking presents significant challenges due to the heterogeneous nature of neuromorphic architectures. Efforts like the Neuromorphic Benchmarking Initiative aim to establish platform-independent metrics that facilitate meaningful comparisons between diverse implementations such as IBM's TrueNorth, Intel's Loihi, and BrainScaleS systems.

Emerging trends in neuromorphic benchmarking include the development of application-specific metrics that evaluate performance on real-world tasks rather than abstract computational capabilities. Additionally, there is growing interest in benchmarks that assess learning capabilities, adaptability, and fault tolerance—properties that are inherent to biological neural systems but challenging to quantify in hardware implementations.

The neuromorphic research community continues to work toward standardization of these metrics and frameworks, recognizing that robust verification methodologies are essential for the maturation and commercial adoption of neuromorphic computing technologies.

Standard metrics for neuromorphic hardware include energy efficiency (typically measured in joules per synaptic operation), throughput (operations per second), latency (response time for spike propagation), and area efficiency (computational density). More specialized metrics focus on spike timing precision, dynamic range of neural responses, and noise tolerance—all critical for brain-inspired computing systems.

The SNN (Spiking Neural Network) community has developed several benchmarking suites specifically designed for neuromorphic hardware. Notable examples include N-MNIST and NTIDIGITS for spike-based pattern recognition, and more complex benchmarks like Spiking HeartNet for biomedical applications. These benchmarks provide standardized workloads that enable fair comparison across different neuromorphic implementations.

Hardware-in-the-loop testing frameworks have emerged as essential tools for neuromorphic verification. These frameworks integrate real-time data acquisition with neuromorphic processing elements, allowing engineers to validate system behavior under realistic operating conditions. Examples include the Neurorobotics Platform and SpiNNaker software stack, which provide comprehensive environments for testing neuromorphic systems in closed-loop scenarios.

Cross-platform benchmarking presents significant challenges due to the heterogeneous nature of neuromorphic architectures. Efforts like the Neuromorphic Benchmarking Initiative aim to establish platform-independent metrics that facilitate meaningful comparisons between diverse implementations such as IBM's TrueNorth, Intel's Loihi, and BrainScaleS systems.

Emerging trends in neuromorphic benchmarking include the development of application-specific metrics that evaluate performance on real-world tasks rather than abstract computational capabilities. Additionally, there is growing interest in benchmarks that assess learning capabilities, adaptability, and fault tolerance—properties that are inherent to biological neural systems but challenging to quantify in hardware implementations.

The neuromorphic research community continues to work toward standardization of these metrics and frameworks, recognizing that robust verification methodologies are essential for the maturation and commercial adoption of neuromorphic computing technologies.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!