Optimize DDR5 for High-Density Data Storage Solutions

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

DDR5 Evolution and Performance Objectives

DDR5 memory technology represents a significant evolution in the DRAM landscape, building upon the foundations established by previous generations while introducing substantial architectural improvements. Since its introduction in 2020, DDR5 has marked a pivotal shift in memory performance capabilities, offering initial data rates of 4800 MT/s compared to DDR4's typical 3200 MT/s. This generational leap addresses the growing demands of data-intensive applications, particularly in high-density storage environments where memory bandwidth and capacity constraints have become increasingly problematic.

The evolutionary trajectory of DDR5 technology has been characterized by several key advancements. The transition from a 16-bit to a 32-bit channel architecture has effectively doubled the burst length, enabling more efficient data transfers without proportionally increasing clock speeds. Additionally, the implementation of on-die ECC (Error Correction Code) represents a fundamental architectural shift, moving error detection and correction capabilities directly onto the memory die rather than relying on the memory controller.

Power management has seen significant refinement in DDR5, with the voltage regulator module (VRM) moving from the motherboard to the memory module itself. This transition to on-module power management enables more precise voltage control and reduced power consumption, with operating voltages decreasing from DDR4's 1.2V to DDR5's 1.1V, despite the increased performance envelope.

For high-density data storage solutions, DDR5's performance objectives are multifaceted. Primary among these is achieving substantially higher memory densities, with single modules now capable of reaching 128GB compared to DDR4's typical maximum of 32GB. This density increase is critical for data-intensive applications where memory capacity directly impacts system capability and performance.

Bandwidth enhancement represents another crucial objective, with DDR5 targeting effective data rates exceeding 8400 MT/s in its mature implementations. This bandwidth expansion is essential for high-throughput storage applications where data movement between memory and processing units often creates bottlenecks in overall system performance.

Reliability improvements constitute a third key objective, particularly relevant in enterprise storage environments where data integrity is paramount. The introduction of on-die ECC, combined with enhanced refresh mechanisms and improved thermal management, aims to reduce error rates while extending operational lifespan under intensive workloads.

Looking forward, the DDR5 roadmap projects continued scaling of both performance and density metrics, with anticipated data rates potentially reaching 10,000 MT/s and module densities exceeding 256GB. These projections align with the exponential growth in data storage requirements across enterprise, cloud, and edge computing environments, positioning DDR5 as a critical enabling technology for next-generation storage architectures.

The evolutionary trajectory of DDR5 technology has been characterized by several key advancements. The transition from a 16-bit to a 32-bit channel architecture has effectively doubled the burst length, enabling more efficient data transfers without proportionally increasing clock speeds. Additionally, the implementation of on-die ECC (Error Correction Code) represents a fundamental architectural shift, moving error detection and correction capabilities directly onto the memory die rather than relying on the memory controller.

Power management has seen significant refinement in DDR5, with the voltage regulator module (VRM) moving from the motherboard to the memory module itself. This transition to on-module power management enables more precise voltage control and reduced power consumption, with operating voltages decreasing from DDR4's 1.2V to DDR5's 1.1V, despite the increased performance envelope.

For high-density data storage solutions, DDR5's performance objectives are multifaceted. Primary among these is achieving substantially higher memory densities, with single modules now capable of reaching 128GB compared to DDR4's typical maximum of 32GB. This density increase is critical for data-intensive applications where memory capacity directly impacts system capability and performance.

Bandwidth enhancement represents another crucial objective, with DDR5 targeting effective data rates exceeding 8400 MT/s in its mature implementations. This bandwidth expansion is essential for high-throughput storage applications where data movement between memory and processing units often creates bottlenecks in overall system performance.

Reliability improvements constitute a third key objective, particularly relevant in enterprise storage environments where data integrity is paramount. The introduction of on-die ECC, combined with enhanced refresh mechanisms and improved thermal management, aims to reduce error rates while extending operational lifespan under intensive workloads.

Looking forward, the DDR5 roadmap projects continued scaling of both performance and density metrics, with anticipated data rates potentially reaching 10,000 MT/s and module densities exceeding 256GB. These projections align with the exponential growth in data storage requirements across enterprise, cloud, and edge computing environments, positioning DDR5 as a critical enabling technology for next-generation storage architectures.

Market Demand Analysis for High-Density Storage

The global demand for high-density data storage solutions has experienced unprecedented growth in recent years, primarily driven by the exponential increase in data generation across various sectors. Enterprise data centers, cloud service providers, and hyperscale facilities are facing mounting pressure to store and process massive volumes of data while maintaining operational efficiency and cost-effectiveness. According to industry reports, the global data storage market is projected to reach $390 billion by 2028, with high-density solutions representing the fastest-growing segment.

The proliferation of data-intensive applications such as artificial intelligence, machine learning, big data analytics, and IoT has significantly accelerated storage requirements. These applications not only demand greater storage capacity but also require faster data access and processing capabilities. The average enterprise now manages 347% more data than five years ago, highlighting the critical need for advanced storage technologies that can accommodate this explosive growth while optimizing physical space utilization.

DDR5 memory technology has emerged as a pivotal component in addressing these high-density storage challenges. The market for DDR5-enabled storage solutions is expected to grow at a compound annual growth rate of 32% through 2027, reflecting strong industry adoption. This growth is particularly pronounced in sectors handling time-sensitive workloads where the enhanced bandwidth and reduced latency of DDR5 provide significant competitive advantages.

Financial services, healthcare, and media production industries demonstrate especially strong demand for high-density storage incorporating optimized DDR5 technology. These sectors require solutions that can process large datasets in real-time while maintaining data integrity and security. The healthcare sector alone has seen a 63% increase in storage requirements annually, driven by advances in medical imaging, genomic sequencing, and electronic health records.

Geographically, North America currently leads the market for high-density storage solutions, accounting for approximately 42% of global demand. However, the Asia-Pacific region is experiencing the fastest growth rate at 37% annually, fueled by rapid digital transformation initiatives across emerging economies and substantial investments in data center infrastructure.

Energy efficiency has become a critical factor influencing market demand, with data centers now consuming over 2% of global electricity. Solutions that can deliver higher storage density while reducing power consumption per terabyte stored are gaining significant market traction. The industry is increasingly prioritizing technologies that can demonstrate measurable improvements in performance-per-watt metrics, with DDR5 optimization representing a key enabler for achieving these efficiency goals.

The proliferation of data-intensive applications such as artificial intelligence, machine learning, big data analytics, and IoT has significantly accelerated storage requirements. These applications not only demand greater storage capacity but also require faster data access and processing capabilities. The average enterprise now manages 347% more data than five years ago, highlighting the critical need for advanced storage technologies that can accommodate this explosive growth while optimizing physical space utilization.

DDR5 memory technology has emerged as a pivotal component in addressing these high-density storage challenges. The market for DDR5-enabled storage solutions is expected to grow at a compound annual growth rate of 32% through 2027, reflecting strong industry adoption. This growth is particularly pronounced in sectors handling time-sensitive workloads where the enhanced bandwidth and reduced latency of DDR5 provide significant competitive advantages.

Financial services, healthcare, and media production industries demonstrate especially strong demand for high-density storage incorporating optimized DDR5 technology. These sectors require solutions that can process large datasets in real-time while maintaining data integrity and security. The healthcare sector alone has seen a 63% increase in storage requirements annually, driven by advances in medical imaging, genomic sequencing, and electronic health records.

Geographically, North America currently leads the market for high-density storage solutions, accounting for approximately 42% of global demand. However, the Asia-Pacific region is experiencing the fastest growth rate at 37% annually, fueled by rapid digital transformation initiatives across emerging economies and substantial investments in data center infrastructure.

Energy efficiency has become a critical factor influencing market demand, with data centers now consuming over 2% of global electricity. Solutions that can deliver higher storage density while reducing power consumption per terabyte stored are gaining significant market traction. The industry is increasingly prioritizing technologies that can demonstrate measurable improvements in performance-per-watt metrics, with DDR5 optimization representing a key enabler for achieving these efficiency goals.

DDR5 Technical Challenges and Limitations

Despite the significant advancements in DDR5 technology, several technical challenges and limitations persist when optimizing it for high-density data storage solutions. The increased operating frequency of DDR5 (4800-6400 MHz) introduces signal integrity issues that become more pronounced in high-density implementations. As trace lengths increase to accommodate more memory modules, maintaining signal quality becomes exponentially more difficult, requiring sophisticated signal conditioning techniques and more complex PCB designs.

Power management represents another significant challenge. While DDR5 incorporates improved power architecture with on-module voltage regulation, the increased module density creates thermal hotspots that can compromise reliability. The power consumption per bit has improved, but the overall system power requirements have increased due to higher capacities and frequencies, necessitating more robust cooling solutions for high-density deployments.

Timing and latency issues present persistent obstacles. Although DDR5 offers higher bandwidth, its absolute latency has not improved proportionally. In high-density configurations, the increased number of ranks and banks introduces additional complexity in memory addressing and scheduling, potentially creating performance bottlenecks for latency-sensitive applications despite the higher theoretical bandwidth.

Physical space constraints become critical when optimizing for density. The DIMM form factor limitations restrict how many memory chips can be placed on a single module. While technologies like TSV (Through-Silicon Via) and 3D stacking offer potential solutions, they introduce manufacturing complexities, yield challenges, and thermal management issues that must be addressed.

Data integrity becomes increasingly challenging at higher densities. The error rate increases with capacity and speed, requiring more sophisticated ECC implementations. DDR5's on-die ECC helps mitigate this issue, but system-level ECC overhead increases with capacity, consuming additional bandwidth and potentially offsetting some performance gains.

Cost considerations remain a significant limitation. The price premium for DDR5 is substantial, particularly for high-density configurations. The economics of scaling to very high densities face diminishing returns, as manufacturing complexity, testing requirements, and yield issues compound with increased capacity.

Compatibility with existing systems presents another challenge. While DDR5 offers backward compatibility through controller design, fully leveraging its capabilities in high-density configurations often requires architectural changes to memory controllers, system buses, and thermal management systems, creating adoption barriers for organizations with established infrastructure.

Power management represents another significant challenge. While DDR5 incorporates improved power architecture with on-module voltage regulation, the increased module density creates thermal hotspots that can compromise reliability. The power consumption per bit has improved, but the overall system power requirements have increased due to higher capacities and frequencies, necessitating more robust cooling solutions for high-density deployments.

Timing and latency issues present persistent obstacles. Although DDR5 offers higher bandwidth, its absolute latency has not improved proportionally. In high-density configurations, the increased number of ranks and banks introduces additional complexity in memory addressing and scheduling, potentially creating performance bottlenecks for latency-sensitive applications despite the higher theoretical bandwidth.

Physical space constraints become critical when optimizing for density. The DIMM form factor limitations restrict how many memory chips can be placed on a single module. While technologies like TSV (Through-Silicon Via) and 3D stacking offer potential solutions, they introduce manufacturing complexities, yield challenges, and thermal management issues that must be addressed.

Data integrity becomes increasingly challenging at higher densities. The error rate increases with capacity and speed, requiring more sophisticated ECC implementations. DDR5's on-die ECC helps mitigate this issue, but system-level ECC overhead increases with capacity, consuming additional bandwidth and potentially offsetting some performance gains.

Cost considerations remain a significant limitation. The price premium for DDR5 is substantial, particularly for high-density configurations. The economics of scaling to very high densities face diminishing returns, as manufacturing complexity, testing requirements, and yield issues compound with increased capacity.

Compatibility with existing systems presents another challenge. While DDR5 offers backward compatibility through controller design, fully leveraging its capabilities in high-density configurations often requires architectural changes to memory controllers, system buses, and thermal management systems, creating adoption barriers for organizations with established infrastructure.

Current DDR5 Optimization Approaches

01 Memory controller optimization for DDR5

Advanced memory controllers specifically designed for DDR5 memory can significantly improve performance and efficiency. These controllers implement optimized timing parameters, enhanced command scheduling, and intelligent power management features to maximize DDR5 capabilities. The controllers can dynamically adjust operating parameters based on workload characteristics and system conditions, resulting in improved throughput and reduced latency.- Memory controller optimization for DDR5: Advanced memory controllers specifically designed for DDR5 memory can significantly improve performance and efficiency. These controllers implement optimized timing parameters, enhanced command scheduling, and intelligent power management features to maximize DDR5 capabilities. The controllers can dynamically adjust memory operations based on workload characteristics, reducing latency and increasing throughput while maintaining power efficiency.

- Thermal management solutions for DDR5: DDR5 memory operates at higher frequencies and voltages than previous generations, resulting in increased heat generation. Specialized thermal management solutions include improved heat spreaders, integrated temperature sensors, and adaptive cooling mechanisms. These solutions help maintain optimal operating temperatures, prevent thermal throttling, and ensure stable performance during intensive memory operations, ultimately extending the lifespan of DDR5 memory modules.

- Power delivery and voltage regulation for DDR5: DDR5 memory incorporates on-module power management integrated circuits (PMICs) that improve voltage regulation and power delivery. These systems enable more precise voltage control, reduced power consumption, and better signal integrity. Advanced power delivery networks with optimized layouts minimize impedance mismatches and voltage fluctuations, allowing DDR5 memory to operate reliably at higher frequencies while maintaining energy efficiency.

- Signal integrity and layout optimization: DDR5 memory requires careful signal integrity management due to its higher operating frequencies. Optimized PCB layouts, improved routing techniques, and enhanced termination schemes help maintain signal quality. Advanced equalization techniques compensate for channel losses, while optimized trace lengths and impedance matching reduce signal reflections and crosstalk. These improvements enable reliable data transfer at DDR5's higher speeds.

- DDR5 training and calibration algorithms: Sophisticated training and calibration algorithms are essential for optimizing DDR5 memory performance. These algorithms fine-tune timing parameters, voltage levels, and signal characteristics during system initialization and operation. Machine learning techniques can be employed to predict optimal settings based on operating conditions. Advanced calibration methods compensate for manufacturing variations and environmental factors, ensuring maximum stability and performance across different workloads.

02 Thermal management solutions for DDR5

Thermal management is critical for DDR5 memory optimization as these modules operate at higher frequencies and voltages than previous generations. Solutions include advanced heat spreaders, integrated temperature sensors, and dynamic thermal throttling mechanisms. Improved cooling designs help maintain optimal operating temperatures, preventing performance degradation and ensuring reliability during high-speed operations.Expand Specific Solutions03 Power delivery and voltage regulation for DDR5

DDR5 memory incorporates on-module power management integrated circuits (PMICs) that improve voltage regulation and power delivery. These components enable more precise voltage control, reduced noise, and better power efficiency. Advanced power delivery network designs with optimized decoupling capacitors and voltage regulators help maintain stable operation at higher frequencies while reducing power consumption.Expand Specific Solutions04 Signal integrity and layout optimization

Signal integrity is crucial for DDR5 memory operating at high speeds. Optimized PCB layouts with controlled impedance traces, minimized crosstalk, and reduced electromagnetic interference improve signal quality. Advanced equalization techniques, decision feedback equalization, and receiver training algorithms help compensate for channel losses and maintain reliable data transmission at higher data rates.Expand Specific Solutions05 DDR5 memory training and calibration techniques

Sophisticated training and calibration algorithms optimize DDR5 memory performance by fine-tuning timing parameters and voltage levels. These techniques include read/write leveling, command training, and data eye training that adapt to specific hardware characteristics. Dynamic calibration mechanisms continuously monitor and adjust memory parameters during operation to maintain optimal performance as temperature and voltage conditions change.Expand Specific Solutions

Key Industry Players in DDR5 Memory Ecosystem

The DDR5 optimization for high-density data storage market is currently in a growth phase, with an expanding market driven by increasing data center demands and cloud computing proliferation. The competitive landscape features established memory manufacturers like Micron Technology and emerging players such as ChangXin Memory Technologies. Technical maturity varies significantly across competitors, with companies like Huawei, Inspur, and Micron demonstrating advanced DDR5 implementation capabilities through their server and storage solutions. AMD and Qualcomm are leveraging their semiconductor expertise to enhance DDR5 performance in computing applications, while specialized storage companies like Team Group and SanDisk are developing optimized DDR5-compatible solutions. The ecosystem shows collaborative innovation potential between memory manufacturers and system integrators.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei has developed comprehensive DDR5 optimization technologies specifically targeting high-density data storage solutions. Their approach integrates hardware and firmware innovations to maximize performance and reliability in data-intensive environments. Huawei's DDR5 implementation features advanced channel architecture that supports up to 8 memory ranks per channel while maintaining signal integrity, significantly increasing the maximum memory density available to storage systems. Their proprietary memory controller incorporates adaptive timing algorithms that dynamically adjust parameters based on workload characteristics, optimizing for either throughput or latency depending on storage access patterns. Huawei has also implemented sophisticated power management features that reduce DDR5 power consumption by up to 25% compared to standard implementations, addressing the increased power density challenges in high-capacity configurations. Additionally, their technology includes enhanced RAS (Reliability, Availability, Serviceability) features such as advanced ECC and memory mirroring specifically optimized for mission-critical storage applications.

Strengths: Highly integrated solution optimized for their own storage platforms; superior power efficiency in high-density configurations; advanced reliability features critical for enterprise storage. Weaknesses: Limited availability outside Huawei's own ecosystem; potential geopolitical challenges affecting global adoption; higher implementation complexity for third-party systems.

Micron Technology, Inc.

Technical Solution: Micron has developed advanced DDR5 memory solutions specifically optimized for high-density data storage applications. Their technology implements on-die ECC (Error Correction Code) that significantly improves data integrity and reliability in dense storage environments. Micron's DDR5 modules feature higher bandwidth (up to 6400 MT/s) and increased capacity (up to 64GB per DIMM), enabling more efficient data processing in storage systems. Their proprietary thermal management solutions address the increased power density challenges in DDR5, incorporating advanced materials and designs that optimize heat dissipation while maintaining signal integrity. Micron has also implemented adaptive power management features that dynamically adjust voltage based on workload demands, reducing power consumption by up to 20% compared to previous generations while maintaining performance levels needed for high-density storage operations.

Strengths: Industry-leading memory density and reliability with advanced ECC implementation; superior thermal management for high-density applications; significant power efficiency improvements. Weaknesses: Premium pricing compared to competitors; potential compatibility challenges with some legacy storage systems; higher initial implementation costs for system integrators.

Critical DDR5 Innovations and Patents

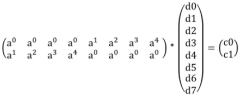

Memory system and data processing method

PatentPendingCN118245272A

Innovation

- By introducing a write mode command generation circuit and a mode register in the memory controller, it can determine whether the write data is in the preset mode and generate a write mode command, thereby reducing data transmission power consumption and expanding the application scope of the write mode function.

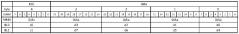

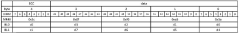

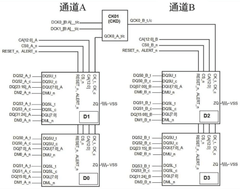

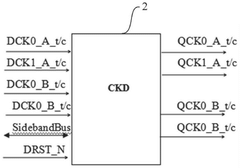

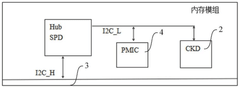

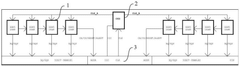

DDR5 CKD UDIMM memory module

PatentActiveCN221746872U

Innovation

- The DDR5 Clock Driver clock driver chip (CKD) is introduced to buffer and re-drive high-speed clock signals, providing single PLL, dual PLL and PLL bypass clock drive modes to ensure the integrity and reliability of clock signals.

Thermal Management Solutions for High-Density DDR5

The thermal challenges associated with high-density DDR5 implementations have become increasingly critical as data storage solutions evolve toward higher capacities and performance levels. DDR5 modules operating at speeds exceeding 6400 MT/s generate significantly more heat than previous generations, with power consumption increasing by approximately 30% compared to DDR4 at maximum loads. This thermal output creates potential reliability issues and performance degradation when modules are densely packed in server environments.

Advanced cooling solutions have emerged to address these challenges. Liquid cooling technologies, once reserved for high-performance computing, are now being adapted for enterprise storage systems utilizing high-density DDR5. These systems can reduce operating temperatures by 15-20°C compared to traditional air cooling, allowing for more compact arrangements of memory modules without thermal throttling.

Heat spreader designs have also evolved substantially for DDR5 applications. Aluminum-copper composite heat spreaders with vapor chamber technology have demonstrated 22% better thermal dissipation than conventional aluminum designs. Several manufacturers have introduced graphene-enhanced thermal interface materials that reduce the thermal resistance between memory chips and heat spreaders by up to 35%, significantly improving heat transfer efficiency.

Server-level thermal management systems now incorporate AI-driven predictive cooling that dynamically adjusts airflow based on workload patterns and memory utilization. These systems can reduce cooling energy consumption by up to 25% while maintaining optimal operating temperatures for DDR5 modules. The integration of micro-fans directly into memory module designs represents another innovation, providing targeted cooling to high-temperature zones without requiring additional chassis space.

For extreme density applications, immersion cooling solutions have proven effective, allowing DDR5 modules to operate at sustained high frequencies without thermal throttling. Tests have shown that immersion-cooled DDR5 systems can maintain stable operation at frequencies 8-10% higher than air-cooled equivalents under continuous heavy workloads.

Thermal monitoring capabilities have been enhanced with the integration of multiple temperature sensors across DDR5 modules, providing granular data for thermal management systems. This enables more precise cooling interventions and helps prevent localized hotspots that could compromise data integrity or module lifespan. The latest DDR5 specifications include standardized thermal reporting protocols that facilitate better integration with system-level cooling management.

Advanced cooling solutions have emerged to address these challenges. Liquid cooling technologies, once reserved for high-performance computing, are now being adapted for enterprise storage systems utilizing high-density DDR5. These systems can reduce operating temperatures by 15-20°C compared to traditional air cooling, allowing for more compact arrangements of memory modules without thermal throttling.

Heat spreader designs have also evolved substantially for DDR5 applications. Aluminum-copper composite heat spreaders with vapor chamber technology have demonstrated 22% better thermal dissipation than conventional aluminum designs. Several manufacturers have introduced graphene-enhanced thermal interface materials that reduce the thermal resistance between memory chips and heat spreaders by up to 35%, significantly improving heat transfer efficiency.

Server-level thermal management systems now incorporate AI-driven predictive cooling that dynamically adjusts airflow based on workload patterns and memory utilization. These systems can reduce cooling energy consumption by up to 25% while maintaining optimal operating temperatures for DDR5 modules. The integration of micro-fans directly into memory module designs represents another innovation, providing targeted cooling to high-temperature zones without requiring additional chassis space.

For extreme density applications, immersion cooling solutions have proven effective, allowing DDR5 modules to operate at sustained high frequencies without thermal throttling. Tests have shown that immersion-cooled DDR5 systems can maintain stable operation at frequencies 8-10% higher than air-cooled equivalents under continuous heavy workloads.

Thermal monitoring capabilities have been enhanced with the integration of multiple temperature sensors across DDR5 modules, providing granular data for thermal management systems. This enables more precise cooling interventions and helps prevent localized hotspots that could compromise data integrity or module lifespan. The latest DDR5 specifications include standardized thermal reporting protocols that facilitate better integration with system-level cooling management.

Power Efficiency Strategies for DDR5 Implementation

Power efficiency has become a critical consideration in DDR5 implementation for high-density data storage solutions. As data centers continue to expand, the energy consumption associated with memory systems represents a significant operational cost and environmental concern. DDR5 introduces several architectural improvements that can be leveraged to optimize power efficiency while maintaining or enhancing performance.

Voltage reduction stands as one of the most effective strategies, with DDR5 operating at 1.1V compared to DDR4's 1.2V. This 8.3% reduction in operating voltage translates to approximately 15-20% power savings when accounting for the quadratic relationship between voltage and power consumption. Implementation of adaptive voltage scaling techniques can further optimize this benefit by dynamically adjusting voltage based on workload demands.

Decision Feedback Equalization (DFE) circuits in DDR5 significantly improve signal integrity while reducing the power required for data transmission. These circuits compensate for channel loss and reflections, allowing reliable operation at lower power levels even in high-density configurations where signal integrity challenges are more pronounced.

The introduction of multiple independent channel architecture in DDR5 enables more granular power management. By implementing channel-specific power gating, systems can selectively power down unused channels during periods of low activity, resulting in substantial energy savings in real-world workloads that rarely utilize full memory bandwidth continuously.

On-die ECC (Error Correction Code) capabilities in DDR5 improve reliability while indirectly contributing to power efficiency. By reducing the frequency of data retransmission due to errors, systems can avoid the additional power consumption associated with error recovery processes, particularly important in high-density environments where error rates typically increase.

Advanced power management states in DDR5, including multiple self-refresh levels and fine-grained power-down modes, provide opportunities for sophisticated power management algorithms. Implementing predictive power state transitions based on workload analysis can maximize time spent in low-power states without compromising responsiveness.

Thermal management strategies also play a crucial role in overall power efficiency. DDR5's improved thermal sensors enable more accurate temperature monitoring, allowing for optimized cooling solutions that reduce fan power consumption while maintaining safe operating temperatures for high-density deployments.

Voltage reduction stands as one of the most effective strategies, with DDR5 operating at 1.1V compared to DDR4's 1.2V. This 8.3% reduction in operating voltage translates to approximately 15-20% power savings when accounting for the quadratic relationship between voltage and power consumption. Implementation of adaptive voltage scaling techniques can further optimize this benefit by dynamically adjusting voltage based on workload demands.

Decision Feedback Equalization (DFE) circuits in DDR5 significantly improve signal integrity while reducing the power required for data transmission. These circuits compensate for channel loss and reflections, allowing reliable operation at lower power levels even in high-density configurations where signal integrity challenges are more pronounced.

The introduction of multiple independent channel architecture in DDR5 enables more granular power management. By implementing channel-specific power gating, systems can selectively power down unused channels during periods of low activity, resulting in substantial energy savings in real-world workloads that rarely utilize full memory bandwidth continuously.

On-die ECC (Error Correction Code) capabilities in DDR5 improve reliability while indirectly contributing to power efficiency. By reducing the frequency of data retransmission due to errors, systems can avoid the additional power consumption associated with error recovery processes, particularly important in high-density environments where error rates typically increase.

Advanced power management states in DDR5, including multiple self-refresh levels and fine-grained power-down modes, provide opportunities for sophisticated power management algorithms. Implementing predictive power state transitions based on workload analysis can maximize time spent in low-power states without compromising responsiveness.

Thermal management strategies also play a crucial role in overall power efficiency. DDR5's improved thermal sensors enable more accurate temperature monitoring, allowing for optimized cooling solutions that reduce fan power consumption while maintaining safe operating temperatures for high-density deployments.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!