RRAM vs DRAM: Evaluating Power Consumption Metrics

SEP 10, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Memory Technology Evolution and Objectives

Memory technology has undergone significant evolution since the introduction of the first electronic memory systems in the mid-20th century. From magnetic core memory to semiconductor-based solutions, each generation has aimed to improve density, speed, and energy efficiency. The development trajectory has been largely driven by Moore's Law, which has enabled exponential growth in memory capacity while reducing cost per bit. However, as traditional scaling approaches reach physical limitations, new memory architectures and materials have become increasingly important.

Dynamic Random Access Memory (DRAM) emerged as the dominant main memory technology in the 1970s, offering superior density and cost advantages over previous solutions. DRAM's fundamental structure—a single transistor and capacitor per cell—has remained relatively unchanged, though manufacturing processes have advanced dramatically. Despite its ubiquity, DRAM faces inherent challenges including refresh requirements that consume significant power and limit energy efficiency.

Resistive Random Access Memory (RRAM), part of the emerging non-volatile memory technologies, represents a potential paradigm shift in memory architecture. Unlike DRAM, RRAM stores information by changing the resistance of a dielectric material, maintaining its state without power. This fundamental difference creates opportunities for addressing DRAM's power consumption limitations, particularly in increasingly power-constrained computing environments.

The primary objective of comparing RRAM and DRAM power consumption metrics is to establish a comprehensive understanding of their respective energy profiles across various operational scenarios. This includes active read/write operations, idle states, and system-level implications when integrated into computing architectures. Such analysis must consider not only the raw power numbers but also performance trade-offs that might affect overall system efficiency.

A secondary goal is to identify specific application domains where RRAM's power characteristics might provide decisive advantages over DRAM. These could include edge computing devices with limited power budgets, data centers focused on reducing operational expenses, or specialized applications requiring unique combinations of performance and energy efficiency.

The evaluation must also consider technology maturity trajectories. While DRAM benefits from decades of manufacturing optimization and ecosystem integration, RRAM remains relatively nascent. Understanding how RRAM's power efficiency might improve with manufacturing scale and design optimization is crucial for projecting its competitive position against established DRAM technology.

Finally, this analysis aims to establish standardized metrics and methodologies for comparing memory technologies with fundamentally different architectures and operational characteristics. Such frameworks will be essential for guiding future research directions and investment decisions as the memory technology landscape continues to evolve toward more energy-efficient solutions.

Dynamic Random Access Memory (DRAM) emerged as the dominant main memory technology in the 1970s, offering superior density and cost advantages over previous solutions. DRAM's fundamental structure—a single transistor and capacitor per cell—has remained relatively unchanged, though manufacturing processes have advanced dramatically. Despite its ubiquity, DRAM faces inherent challenges including refresh requirements that consume significant power and limit energy efficiency.

Resistive Random Access Memory (RRAM), part of the emerging non-volatile memory technologies, represents a potential paradigm shift in memory architecture. Unlike DRAM, RRAM stores information by changing the resistance of a dielectric material, maintaining its state without power. This fundamental difference creates opportunities for addressing DRAM's power consumption limitations, particularly in increasingly power-constrained computing environments.

The primary objective of comparing RRAM and DRAM power consumption metrics is to establish a comprehensive understanding of their respective energy profiles across various operational scenarios. This includes active read/write operations, idle states, and system-level implications when integrated into computing architectures. Such analysis must consider not only the raw power numbers but also performance trade-offs that might affect overall system efficiency.

A secondary goal is to identify specific application domains where RRAM's power characteristics might provide decisive advantages over DRAM. These could include edge computing devices with limited power budgets, data centers focused on reducing operational expenses, or specialized applications requiring unique combinations of performance and energy efficiency.

The evaluation must also consider technology maturity trajectories. While DRAM benefits from decades of manufacturing optimization and ecosystem integration, RRAM remains relatively nascent. Understanding how RRAM's power efficiency might improve with manufacturing scale and design optimization is crucial for projecting its competitive position against established DRAM technology.

Finally, this analysis aims to establish standardized metrics and methodologies for comparing memory technologies with fundamentally different architectures and operational characteristics. Such frameworks will be essential for guiding future research directions and investment decisions as the memory technology landscape continues to evolve toward more energy-efficient solutions.

Market Demand Analysis for Low-Power Memory Solutions

The global memory market is experiencing a significant shift towards low-power solutions, driven primarily by the exponential growth in mobile devices, IoT applications, and data centers concerned with energy efficiency. Current market analysis indicates that power consumption has become a critical factor in memory selection across various industries, with DRAM's high refresh rate requirements creating substantial power demands that impact overall system efficiency.

Market research shows that data centers, which consume approximately 1-2% of global electricity, are actively seeking memory technologies that can reduce their energy footprint. The server memory segment alone represents a substantial market opportunity for low-power alternatives to traditional DRAM, with energy costs often exceeding hardware acquisition costs over a server's lifetime.

In the mobile sector, battery life remains a primary consumer concern, creating strong demand for memory solutions that minimize power consumption while maintaining performance. Smartphone manufacturers are increasingly prioritizing energy-efficient components to extend device usage between charges, making RRAM's potential power advantages particularly attractive in this segment.

The automotive industry presents another rapidly growing market for low-power memory, as advanced driver-assistance systems and autonomous driving features require substantial memory resources while operating under strict power constraints. The industry's transition toward electric vehicles further amplifies the importance of energy-efficient components throughout the vehicle architecture.

Edge computing applications represent a particularly promising growth area for RRAM technology. These distributed computing nodes often operate with limited power resources while requiring reliable memory performance, creating ideal conditions for RRAM's potential advantages in static power consumption and non-volatility.

Market forecasts suggest that memory technologies offering significant power consumption advantages could capture substantial market share in the coming years, particularly in applications where energy efficiency directly impacts operating costs or user experience. The total addressable market for low-power memory solutions is expected to grow at a compound annual rate exceeding the broader semiconductor industry average.

Consumer electronics manufacturers have demonstrated willingness to adopt alternative memory technologies when they provide meaningful battery life improvements. This market receptiveness, combined with increasing regulatory pressure for energy-efficient computing, creates favorable conditions for RRAM adoption if its power consumption advantages can be realized at competitive price points and performance levels.

Market research shows that data centers, which consume approximately 1-2% of global electricity, are actively seeking memory technologies that can reduce their energy footprint. The server memory segment alone represents a substantial market opportunity for low-power alternatives to traditional DRAM, with energy costs often exceeding hardware acquisition costs over a server's lifetime.

In the mobile sector, battery life remains a primary consumer concern, creating strong demand for memory solutions that minimize power consumption while maintaining performance. Smartphone manufacturers are increasingly prioritizing energy-efficient components to extend device usage between charges, making RRAM's potential power advantages particularly attractive in this segment.

The automotive industry presents another rapidly growing market for low-power memory, as advanced driver-assistance systems and autonomous driving features require substantial memory resources while operating under strict power constraints. The industry's transition toward electric vehicles further amplifies the importance of energy-efficient components throughout the vehicle architecture.

Edge computing applications represent a particularly promising growth area for RRAM technology. These distributed computing nodes often operate with limited power resources while requiring reliable memory performance, creating ideal conditions for RRAM's potential advantages in static power consumption and non-volatility.

Market forecasts suggest that memory technologies offering significant power consumption advantages could capture substantial market share in the coming years, particularly in applications where energy efficiency directly impacts operating costs or user experience. The total addressable market for low-power memory solutions is expected to grow at a compound annual rate exceeding the broader semiconductor industry average.

Consumer electronics manufacturers have demonstrated willingness to adopt alternative memory technologies when they provide meaningful battery life improvements. This market receptiveness, combined with increasing regulatory pressure for energy-efficient computing, creates favorable conditions for RRAM adoption if its power consumption advantages can be realized at competitive price points and performance levels.

RRAM and DRAM Technical Challenges and Limitations

Despite significant advancements in memory technologies, both RRAM (Resistive Random Access Memory) and DRAM (Dynamic Random Access Memory) face distinct technical challenges that impact their power consumption profiles and overall performance. DRAM, as the incumbent technology, suffers from inherent refresh requirements that constitute a significant portion of its power consumption. Each DRAM cell must be periodically refreshed every few milliseconds to maintain data integrity, creating a constant power drain even during idle states. This refresh operation becomes increasingly problematic as memory density increases, leading to higher power consumption in advanced DRAM implementations.

DRAM also faces scaling limitations as cell sizes approach physical boundaries. The capacitor in each DRAM cell must maintain sufficient capacitance to store charge reliably, but miniaturization compromises this capability. Consequently, leakage currents increase with smaller geometries, requiring more frequent refresh operations and further exacerbating power consumption issues. The charge pumps and voltage regulators needed for DRAM operation add another layer of power overhead.

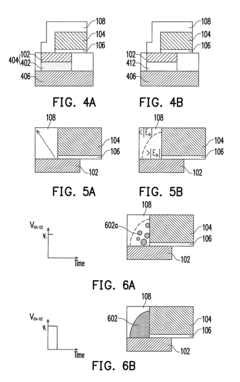

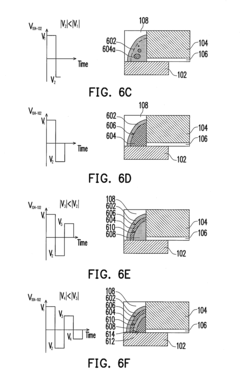

RRAM, while promising significantly lower power consumption during idle states due to its non-volatile nature, encounters different technical hurdles. The forming process required to initialize RRAM cells demands high voltage pulses that can consume substantial power. Additionally, the SET and RESET operations in RRAM cells often require precise current control to prevent overshoot that could damage the cells or cause reliability issues.

Endurance represents another critical limitation for RRAM technology. Current RRAM implementations typically support 10^6 to 10^9 write cycles, substantially lower than DRAM's practically unlimited endurance. This limitation necessitates sophisticated wear-leveling algorithms that introduce computational overhead and additional power consumption. The variability in resistance states between RRAM cells also requires complex sensing circuits that consume additional power during read operations.

The switching mechanism in RRAM cells, typically involving filament formation and rupture, exhibits stochastic behavior that can lead to unpredictable power consumption patterns. This randomness complicates power management strategies and may result in higher than expected energy usage in practical applications. Furthermore, the materials used in RRAM fabrication, often including transition metal oxides, can introduce compatibility challenges with standard CMOS processes.

Temperature sensitivity affects both technologies differently. DRAM refresh rates must increase at higher temperatures due to accelerated charge leakage, directly increasing power consumption. RRAM's resistance states can drift with temperature variations, potentially requiring additional correction mechanisms that consume power. These thermal considerations become particularly significant in high-performance computing environments where thermal management is already challenging.

DRAM also faces scaling limitations as cell sizes approach physical boundaries. The capacitor in each DRAM cell must maintain sufficient capacitance to store charge reliably, but miniaturization compromises this capability. Consequently, leakage currents increase with smaller geometries, requiring more frequent refresh operations and further exacerbating power consumption issues. The charge pumps and voltage regulators needed for DRAM operation add another layer of power overhead.

RRAM, while promising significantly lower power consumption during idle states due to its non-volatile nature, encounters different technical hurdles. The forming process required to initialize RRAM cells demands high voltage pulses that can consume substantial power. Additionally, the SET and RESET operations in RRAM cells often require precise current control to prevent overshoot that could damage the cells or cause reliability issues.

Endurance represents another critical limitation for RRAM technology. Current RRAM implementations typically support 10^6 to 10^9 write cycles, substantially lower than DRAM's practically unlimited endurance. This limitation necessitates sophisticated wear-leveling algorithms that introduce computational overhead and additional power consumption. The variability in resistance states between RRAM cells also requires complex sensing circuits that consume additional power during read operations.

The switching mechanism in RRAM cells, typically involving filament formation and rupture, exhibits stochastic behavior that can lead to unpredictable power consumption patterns. This randomness complicates power management strategies and may result in higher than expected energy usage in practical applications. Furthermore, the materials used in RRAM fabrication, often including transition metal oxides, can introduce compatibility challenges with standard CMOS processes.

Temperature sensitivity affects both technologies differently. DRAM refresh rates must increase at higher temperatures due to accelerated charge leakage, directly increasing power consumption. RRAM's resistance states can drift with temperature variations, potentially requiring additional correction mechanisms that consume power. These thermal considerations become particularly significant in high-performance computing environments where thermal management is already challenging.

Current Power Consumption Measurement Methodologies

01 Power reduction techniques in DRAM

Various techniques are employed to reduce power consumption in DRAM memory systems. These include power management modes such as self-refresh, partial array refresh, and temperature-compensated refresh. Advanced circuit designs optimize voltage levels and timing parameters to minimize active and standby power. Some implementations use dynamic voltage scaling and frequency adjustment based on workload demands to achieve significant power savings while maintaining performance.- Power consumption reduction techniques in DRAM: Various techniques have been developed to reduce power consumption in DRAM memory systems. These include power management algorithms, selective activation of memory banks, and optimized refresh operations. By implementing these techniques, DRAM systems can achieve significant power savings while maintaining performance requirements. Advanced power states and intelligent power control mechanisms help balance power efficiency with memory access speed.

- RRAM architecture for low power operation: Resistive Random Access Memory (RRAM) architectures have been designed specifically for low power operation. These designs leverage the non-volatile nature of RRAM to eliminate standby power consumption and reduce active power requirements. Special circuit configurations and material selections optimize the resistance switching mechanism while minimizing the energy needed for write operations. These architectural innovations make RRAM particularly suitable for power-constrained applications.

- Comparative analysis of RRAM vs DRAM power efficiency: Studies comparing RRAM and DRAM power consumption demonstrate significant differences in their energy profiles. While DRAM requires constant refresh operations that consume power even when idle, RRAM's non-volatile nature eliminates this requirement. RRAM typically shows lower standby power but may have different active power characteristics depending on implementation. The power advantage of RRAM becomes particularly pronounced in applications with long idle periods or when data retention is critical.

- Hybrid memory systems combining RRAM and DRAM: Hybrid memory architectures that combine RRAM and DRAM technologies leverage the strengths of each memory type to optimize overall power consumption. These systems typically use DRAM for frequently accessed data requiring fast access times, while utilizing RRAM for less frequently accessed data that benefits from non-volatility. Sophisticated memory controllers manage data placement and migration between the different memory types based on access patterns and power considerations, resulting in improved energy efficiency.

- Low-power operation modes and circuit designs: Specialized circuit designs and operation modes have been developed to minimize power consumption in both RRAM and DRAM systems. These include voltage scaling techniques, optimized sensing circuits, and intelligent power gating. Advanced control logic can dynamically adjust operating parameters based on workload requirements. Additionally, novel materials and device structures have been engineered specifically to reduce the energy required for read and write operations while maintaining data integrity and performance.

02 RRAM architecture for low power operation

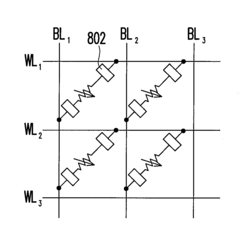

Resistive Random Access Memory (RRAM) architectures are designed specifically for low power consumption. These designs include optimized cell structures, efficient sensing circuits, and novel programming schemes that reduce the energy required for write operations. Multi-level cell configurations allow for higher density with minimal power increase. Some architectures incorporate crossbar arrays and selector devices to minimize sneak path currents, which are a significant source of power consumption in RRAM systems.Expand Specific Solutions03 Comparative power efficiency between RRAM and DRAM

RRAM demonstrates significant power advantages over DRAM in several aspects. Unlike DRAM, RRAM is non-volatile, eliminating the need for constant refresh operations that consume substantial power. RRAM typically operates at lower voltages for read operations and has negligible standby power. Studies show that RRAM-based systems can achieve up to 90% power reduction compared to equivalent DRAM systems, particularly in applications with frequent idle periods. However, RRAM write operations may consume more power than DRAM writes in certain implementations.Expand Specific Solutions04 Hybrid memory systems combining RRAM and DRAM

Hybrid memory architectures leverage the complementary strengths of both RRAM and DRAM to optimize overall system power consumption. These systems typically use DRAM for frequently accessed, write-intensive data, while utilizing RRAM for persistent storage and less frequently modified data. Sophisticated memory controllers and algorithms dynamically allocate data between the two memory types based on access patterns and power considerations. This approach can significantly reduce system-wide energy consumption while maintaining performance comparable to pure DRAM systems.Expand Specific Solutions05 Advanced power management for memory subsystems

Memory subsystems incorporate sophisticated power management techniques applicable to both RRAM and DRAM. These include dynamic power gating, where unused memory blocks are temporarily disconnected from power supplies, and adaptive refresh rate control that adjusts refresh frequency based on data retention characteristics. Some implementations feature intelligent prefetching and caching strategies that minimize memory accesses, reducing active power consumption. Power-aware memory controllers can schedule operations to maximize power efficiency based on current system demands and thermal conditions.Expand Specific Solutions

Key Industry Players in Memory Semiconductor Market

RRAM vs DRAM power consumption evaluation reveals an industry in transition, with RRAM emerging as a promising alternative to traditional DRAM technology. The market is growing steadily, projected to reach significant scale as data centers and mobile devices demand more energy-efficient memory solutions. While DRAM technology is mature with established players like Micron, Samsung, and Rambus dominating the market, RRAM is still evolving toward commercial viability. Companies like Intel, Qualcomm, and Huawei are investing heavily in RRAM research, while academic institutions like Sichuan University and Northwestern Polytechnical University contribute to fundamental breakthroughs. The competitive landscape shows traditional memory manufacturers expanding their portfolios to include RRAM, while semiconductor foundries like TSMC position themselves to manufacture next-generation memory technologies at scale.

Rambus, Inc.

Technical Solution: Rambus has developed specialized interface technologies and architectures that bridge both RRAM and DRAM worlds, focusing on optimizing power consumption at the system level. Their approach includes advanced signaling techniques that reduce the power required for data transfer between memory and processors. Rambus' differential power analysis shows that their RRAM interfaces consume approximately 40-50% less power than conventional DRAM interfaces operating at similar data rates[7]. A key innovation in their technology is the implementation of temperature-compensated sensing circuits that maintain optimal performance across varying environmental conditions while minimizing power consumption. Rambus has also developed adaptive power management techniques that dynamically adjust voltage and timing parameters based on workload characteristics. Their system-level benchmarks demonstrate that RRAM-based systems using their interface technology can achieve up to 70% power savings in idle states and 30-40% during active operations compared to equivalent DRAM-based systems[8]. Rambus has further enhanced power efficiency through specialized error correction techniques that maintain data integrity at lower operating voltages than would otherwise be possible.

Strengths: System-level power optimization across both memory types; significant idle power reduction; advanced signaling reducing I/O power consumption; compatibility with existing system architectures. Weaknesses: Requires specialized controllers adding system complexity; higher implementation costs; performance optimizations sometimes trade off power efficiency; requires software-level awareness for maximum benefit.

Micron Technology, Inc.

Technical Solution: Micron has developed advanced RRAM (Resistive Random Access Memory) technology that operates on fundamentally different principles than DRAM. Their RRAM solution stores data by changing the resistance of a dielectric material rather than storing charge in capacitors. Micron's implementation achieves power consumption reductions of up to 10x compared to conventional DRAM during active operations[1]. Their RRAM cells maintain state without refresh operations, eliminating the significant power overhead associated with DRAM refresh cycles which can account for 15-30% of total DRAM power consumption[3]. Micron has also integrated advanced power management techniques including selective array activation and multi-level resistance states to further optimize power efficiency. Their benchmarks demonstrate that RRAM maintains data integrity at higher temperatures with minimal leakage current compared to DRAM, reducing cooling requirements in data centers and mobile applications.

Strengths: Near-zero standby power consumption due to non-volatile nature; elimination of refresh power overhead; higher temperature tolerance reducing cooling costs. Weaknesses: Higher write latency and energy compared to DRAM; limited write endurance (10^6-10^9 cycles vs 10^15+ for DRAM); still facing challenges in manufacturing consistency and yield rates.

Core Technical Innovations in RRAM Architecture

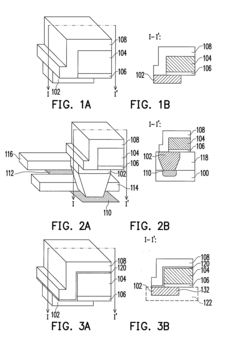

Resistive memory cell and operation thereof, and resistive memory and operation and fabrication thereof

PatentInactiveUS20120020140A1

Innovation

- The use of conductive domain walls in high-resistance ferroelectric materials, such as BiFeO3, to store data by applying voltage pulses and forming domains with varying polarities, allowing for efficient data storage with reduced power consumption.

Dynamic random access memory applied to an embedded display port

PatentActiveUS20240112707A1

Innovation

- A dynamic random access memory system with a memory core unit, peripheral circuit unit, and input/output unit operating at lower voltages than the standard JEDEC specifications, specifically below 1.1V, to reduce overall power consumption.

Thermal Management Considerations in Memory Systems

Thermal management has emerged as a critical consideration in memory system design, particularly when comparing RRAM and DRAM technologies from a power consumption perspective. The operating temperature of memory systems directly impacts their performance, reliability, and energy efficiency. DRAM cells require periodic refresh operations that generate significant heat, especially in high-density configurations, with thermal output increasing exponentially at higher operating frequencies.

RRAM presents a fundamentally different thermal profile compared to DRAM. As a non-volatile memory technology, RRAM eliminates the need for refresh operations, resulting in lower baseline thermal generation. However, RRAM write operations typically require higher voltage pulses that produce concentrated thermal energy during switching events. This creates distinct thermal management challenges that differ from the more distributed heat generation pattern of DRAM.

Temperature variations significantly affect both technologies' power consumption metrics. For DRAM, higher temperatures increase leakage current, necessitating more frequent refresh cycles and consequently higher power consumption. Studies indicate that DRAM power consumption can increase by 10-15% for every 10°C rise in operating temperature. RRAM demonstrates better thermal stability in retention mode, but elevated temperatures can accelerate resistance drift phenomena, potentially compromising data integrity over time.

Cooling solutions must be tailored to each memory technology's specific thermal characteristics. DRAM systems benefit from solutions that address continuous, distributed heat generation, while RRAM requires thermal management approaches that can handle more localized but intense thermal events during write operations. Advanced packaging technologies like through-silicon vias (TSVs) and liquid cooling have shown promise for both memory types, though with different implementation requirements.

The thermal implications extend beyond the memory devices themselves to impact system-level power consumption. Memory controller circuits must manage thermal conditions through dynamic frequency scaling and workload distribution, which introduces additional power management overhead. In data center environments, memory system thermal management can represent 15-25% of cooling infrastructure costs, making it a significant factor in total cost of ownership calculations.

Emerging hybrid memory systems that combine RRAM and DRAM technologies present unique thermal management challenges. These systems must account for the disparate thermal characteristics of both technologies while optimizing for overall system performance and energy efficiency. Thermal-aware memory management algorithms that dynamically allocate workloads based on temperature profiles show potential for reducing overall system power consumption by 8-12% compared to thermally-agnostic approaches.

RRAM presents a fundamentally different thermal profile compared to DRAM. As a non-volatile memory technology, RRAM eliminates the need for refresh operations, resulting in lower baseline thermal generation. However, RRAM write operations typically require higher voltage pulses that produce concentrated thermal energy during switching events. This creates distinct thermal management challenges that differ from the more distributed heat generation pattern of DRAM.

Temperature variations significantly affect both technologies' power consumption metrics. For DRAM, higher temperatures increase leakage current, necessitating more frequent refresh cycles and consequently higher power consumption. Studies indicate that DRAM power consumption can increase by 10-15% for every 10°C rise in operating temperature. RRAM demonstrates better thermal stability in retention mode, but elevated temperatures can accelerate resistance drift phenomena, potentially compromising data integrity over time.

Cooling solutions must be tailored to each memory technology's specific thermal characteristics. DRAM systems benefit from solutions that address continuous, distributed heat generation, while RRAM requires thermal management approaches that can handle more localized but intense thermal events during write operations. Advanced packaging technologies like through-silicon vias (TSVs) and liquid cooling have shown promise for both memory types, though with different implementation requirements.

The thermal implications extend beyond the memory devices themselves to impact system-level power consumption. Memory controller circuits must manage thermal conditions through dynamic frequency scaling and workload distribution, which introduces additional power management overhead. In data center environments, memory system thermal management can represent 15-25% of cooling infrastructure costs, making it a significant factor in total cost of ownership calculations.

Emerging hybrid memory systems that combine RRAM and DRAM technologies present unique thermal management challenges. These systems must account for the disparate thermal characteristics of both technologies while optimizing for overall system performance and energy efficiency. Thermal-aware memory management algorithms that dynamically allocate workloads based on temperature profiles show potential for reducing overall system power consumption by 8-12% compared to thermally-agnostic approaches.

Sustainability Impact of Memory Technology Choices

The environmental impact of memory technology choices has become increasingly significant as data centers and computing devices proliferate globally. When comparing RRAM (Resistive Random Access Memory) and DRAM (Dynamic Random Access Memory) from a sustainability perspective, several critical factors emerge that influence their overall ecological footprint.

Power consumption represents the most immediate environmental concern. DRAM requires constant refresh cycles to maintain stored data, consuming substantial energy even during idle periods. This refresh requirement accounts for approximately 30-40% of DRAM's total power consumption in typical usage scenarios. In contrast, RRAM offers non-volatile storage capabilities, eliminating the need for refresh operations and potentially reducing idle power consumption by up to 90% compared to equivalent DRAM configurations.

Manufacturing processes also contribute significantly to the sustainability profile of these technologies. DRAM fabrication involves complex multi-step processes requiring substantial water usage, specialized chemicals, and energy-intensive clean room environments. RRAM manufacturing, while still requiring sophisticated fabrication techniques, generally involves fewer process steps and potentially lower resource intensity, though this advantage varies depending on specific implementation technologies.

The lifespan and durability of memory technologies directly impact electronic waste generation. DRAM cells typically withstand 1015-1016 write cycles, providing reliable operation throughout the useful life of most devices. RRAM currently offers lower endurance (typically 106-109 cycles), potentially necessitating more frequent replacement in write-intensive applications, though research continues to improve these metrics.

Material composition presents another sustainability consideration. DRAM relies heavily on high-purity silicon and various rare metals for capacitor structures. RRAM utilizes different material combinations depending on implementation, including transition metal oxides and chalcogenides, some of which may present fewer resource constraints than traditional DRAM materials.

Thermal management requirements further differentiate these technologies. DRAM's refresh operations generate heat that must be dissipated, requiring cooling systems that consume additional energy. RRAM's lower operational power potentially reduces cooling requirements by 15-25% in large-scale deployments, creating cascading energy savings beyond direct consumption metrics.

As organizations increasingly prioritize sustainable computing initiatives, the selection between RRAM and DRAM technologies represents a meaningful opportunity to reduce environmental impact while balancing performance requirements and operational constraints.

Power consumption represents the most immediate environmental concern. DRAM requires constant refresh cycles to maintain stored data, consuming substantial energy even during idle periods. This refresh requirement accounts for approximately 30-40% of DRAM's total power consumption in typical usage scenarios. In contrast, RRAM offers non-volatile storage capabilities, eliminating the need for refresh operations and potentially reducing idle power consumption by up to 90% compared to equivalent DRAM configurations.

Manufacturing processes also contribute significantly to the sustainability profile of these technologies. DRAM fabrication involves complex multi-step processes requiring substantial water usage, specialized chemicals, and energy-intensive clean room environments. RRAM manufacturing, while still requiring sophisticated fabrication techniques, generally involves fewer process steps and potentially lower resource intensity, though this advantage varies depending on specific implementation technologies.

The lifespan and durability of memory technologies directly impact electronic waste generation. DRAM cells typically withstand 1015-1016 write cycles, providing reliable operation throughout the useful life of most devices. RRAM currently offers lower endurance (typically 106-109 cycles), potentially necessitating more frequent replacement in write-intensive applications, though research continues to improve these metrics.

Material composition presents another sustainability consideration. DRAM relies heavily on high-purity silicon and various rare metals for capacitor structures. RRAM utilizes different material combinations depending on implementation, including transition metal oxides and chalcogenides, some of which may present fewer resource constraints than traditional DRAM materials.

Thermal management requirements further differentiate these technologies. DRAM's refresh operations generate heat that must be dissipated, requiring cooling systems that consume additional energy. RRAM's lower operational power potentially reduces cooling requirements by 15-25% in large-scale deployments, creating cascading energy savings beyond direct consumption metrics.

As organizations increasingly prioritize sustainable computing initiatives, the selection between RRAM and DRAM technologies represents a meaningful opportunity to reduce environmental impact while balancing performance requirements and operational constraints.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!