Standards for Spin Qubits in Silicon-based Quantum Devices

OCT 10, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Silicon Spin Qubit Evolution and Objectives

Silicon spin qubits have emerged as one of the most promising platforms for quantum computing due to their compatibility with existing semiconductor manufacturing infrastructure. The evolution of silicon-based quantum devices began in the late 1990s with theoretical proposals for quantum bits based on electron spins in silicon. A significant milestone was reached in 2012 when researchers demonstrated the first single-qubit operations in silicon, marking the beginning of practical silicon spin qubit development.

The technological progression has been characterized by several key advancements. Initially, the focus was on demonstrating basic quantum operations with single electron spins. This evolved to include two-qubit gates, which are essential for universal quantum computation. Recent years have witnessed improvements in coherence times, gate fidelities, and the integration of multiple qubits on a single chip, pushing the boundaries of what silicon quantum devices can achieve.

Current objectives in the field center around establishing comprehensive standards for silicon spin qubits to ensure consistency, reliability, and interoperability across different research groups and commercial entities. These standards aim to address critical parameters such as qubit initialization fidelity, gate operation times, coherence times, readout accuracy, and inter-qubit coupling strength. Standardization efforts also extend to fabrication processes, material specifications, and testing methodologies.

The development of these standards is driven by the need to transition from laboratory demonstrations to scalable quantum computing systems. As the field matures, there is growing recognition that without agreed-upon benchmarks and specifications, progress toward practical quantum computers will be hindered by fragmentation and incompatibility issues between different implementations.

Long-term objectives include the creation of a silicon spin qubit ecosystem with standardized interfaces between quantum processors and classical control electronics. This would facilitate the development of modular quantum computing architectures where components from different manufacturers can work together seamlessly. Additionally, there is a push toward establishing error correction protocols specifically optimized for silicon spin qubits, which would be a crucial step toward fault-tolerant quantum computation.

The evolution trajectory suggests that silicon spin qubits are approaching a critical juncture where standardization will play a pivotal role in determining the pace of future advancements. Industry consortia, academic institutions, and national laboratories are increasingly collaborating to define these standards, recognizing that collective effort is essential for overcoming the remaining technical challenges in this field.

The technological progression has been characterized by several key advancements. Initially, the focus was on demonstrating basic quantum operations with single electron spins. This evolved to include two-qubit gates, which are essential for universal quantum computation. Recent years have witnessed improvements in coherence times, gate fidelities, and the integration of multiple qubits on a single chip, pushing the boundaries of what silicon quantum devices can achieve.

Current objectives in the field center around establishing comprehensive standards for silicon spin qubits to ensure consistency, reliability, and interoperability across different research groups and commercial entities. These standards aim to address critical parameters such as qubit initialization fidelity, gate operation times, coherence times, readout accuracy, and inter-qubit coupling strength. Standardization efforts also extend to fabrication processes, material specifications, and testing methodologies.

The development of these standards is driven by the need to transition from laboratory demonstrations to scalable quantum computing systems. As the field matures, there is growing recognition that without agreed-upon benchmarks and specifications, progress toward practical quantum computers will be hindered by fragmentation and incompatibility issues between different implementations.

Long-term objectives include the creation of a silicon spin qubit ecosystem with standardized interfaces between quantum processors and classical control electronics. This would facilitate the development of modular quantum computing architectures where components from different manufacturers can work together seamlessly. Additionally, there is a push toward establishing error correction protocols specifically optimized for silicon spin qubits, which would be a crucial step toward fault-tolerant quantum computation.

The evolution trajectory suggests that silicon spin qubits are approaching a critical juncture where standardization will play a pivotal role in determining the pace of future advancements. Industry consortia, academic institutions, and national laboratories are increasingly collaborating to define these standards, recognizing that collective effort is essential for overcoming the remaining technical challenges in this field.

Market Analysis for Silicon Quantum Computing

The silicon quantum computing market is experiencing significant growth, driven by the potential of silicon-based quantum devices to revolutionize computing capabilities. Current market valuations estimate the global quantum computing market at approximately $866 million in 2023, with silicon-based approaches capturing roughly 25% of this segment. Industry analysts project the overall market to expand at a CAGR of 38.3% through 2030, with silicon quantum computing potentially growing at an even faster rate of 42-45% annually.

Market demand is primarily concentrated in research institutions, government agencies, and forward-thinking corporations in the pharmaceutical, financial, and materials science sectors. These entities seek quantum advantage for complex optimization problems, molecular simulations, and cryptographic applications. Silicon-based quantum computing attracts particular interest due to its compatibility with existing semiconductor manufacturing infrastructure, potentially lowering barriers to commercialization.

Regional analysis reveals North America currently dominates market investment with approximately 45% of global funding, followed by Europe (30%) and Asia-Pacific (20%). However, China's national quantum initiative and significant investments from Japan and South Korea are rapidly shifting this balance. The Asia-Pacific region is projected to demonstrate the highest growth rate over the next five years.

Customer segmentation shows three distinct market tiers: quantum computing providers developing hardware platforms, quantum software companies creating applications, and end-users seeking quantum solutions for specific business challenges. The enterprise segment represents the largest potential market by volume, though currently at early adoption stages.

Market barriers include technical challenges in qubit coherence times, error rates, and scalability of silicon-based architectures. The lack of standardization for spin qubits in silicon devices specifically represents a critical market constraint, as it hampers interoperability and slows ecosystem development. Additionally, the shortage of quantum-trained talent and the high cost of research infrastructure limit market expansion.

Competitive dynamics reveal an ecosystem divided between established technology corporations (IBM, Intel, Microsoft), specialized quantum startups (Silicon Quantum Computing, Quantum Motion), and academic spin-offs. Recent strategic partnerships between hardware and software providers indicate market maturation, with increasing vertical integration across the quantum computing value chain.

Market forecasts suggest silicon-based quantum computing will reach commercial viability for specific applications by 2025-2027, with broader market penetration expected in the 2028-2030 timeframe as standards for spin qubits become established and technical challenges are overcome.

Market demand is primarily concentrated in research institutions, government agencies, and forward-thinking corporations in the pharmaceutical, financial, and materials science sectors. These entities seek quantum advantage for complex optimization problems, molecular simulations, and cryptographic applications. Silicon-based quantum computing attracts particular interest due to its compatibility with existing semiconductor manufacturing infrastructure, potentially lowering barriers to commercialization.

Regional analysis reveals North America currently dominates market investment with approximately 45% of global funding, followed by Europe (30%) and Asia-Pacific (20%). However, China's national quantum initiative and significant investments from Japan and South Korea are rapidly shifting this balance. The Asia-Pacific region is projected to demonstrate the highest growth rate over the next five years.

Customer segmentation shows three distinct market tiers: quantum computing providers developing hardware platforms, quantum software companies creating applications, and end-users seeking quantum solutions for specific business challenges. The enterprise segment represents the largest potential market by volume, though currently at early adoption stages.

Market barriers include technical challenges in qubit coherence times, error rates, and scalability of silicon-based architectures. The lack of standardization for spin qubits in silicon devices specifically represents a critical market constraint, as it hampers interoperability and slows ecosystem development. Additionally, the shortage of quantum-trained talent and the high cost of research infrastructure limit market expansion.

Competitive dynamics reveal an ecosystem divided between established technology corporations (IBM, Intel, Microsoft), specialized quantum startups (Silicon Quantum Computing, Quantum Motion), and academic spin-offs. Recent strategic partnerships between hardware and software providers indicate market maturation, with increasing vertical integration across the quantum computing value chain.

Market forecasts suggest silicon-based quantum computing will reach commercial viability for specific applications by 2025-2027, with broader market penetration expected in the 2028-2030 timeframe as standards for spin qubits become established and technical challenges are overcome.

Technical Barriers in Spin Qubit Standardization

Despite significant advancements in silicon-based spin qubit technology, several formidable technical barriers impede the establishment of comprehensive standards. The primary challenge lies in achieving consistent qubit performance across different fabrication processes. Current manufacturing techniques produce qubits with varying coherence times, gate fidelities, and coupling strengths, making standardization exceptionally difficult. This variability stems from atomic-level differences in the silicon substrate, dopant placement precision limitations, and interface quality fluctuations.

Charge noise represents another substantial barrier, causing decoherence and reducing operational fidelity. While various mitigation strategies exist, no universal solution has emerged that can be standardized across all silicon spin qubit implementations. The sources of charge noise vary between fabrication facilities and even between devices produced in the same batch, complicating efforts to establish noise tolerance standards.

Temperature dependence presents additional complications for standardization. Silicon spin qubits typically operate at extremely low temperatures (below 100 mK), but their sensitivity to thermal fluctuations varies based on specific design and materials. Establishing standard operating temperature ranges and thermal management protocols requires addressing these device-specific thermal responses.

Readout fidelity remains inconsistent across different spin qubit implementations. Single-shot readout techniques vary in their signal-to-noise ratios, speed, and compatibility with scalable architectures. Without standardized measurement protocols and performance metrics, comparing qubit quality across different research groups and commercial entities becomes problematic.

Integration with classical control electronics represents a significant standardization challenge. The interface between quantum and classical systems requires precise timing, minimal crosstalk, and efficient signal routing. Current approaches vary widely, from custom CMOS integration to separate control electronics, making it difficult to establish interface standards that accommodate all implementation strategies.

Scalability introduces additional complexity, as techniques that work for small qubit arrays often fail when scaled to larger systems. Addressing, control, and readout schemes that function effectively for tens of qubits may become impractical for systems with hundreds or thousands of qubits. Standards must therefore account for scaling trajectories and evolving architectural approaches.

Finally, the rapid pace of innovation in the field creates a moving target for standardization efforts. New materials, fabrication techniques, and qubit designs continually emerge, potentially rendering established standards obsolete. Creating flexible standards that can accommodate technological evolution while providing meaningful benchmarks represents perhaps the most fundamental challenge in spin qubit standardization.

Charge noise represents another substantial barrier, causing decoherence and reducing operational fidelity. While various mitigation strategies exist, no universal solution has emerged that can be standardized across all silicon spin qubit implementations. The sources of charge noise vary between fabrication facilities and even between devices produced in the same batch, complicating efforts to establish noise tolerance standards.

Temperature dependence presents additional complications for standardization. Silicon spin qubits typically operate at extremely low temperatures (below 100 mK), but their sensitivity to thermal fluctuations varies based on specific design and materials. Establishing standard operating temperature ranges and thermal management protocols requires addressing these device-specific thermal responses.

Readout fidelity remains inconsistent across different spin qubit implementations. Single-shot readout techniques vary in their signal-to-noise ratios, speed, and compatibility with scalable architectures. Without standardized measurement protocols and performance metrics, comparing qubit quality across different research groups and commercial entities becomes problematic.

Integration with classical control electronics represents a significant standardization challenge. The interface between quantum and classical systems requires precise timing, minimal crosstalk, and efficient signal routing. Current approaches vary widely, from custom CMOS integration to separate control electronics, making it difficult to establish interface standards that accommodate all implementation strategies.

Scalability introduces additional complexity, as techniques that work for small qubit arrays often fail when scaled to larger systems. Addressing, control, and readout schemes that function effectively for tens of qubits may become impractical for systems with hundreds or thousands of qubits. Standards must therefore account for scaling trajectories and evolving architectural approaches.

Finally, the rapid pace of innovation in the field creates a moving target for standardization efforts. New materials, fabrication techniques, and qubit designs continually emerge, potentially rendering established standards obsolete. Creating flexible standards that can accommodate technological evolution while providing meaningful benchmarks represents perhaps the most fundamental challenge in spin qubit standardization.

Current Standardization Approaches

01 Silicon-based spin qubit fabrication techniques

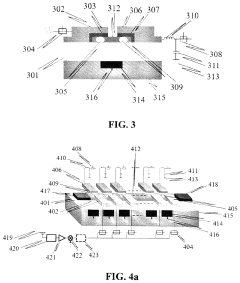

Advanced fabrication methods for creating spin qubits in silicon substrates, including lithographic techniques, ion implantation, and epitaxial growth processes. These techniques enable precise control over the placement and characteristics of quantum dots that host spin qubits, allowing for scalable quantum device architectures. The fabrication processes focus on minimizing defects and maintaining coherence times necessary for quantum operations.- Silicon-based spin qubit fabrication techniques: Advanced fabrication methods for creating spin qubits in silicon substrates, including lithographic techniques, ion implantation, and epitaxial growth processes. These techniques enable precise positioning and control of individual electron spins in silicon quantum dots, which serve as qubits. The fabrication standards address challenges such as reducing interface defects, controlling dopant placement, and achieving consistent quantum dot geometries necessary for reliable qubit operation.

- Quantum gate operations and control systems: Methods and systems for implementing quantum gate operations on silicon-based spin qubits, including single-qubit rotations and two-qubit entangling gates. These control systems involve precise microwave and RF pulse sequences, voltage control of exchange interactions, and magnetic field manipulation. Standards for gate fidelity measurement, calibration protocols, and error characterization are essential for comparing different silicon qubit implementations and ensuring reliable quantum computation.

- Readout and measurement techniques: Standardized approaches for spin qubit state readout and measurement in silicon-based quantum devices. These include single-shot readout methods using spin-to-charge conversion, reflectometry techniques, and dispersive gate sensing. The standards address signal-to-noise optimization, measurement fidelity benchmarks, and protocols for characterizing readout errors. Consistent measurement techniques are crucial for comparing qubit performance across different silicon quantum computing platforms.

- Quantum error correction and fault tolerance: Implementation of quantum error correction codes specifically adapted for silicon spin qubit architectures. These standards address the requirements for fault-tolerant quantum computation using silicon spin qubits, including surface codes, logical qubit encoding, and error detection protocols. The approaches consider the specific noise characteristics and error mechanisms in silicon-based quantum devices, such as charge noise, nuclear spin fluctuations, and exchange coupling variations.

- Integration with classical control electronics: Standards for interfacing silicon spin qubits with classical control electronics, addressing challenges in cryogenic operation, signal integrity, and scalability. These include specifications for cryogenic CMOS circuits, multiplexing architectures, and control signal routing that minimize thermal load and electromagnetic interference. The integration standards are crucial for scaling silicon quantum processors beyond few-qubit demonstrations to practical quantum computing systems with hundreds or thousands of qubits.

02 Quantum gate operations and control mechanisms

Methods for implementing and controlling quantum gate operations in silicon-based spin qubit systems. These include techniques for single-qubit rotations, two-qubit entangling gates, and multi-qubit operations essential for quantum computing. The control mechanisms involve precise microwave pulses, magnetic field gradients, and electric field manipulation to achieve high-fidelity quantum operations while minimizing decoherence effects.Expand Specific Solutions03 Error correction and quantum measurement standards

Standardized approaches for error detection, correction, and measurement in silicon spin qubit systems. These standards address quantum state readout techniques, error thresholds, and protocols for implementing quantum error correction codes. The methods include spin-to-charge conversion for readout, dynamic decoupling sequences to extend coherence times, and surface code implementations tailored for silicon-based quantum architectures.Expand Specific Solutions04 Scalable quantum processor architectures

Design standards for scaling silicon-based spin qubit systems to create large-scale quantum processors. These architectures address qubit connectivity, control line routing, and integration with classical electronics. The standards include specifications for crossbar arrays, quantum interconnects, and modular designs that enable fault-tolerant quantum computation while managing thermal and electromagnetic interference challenges.Expand Specific Solutions05 Interface standards for quantum-classical integration

Standardized interfaces between silicon spin qubit quantum processors and classical control electronics. These standards define protocols for signal conversion, timing synchronization, and data exchange between quantum and classical domains. The specifications address cryogenic control electronics, room-temperature instrumentation requirements, and software interfaces for programming and operating silicon-based quantum devices in research and commercial applications.Expand Specific Solutions

Leading Organizations in Silicon Quantum Technology

Silicon-based spin qubit quantum computing is currently in the early development stage, characterized by significant research momentum but limited commercial deployment. The market is projected to grow substantially as quantum technologies mature, with estimates suggesting a multi-billion dollar potential within the next decade. Technologically, companies are at varying maturity levels: Intel and Fujitsu represent established semiconductor players leveraging their manufacturing expertise; specialized quantum startups like Quantum Motion Technologies, C12 Quantum Electronics, and SeeQC are developing innovative spin qubit architectures; while research institutions including CNRS, IMEC, and Origin Quantum are advancing fundamental science. The competitive landscape features collaboration between academic institutions and industry partners, with standardization efforts emerging as critical for enabling interoperability and accelerating commercialization of silicon-based quantum devices.

Commissariat à l´énergie atomique et aux énergies Alternatives

Technical Solution: The French Alternative Energies and Atomic Energy Commission (CEA) has developed advanced silicon-based spin qubit technologies through their quantum computing research program. Their approach centers on creating silicon-germanium (SiGe) heterostructures that form quantum wells where electron spins can be trapped and manipulated as qubits. CEA has pioneered techniques for isotopically purified silicon, reducing decoherence caused by nuclear spins. Their technology includes specialized gate architectures for high-fidelity qubit control, with demonstrated coherence times exceeding 1 millisecond. CEA has established standardized fabrication processes using 300mm silicon wafers, compatible with industrial semiconductor manufacturing. Their architecture includes on-chip multiplexing for qubit control signals, addressing a key challenge in scaling quantum processors. CEA has also developed integrated cryogenic electronics for qubit readout and control, operating at temperatures around 1-4 Kelvin. Their research has demonstrated two-qubit gates with fidelities approaching 99%, a critical benchmark for quantum error correction.

Strengths: Advanced materials engineering with SiGe heterostructures; industrial-scale fabrication processes; long coherence times; integrated cryogenic control electronics. Weaknesses: Complex fabrication requirements for heterostructures; challenges in scaling to large qubit numbers; requires precise control of material interfaces.

Interuniversitair Micro-Electronica Centrum VZW

Technical Solution: IMEC has developed a comprehensive platform for silicon-based spin qubits through their quantum computing research program. Their approach focuses on creating quantum dots in silicon using advanced semiconductor manufacturing processes compatible with their 300mm fabrication facility. IMEC's technology involves creating gate-defined quantum dots in silicon that can trap individual electrons, whose spin states serve as qubits. They have pioneered techniques for isotopically purified silicon-28, which provides a "quiet" environment for spin qubits by removing nuclear spin noise. IMEC has established standardized processes for creating arrays of uniform quantum dots with high yield rates and reproducible characteristics. Their architecture includes specialized gate designs for qubit manipulation and readout, with demonstrated single-qubit gate fidelities exceeding 99.9%. IMEC has also developed integrated cryogenic electronics for qubit control, operating at temperatures around 1-4 Kelvin. Their research has demonstrated coherence times exceeding 1 millisecond and includes work on two-qubit gates necessary for quantum algorithms.

Strengths: World-class semiconductor fabrication capabilities; advanced materials engineering with isotopically purified silicon; industrial-scale manufacturing processes; integrated cryogenic electronics. Weaknesses: Challenges in scaling to large qubit numbers; requires extremely precise control of semiconductor interfaces; sensitive to manufacturing variations.

Key Patents in Spin Qubit Architecture

Silicon-based spin-qubit quantum magnetometer and radar system with all electrical control

PatentActiveUS11894475B2

Innovation

- A silicon-based spin-qubit quantum radar system with all-electrical control, utilizing FETs with Back-Gates and Front-Gates to induce spin qubit rotation and measure echo signals, allowing for scalable 4-Dimension target detection through multiple range bins and antenna configurations.

International Collaboration Frameworks

The development of silicon-based quantum computing technologies necessitates robust international collaboration frameworks to establish universal standards for spin qubits. Currently, several significant collaborative initiatives are driving standardization efforts across borders. The Quantum Economic Development Consortium (QED-C) represents a pivotal public-private partnership that brings together industry leaders, academic institutions, and government agencies to accelerate quantum technology commercialization, with specific working groups dedicated to silicon-based qubit standardization.

The European Quantum Industry Consortium (QuIC) has established dedicated technical committees focusing on silicon spin qubit characterization protocols and performance metrics. These committees facilitate knowledge exchange between European research institutions and industry partners, creating a unified approach to standards development that balances innovation with practical implementation requirements.

In Asia, Japan's Quantum Technology Innovation Hub collaborates extensively with international partners on silicon qubit fabrication standards, while China's National Quantum Laboratory maintains active participation in global standardization discussions through bilateral research agreements with European and North American institutions.

The IEEE Quantum Initiative serves as a neutral platform for international standardization efforts, having launched specific working groups on silicon-based quantum computing that address measurement protocols, qubit quality metrics, and interface specifications. Their published technical standards are increasingly recognized as global benchmarks for the industry.

Academic-industrial partnerships form another critical dimension of international collaboration, with notable examples including the Silicon Quantum Computing Consortium linking universities across Australia, Europe, and North America. This consortium has published influential white papers on standardized characterization methods for spin qubits that have been widely adopted.

International standards organizations like ISO and IEC have recently established joint technical committees specifically addressing quantum computing technologies, with dedicated subcommittees for solid-state qubit implementations. These committees are developing formal international standards for silicon spin qubit terminology, measurement techniques, and performance benchmarking.

Funding mechanisms supporting these collaborative frameworks include multinational research initiatives like the EU Quantum Flagship program and the US National Quantum Initiative, both of which allocate significant resources to standards development through international partnerships. These programs facilitate researcher exchanges, joint laboratory access, and shared experimental protocols that accelerate consensus-building on technical standards.

The European Quantum Industry Consortium (QuIC) has established dedicated technical committees focusing on silicon spin qubit characterization protocols and performance metrics. These committees facilitate knowledge exchange between European research institutions and industry partners, creating a unified approach to standards development that balances innovation with practical implementation requirements.

In Asia, Japan's Quantum Technology Innovation Hub collaborates extensively with international partners on silicon qubit fabrication standards, while China's National Quantum Laboratory maintains active participation in global standardization discussions through bilateral research agreements with European and North American institutions.

The IEEE Quantum Initiative serves as a neutral platform for international standardization efforts, having launched specific working groups on silicon-based quantum computing that address measurement protocols, qubit quality metrics, and interface specifications. Their published technical standards are increasingly recognized as global benchmarks for the industry.

Academic-industrial partnerships form another critical dimension of international collaboration, with notable examples including the Silicon Quantum Computing Consortium linking universities across Australia, Europe, and North America. This consortium has published influential white papers on standardized characterization methods for spin qubits that have been widely adopted.

International standards organizations like ISO and IEC have recently established joint technical committees specifically addressing quantum computing technologies, with dedicated subcommittees for solid-state qubit implementations. These committees are developing formal international standards for silicon spin qubit terminology, measurement techniques, and performance benchmarking.

Funding mechanisms supporting these collaborative frameworks include multinational research initiatives like the EU Quantum Flagship program and the US National Quantum Initiative, both of which allocate significant resources to standards development through international partnerships. These programs facilitate researcher exchanges, joint laboratory access, and shared experimental protocols that accelerate consensus-building on technical standards.

Quantum Error Correction Strategies

Quantum Error Correction (QEC) represents a critical frontier for silicon-based spin qubit systems, as quantum information is inherently vulnerable to environmental noise and decoherence. For silicon spin qubits to achieve fault-tolerance and scalability, robust error correction protocols must be standardized. Current QEC strategies for silicon-based quantum devices primarily focus on surface codes and Steane codes, which have demonstrated promising error thresholds in theoretical models and early experimental implementations.

The surface code architecture appears particularly well-suited for silicon spin qubit arrays due to its nearest-neighbor connectivity requirements and relatively high error thresholds (approximately 1%). Recent experimental demonstrations have shown the feasibility of implementing basic surface code elements in silicon quantum dot arrays, with two-qubit gate fidelities approaching the threshold required for error correction. However, challenges remain in scaling these implementations while maintaining uniform qubit properties across the array.

Concatenated codes offer an alternative approach, with the advantage of potentially lower resource requirements for moderate-scale quantum processors. The Steane [[7,1,3]] code has been adapted for silicon spin qubits by leveraging their long coherence times, though the non-local nature of these codes presents significant engineering challenges for physical implementation in silicon architectures.

Hardware-efficient QEC codes tailored specifically to silicon spin qubits are emerging as a promising direction. These codes exploit the unique characteristics of silicon platforms, such as the ability to perform high-fidelity single-shot readout and the natural isolation of nuclear spins for auxiliary quantum memory. The bosonic encoding approach, originally developed for superconducting circuits, is being adapted for electron spin ensembles in silicon, potentially offering more efficient error correction with fewer physical qubits.

Leakage errors present a particular challenge for silicon spin qubits, as the two-level approximation can break down under certain control sequences. Specialized leakage reduction units (LRUs) are being developed to address this issue, with recent protocols demonstrating the ability to detect and reset leakage with minimal impact on computational qubits. These protocols will likely form an essential component of standardized error correction frameworks for silicon-based quantum devices.

Dynamical decoupling sequences integrated with error correction codes show promise for extending coherence times during QEC cycles. Optimized pulse sequences that are compatible with the requirements of error syndrome extraction are being standardized, with recent demonstrations achieving an order of magnitude improvement in effective T2 times during active error correction.

The surface code architecture appears particularly well-suited for silicon spin qubit arrays due to its nearest-neighbor connectivity requirements and relatively high error thresholds (approximately 1%). Recent experimental demonstrations have shown the feasibility of implementing basic surface code elements in silicon quantum dot arrays, with two-qubit gate fidelities approaching the threshold required for error correction. However, challenges remain in scaling these implementations while maintaining uniform qubit properties across the array.

Concatenated codes offer an alternative approach, with the advantage of potentially lower resource requirements for moderate-scale quantum processors. The Steane [[7,1,3]] code has been adapted for silicon spin qubits by leveraging their long coherence times, though the non-local nature of these codes presents significant engineering challenges for physical implementation in silicon architectures.

Hardware-efficient QEC codes tailored specifically to silicon spin qubits are emerging as a promising direction. These codes exploit the unique characteristics of silicon platforms, such as the ability to perform high-fidelity single-shot readout and the natural isolation of nuclear spins for auxiliary quantum memory. The bosonic encoding approach, originally developed for superconducting circuits, is being adapted for electron spin ensembles in silicon, potentially offering more efficient error correction with fewer physical qubits.

Leakage errors present a particular challenge for silicon spin qubits, as the two-level approximation can break down under certain control sequences. Specialized leakage reduction units (LRUs) are being developed to address this issue, with recent protocols demonstrating the ability to detect and reset leakage with minimal impact on computational qubits. These protocols will likely form an essential component of standardized error correction frameworks for silicon-based quantum devices.

Dynamical decoupling sequences integrated with error correction codes show promise for extending coherence times during QEC cycles. Optimized pulse sequences that are compatible with the requirements of error syndrome extraction are being standardized, with recent demonstrations achieving an order of magnitude improvement in effective T2 times during active error correction.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!