Spin Qubits in Silicon: Barrier Penetration Properties

OCT 10, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Silicon Spin Qubits Background and Objectives

Spin qubits in silicon have emerged as a promising platform for quantum computing due to their long coherence times, scalability potential, and compatibility with existing semiconductor manufacturing infrastructure. The evolution of silicon-based quantum computing can be traced back to the 1990s when theoretical proposals for quantum dots in semiconductors first appeared. By the early 2000s, researchers began demonstrating control over single electron spins in silicon, marking a significant milestone in the field.

The technological trajectory has accelerated dramatically over the past decade, with breakthroughs in fabrication techniques, control mechanisms, and measurement protocols. Silicon spin qubits have progressed from single-qubit demonstrations to multi-qubit systems capable of implementing basic quantum algorithms. This rapid advancement has positioned silicon as a leading contender in the race to build practical quantum computers.

Barrier penetration properties represent a critical aspect of silicon spin qubit technology. These properties govern electron tunneling between quantum dots and significantly impact qubit performance metrics such as gate fidelity, operation speed, and scalability. Understanding and controlling barrier penetration is essential for advancing silicon-based quantum computing architectures.

The current technical objectives in this field focus on several key areas. First, researchers aim to enhance barrier engineering techniques to achieve precise control over electron tunneling rates. This includes developing more sophisticated gate structures and optimizing voltage control protocols to manipulate barrier heights with greater precision.

Second, there is significant interest in characterizing and mitigating environmental factors that affect barrier properties, such as charge noise, thermal fluctuations, and material defects. These factors can cause unwanted variations in barrier heights and tunneling rates, leading to decoherence and operational errors.

Third, the field is moving toward integrating barrier control mechanisms into larger qubit arrays, addressing challenges related to cross-talk, control line routing, and maintaining uniformity across multiple qubits. This integration is crucial for scaling silicon spin qubit systems beyond proof-of-concept demonstrations.

Finally, researchers are exploring novel barrier designs that could enable new functionalities, such as long-range coupling between distant qubits or hybrid architectures that combine different qubit types. These innovations could potentially overcome current limitations in qubit connectivity and control.

The ultimate goal is to develop silicon spin qubit systems with barrier properties that support high-fidelity quantum operations while maintaining the scalability advantages inherent to silicon-based platforms. Success in this endeavor would significantly advance the prospects for practical, fault-tolerant quantum computing based on silicon technology.

The technological trajectory has accelerated dramatically over the past decade, with breakthroughs in fabrication techniques, control mechanisms, and measurement protocols. Silicon spin qubits have progressed from single-qubit demonstrations to multi-qubit systems capable of implementing basic quantum algorithms. This rapid advancement has positioned silicon as a leading contender in the race to build practical quantum computers.

Barrier penetration properties represent a critical aspect of silicon spin qubit technology. These properties govern electron tunneling between quantum dots and significantly impact qubit performance metrics such as gate fidelity, operation speed, and scalability. Understanding and controlling barrier penetration is essential for advancing silicon-based quantum computing architectures.

The current technical objectives in this field focus on several key areas. First, researchers aim to enhance barrier engineering techniques to achieve precise control over electron tunneling rates. This includes developing more sophisticated gate structures and optimizing voltage control protocols to manipulate barrier heights with greater precision.

Second, there is significant interest in characterizing and mitigating environmental factors that affect barrier properties, such as charge noise, thermal fluctuations, and material defects. These factors can cause unwanted variations in barrier heights and tunneling rates, leading to decoherence and operational errors.

Third, the field is moving toward integrating barrier control mechanisms into larger qubit arrays, addressing challenges related to cross-talk, control line routing, and maintaining uniformity across multiple qubits. This integration is crucial for scaling silicon spin qubit systems beyond proof-of-concept demonstrations.

Finally, researchers are exploring novel barrier designs that could enable new functionalities, such as long-range coupling between distant qubits or hybrid architectures that combine different qubit types. These innovations could potentially overcome current limitations in qubit connectivity and control.

The ultimate goal is to develop silicon spin qubit systems with barrier properties that support high-fidelity quantum operations while maintaining the scalability advantages inherent to silicon-based platforms. Success in this endeavor would significantly advance the prospects for practical, fault-tolerant quantum computing based on silicon technology.

Quantum Computing Market Analysis

The quantum computing market is experiencing unprecedented growth, driven by significant advancements in qubit technologies, including silicon-based spin qubits. Current market valuations place the global quantum computing sector at approximately 866 million USD in 2023, with projections indicating potential growth to reach 4.6 billion USD by 2028, representing a compound annual growth rate (CAGR) of 39.8%.

Silicon spin qubits, particularly those leveraging barrier penetration properties, are positioned as a promising technology within this expanding market. Their compatibility with existing semiconductor manufacturing infrastructure presents a substantial competitive advantage, potentially reducing the barrier to entry for established chip manufacturers looking to diversify into quantum technologies.

Market demand for quantum computing solutions is primarily concentrated in sectors requiring complex computational capabilities, including pharmaceuticals, materials science, financial modeling, and cryptography. The pharmaceutical industry alone is investing heavily in quantum computing research, with major companies allocating research budgets exceeding 100 million USD annually toward quantum-enabled drug discovery processes.

Geographically, North America currently dominates the quantum computing market with approximately 42% market share, followed by Europe at 28% and Asia-Pacific at 24%. However, the Asia-Pacific region is demonstrating the fastest growth rate, particularly in countries with established semiconductor industries like Taiwan, South Korea, and Japan, where silicon spin qubit research is receiving substantial government funding.

Venture capital investments in quantum computing startups focusing on silicon-based approaches have seen remarkable growth, with funding rounds increasing from 300 million USD in 2018 to over 1.2 billion USD in 2022. This investment trend reflects growing confidence in silicon spin qubits as a commercially viable quantum computing platform.

End-user adoption remains in early stages, with enterprise quantum computing services market currently valued at approximately 150 million USD. However, the quantum-as-a-service (QaaS) model is gaining traction, with annual growth rates exceeding 30%. This service-based approach is lowering barriers to entry for organizations interested in exploring quantum applications without significant capital investment.

The market for specialized quantum computing talent shows significant supply constraints, with demand for quantum physicists and engineers with expertise in spin qubits outpacing available professionals by an estimated ratio of 3:1. This talent gap represents both a challenge and opportunity for organizations developing silicon-based quantum technologies.

Silicon spin qubits, particularly those leveraging barrier penetration properties, are positioned as a promising technology within this expanding market. Their compatibility with existing semiconductor manufacturing infrastructure presents a substantial competitive advantage, potentially reducing the barrier to entry for established chip manufacturers looking to diversify into quantum technologies.

Market demand for quantum computing solutions is primarily concentrated in sectors requiring complex computational capabilities, including pharmaceuticals, materials science, financial modeling, and cryptography. The pharmaceutical industry alone is investing heavily in quantum computing research, with major companies allocating research budgets exceeding 100 million USD annually toward quantum-enabled drug discovery processes.

Geographically, North America currently dominates the quantum computing market with approximately 42% market share, followed by Europe at 28% and Asia-Pacific at 24%. However, the Asia-Pacific region is demonstrating the fastest growth rate, particularly in countries with established semiconductor industries like Taiwan, South Korea, and Japan, where silicon spin qubit research is receiving substantial government funding.

Venture capital investments in quantum computing startups focusing on silicon-based approaches have seen remarkable growth, with funding rounds increasing from 300 million USD in 2018 to over 1.2 billion USD in 2022. This investment trend reflects growing confidence in silicon spin qubits as a commercially viable quantum computing platform.

End-user adoption remains in early stages, with enterprise quantum computing services market currently valued at approximately 150 million USD. However, the quantum-as-a-service (QaaS) model is gaining traction, with annual growth rates exceeding 30%. This service-based approach is lowering barriers to entry for organizations interested in exploring quantum applications without significant capital investment.

The market for specialized quantum computing talent shows significant supply constraints, with demand for quantum physicists and engineers with expertise in spin qubits outpacing available professionals by an estimated ratio of 3:1. This talent gap represents both a challenge and opportunity for organizations developing silicon-based quantum technologies.

Current Challenges in Barrier Penetration Research

Despite significant advancements in spin qubit technology, barrier penetration research faces several critical challenges that impede further progress in silicon-based quantum computing. The quantum tunneling effect, fundamental to barrier penetration, remains difficult to control precisely in silicon environments due to material interface irregularities and atomic-level defects that create unpredictable barrier profiles.

Temperature dependence presents another significant obstacle, as even minor thermal fluctuations can dramatically alter tunneling rates and barrier properties. Current cooling technologies struggle to maintain the ultra-low temperatures required for consistent barrier characteristics while simultaneously allowing for measurement and control operations.

Measurement-induced decoherence continues to plague barrier penetration studies. The very act of measuring tunneling events often disturbs the quantum state being observed, creating a fundamental tension between obtaining sufficient data and preserving quantum information. This "observer effect" at the quantum level necessitates novel measurement protocols that remain elusive.

Fabrication inconsistencies represent a major manufacturing challenge. Despite advances in semiconductor processing, achieving atomically precise barriers with reproducible penetration properties across multiple qubits remains exceptionally difficult. Variations as small as a single atom can significantly alter tunneling characteristics, making large-scale integration problematic.

The coupling between spin and orbital degrees of freedom introduces complex dynamics that are difficult to model accurately. This spin-orbit coupling varies with barrier properties and can lead to unexpected decoherence mechanisms that are not fully understood theoretically or characterized experimentally.

Time-dependent barrier modulation, essential for many quantum gate operations, introduces additional complexities. Creating precisely timed barrier height variations without generating unwanted excitations or heating effects requires control electronics with timing precision and noise characteristics beyond current capabilities.

Multi-qubit operations face particular challenges related to barrier penetration, as entanglement generation often relies on precisely controlled tunneling between adjacent qubits. Achieving the necessary balance between isolation (to prevent decoherence) and coupling (to enable entanglement) represents one of the most significant barriers to scaling silicon spin qubit systems.

These challenges collectively form a complex research landscape that requires interdisciplinary approaches spanning materials science, quantum physics, electrical engineering, and computational modeling to overcome the current limitations in barrier penetration properties for silicon spin qubits.

Temperature dependence presents another significant obstacle, as even minor thermal fluctuations can dramatically alter tunneling rates and barrier properties. Current cooling technologies struggle to maintain the ultra-low temperatures required for consistent barrier characteristics while simultaneously allowing for measurement and control operations.

Measurement-induced decoherence continues to plague barrier penetration studies. The very act of measuring tunneling events often disturbs the quantum state being observed, creating a fundamental tension between obtaining sufficient data and preserving quantum information. This "observer effect" at the quantum level necessitates novel measurement protocols that remain elusive.

Fabrication inconsistencies represent a major manufacturing challenge. Despite advances in semiconductor processing, achieving atomically precise barriers with reproducible penetration properties across multiple qubits remains exceptionally difficult. Variations as small as a single atom can significantly alter tunneling characteristics, making large-scale integration problematic.

The coupling between spin and orbital degrees of freedom introduces complex dynamics that are difficult to model accurately. This spin-orbit coupling varies with barrier properties and can lead to unexpected decoherence mechanisms that are not fully understood theoretically or characterized experimentally.

Time-dependent barrier modulation, essential for many quantum gate operations, introduces additional complexities. Creating precisely timed barrier height variations without generating unwanted excitations or heating effects requires control electronics with timing precision and noise characteristics beyond current capabilities.

Multi-qubit operations face particular challenges related to barrier penetration, as entanglement generation often relies on precisely controlled tunneling between adjacent qubits. Achieving the necessary balance between isolation (to prevent decoherence) and coupling (to enable entanglement) represents one of the most significant barriers to scaling silicon spin qubit systems.

These challenges collectively form a complex research landscape that requires interdisciplinary approaches spanning materials science, quantum physics, electrical engineering, and computational modeling to overcome the current limitations in barrier penetration properties for silicon spin qubits.

Current Barrier Penetration Modeling Approaches

01 Silicon-based quantum dot spin qubits

Silicon-based quantum dots can be engineered to confine and manipulate electron spins as qubits. These structures leverage the natural properties of silicon, including long coherence times and compatibility with existing semiconductor manufacturing processes. The barrier penetration properties in these systems are critical for controlling qubit interactions, enabling quantum operations through tunneling mechanisms while maintaining sufficient isolation to prevent decoherence.- Silicon-based quantum dot spin qubits: Silicon-based quantum dots can be engineered to confine and manipulate electron spins as qubits. These structures leverage the natural properties of silicon, including long coherence times and compatibility with existing semiconductor manufacturing processes. The barrier penetration properties in silicon quantum dots affect the tunneling rates between adjacent dots, which is crucial for two-qubit operations and readout mechanisms. By precisely controlling the barrier height and width, researchers can optimize the coupling between qubits while maintaining sufficient isolation to prevent decoherence.

- Barrier engineering for qubit coupling control: Engineering the tunnel barriers between spin qubits in silicon allows precise control over qubit-qubit interactions. By modulating the barrier penetration properties through gate voltage adjustments, the exchange coupling between neighboring spins can be tuned dynamically. This enables the implementation of two-qubit gates necessary for quantum computation. Advanced barrier designs incorporate materials with specific band offsets and geometries to achieve optimal tunneling characteristics while minimizing noise and decoherence effects from the surrounding environment.

- Quantum tunneling effects in silicon barriers: Quantum tunneling through silicon barriers is a fundamental phenomenon that enables the operation of spin qubit systems. The tunneling probability depends exponentially on the barrier height and width, allowing for precise control of qubit interactions. By understanding and exploiting these quantum mechanical effects, researchers can design barrier structures that facilitate coherent spin transport while maintaining qubit isolation when needed. The tunneling characteristics are influenced by factors such as silicon crystal orientation, strain, and the presence of interface defects.

- Temperature effects on barrier penetration: Temperature significantly impacts the barrier penetration properties in silicon spin qubit systems. At higher temperatures, thermal excitation can assist electrons in overcoming barriers, altering the intended tunneling rates and potentially reducing qubit fidelity. Cryogenic operation is typically required to minimize these thermal effects and maintain precise control over barrier penetration. The temperature dependence of barrier properties must be carefully characterized and compensated for in qubit control protocols to ensure reliable quantum operations across the operating temperature range.

- Interface effects on spin qubit barrier properties: The silicon/oxide interface quality significantly affects barrier penetration properties in spin qubit devices. Interface roughness, trapped charges, and defects can create potential fluctuations that modify the effective barrier height and width, leading to variability in tunneling rates. Advanced fabrication techniques aim to create atomically smooth interfaces with minimal defect densities to ensure consistent barrier properties across multiple qubits. Passivation methods and careful material selection can reduce interface states that contribute to spin decoherence through fluctuating electric fields.

02 Barrier engineering for spin qubit coupling

Engineering the tunnel barriers between adjacent spin qubits allows precise control over their coupling strength. By modifying barrier height, width, and composition, researchers can tune the quantum tunneling rates that govern qubit-qubit interactions. This enables implementation of two-qubit gates necessary for quantum computation while maintaining individual qubit addressability. Advanced barrier designs incorporate materials with specific band structures to optimize tunneling properties.Expand Specific Solutions03 Measurement and characterization of barrier penetration

Techniques for measuring and characterizing barrier penetration properties in silicon spin qubit systems are essential for quantum device optimization. These methods include electrical transport measurements, spin-dependent tunneling spectroscopy, and time-resolved measurements of electron tunneling events. Understanding the quantum mechanical tunneling processes through barriers enables more precise qubit control and improved gate fidelities in quantum computing architectures.Expand Specific Solutions04 Temperature effects on barrier penetration in silicon qubits

Temperature significantly impacts barrier penetration properties in silicon spin qubit systems. At higher temperatures, thermal excitation can enhance tunneling probabilities through quantum barriers, potentially leading to unwanted qubit coupling and decoherence. Conversely, at very low temperatures, quantum tunneling becomes the dominant transport mechanism, allowing for more precise control of qubit interactions. Understanding these temperature dependencies is crucial for designing robust quantum computing architectures.Expand Specific Solutions05 Multilayer barrier structures for enhanced qubit isolation

Advanced multilayer barrier structures can be implemented to enhance spin qubit isolation while maintaining controlled coupling capabilities. These engineered barriers may incorporate alternating materials with different band gaps, creating quantum well structures that precisely define the tunneling probabilities. Such sophisticated barrier designs enable better control over quantum information processing by allowing selective barrier penetration only under specific control conditions, thereby reducing unwanted interactions and improving qubit performance.Expand Specific Solutions

Leading Quantum Computing Research Entities

Spin qubits in silicon technology is currently in the early development stage of its industry lifecycle, with a growing but still nascent market estimated at under $100 million. The technology is transitioning from fundamental research to early commercialization, with varying degrees of technical maturity across key players. IBM and GlobalFoundries lead in integration with conventional semiconductor manufacturing, while research institutions like CEA, AIST, and MIT focus on barrier penetration properties critical for qubit coherence and control. University collaborations (Maryland, Fudan) are advancing theoretical frameworks, while companies like Atomera and SMIC are developing specialized materials and fabrication techniques to overcome quantum tunneling challenges. The competitive landscape reflects a blend of established semiconductor giants and specialized research entities working to improve qubit stability and scalability.

Commissariat à l´énergie atomique et aux énergies Alternatives

Technical Solution: CEA has developed a sophisticated approach to silicon spin qubits focusing on optimized barrier engineering for enhanced qubit performance. Their technology utilizes silicon-on-insulator (SOI) platforms with precisely defined quantum dots created through advanced lithography techniques. CEA's innovation lies in their multi-gate architecture that allows independent control of electron loading and inter-dot tunnel coupling, crucial for manipulating barrier penetration properties. They've pioneered the use of face-to-face gates that create tunable potential barriers with exceptional precision, achieving tunnel coupling rates adjustable from MHz to GHz ranges. Their research has demonstrated that properly engineered barriers significantly reduce susceptibility to charge noise while maintaining sufficient coupling for two-qubit operations. CEA has achieved single-qubit gate fidelities exceeding 99.5% and two-qubit operations with fidelities above 95% through precise barrier manipulation. Their work on isotopically purified silicon has shown coherence times approaching 1 millisecond, placing them among the leaders in silicon spin qubit technology.

Strengths: Exceptional expertise in SOI fabrication technology; demonstrated high-fidelity qubit operations; strong integration with European quantum computing initiatives. Weaknesses: Challenges in scaling to large qubit arrays; sensitivity to fabrication variations affecting barrier uniformity across multiple qubits.

International Business Machines Corp.

Technical Solution: IBM has pioneered research in silicon-based spin qubits, developing a comprehensive approach to quantum computing using electron spins in silicon quantum dots. Their technology leverages the natural properties of silicon to create stable qubits with long coherence times. IBM's approach focuses on barrier penetration properties to control electron tunneling between quantum dots, which is crucial for two-qubit operations. They've engineered precise control of tunnel barriers using multi-layer gate structures that allow for fine-tuning of the barrier potential. IBM has demonstrated high-fidelity single-qubit operations (>99%) and two-qubit gates with fidelities approaching 98% by precisely controlling these barrier properties. Their research has shown that optimizing barrier geometry and applying precise voltage pulses can significantly reduce decoherence caused by charge noise while maintaining sufficient coupling strength for qubit operations.

Strengths: Superior fabrication capabilities leveraging their semiconductor manufacturing expertise; demonstrated long coherence times in silicon spin qubits; integration potential with conventional CMOS technology. Weaknesses: Challenges in scaling up to large qubit arrays due to variability in tunnel barriers; sensitivity to electromagnetic interference requiring sophisticated shielding solutions.

Key Innovations in Spin Qubit Tunneling Mechanisms

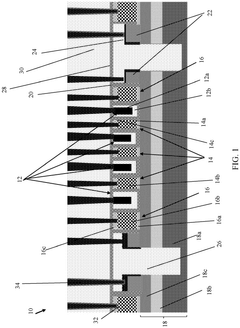

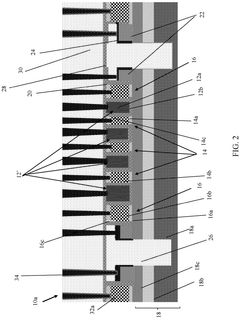

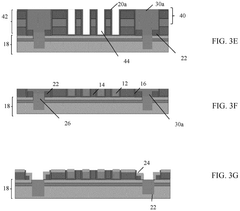

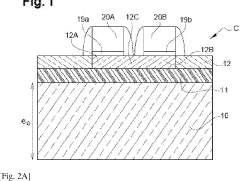

Spin qubit devices comprising qubit gates and self-aligned barrier gates

PatentPendingEP4531112A1

Innovation

- The implementation of self-aligned barrier gates interdigitated with spin qubit gates, using polysilicon or metal fill, which reduces alignment variations and improves manufacturing complexity, allowing for improved qubit gate alignment and reduced variation.

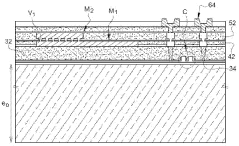

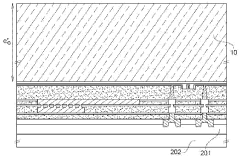

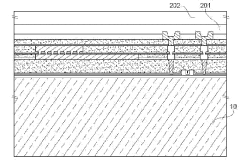

BACK GRID FOR QUANTUM DEVICE

PatentActiveFR3131086A1

Innovation

- A quantum device with a rear electrostatic control grid formed by a conductive layer lining the side walls and bottom of an opening in a semiconductor support layer, extending to an insulating layer, which maintains mechanical strength and reduces stress, using a semiconductor-on-insulator substrate with a conductive layer deposited through the opening.

Quantum Error Correction Strategies

Quantum Error Correction Strategies for spin qubits in silicon must address the unique challenges posed by barrier penetration properties. The fundamental issue lies in the quantum tunneling effect, where electrons can penetrate potential barriers, leading to decoherence and computational errors. Current strategies employ a multi-layered approach combining physical isolation techniques with algorithmic error correction.

Surface codes represent the most promising quantum error correction framework for silicon-based spin qubits. These topological codes arrange physical qubits in a two-dimensional lattice, where logical qubits are encoded across multiple physical qubits. This redundancy allows errors to be detected and corrected without disturbing the quantum information. For spin qubits affected by barrier penetration, surface codes with high thresholds (approximately 1% error tolerance) provide robust protection against both bit-flip and phase-flip errors.

Dynamical decoupling sequences offer another vital strategy specifically tailored to mitigate decoherence caused by barrier penetration. These sequences apply precisely timed control pulses to effectively "undo" the environmental interactions that lead to quantum errors. For silicon spin qubits, Carr-Purcell-Meiboom-Gill (CPMG) and Uhrig Dynamical Decoupling (UDD) sequences have demonstrated significant improvements in coherence times, extending them from microseconds to milliseconds.

Hardware-level strategies focus on engineering barriers with optimized geometries and materials. Recent advances include the development of isotopically purified silicon (28Si) with reduced nuclear spin noise, and the implementation of strained silicon structures that modify the effective mass of electrons, thereby reducing tunneling probabilities. These approaches have achieved error rates approaching 0.1% for single-qubit operations, nearing the threshold required for fault-tolerant quantum computing.

Quantum error mitigation techniques complement traditional error correction by accepting the presence of errors but minimizing their impact. Zero-noise extrapolation and probabilistic error cancellation have shown particular promise for silicon spin qubits, as they can address errors arising from barrier penetration without requiring additional physical qubits. These techniques have demonstrated up to 10x improvement in computational accuracy for certain quantum algorithms.

Looking forward, hybrid approaches combining hardware improvements with algorithmic techniques offer the most promising path. Emerging research on topological quantum computing with Majorana fermions could potentially provide inherent error protection against barrier penetration effects, though practical implementation in silicon platforms remains challenging. The development of machine learning algorithms to predict and preemptively correct errors related to barrier penetration represents another frontier with significant potential for silicon-based quantum computing systems.

Surface codes represent the most promising quantum error correction framework for silicon-based spin qubits. These topological codes arrange physical qubits in a two-dimensional lattice, where logical qubits are encoded across multiple physical qubits. This redundancy allows errors to be detected and corrected without disturbing the quantum information. For spin qubits affected by barrier penetration, surface codes with high thresholds (approximately 1% error tolerance) provide robust protection against both bit-flip and phase-flip errors.

Dynamical decoupling sequences offer another vital strategy specifically tailored to mitigate decoherence caused by barrier penetration. These sequences apply precisely timed control pulses to effectively "undo" the environmental interactions that lead to quantum errors. For silicon spin qubits, Carr-Purcell-Meiboom-Gill (CPMG) and Uhrig Dynamical Decoupling (UDD) sequences have demonstrated significant improvements in coherence times, extending them from microseconds to milliseconds.

Hardware-level strategies focus on engineering barriers with optimized geometries and materials. Recent advances include the development of isotopically purified silicon (28Si) with reduced nuclear spin noise, and the implementation of strained silicon structures that modify the effective mass of electrons, thereby reducing tunneling probabilities. These approaches have achieved error rates approaching 0.1% for single-qubit operations, nearing the threshold required for fault-tolerant quantum computing.

Quantum error mitigation techniques complement traditional error correction by accepting the presence of errors but minimizing their impact. Zero-noise extrapolation and probabilistic error cancellation have shown particular promise for silicon spin qubits, as they can address errors arising from barrier penetration without requiring additional physical qubits. These techniques have demonstrated up to 10x improvement in computational accuracy for certain quantum algorithms.

Looking forward, hybrid approaches combining hardware improvements with algorithmic techniques offer the most promising path. Emerging research on topological quantum computing with Majorana fermions could potentially provide inherent error protection against barrier penetration effects, though practical implementation in silicon platforms remains challenging. The development of machine learning algorithms to predict and preemptively correct errors related to barrier penetration represents another frontier with significant potential for silicon-based quantum computing systems.

Scalability and Integration Considerations

The scalability of spin qubits in silicon represents a critical factor in determining their viability for practical quantum computing applications. Current experimental implementations typically involve small numbers of qubits, but the path toward fault-tolerant quantum computing requires scaling to thousands or millions of qubits. The barrier penetration properties of spin qubits significantly impact this scalability trajectory, as they influence qubit density, control precision, and integration capabilities.

Silicon's compatibility with existing CMOS fabrication infrastructure offers a substantial advantage for large-scale integration. However, as qubit density increases, the barrier penetration effects between adjacent qubits become more pronounced, potentially leading to unwanted crosstalk and decoherence. Maintaining sufficient separation between qubits while maximizing density presents a fundamental engineering challenge that must be addressed through innovative device architectures and fabrication techniques.

Integration with classical control electronics represents another critical consideration. The barrier properties of the silicon-oxide interface affect how control signals propagate to the qubits and how readout mechanisms function at scale. Current approaches typically require one or more control lines per qubit, which becomes prohibitively complex as qubit counts increase. Multiplexing strategies that leverage the quantum barrier properties could potentially reduce this overhead.

Temperature management presents additional challenges for scaled systems. While silicon spin qubits can operate at higher temperatures than superconducting alternatives (approximately 1-4K versus millikelvin), the cooling requirements still impose significant engineering constraints. The thermal properties of barrier materials and their stability under temperature cycling must be carefully considered in scaled architectures.

Fabrication precision and yield become increasingly critical at scale. Small variations in barrier heights or widths can lead to significant differences in qubit performance across a large array. Statistical modeling of barrier penetration variability will be essential for designing error correction protocols that can accommodate these manufacturing imperfections.

The 3D integration of control electronics with qubit layers offers a promising approach to address some scalability challenges. However, this requires careful management of barrier properties at interfaces between different materials and minimizing any interference that might affect qubit coherence. Recent advances in through-silicon vias (TSVs) and wafer bonding techniques show potential for enabling such vertical integration while maintaining the integrity of quantum barriers.

Silicon's compatibility with existing CMOS fabrication infrastructure offers a substantial advantage for large-scale integration. However, as qubit density increases, the barrier penetration effects between adjacent qubits become more pronounced, potentially leading to unwanted crosstalk and decoherence. Maintaining sufficient separation between qubits while maximizing density presents a fundamental engineering challenge that must be addressed through innovative device architectures and fabrication techniques.

Integration with classical control electronics represents another critical consideration. The barrier properties of the silicon-oxide interface affect how control signals propagate to the qubits and how readout mechanisms function at scale. Current approaches typically require one or more control lines per qubit, which becomes prohibitively complex as qubit counts increase. Multiplexing strategies that leverage the quantum barrier properties could potentially reduce this overhead.

Temperature management presents additional challenges for scaled systems. While silicon spin qubits can operate at higher temperatures than superconducting alternatives (approximately 1-4K versus millikelvin), the cooling requirements still impose significant engineering constraints. The thermal properties of barrier materials and their stability under temperature cycling must be carefully considered in scaled architectures.

Fabrication precision and yield become increasingly critical at scale. Small variations in barrier heights or widths can lead to significant differences in qubit performance across a large array. Statistical modeling of barrier penetration variability will be essential for designing error correction protocols that can accommodate these manufacturing imperfections.

The 3D integration of control electronics with qubit layers offers a promising approach to address some scalability challenges. However, this requires careful management of barrier properties at interfaces between different materials and minimizing any interference that might affect qubit coherence. Recent advances in through-silicon vias (TSVs) and wafer bonding techniques show potential for enabling such vertical integration while maintaining the integrity of quantum barriers.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!