Spin Qubits in Silicon: Application in Advanced Simulations

OCT 10, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Silicon Spin Qubit Evolution and Research Objectives

Spin qubits in silicon have emerged as a promising platform for quantum computing, evolving significantly over the past two decades. The journey began with the theoretical proposal by Kane in 1998, suggesting the use of nuclear spins of phosphorus donors in silicon as qubits. This seminal work laid the foundation for silicon-based quantum computing research, highlighting silicon's potential compatibility with existing semiconductor manufacturing infrastructure.

The field gained momentum in the early 2000s with experimental demonstrations of single-electron spin control in quantum dots, followed by the achievement of coherent manipulation of electron spins in silicon in 2010. These milestones established silicon as a viable quantum computing platform, leveraging its natural abundance of spin-zero isotopes that provide a "quiet" environment for qubits.

Recent years have witnessed remarkable progress in extending coherence times, with T2 times exceeding seconds under optimal conditions, and significant improvements in gate fidelities approaching the threshold required for fault-tolerant quantum computing. The development of multi-qubit systems and demonstration of two-qubit gates represent critical advances toward scalable quantum processors.

The technical evolution has been accompanied by growing interest in applying silicon spin qubits to advanced simulation problems. Quantum simulations of complex physical systems, particularly in materials science and chemistry, represent a near-term application where quantum advantage might be achieved before full-scale fault-tolerant quantum computing becomes available.

Current research objectives focus on several key areas: improving qubit coherence times through material engineering and isotopic purification; enhancing gate fidelities to exceed the fault-tolerance threshold; developing scalable architectures that can accommodate thousands of qubits; and designing specialized algorithms optimized for silicon spin qubit hardware characteristics.

Specifically for advanced simulations, research aims to develop hybrid quantum-classical algorithms that can leverage the strengths of silicon spin qubits while mitigating their limitations. This includes exploring variational algorithms for quantum chemistry simulations and developing error mitigation techniques suitable for the noise characteristics of silicon spin qubits.

The long-term technical goal is to achieve quantum advantage in practical simulation problems that are intractable for classical computers. This requires not only hardware improvements but also the development of a complete software stack and simulation frameworks specifically designed for silicon spin qubit systems, enabling researchers to efficiently map simulation problems onto the quantum hardware.

The field gained momentum in the early 2000s with experimental demonstrations of single-electron spin control in quantum dots, followed by the achievement of coherent manipulation of electron spins in silicon in 2010. These milestones established silicon as a viable quantum computing platform, leveraging its natural abundance of spin-zero isotopes that provide a "quiet" environment for qubits.

Recent years have witnessed remarkable progress in extending coherence times, with T2 times exceeding seconds under optimal conditions, and significant improvements in gate fidelities approaching the threshold required for fault-tolerant quantum computing. The development of multi-qubit systems and demonstration of two-qubit gates represent critical advances toward scalable quantum processors.

The technical evolution has been accompanied by growing interest in applying silicon spin qubits to advanced simulation problems. Quantum simulations of complex physical systems, particularly in materials science and chemistry, represent a near-term application where quantum advantage might be achieved before full-scale fault-tolerant quantum computing becomes available.

Current research objectives focus on several key areas: improving qubit coherence times through material engineering and isotopic purification; enhancing gate fidelities to exceed the fault-tolerance threshold; developing scalable architectures that can accommodate thousands of qubits; and designing specialized algorithms optimized for silicon spin qubit hardware characteristics.

Specifically for advanced simulations, research aims to develop hybrid quantum-classical algorithms that can leverage the strengths of silicon spin qubits while mitigating their limitations. This includes exploring variational algorithms for quantum chemistry simulations and developing error mitigation techniques suitable for the noise characteristics of silicon spin qubits.

The long-term technical goal is to achieve quantum advantage in practical simulation problems that are intractable for classical computers. This requires not only hardware improvements but also the development of a complete software stack and simulation frameworks specifically designed for silicon spin qubit systems, enabling researchers to efficiently map simulation problems onto the quantum hardware.

Market Analysis for Quantum Simulation Technologies

The quantum simulation market is experiencing significant growth, driven by increasing demand for advanced computational capabilities across various industries. Current market estimates value the global quantum computing market at approximately $500 million, with quantum simulation technologies representing about 15% of this segment. This market is projected to grow at a compound annual growth rate of 30% over the next five years, potentially reaching $2.5 billion by 2028.

The demand for quantum simulation technologies is particularly strong in pharmaceutical and materials science sectors, where complex molecular interactions require computational power beyond classical systems. Approximately 40% of current quantum simulation applications are focused on drug discovery and development, where simulating quantum mechanical properties of molecules can potentially reduce R&D timelines by years and save billions in development costs.

Silicon-based spin qubits represent a promising segment within this market, offering advantages in scalability and compatibility with existing semiconductor manufacturing infrastructure. Market analysis indicates that silicon spin qubit technologies could capture up to 25% of the quantum simulation market within the next decade, particularly as their coherence times and gate fidelities continue to improve.

Key market drivers include increasing research funding from both public and private sectors, with government initiatives worldwide committing over $20 billion to quantum technology development. Corporate investment has similarly accelerated, with venture capital funding in quantum technologies reaching $1.7 billion in 2022 alone.

Customer segments for quantum simulation technologies include pharmaceutical companies, materials science researchers, financial institutions, and increasingly, manufacturing organizations seeking to optimize complex processes. Early adopters are primarily large enterprises with substantial R&D budgets, though the market is expected to broaden as quantum simulation becomes more accessible through cloud-based services.

Regional analysis shows North America leading with approximately 45% market share, followed by Europe (30%) and Asia-Pacific (20%). However, China's aggressive investment in quantum technologies may shift this distribution significantly in the coming years.

Market barriers include high implementation costs, technical complexity, and the current limited accessibility of quantum simulation technologies. Additionally, the shortage of qualified quantum computing specialists represents a significant constraint on market growth, with industry reports indicating a global deficit of over 5,000 quantum technology professionals.

The competitive landscape features both established technology corporations and specialized quantum computing startups, with increasing partnership activity between hardware developers, software providers, and end-users to create comprehensive quantum simulation solutions tailored to specific industry applications.

The demand for quantum simulation technologies is particularly strong in pharmaceutical and materials science sectors, where complex molecular interactions require computational power beyond classical systems. Approximately 40% of current quantum simulation applications are focused on drug discovery and development, where simulating quantum mechanical properties of molecules can potentially reduce R&D timelines by years and save billions in development costs.

Silicon-based spin qubits represent a promising segment within this market, offering advantages in scalability and compatibility with existing semiconductor manufacturing infrastructure. Market analysis indicates that silicon spin qubit technologies could capture up to 25% of the quantum simulation market within the next decade, particularly as their coherence times and gate fidelities continue to improve.

Key market drivers include increasing research funding from both public and private sectors, with government initiatives worldwide committing over $20 billion to quantum technology development. Corporate investment has similarly accelerated, with venture capital funding in quantum technologies reaching $1.7 billion in 2022 alone.

Customer segments for quantum simulation technologies include pharmaceutical companies, materials science researchers, financial institutions, and increasingly, manufacturing organizations seeking to optimize complex processes. Early adopters are primarily large enterprises with substantial R&D budgets, though the market is expected to broaden as quantum simulation becomes more accessible through cloud-based services.

Regional analysis shows North America leading with approximately 45% market share, followed by Europe (30%) and Asia-Pacific (20%). However, China's aggressive investment in quantum technologies may shift this distribution significantly in the coming years.

Market barriers include high implementation costs, technical complexity, and the current limited accessibility of quantum simulation technologies. Additionally, the shortage of qualified quantum computing specialists represents a significant constraint on market growth, with industry reports indicating a global deficit of over 5,000 quantum technology professionals.

The competitive landscape features both established technology corporations and specialized quantum computing startups, with increasing partnership activity between hardware developers, software providers, and end-users to create comprehensive quantum simulation solutions tailored to specific industry applications.

Silicon Spin Qubit Technical Challenges

Silicon spin qubits face several significant technical challenges that currently limit their widespread application in advanced quantum simulations. The primary obstacle remains coherence time limitations, with typical T2 times ranging from microseconds to milliseconds, which restricts the complexity of quantum operations that can be performed before information is lost to environmental noise. This decoherence primarily stems from interactions with nuclear spins in the silicon lattice and charge noise from nearby interfaces and impurities.

Qubit initialization and readout fidelity presents another major challenge. Current single-shot readout fidelities hover around 98%, falling short of the 99.9% threshold typically required for fault-tolerant quantum computing. The speed of these operations also remains problematic, with initialization times often exceeding microseconds, creating a bottleneck for computational throughput in simulation applications.

Scaling beyond small qubit arrays introduces significant engineering hurdles. As the number of qubits increases, maintaining uniform control over each qubit becomes exponentially more difficult. The dense wiring required for individual qubit control creates cross-talk issues and heat dissipation problems that can destabilize the quantum system. Current architectures struggle to maintain consistent qubit-to-qubit coupling strengths across larger arrays, leading to non-uniform gate fidelities.

Fabrication precision represents a critical limitation, as atomic-scale variations in the silicon substrate can dramatically alter qubit properties. Even state-of-the-art semiconductor manufacturing processes struggle to achieve the nanometer-scale precision required for reliable, identical qubit formation. This variability necessitates individual calibration procedures for each qubit, significantly complicating the scaling process.

Gate operation fidelities, while improving, still fall short of theoretical requirements for complex simulations. Two-qubit gates typically demonstrate fidelities between 95-99%, whereas advanced quantum simulations may require fidelities exceeding 99.9%. The speed of these operations also remains suboptimal, with typical gate times in the microsecond range limiting the computational advantage for time-sensitive simulations.

Integration with classical control electronics presents additional challenges. The cryogenic temperatures required for silicon spin qubit operation (typically below 100 mK) are incompatible with conventional electronics. This necessitates either long signal paths that introduce latency and noise or the development of specialized cryogenic electronics that can function at these extreme temperatures without disturbing the quantum system.

Qubit initialization and readout fidelity presents another major challenge. Current single-shot readout fidelities hover around 98%, falling short of the 99.9% threshold typically required for fault-tolerant quantum computing. The speed of these operations also remains problematic, with initialization times often exceeding microseconds, creating a bottleneck for computational throughput in simulation applications.

Scaling beyond small qubit arrays introduces significant engineering hurdles. As the number of qubits increases, maintaining uniform control over each qubit becomes exponentially more difficult. The dense wiring required for individual qubit control creates cross-talk issues and heat dissipation problems that can destabilize the quantum system. Current architectures struggle to maintain consistent qubit-to-qubit coupling strengths across larger arrays, leading to non-uniform gate fidelities.

Fabrication precision represents a critical limitation, as atomic-scale variations in the silicon substrate can dramatically alter qubit properties. Even state-of-the-art semiconductor manufacturing processes struggle to achieve the nanometer-scale precision required for reliable, identical qubit formation. This variability necessitates individual calibration procedures for each qubit, significantly complicating the scaling process.

Gate operation fidelities, while improving, still fall short of theoretical requirements for complex simulations. Two-qubit gates typically demonstrate fidelities between 95-99%, whereas advanced quantum simulations may require fidelities exceeding 99.9%. The speed of these operations also remains suboptimal, with typical gate times in the microsecond range limiting the computational advantage for time-sensitive simulations.

Integration with classical control electronics presents additional challenges. The cryogenic temperatures required for silicon spin qubit operation (typically below 100 mK) are incompatible with conventional electronics. This necessitates either long signal paths that introduce latency and noise or the development of specialized cryogenic electronics that can function at these extreme temperatures without disturbing the quantum system.

Current Silicon Spin Qubit Implementation Approaches

01 Silicon-based quantum dot spin qubits

Silicon quantum dots can be used to create spin qubits by confining electrons in nanoscale structures. These quantum dots allow for precise control of individual electron spins, which can represent quantum bits. Silicon provides an excellent host material due to its compatibility with existing semiconductor manufacturing processes and the possibility of achieving long coherence times. The spin states of electrons in silicon quantum dots can be manipulated using electrical or magnetic fields for quantum information processing.- Silicon-based quantum dot spin qubits: Silicon quantum dots can be used to create spin qubits for quantum computing applications. These qubits leverage the spin states of electrons confined in silicon structures to store and process quantum information. Silicon provides an excellent host material due to its compatibility with existing semiconductor manufacturing processes and the long coherence times of electron spins in silicon, particularly in isotopically purified silicon-28.

- Multi-qubit architectures and coupling mechanisms: Advanced architectures for multiple spin qubits in silicon involve various coupling mechanisms between qubits to enable quantum operations. These include exchange coupling between adjacent quantum dots, long-range coupling using cavity quantum electrodynamics, and hybrid systems combining different qubit types. Such architectures are essential for scaling up quantum processors and implementing quantum error correction protocols.

- Readout and control techniques for silicon spin qubits: Various techniques have been developed for the precise readout and control of spin qubits in silicon. These include single-shot readout methods using spin-to-charge conversion, microwave-based control of spin states, and gate-based dispersive readout. Advanced control techniques enable high-fidelity quantum gate operations necessary for quantum algorithms and error correction.

- Fabrication methods for silicon spin qubit devices: Specialized fabrication techniques are required to create silicon spin qubit devices with high precision and reliability. These methods include advanced lithography processes, selective doping techniques, and precise placement of control electrodes. The fabrication approaches aim to minimize sources of noise and decoherence while enabling scalable manufacturing of quantum devices compatible with conventional CMOS technology.

- Integration with classical electronics and scaling approaches: Integration of silicon spin qubits with classical control electronics is crucial for practical quantum computing systems. This includes on-chip control circuitry, cryogenic electronics, and multiplexing schemes to address the wiring bottleneck in scaled-up systems. Various architectural approaches have been developed to enable the scaling of silicon spin qubit systems to the large numbers required for fault-tolerant quantum computing.

02 Fabrication methods for silicon spin qubits

Various fabrication techniques have been developed to create spin qubits in silicon. These include methods for precise dopant placement, gate-defined quantum dots, and silicon-germanium heterostructures. Advanced lithography and etching processes enable the creation of nanoscale structures necessary for qubit operation. Fabrication methods also focus on reducing interface defects and improving material purity to enhance qubit performance and coherence times.Expand Specific Solutions03 Readout and control mechanisms for silicon spin qubits

Effective readout and control mechanisms are essential for operating silicon spin qubits. These include techniques for spin-to-charge conversion, gate-based dispersive readout, and single-shot measurements. Control mechanisms involve microwave pulses for spin manipulation, exchange coupling between adjacent qubits, and dynamic decoupling sequences to mitigate decoherence. Advanced readout schemes can achieve high fidelity measurements while minimizing back-action on the quantum state.Expand Specific Solutions04 Scalable architectures for silicon spin qubit systems

Developing scalable architectures is crucial for practical quantum computing with silicon spin qubits. These architectures include designs for qubit arrays, interconnects, and control electronics that can be scaled to larger systems. Approaches include crossbar arrays, quantum bus structures, and modular designs that allow for error correction. Scalable architectures must address challenges such as cross-talk, control line routing, and maintaining coherence across the entire system.Expand Specific Solutions05 Error correction and quantum algorithms for silicon spin qubits

Error correction techniques and quantum algorithms specifically adapted for silicon spin qubits are essential for practical quantum computing. These include surface codes, decoherence-free subspaces, and dynamical decoupling sequences tailored to the noise profile of silicon systems. Quantum algorithms optimized for the constraints and capabilities of silicon spin qubits can achieve computational advantages despite limited qubit counts. Implementation strategies focus on maximizing algorithm performance while minimizing resource requirements.Expand Specific Solutions

Leading Organizations in Silicon Spin Qubit Research

Spin Qubits in Silicon technology is currently in the early growth phase, with a rapidly expanding market projected to reach significant scale as quantum computing applications mature. The technology demonstrates moderate maturity, with key players like Intel, IBM, and Google driving commercial development while research institutions such as MIT, USTC, and Delft University advance fundamental capabilities. Imec and CEA are establishing critical fabrication standards, while Origin Quantum and GlobalFoundries work on manufacturing scalability. The competitive landscape shows a balanced ecosystem of semiconductor giants, specialized quantum startups, and academic institutions collaborating to overcome technical challenges in qubit coherence, control electronics, and error correction necessary for practical quantum simulation applications.

Intel Corp.

Technical Solution: Intel has developed a silicon spin qubit platform leveraging their advanced semiconductor manufacturing capabilities. Their approach focuses on fabricating spin qubits using their 300mm manufacturing process, the same used for commercial microprocessors, providing a pathway to large-scale quantum processors[1]. Intel's technology utilizes silicon-28 enriched wafers to minimize nuclear spin noise and employs a split-gate architecture to form quantum dots that trap individual electrons. Their Horse Ridge cryogenic control chip, designed specifically for quantum computing, enables efficient control of multiple spin qubits while reducing the wiring complexity that typically limits quantum processor scaling[3]. Intel has demonstrated single-qubit gate fidelities exceeding 99.5% and two-qubit operations with fidelities approaching 98%. Their integration strategy includes on-chip multiplexing of control signals and co-integration of classical control electronics with quantum devices, addressing key challenges in building practical quantum computers. Intel's recent advancements include developing specialized test chips that allow rapid characterization of hundreds of quantum dots simultaneously[6].

Strengths: Leverages Intel's world-class semiconductor manufacturing infrastructure; potential for high-volume production of quantum processors; integrated cryogenic control electronics reduce system complexity; demonstrated high qubit uniformity across wafers. Weaknesses: Relatively new entrant to spin qubit research compared to academic leaders; faces challenges in achieving competitive two-qubit gate fidelities; requires extremely low temperatures for operation; still working to demonstrate larger multi-qubit algorithms.

Commissariat à l´énergie atomique et aux énergies Alternatives

Technical Solution: CEA (Commissariat à l'énergie atomique et aux énergies alternatives) has developed a distinctive silicon spin qubit platform through their quantum computing research division. Their approach centers on silicon-on-insulator (SOI) technology, where they create quantum dots in silicon nanowire transistors fabricated using industry-standard CMOS processes[2]. CEA's architecture employs both electron and hole spins as qubits, with recent focus on hole spin qubits that offer advantages in all-electrical control through strong spin-orbit coupling. Their technology includes integrated charge sensors for high-fidelity qubit readout and initialization. CEA researchers have demonstrated coherent manipulation of hole spin qubits with fidelities exceeding 99% for single-qubit gates and have shown coupling between adjacent qubits through direct exchange interaction[4]. Their platform benefits from close collaboration with semiconductor industry partners, enabling fabrication on 300mm wafers using industrial processes. Recent advancements include demonstrating coherent coupling between spin qubits and microwave photons in superconducting resonators, opening pathways to long-distance qubit coupling[7].

Strengths: Utilizes established CMOS manufacturing processes; hole spin qubits offer simplified all-electrical control; strong integration with European semiconductor ecosystem; demonstrated operation at relatively higher temperatures than electron spin qubits. Weaknesses: Hole spin qubits typically have shorter coherence times than electron spins; SOI platform faces challenges in scaling to very large qubit numbers; requires precise control of interface quality between silicon and oxide layers; still working to improve two-qubit gate fidelities.

Key Patents and Breakthroughs in Spin Qubit Technology

Phononic quantum networks of solid-state spins with alternating and frequency-selective waveguides

PatentActiveUS11113622B2

Innovation

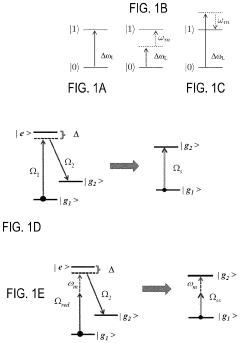

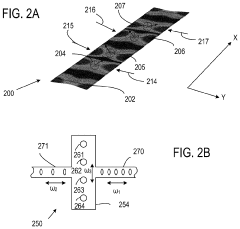

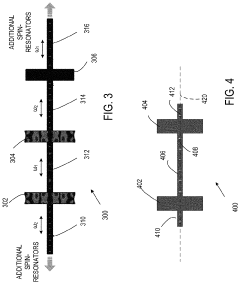

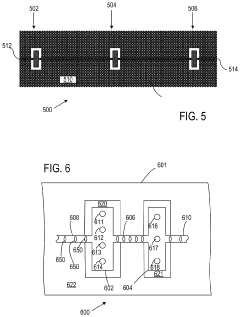

- The use of phononic waveguides coupled with spin-mechanical resonators on a diamond membrane, which allow for directional transfer of quantum states between qubits and internal state transfer within resonators, utilizing periodic variations in acoustic impedance to define non-overlapping frequency bands for acoustic coupling.

Quantum Error Correction Strategies for Silicon Platforms

Quantum Error Correction (QEC) represents a critical frontier for silicon-based spin qubit systems in advanced simulation applications. Silicon platforms offer promising advantages for quantum computing due to their compatibility with existing semiconductor manufacturing infrastructure, but they remain susceptible to various error sources that can compromise computational integrity. Current QEC strategies for silicon platforms primarily focus on surface codes and topological codes, which have demonstrated theoretical error thresholds compatible with silicon spin qubit fidelity rates.

The implementation of QEC in silicon systems requires addressing specific challenges related to the physical properties of spin qubits. Decoherence mechanisms in silicon, including hyperfine interactions with nuclear spins and charge noise, necessitate tailored error correction approaches. Recent advancements have shown that dynamical decoupling sequences can be effectively integrated with QEC protocols to extend coherence times while maintaining error correction capabilities.

Hardware-efficient QEC codes specifically designed for silicon architectures have emerged as a promising direction. These include the development of small stabilizer codes that can be implemented with limited qubit connectivity, a common constraint in silicon quantum dot arrays. The "heavy-hexagon" code variant has shown particular promise for silicon implementations due to its reduced connectivity requirements while maintaining reasonable error thresholds.

Leakage errors, where qubits evolve outside the computational subspace, present a unique challenge for silicon spin qubits. Advanced leakage reduction units (LRUs) have been developed to detect and correct these errors without disrupting the underlying QEC protocol. These techniques utilize auxiliary qubits and specialized measurement sequences to identify and reset leakage events.

Fault-tolerant logical operations represent another critical aspect of QEC strategies for silicon platforms. Transversal gates, which naturally prevent error propagation, have been adapted for silicon architectures with restricted connectivity. Additionally, lattice surgery techniques provide a pathway for implementing logical operations between encoded qubits while maintaining the error correction properties of the underlying code.

Recent experimental demonstrations have validated several QEC concepts in small silicon qubit arrays. Notable achievements include the implementation of the three-qubit bit-flip code and demonstration of error detection using the four-qubit Bacon-Shor subsystem code. These proof-of-principle experiments, while still limited in scale, provide crucial validation for the theoretical frameworks underpinning silicon-based QEC strategies.

Looking forward, the integration of machine learning techniques with QEC protocols shows promise for optimizing error correction in silicon systems. Adaptive protocols that can identify and respond to system-specific noise profiles may significantly enhance the performance of QEC in practical silicon quantum processors used for advanced simulation applications.

The implementation of QEC in silicon systems requires addressing specific challenges related to the physical properties of spin qubits. Decoherence mechanisms in silicon, including hyperfine interactions with nuclear spins and charge noise, necessitate tailored error correction approaches. Recent advancements have shown that dynamical decoupling sequences can be effectively integrated with QEC protocols to extend coherence times while maintaining error correction capabilities.

Hardware-efficient QEC codes specifically designed for silicon architectures have emerged as a promising direction. These include the development of small stabilizer codes that can be implemented with limited qubit connectivity, a common constraint in silicon quantum dot arrays. The "heavy-hexagon" code variant has shown particular promise for silicon implementations due to its reduced connectivity requirements while maintaining reasonable error thresholds.

Leakage errors, where qubits evolve outside the computational subspace, present a unique challenge for silicon spin qubits. Advanced leakage reduction units (LRUs) have been developed to detect and correct these errors without disrupting the underlying QEC protocol. These techniques utilize auxiliary qubits and specialized measurement sequences to identify and reset leakage events.

Fault-tolerant logical operations represent another critical aspect of QEC strategies for silicon platforms. Transversal gates, which naturally prevent error propagation, have been adapted for silicon architectures with restricted connectivity. Additionally, lattice surgery techniques provide a pathway for implementing logical operations between encoded qubits while maintaining the error correction properties of the underlying code.

Recent experimental demonstrations have validated several QEC concepts in small silicon qubit arrays. Notable achievements include the implementation of the three-qubit bit-flip code and demonstration of error detection using the four-qubit Bacon-Shor subsystem code. These proof-of-principle experiments, while still limited in scale, provide crucial validation for the theoretical frameworks underpinning silicon-based QEC strategies.

Looking forward, the integration of machine learning techniques with QEC protocols shows promise for optimizing error correction in silicon systems. Adaptive protocols that can identify and respond to system-specific noise profiles may significantly enhance the performance of QEC in practical silicon quantum processors used for advanced simulation applications.

Scalability and Integration Pathways for Spin Qubit Systems

The scalability of spin qubit systems represents a critical frontier in quantum computing research, particularly for silicon-based implementations. Current laboratory demonstrations have successfully manipulated small arrays of spin qubits, typically ranging from 2 to 6 qubits. However, practical quantum simulation applications require scaling to hundreds or thousands of qubits, presenting significant integration challenges.

Several promising pathways for scaling silicon spin qubit systems have emerged in recent research. The crossbar architecture, which utilizes shared control lines to address multiple qubits, offers a potential solution for reducing the number of control wires needed as qubit counts increase. This approach could potentially support arrays of up to 1,000 qubits while maintaining manageable interconnect complexity.

Integration with conventional CMOS technology presents another viable scaling strategy. Leading semiconductor manufacturers have begun exploring the fabrication of spin qubits using modified versions of standard semiconductor manufacturing processes. This compatibility with existing fabrication infrastructure could accelerate the development of large-scale qubit arrays while leveraging decades of semiconductor scaling expertise.

Modular quantum computing architectures represent a third scaling pathway. These designs incorporate quantum interconnects between smaller qubit modules, potentially overcoming the physical limitations of monolithic approaches. Recent demonstrations of coherent spin qubit coupling across chip boundaries suggest this approach may enable scaling beyond what single-die implementations can achieve.

Cryogenic control electronics integration stands as a crucial enabling technology for large-scale spin qubit systems. By positioning control electronics closer to the qubits within the cryogenic environment, researchers can reduce wiring complexity and signal degradation. Several research groups have demonstrated cryogenic multiplexers and digital-to-analog converters operating at temperatures below 4 Kelvin.

Error correction implementation represents perhaps the most significant scaling challenge. Current spin qubit fidelities remain below the thresholds required for fault-tolerant quantum computing. Surface code implementations for spin qubits would require significant advances in qubit uniformity and control precision, with current estimates suggesting the need for 10-100 physical qubits per logical qubit.

The timeline for achieving practical scale remains uncertain, with most industry roadmaps projecting 5-10 years before spin qubit systems reach the 100+ qubit threshold needed for quantum advantage in simulation applications. However, the inherent compatibility with semiconductor manufacturing processes gives silicon spin qubits a potential advantage in the long-term race toward large-scale quantum computing systems.

Several promising pathways for scaling silicon spin qubit systems have emerged in recent research. The crossbar architecture, which utilizes shared control lines to address multiple qubits, offers a potential solution for reducing the number of control wires needed as qubit counts increase. This approach could potentially support arrays of up to 1,000 qubits while maintaining manageable interconnect complexity.

Integration with conventional CMOS technology presents another viable scaling strategy. Leading semiconductor manufacturers have begun exploring the fabrication of spin qubits using modified versions of standard semiconductor manufacturing processes. This compatibility with existing fabrication infrastructure could accelerate the development of large-scale qubit arrays while leveraging decades of semiconductor scaling expertise.

Modular quantum computing architectures represent a third scaling pathway. These designs incorporate quantum interconnects between smaller qubit modules, potentially overcoming the physical limitations of monolithic approaches. Recent demonstrations of coherent spin qubit coupling across chip boundaries suggest this approach may enable scaling beyond what single-die implementations can achieve.

Cryogenic control electronics integration stands as a crucial enabling technology for large-scale spin qubit systems. By positioning control electronics closer to the qubits within the cryogenic environment, researchers can reduce wiring complexity and signal degradation. Several research groups have demonstrated cryogenic multiplexers and digital-to-analog converters operating at temperatures below 4 Kelvin.

Error correction implementation represents perhaps the most significant scaling challenge. Current spin qubit fidelities remain below the thresholds required for fault-tolerant quantum computing. Surface code implementations for spin qubits would require significant advances in qubit uniformity and control precision, with current estimates suggesting the need for 10-100 physical qubits per logical qubit.

The timeline for achieving practical scale remains uncertain, with most industry roadmaps projecting 5-10 years before spin qubit systems reach the 100+ qubit threshold needed for quantum advantage in simulation applications. However, the inherent compatibility with semiconductor manufacturing processes gives silicon spin qubits a potential advantage in the long-term race toward large-scale quantum computing systems.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!