What Are the Challenges in Deploying Spin Qubits in Silicon?

OCT 10, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Silicon Spin Qubits Background and Objectives

Silicon spin qubits represent one of the most promising platforms for quantum computing due to their compatibility with existing semiconductor manufacturing infrastructure. The concept of using electron spins in silicon as quantum bits dates back to the early 2000s, following Bruce Kane's seminal proposal in 1998. Since then, the field has witnessed remarkable progress, evolving from theoretical concepts to experimental demonstrations of high-fidelity quantum operations.

The technological trajectory of silicon spin qubits has been characterized by steady improvements in coherence times, gate fidelities, and readout accuracy. Early implementations faced significant challenges with decoherence due to nuclear spin interactions, but the development of isotopically purified silicon (28Si) has substantially mitigated this issue. The field has progressed from single-qubit demonstrations to two-qubit gates, with recent achievements showing fidelities approaching the thresholds required for fault-tolerant quantum computing.

Current technical objectives in the silicon spin qubit domain focus on several critical areas. First, scaling beyond few-qubit systems to create arrays containing dozens or hundreds of qubits while maintaining high-fidelity control. Second, improving the reliability and reproducibility of qubit fabrication to reduce variability between devices. Third, developing integrated control electronics that can operate at cryogenic temperatures to minimize wiring complexity as systems scale.

The evolution of silicon spin qubits is closely tied to advances in semiconductor fabrication techniques. The ability to precisely position dopants, create quantum dots with consistent properties, and integrate sensing and control elements has been crucial for experimental progress. Recent innovations in fabrication methods, including the use of advanced lithography techniques and novel materials integration, have enabled more sophisticated qubit architectures.

Looking forward, the field aims to demonstrate quantum advantage in practical applications by leveraging the inherent scalability of silicon-based approaches. This includes developing error correction protocols specifically tailored to silicon spin qubits, creating hybrid quantum-classical computing architectures, and identifying early applications where even modest-sized quantum processors could provide computational benefits.

The convergence of quantum physics, materials science, and semiconductor engineering has created a rich interdisciplinary research environment for silicon spin qubits. As the technology continues to mature, the focus is increasingly shifting from fundamental physics demonstrations to engineering challenges associated with creating practical quantum computing systems that can eventually outperform classical computers for specific computational tasks.

The technological trajectory of silicon spin qubits has been characterized by steady improvements in coherence times, gate fidelities, and readout accuracy. Early implementations faced significant challenges with decoherence due to nuclear spin interactions, but the development of isotopically purified silicon (28Si) has substantially mitigated this issue. The field has progressed from single-qubit demonstrations to two-qubit gates, with recent achievements showing fidelities approaching the thresholds required for fault-tolerant quantum computing.

Current technical objectives in the silicon spin qubit domain focus on several critical areas. First, scaling beyond few-qubit systems to create arrays containing dozens or hundreds of qubits while maintaining high-fidelity control. Second, improving the reliability and reproducibility of qubit fabrication to reduce variability between devices. Third, developing integrated control electronics that can operate at cryogenic temperatures to minimize wiring complexity as systems scale.

The evolution of silicon spin qubits is closely tied to advances in semiconductor fabrication techniques. The ability to precisely position dopants, create quantum dots with consistent properties, and integrate sensing and control elements has been crucial for experimental progress. Recent innovations in fabrication methods, including the use of advanced lithography techniques and novel materials integration, have enabled more sophisticated qubit architectures.

Looking forward, the field aims to demonstrate quantum advantage in practical applications by leveraging the inherent scalability of silicon-based approaches. This includes developing error correction protocols specifically tailored to silicon spin qubits, creating hybrid quantum-classical computing architectures, and identifying early applications where even modest-sized quantum processors could provide computational benefits.

The convergence of quantum physics, materials science, and semiconductor engineering has created a rich interdisciplinary research environment for silicon spin qubits. As the technology continues to mature, the focus is increasingly shifting from fundamental physics demonstrations to engineering challenges associated with creating practical quantum computing systems that can eventually outperform classical computers for specific computational tasks.

Market Demand Analysis for Silicon Quantum Computing

The quantum computing market is experiencing unprecedented growth, with silicon-based quantum technologies emerging as a particularly promising segment. Current market projections indicate that the global quantum computing market could reach $1.3 billion by 2026, with silicon quantum computing potentially capturing a significant portion of this expanding market. The integration of quantum technologies with existing semiconductor infrastructure represents a compelling value proposition that is driving substantial investment interest.

Market research reveals strong demand signals from several key sectors. Financial services organizations are increasingly exploring quantum computing for portfolio optimization, risk assessment, and fraud detection applications. Pharmaceutical companies are investing in quantum research capabilities to accelerate drug discovery processes and reduce development costs. Additionally, materials science, logistics optimization, and cybersecurity sectors have demonstrated growing interest in quantum computing solutions that could potentially be delivered through silicon-based architectures.

Silicon spin qubits offer distinct market advantages that align with current industry needs. Their compatibility with existing CMOS manufacturing processes presents a clear pathway to scalability that resonates with commercial stakeholders. This manufacturing synergy potentially enables faster time-to-market and more cost-effective production compared to competing quantum technologies, addressing critical concerns for early enterprise adopters.

Venture capital funding for silicon quantum computing startups has shown remarkable growth, with investment increasing by approximately 40% annually over the past three years. This trend reflects market confidence in silicon-based approaches as commercially viable quantum computing platforms. Major semiconductor companies are also establishing strategic partnerships with quantum computing research institutions, further validating market expectations for silicon spin qubit technologies.

Customer surveys indicate that enterprise clients prioritize quantum solutions that can integrate with existing IT infrastructure, a requirement that silicon-based quantum computers are well-positioned to meet. The potential for room-temperature operation of silicon spin qubits, though still under development, represents a significant market differentiator that could substantially reduce total cost of ownership for end users.

Market analysis suggests that early commercial applications will likely focus on hybrid classical-quantum computing models, where silicon spin qubits could offer particular advantages due to their potential integration with conventional computing systems. This hybrid approach aligns with enterprise adoption strategies that seek to incrementally incorporate quantum capabilities into existing computational workflows.

Despite technical challenges, market demand for silicon quantum computing solutions remains robust, driven by the technology's promising scalability pathway and potential for integration with established semiconductor manufacturing processes. This market momentum continues to attract both public and private investment, creating a positive feedback loop that accelerates technology development and commercialization efforts.

Market research reveals strong demand signals from several key sectors. Financial services organizations are increasingly exploring quantum computing for portfolio optimization, risk assessment, and fraud detection applications. Pharmaceutical companies are investing in quantum research capabilities to accelerate drug discovery processes and reduce development costs. Additionally, materials science, logistics optimization, and cybersecurity sectors have demonstrated growing interest in quantum computing solutions that could potentially be delivered through silicon-based architectures.

Silicon spin qubits offer distinct market advantages that align with current industry needs. Their compatibility with existing CMOS manufacturing processes presents a clear pathway to scalability that resonates with commercial stakeholders. This manufacturing synergy potentially enables faster time-to-market and more cost-effective production compared to competing quantum technologies, addressing critical concerns for early enterprise adopters.

Venture capital funding for silicon quantum computing startups has shown remarkable growth, with investment increasing by approximately 40% annually over the past three years. This trend reflects market confidence in silicon-based approaches as commercially viable quantum computing platforms. Major semiconductor companies are also establishing strategic partnerships with quantum computing research institutions, further validating market expectations for silicon spin qubit technologies.

Customer surveys indicate that enterprise clients prioritize quantum solutions that can integrate with existing IT infrastructure, a requirement that silicon-based quantum computers are well-positioned to meet. The potential for room-temperature operation of silicon spin qubits, though still under development, represents a significant market differentiator that could substantially reduce total cost of ownership for end users.

Market analysis suggests that early commercial applications will likely focus on hybrid classical-quantum computing models, where silicon spin qubits could offer particular advantages due to their potential integration with conventional computing systems. This hybrid approach aligns with enterprise adoption strategies that seek to incrementally incorporate quantum capabilities into existing computational workflows.

Despite technical challenges, market demand for silicon quantum computing solutions remains robust, driven by the technology's promising scalability pathway and potential for integration with established semiconductor manufacturing processes. This market momentum continues to attract both public and private investment, creating a positive feedback loop that accelerates technology development and commercialization efforts.

Current Challenges in Silicon Spin Qubit Implementation

Silicon spin qubits represent one of the most promising platforms for quantum computing due to their compatibility with existing semiconductor manufacturing infrastructure. However, several significant challenges currently impede their widespread deployment and practical implementation.

Coherence time limitations remain a primary obstacle in silicon spin qubit systems. Despite silicon's potential for long coherence times due to weak spin-orbit coupling and the availability of isotopically purified Si-28, actual implementations still suffer from decoherence caused by nuclear spins, charge noise, and magnetic field fluctuations. These factors significantly restrict the number of operations that can be performed before quantum information is lost.

Qubit initialization and readout present substantial technical hurdles. Current readout methods often rely on charge sensing or spin-to-charge conversion, which can be slow and prone to errors. The fidelity of these processes typically falls below the thresholds required for fault-tolerant quantum computing, necessitating significant improvements in both speed and accuracy.

Scaling remains perhaps the most formidable challenge. While silicon's compatibility with CMOS technology theoretically enables large-scale integration, practical implementations face numerous obstacles. The dense wiring required for controlling individual qubits creates routing congestion as system size increases. Additionally, maintaining uniform control over many qubits while minimizing crosstalk between adjacent qubits presents significant engineering challenges.

Variability between qubits poses another critical issue. Manufacturing processes inevitably introduce variations in qubit parameters, such as resonance frequencies and coupling strengths. This variability necessitates individual calibration procedures for each qubit, which becomes increasingly impractical as system size grows.

Temperature requirements add another layer of complexity. While silicon spin qubits can operate at higher temperatures (around 1-4 Kelvin) compared to superconducting qubits, they still require sophisticated cryogenic systems. The heat dissipation from control electronics becomes problematic as the number of qubits increases, creating thermal management challenges.

Two-qubit gate fidelity represents a significant technical barrier. Current implementations of entangling gates between spin qubits often exhibit fidelities below the threshold required for fault-tolerant quantum computing. Improving these gate operations while maintaining compatibility with scalable architectures remains an active area of research.

Integration with classical control electronics presents additional challenges. The interface between the quantum and classical domains requires careful design to minimize noise and maintain qubit coherence while providing sufficient bandwidth for qubit control and readout.

Coherence time limitations remain a primary obstacle in silicon spin qubit systems. Despite silicon's potential for long coherence times due to weak spin-orbit coupling and the availability of isotopically purified Si-28, actual implementations still suffer from decoherence caused by nuclear spins, charge noise, and magnetic field fluctuations. These factors significantly restrict the number of operations that can be performed before quantum information is lost.

Qubit initialization and readout present substantial technical hurdles. Current readout methods often rely on charge sensing or spin-to-charge conversion, which can be slow and prone to errors. The fidelity of these processes typically falls below the thresholds required for fault-tolerant quantum computing, necessitating significant improvements in both speed and accuracy.

Scaling remains perhaps the most formidable challenge. While silicon's compatibility with CMOS technology theoretically enables large-scale integration, practical implementations face numerous obstacles. The dense wiring required for controlling individual qubits creates routing congestion as system size increases. Additionally, maintaining uniform control over many qubits while minimizing crosstalk between adjacent qubits presents significant engineering challenges.

Variability between qubits poses another critical issue. Manufacturing processes inevitably introduce variations in qubit parameters, such as resonance frequencies and coupling strengths. This variability necessitates individual calibration procedures for each qubit, which becomes increasingly impractical as system size grows.

Temperature requirements add another layer of complexity. While silicon spin qubits can operate at higher temperatures (around 1-4 Kelvin) compared to superconducting qubits, they still require sophisticated cryogenic systems. The heat dissipation from control electronics becomes problematic as the number of qubits increases, creating thermal management challenges.

Two-qubit gate fidelity represents a significant technical barrier. Current implementations of entangling gates between spin qubits often exhibit fidelities below the threshold required for fault-tolerant quantum computing. Improving these gate operations while maintaining compatibility with scalable architectures remains an active area of research.

Integration with classical control electronics presents additional challenges. The interface between the quantum and classical domains requires careful design to minimize noise and maintain qubit coherence while providing sufficient bandwidth for qubit control and readout.

Current Silicon Spin Qubit Deployment Approaches

01 Fabrication and integration challenges

The fabrication of spin qubits in silicon faces significant challenges related to precise dopant placement, interface quality control, and integration with conventional CMOS technology. These challenges include maintaining quantum coherence during manufacturing processes, achieving consistent qubit performance across large arrays, and developing scalable fabrication techniques that can produce uniform qubit properties. Advanced lithography and processing methods are required to create the nanoscale structures needed for reliable qubit operation.- Fabrication and integration challenges: The fabrication of spin qubits in silicon faces significant challenges related to precise dopant placement, interface quality control, and integration with conventional CMOS technology. These challenges include maintaining quantum coherence during manufacturing processes, achieving consistent qubit performance across large arrays, and developing scalable fabrication techniques that can produce uniform qubit properties. Advanced lithography and deposition methods are required to create the nanoscale structures needed for reliable qubit operation.

- Quantum coherence and decoherence mitigation: Maintaining quantum coherence in silicon-based spin qubits remains a fundamental challenge for practical deployment. Environmental factors such as nuclear spin interactions, charge noise, and thermal fluctuations can cause decoherence, reducing qubit fidelity and limiting computation time. Various approaches to mitigate these effects include isotopic purification of silicon, sophisticated pulse sequences for dynamical decoupling, improved materials interfaces, and error correction techniques that can extend coherence times sufficiently for practical quantum operations.

- Control electronics and cryogenic operation: Operating silicon spin qubits requires sophisticated control electronics that must function at cryogenic temperatures, typically below 100 mK. The challenges include designing low-power control circuits that don't generate excessive heat, developing multiplexing schemes to address large numbers of qubits with limited input/output lines, and creating integrated control systems that can scale with increasing qubit counts. The interface between room temperature control systems and cryogenic qubit arrays presents significant engineering challenges for practical quantum computing systems.

- Scalability and system architecture: Scaling silicon spin qubit systems from few-qubit demonstrations to practical quantum computers with thousands or millions of qubits presents architectural challenges. These include developing efficient qubit coupling mechanisms, implementing fault-tolerant error correction codes, designing quantum memory systems, and creating modular architectures that allow for incremental scaling. The physical layout of qubit arrays, interconnects, and control lines must be optimized to maintain qubit performance while enabling the complex operations required for quantum algorithms.

- Readout and measurement techniques: Accurate and high-fidelity readout of silicon spin qubits is essential for quantum computation but faces several deployment challenges. These include developing sensitive charge sensors that can detect single-spin states, implementing fast readout protocols that minimize measurement-induced decoherence, and designing multiplexed readout systems for large qubit arrays. The signal-to-noise ratio in spin detection must be optimized while maintaining compatibility with integrated circuit fabrication processes and cryogenic operating conditions.

02 Quantum coherence and decoherence mitigation

Maintaining quantum coherence in silicon spin qubits is a major deployment challenge. Environmental factors such as nuclear spin interactions, charge noise, and thermal fluctuations can cause decoherence, reducing qubit fidelity and limiting computational capabilities. Various approaches to mitigate decoherence include isotopic purification of silicon, improved materials engineering, pulse sequence optimization, and dynamic decoupling techniques. These methods aim to extend coherence times and improve qubit performance in practical quantum computing systems.Expand Specific Solutions03 Control electronics and readout systems

Developing efficient control electronics and readout systems for silicon spin qubits presents significant deployment challenges. These systems must operate at cryogenic temperatures while providing precise control signals with minimal noise. Challenges include designing low-power cryogenic electronics, implementing high-fidelity readout mechanisms, and creating scalable control architectures that can address multiple qubits simultaneously. Integration of classical control systems with quantum processors requires specialized interfaces and signal processing techniques to maintain qubit coherence during operation.Expand Specific Solutions04 Scalability and quantum error correction

Scaling silicon spin qubit systems to practical sizes requires addressing challenges in qubit connectivity, control line routing, and implementing effective quantum error correction. As the number of qubits increases, maintaining uniform control across the system becomes increasingly difficult. Implementing error correction codes requires additional physical qubits and complex control protocols. Challenges include developing architectures that balance connectivity with fabrication constraints, creating efficient error correction implementations, and designing systems that can scale while maintaining high fidelity operations.Expand Specific Solutions05 System integration and operating environment

Deploying silicon spin qubit systems requires addressing challenges related to the operating environment and integration with supporting infrastructure. These systems typically require ultra-low temperatures near absolute zero, which necessitates complex cryogenic equipment. Challenges include developing more efficient cooling systems, reducing the footprint of supporting infrastructure, and creating interfaces between quantum and classical computing components. Additionally, shielding qubits from electromagnetic interference and vibration while maintaining accessibility for control signals presents significant engineering challenges.Expand Specific Solutions

Key Players in Silicon Quantum Computing Ecosystem

The silicon spin qubit technology landscape is currently in the early development stage, with a growing market projected to reach significant scale as quantum computing matures. Technical challenges in deploying spin qubits in silicon have created a competitive environment where academic institutions (MIT, Delft University, USTC) collaborate with industry players. Major semiconductor manufacturers (TSMC, GlobalFoundries) are investing in this space, while specialized quantum startups (Quantum Motion Technologies, QpiAI) focus on overcoming coherence time limitations, qubit coupling issues, and scalability challenges. Research consortia led by organizations like Imec and Forschungszentrum Jülich are advancing fabrication techniques to improve qubit fidelity and control electronics integration, positioning silicon spin qubits as a promising platform for fault-tolerant quantum computing.

Commissariat à l´énergie atomique et aux énergies Alternatives

Technical Solution: CEA (Commissariat à l'énergie atomique et aux énergies alternatives) has developed silicon spin qubit technology based on silicon-on-insulator (SOI) platforms. Their approach leverages nanowire transistors where individual electrons are confined in quantum dots formed at silicon/silicon oxide interfaces. CEA has demonstrated coherent spin manipulation in these devices with coherence times in the microsecond range. A distinctive aspect of their technology is the use of fully-depleted SOI (FD-SOI) technology, which is compatible with existing semiconductor manufacturing processes. They've achieved single-qubit gate fidelities exceeding 99% and are working on two-qubit operations based on exchange coupling. CEA has also developed specialized cryogenic electronics for qubit control and readout, operating at temperatures below 1K. Their research includes hole-spin qubits, which offer advantages in terms of spin-orbit coupling strength and potential for all-electrical control.

Strengths: Strong integration with industrial semiconductor processes, particularly leveraging FD-SOI technology that could enable manufacturing scalability. Their approach benefits from existing infrastructure and expertise in silicon electronics. Weaknesses: Lower coherence times compared to some competing approaches, challenges with hole-spin stability, and difficulties in achieving uniform qubit properties across devices.

Massachusetts Institute of Technology

Technical Solution: MIT has developed a distinctive approach to silicon spin qubits focusing on isotopically purified silicon-28 substrates to minimize nuclear spin noise. Their technology utilizes gate-defined quantum dots in silicon/silicon-germanium heterostructures, where electrons are confined by electrostatic potentials. MIT researchers have achieved coherence times exceeding 1 millisecond and demonstrated high-fidelity single-qubit operations with control fidelities above 99.9%. A significant innovation is their development of "shared control" architectures that reduce the number of control lines needed per qubit, addressing one of the key scaling challenges. They've also pioneered techniques for shuttling electrons between quantum dots, enabling long-range qubit coupling that could be crucial for error correction schemes. MIT's approach includes integration with superconducting resonators for improved qubit readout and coupling.

Strengths: Exceptional coherence times, innovative architectural solutions for scaling, and advanced techniques for qubit coupling and readout. Weaknesses: Fabrication complexity requiring precise material interfaces, sensitivity to charge noise, and challenges in maintaining uniform qubit properties across larger arrays.

Critical Patents and Research in Spin Qubit Technology

A qubit processing method

PatentPendingUS20230153673A1

Innovation

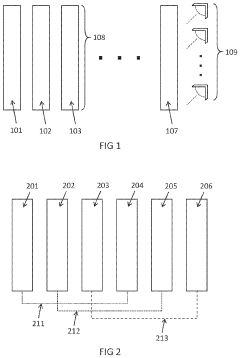

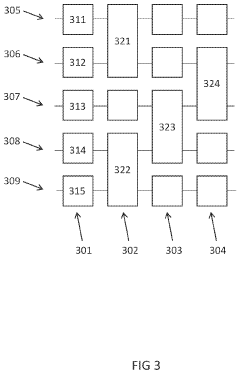

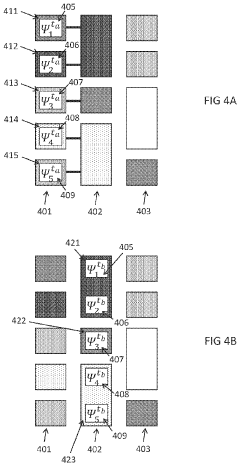

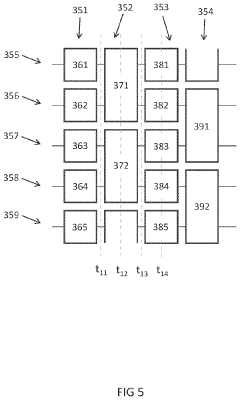

- A qubit processing method that configures sets of locations to perform specific one- or two-qubit operations, allowing qubits to be transferred between locations to maintain fixed configurations during processing, enabling efficient processing of multiple qubit groups simultaneously and reducing resource requirements.

Patent

Innovation

- Development of high-fidelity single-qubit and two-qubit gate operations in silicon spin qubits with improved coherence times and reduced error rates.

- Novel fabrication techniques for precise dopant placement and control of exchange coupling between qubits in silicon, enabling scalable quantum processor architectures.

- Integration of silicon spin qubits with conventional CMOS technology, leveraging existing semiconductor manufacturing infrastructure for scalable quantum computing platforms.

Quantum Error Correction Strategies for Spin Qubits

Quantum Error Correction (QEC) represents a critical frontier in the development of practical spin qubit systems in silicon. The inherent fragility of quantum states necessitates robust error correction mechanisms to achieve fault-tolerant quantum computation. For spin qubits in silicon, several specialized QEC strategies have emerged to address their unique characteristics and challenges.

Surface codes have gained significant traction as a promising QEC approach for spin qubits due to their high error threshold and compatibility with 2D architectures. These codes organize physical qubits in a lattice structure where logical qubits are encoded across multiple physical qubits, allowing errors to be detected and corrected through syndrome measurements. Recent adaptations of surface codes specifically for spin qubit architectures have demonstrated theoretical error thresholds approaching 1%, making them particularly attractive for silicon-based implementations.

Dynamical decoupling sequences represent another crucial error mitigation strategy for spin qubits. These techniques, including Hahn echo and Carr-Purcell-Meiboom-Gill (CPMG) sequences, effectively combat decoherence by applying precisely timed control pulses that reverse the accumulation of phase errors. Research has shown that optimized dynamical decoupling protocols can extend coherence times of silicon spin qubits by orders of magnitude, providing valuable error suppression during quantum operations.

Leakage reduction techniques address the unique challenge of spin qubits where quantum information can "leak" outside the computational subspace. This is particularly relevant in silicon spin qubits where valley states or higher orbital states can capture quantum information. Specialized leakage reduction operators (LROs) have been developed to detect and reset these leakage events, ensuring quantum information remains within the computational basis.

Hardware-efficient QEC codes tailored specifically for spin qubits are emerging as a promising direction. These codes exploit the natural properties of spin systems, such as exchange interactions and hyperfine coupling, to implement error correction with minimal overhead. The Bacon-Shor subsystem code and small stabilizer codes have been adapted for spin qubit architectures, offering practical paths toward error correction with current technology capabilities.

Hybrid approaches combining hardware and software error correction show particular promise for near-term spin qubit systems. These strategies integrate physical error suppression techniques (improved materials, optimized control pulses) with logical encoding schemes to achieve better overall performance than either approach alone. Such hybrid methods may provide the most realistic path toward fault-tolerance for silicon spin qubits given current technological constraints.

Surface codes have gained significant traction as a promising QEC approach for spin qubits due to their high error threshold and compatibility with 2D architectures. These codes organize physical qubits in a lattice structure where logical qubits are encoded across multiple physical qubits, allowing errors to be detected and corrected through syndrome measurements. Recent adaptations of surface codes specifically for spin qubit architectures have demonstrated theoretical error thresholds approaching 1%, making them particularly attractive for silicon-based implementations.

Dynamical decoupling sequences represent another crucial error mitigation strategy for spin qubits. These techniques, including Hahn echo and Carr-Purcell-Meiboom-Gill (CPMG) sequences, effectively combat decoherence by applying precisely timed control pulses that reverse the accumulation of phase errors. Research has shown that optimized dynamical decoupling protocols can extend coherence times of silicon spin qubits by orders of magnitude, providing valuable error suppression during quantum operations.

Leakage reduction techniques address the unique challenge of spin qubits where quantum information can "leak" outside the computational subspace. This is particularly relevant in silicon spin qubits where valley states or higher orbital states can capture quantum information. Specialized leakage reduction operators (LROs) have been developed to detect and reset these leakage events, ensuring quantum information remains within the computational basis.

Hardware-efficient QEC codes tailored specifically for spin qubits are emerging as a promising direction. These codes exploit the natural properties of spin systems, such as exchange interactions and hyperfine coupling, to implement error correction with minimal overhead. The Bacon-Shor subsystem code and small stabilizer codes have been adapted for spin qubit architectures, offering practical paths toward error correction with current technology capabilities.

Hybrid approaches combining hardware and software error correction show particular promise for near-term spin qubit systems. These strategies integrate physical error suppression techniques (improved materials, optimized control pulses) with logical encoding schemes to achieve better overall performance than either approach alone. Such hybrid methods may provide the most realistic path toward fault-tolerance for silicon spin qubits given current technological constraints.

Scalability and Integration Challenges in Silicon Platforms

Silicon platforms present significant scalability and integration challenges for spin qubit deployment, despite their compatibility with existing semiconductor manufacturing infrastructure. The primary obstacle lies in maintaining quantum coherence while scaling up the number of qubits. As device density increases, cross-talk between adjacent qubits becomes more pronounced, leading to decoherence and operational errors. This fundamental tension between integration density and quantum information preservation represents a critical bottleneck in silicon-based quantum computing.

The fabrication precision required for spin qubit devices exceeds that of classical CMOS technology. Atomic-level variations in silicon substrates can dramatically alter qubit properties, creating inconsistencies across arrays. Current manufacturing processes struggle to achieve the sub-nanometer precision necessary for reliable large-scale qubit arrays, with even minor imperfections potentially rendering entire quantum circuits inoperable.

Thermal management presents another substantial challenge. Quantum operations typically require cryogenic temperatures (below 100 mK), while control electronics generate heat that can disrupt quantum states. As systems scale to thousands or millions of qubits, maintaining uniform ultra-low temperatures becomes increasingly difficult, necessitating novel cooling architectures and thermally-isolated integration approaches.

Interconnect complexity grows exponentially with qubit count. Each qubit requires multiple control lines for initialization, manipulation, and readout. Traditional wiring approaches quickly become impractical beyond a few dozen qubits, creating a "wiring bottleneck" that limits scalability. Multiplexing strategies and on-chip control electronics offer potential solutions but introduce additional heat sources and potential interference.

Integration of classical control electronics with quantum processing units presents further complications. The physical separation between room-temperature electronics and cryogenic qubits introduces latency and signal integrity issues. Cryogenic control electronics could mitigate these problems but face significant design constraints due to altered semiconductor behavior at extremely low temperatures.

Material interface engineering remains challenging, particularly at the silicon-oxide boundary where dangling bonds and charge traps can disrupt qubit performance. Advanced materials science approaches, including isotopically purified silicon and precisely engineered barrier materials, show promise but require further development for industrial-scale implementation.

The fabrication precision required for spin qubit devices exceeds that of classical CMOS technology. Atomic-level variations in silicon substrates can dramatically alter qubit properties, creating inconsistencies across arrays. Current manufacturing processes struggle to achieve the sub-nanometer precision necessary for reliable large-scale qubit arrays, with even minor imperfections potentially rendering entire quantum circuits inoperable.

Thermal management presents another substantial challenge. Quantum operations typically require cryogenic temperatures (below 100 mK), while control electronics generate heat that can disrupt quantum states. As systems scale to thousands or millions of qubits, maintaining uniform ultra-low temperatures becomes increasingly difficult, necessitating novel cooling architectures and thermally-isolated integration approaches.

Interconnect complexity grows exponentially with qubit count. Each qubit requires multiple control lines for initialization, manipulation, and readout. Traditional wiring approaches quickly become impractical beyond a few dozen qubits, creating a "wiring bottleneck" that limits scalability. Multiplexing strategies and on-chip control electronics offer potential solutions but introduce additional heat sources and potential interference.

Integration of classical control electronics with quantum processing units presents further complications. The physical separation between room-temperature electronics and cryogenic qubits introduces latency and signal integrity issues. Cryogenic control electronics could mitigate these problems but face significant design constraints due to altered semiconductor behavior at extremely low temperatures.

Material interface engineering remains challenging, particularly at the silicon-oxide boundary where dangling bonds and charge traps can disrupt qubit performance. Advanced materials science approaches, including isotopically purified silicon and precisely engineered barrier materials, show promise but require further development for industrial-scale implementation.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!