Designing chiplet-based SOCs around RISC-V

AUG 25, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

RISC-V Chiplet Evolution and Objectives

The RISC-V architecture has evolved significantly since its inception at UC Berkeley in 2010, transforming from an academic project to a global open-source instruction set architecture (ISA) with substantial industry adoption. This evolution has coincided with the semiconductor industry's paradigm shift toward chiplet-based designs, which decompose monolithic systems-on-chip (SoCs) into smaller, specialized dies interconnected on a package substrate. The convergence of RISC-V and chiplet technology represents a strategic opportunity to address the escalating challenges of traditional semiconductor scaling.

The chiplet approach emerged as a response to the slowing of Moore's Law and the increasing costs of advanced process nodes. By enabling different components to be manufactured using optimal process technologies, chiplets offer improved yield, reduced development costs, and enhanced design flexibility. RISC-V's modular and extensible nature makes it particularly well-suited for chiplet implementations, allowing for customized processor cores to be combined with specialized accelerators and I/O components.

Early RISC-V implementations were primarily monolithic designs focused on proving the viability of the ISA. The transition toward chiplet-based RISC-V systems began around 2018-2019, with companies like SiFive and Esperanto Technologies pioneering multi-core RISC-V designs that laid the groundwork for more sophisticated chiplet architectures. This evolution has accelerated with the establishment of industry standards for chiplet interfaces, such as UCIe (Universal Chiplet Interconnect Express) and CHIPS Alliance's Advanced Interface Bus (AIB).

The primary technical objectives for RISC-V chiplet-based SoCs include achieving seamless integration between heterogeneous chiplets, minimizing inter-chiplet communication overhead, and maintaining power efficiency while maximizing performance. These objectives necessitate innovations in die-to-die interfaces, packaging technologies, and system-level design methodologies specific to RISC-V implementations.

Another critical objective is establishing standardized interfaces and protocols that enable interoperability between RISC-V chiplets from different vendors. This "chiplet ecosystem" approach aims to create a marketplace of compatible components that can be mixed and matched to create customized SoCs, similar to how printed circuit boards allow for the combination of discrete components but at a much finer granularity.

The long-term vision for RISC-V chiplet technology encompasses domain-specific architectures that combine general-purpose RISC-V cores with specialized accelerators for applications such as AI/ML, networking, and security. This approach promises to deliver performance and efficiency improvements that surpass what would be possible with monolithic designs, while maintaining the openness and flexibility that are hallmarks of the RISC-V ecosystem.

The chiplet approach emerged as a response to the slowing of Moore's Law and the increasing costs of advanced process nodes. By enabling different components to be manufactured using optimal process technologies, chiplets offer improved yield, reduced development costs, and enhanced design flexibility. RISC-V's modular and extensible nature makes it particularly well-suited for chiplet implementations, allowing for customized processor cores to be combined with specialized accelerators and I/O components.

Early RISC-V implementations were primarily monolithic designs focused on proving the viability of the ISA. The transition toward chiplet-based RISC-V systems began around 2018-2019, with companies like SiFive and Esperanto Technologies pioneering multi-core RISC-V designs that laid the groundwork for more sophisticated chiplet architectures. This evolution has accelerated with the establishment of industry standards for chiplet interfaces, such as UCIe (Universal Chiplet Interconnect Express) and CHIPS Alliance's Advanced Interface Bus (AIB).

The primary technical objectives for RISC-V chiplet-based SoCs include achieving seamless integration between heterogeneous chiplets, minimizing inter-chiplet communication overhead, and maintaining power efficiency while maximizing performance. These objectives necessitate innovations in die-to-die interfaces, packaging technologies, and system-level design methodologies specific to RISC-V implementations.

Another critical objective is establishing standardized interfaces and protocols that enable interoperability between RISC-V chiplets from different vendors. This "chiplet ecosystem" approach aims to create a marketplace of compatible components that can be mixed and matched to create customized SoCs, similar to how printed circuit boards allow for the combination of discrete components but at a much finer granularity.

The long-term vision for RISC-V chiplet technology encompasses domain-specific architectures that combine general-purpose RISC-V cores with specialized accelerators for applications such as AI/ML, networking, and security. This approach promises to deliver performance and efficiency improvements that surpass what would be possible with monolithic designs, while maintaining the openness and flexibility that are hallmarks of the RISC-V ecosystem.

Market Demand Analysis for RISC-V Chiplet-based SOCs

The RISC-V chiplet-based SoC market is experiencing unprecedented growth, driven by the convergence of several industry trends. The global semiconductor industry's shift toward modular design approaches has created fertile ground for RISC-V chiplet solutions. Market research indicates that the chiplet market is projected to grow at a CAGR of 40% through 2027, with RISC-V implementations representing an increasingly significant portion of this expansion.

The demand for RISC-V chiplet-based SoCs stems primarily from four key market segments. Data centers and cloud infrastructure providers are seeking more customizable, power-efficient computing solutions to address the exponential growth in data processing requirements. These organizations value the flexibility of RISC-V chiplets to create specialized accelerators for workloads like AI inference, database operations, and video transcoding.

The edge computing sector represents another substantial market, with IoT deployments, autonomous systems, and smart infrastructure requiring heterogeneous computing capabilities that can be efficiently delivered through chiplet-based designs. The ability to integrate specialized processing elements alongside RISC-V cores creates compelling value propositions for these applications.

Consumer electronics manufacturers are increasingly exploring RISC-V chiplet solutions to differentiate their products while controlling development costs. The modular nature of chiplet designs allows companies to rapidly iterate on product features without complete redesigns, significantly reducing time-to-market for new devices.

The automotive industry presents perhaps the most promising long-term growth opportunity. Advanced driver-assistance systems and autonomous driving platforms require sophisticated heterogeneous computing architectures that can be efficiently implemented using chiplet approaches. RISC-V's open standard provides automotive manufacturers with greater supply chain security and customization options compared to proprietary architectures.

Market analysis reveals that organizations are primarily motivated to adopt RISC-V chiplet solutions by three factors: reduced development costs through IP reuse and modular design; enhanced performance and power efficiency through specialized processing elements; and supply chain resilience through the open ecosystem. The ability to mix proprietary and open-source IP blocks within a single SoC design is particularly attractive to companies seeking to balance innovation with cost control.

Regional market trends indicate North America and Asia-Pacific leading adoption, with Europe showing accelerated interest driven by initiatives to develop sovereign semiconductor capabilities. China represents a particularly strong growth market due to strategic investments in domestic semiconductor infrastructure and the geopolitical advantages of RISC-V's open nature.

The demand for RISC-V chiplet-based SoCs stems primarily from four key market segments. Data centers and cloud infrastructure providers are seeking more customizable, power-efficient computing solutions to address the exponential growth in data processing requirements. These organizations value the flexibility of RISC-V chiplets to create specialized accelerators for workloads like AI inference, database operations, and video transcoding.

The edge computing sector represents another substantial market, with IoT deployments, autonomous systems, and smart infrastructure requiring heterogeneous computing capabilities that can be efficiently delivered through chiplet-based designs. The ability to integrate specialized processing elements alongside RISC-V cores creates compelling value propositions for these applications.

Consumer electronics manufacturers are increasingly exploring RISC-V chiplet solutions to differentiate their products while controlling development costs. The modular nature of chiplet designs allows companies to rapidly iterate on product features without complete redesigns, significantly reducing time-to-market for new devices.

The automotive industry presents perhaps the most promising long-term growth opportunity. Advanced driver-assistance systems and autonomous driving platforms require sophisticated heterogeneous computing architectures that can be efficiently implemented using chiplet approaches. RISC-V's open standard provides automotive manufacturers with greater supply chain security and customization options compared to proprietary architectures.

Market analysis reveals that organizations are primarily motivated to adopt RISC-V chiplet solutions by three factors: reduced development costs through IP reuse and modular design; enhanced performance and power efficiency through specialized processing elements; and supply chain resilience through the open ecosystem. The ability to mix proprietary and open-source IP blocks within a single SoC design is particularly attractive to companies seeking to balance innovation with cost control.

Regional market trends indicate North America and Asia-Pacific leading adoption, with Europe showing accelerated interest driven by initiatives to develop sovereign semiconductor capabilities. China represents a particularly strong growth market due to strategic investments in domestic semiconductor infrastructure and the geopolitical advantages of RISC-V's open nature.

Current Chiplet Technology Landscape and Challenges

The chiplet landscape has evolved significantly in recent years, with major semiconductor companies adopting disaggregated design approaches to overcome monolithic integration challenges. Currently, AMD's Infinity Fabric, Intel's EMIB and Foveros technologies, and TSMC's CoWoS platform represent the leading commercial chiplet integration solutions. These technologies enable heterogeneous integration of multiple silicon dies within a single package, allowing manufacturers to mix process nodes and specialized components while maintaining high-bandwidth, low-latency interconnections.

Despite these advancements, the chiplet ecosystem faces significant standardization challenges. The UCIe (Universal Chiplet Interconnect Express) consortium, formed in 2022, represents a major industry effort to establish common interfaces and protocols for chiplet-to-chiplet communication. However, widespread adoption remains in progress, with many companies still utilizing proprietary interconnect solutions that limit interoperability between different vendors' chiplets.

In the RISC-V chiplet domain specifically, several technical hurdles persist. Die-to-die interfaces require careful optimization to minimize latency and power consumption while maintaining signal integrity across chiplet boundaries. Current solutions often involve trade-offs between bandwidth, power efficiency, and implementation complexity. The physical integration challenges include thermal management across multiple dies, testing methodologies for partially assembled systems, and yield optimization strategies when combining chiplets from different process nodes.

Manufacturing and supply chain considerations further complicate the chiplet landscape. Known good die (KGD) testing, advanced packaging technologies, and assembly processes require specialized equipment and expertise. The ecosystem currently lacks standardized design tools specifically optimized for multi-chiplet architectures, creating barriers to entry for smaller companies and research institutions working with RISC-V.

From a business perspective, the chiplet approach introduces complex intellectual property considerations. The ability to mix proprietary and open-source components at the chiplet level creates new licensing and integration challenges, particularly relevant for RISC-V implementations where the core ISA is open but surrounding components may incorporate proprietary technologies.

Looking at geographical distribution, chiplet technology development remains concentrated in North America, Taiwan, and increasingly China, with significant investments in advanced packaging capabilities. European initiatives like the European Processor Initiative are also exploring chiplet-based approaches for high-performance computing applications using RISC-V cores.

The current state of RISC-V chiplet technology represents a transition period, with promising proof-of-concept designs emerging but full commercial deployment still facing significant technical and ecosystem challenges. The flexibility of RISC-V makes it particularly suitable for chiplet-based designs, but realizing this potential requires overcoming the current fragmentation in interconnect standards and design methodologies.

Despite these advancements, the chiplet ecosystem faces significant standardization challenges. The UCIe (Universal Chiplet Interconnect Express) consortium, formed in 2022, represents a major industry effort to establish common interfaces and protocols for chiplet-to-chiplet communication. However, widespread adoption remains in progress, with many companies still utilizing proprietary interconnect solutions that limit interoperability between different vendors' chiplets.

In the RISC-V chiplet domain specifically, several technical hurdles persist. Die-to-die interfaces require careful optimization to minimize latency and power consumption while maintaining signal integrity across chiplet boundaries. Current solutions often involve trade-offs between bandwidth, power efficiency, and implementation complexity. The physical integration challenges include thermal management across multiple dies, testing methodologies for partially assembled systems, and yield optimization strategies when combining chiplets from different process nodes.

Manufacturing and supply chain considerations further complicate the chiplet landscape. Known good die (KGD) testing, advanced packaging technologies, and assembly processes require specialized equipment and expertise. The ecosystem currently lacks standardized design tools specifically optimized for multi-chiplet architectures, creating barriers to entry for smaller companies and research institutions working with RISC-V.

From a business perspective, the chiplet approach introduces complex intellectual property considerations. The ability to mix proprietary and open-source components at the chiplet level creates new licensing and integration challenges, particularly relevant for RISC-V implementations where the core ISA is open but surrounding components may incorporate proprietary technologies.

Looking at geographical distribution, chiplet technology development remains concentrated in North America, Taiwan, and increasingly China, with significant investments in advanced packaging capabilities. European initiatives like the European Processor Initiative are also exploring chiplet-based approaches for high-performance computing applications using RISC-V cores.

The current state of RISC-V chiplet technology represents a transition period, with promising proof-of-concept designs emerging but full commercial deployment still facing significant technical and ecosystem challenges. The flexibility of RISC-V makes it particularly suitable for chiplet-based designs, but realizing this potential requires overcoming the current fragmentation in interconnect standards and design methodologies.

Current Chiplet-based SOC Design Methodologies

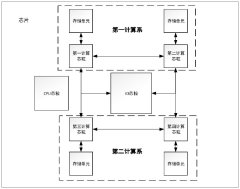

01 Chiplet Architecture for RISC-V Based Systems

Chiplet-based architectures enable modular design of RISC-V systems-on-chip, allowing different functional blocks to be implemented as separate dies and then integrated into a single package. This approach provides flexibility in combining various processing elements, memory subsystems, and specialized accelerators while maintaining the open instruction set architecture benefits of RISC-V. The modular nature allows for mixing different process technologies and IP blocks to optimize performance, power, and cost.- Chiplet architecture for RISC-V based systems: Chiplet-based architectures allow for modular design of RISC-V systems-on-chip, enabling flexible integration of different functional blocks. These architectures facilitate the combination of RISC-V processor cores with other components such as memory, I/O interfaces, and specialized accelerators. The modular approach improves scalability, reduces development costs, and allows for more efficient use of silicon area compared to monolithic designs.

- Interconnect technologies for RISC-V chiplets: Advanced interconnect technologies are essential for chiplet-based RISC-V SOCs to ensure efficient communication between different chiplets. These technologies include high-speed die-to-die interfaces, network-on-chip (NoC) architectures, and standardized protocols that enable seamless integration of chiplets from different vendors. The interconnect solutions address challenges related to bandwidth, latency, and power consumption while maintaining the flexibility of the chiplet approach.

- Power management in RISC-V chiplet-based designs: Power management techniques specifically designed for RISC-V chiplet-based SOCs enable efficient operation across various performance levels. These techniques include dynamic voltage and frequency scaling, power gating for inactive chiplets, and intelligent power distribution systems. Advanced power management controllers coordinate between chiplets to optimize overall system power consumption while maintaining required performance levels for specific applications.

- Security features for RISC-V chiplet architectures: Security implementations in RISC-V chiplet-based SOCs address the unique challenges of modular architectures. These include secure boot mechanisms that verify the integrity of each chiplet, hardware-based isolation between chiplets containing sensitive data, and cryptographic accelerators for secure communications. The security architecture ensures that the benefits of chiplet modularity don't compromise the overall system security posture, with features like trusted execution environments spanning across multiple chiplets.

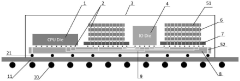

- Manufacturing and integration techniques for RISC-V chiplets: Advanced manufacturing and integration techniques enable the production of high-performance RISC-V chiplet-based SOCs. These include advanced packaging technologies like 2.5D and 3D integration, silicon interposers, and through-silicon vias (TSVs) that allow for dense interconnections between chiplets. Testing methodologies specific to chiplet architectures ensure functionality across chiplet boundaries, while design tools support the unique requirements of multi-die integration with RISC-V cores.

02 Interconnect Technologies for Chiplet Integration

Advanced interconnect technologies are crucial for chiplet-based RISC-V SOCs to ensure high-bandwidth, low-latency communication between dies. These include die-to-die interfaces, through-silicon vias (TSVs), and specialized packaging technologies that enable efficient data transfer between RISC-V cores and other chiplets. The interconnect architecture must address coherency protocols, memory consistency models, and power management challenges specific to disaggregated designs while maintaining the performance advantages of monolithic integration.Expand Specific Solutions03 Power Management and Thermal Optimization in RISC-V Chiplet SOCs

Effective power management strategies are essential for chiplet-based RISC-V SOCs to optimize energy efficiency across multiple dies. These include dynamic voltage and frequency scaling, power gating of inactive chiplets, and thermal management techniques that address the unique challenges of multi-die packages. Advanced power control mechanisms allow for fine-grained management of RISC-V cores and associated chiplets, enabling systems to adapt to workload requirements while minimizing energy consumption and managing thermal constraints.Expand Specific Solutions04 Security Features in Chiplet-based RISC-V Designs

Security architectures for chiplet-based RISC-V SOCs implement hardware-level protection mechanisms across die boundaries. These include secure boot processes, trusted execution environments, cryptographic accelerators, and physical attack countermeasures. The modular nature of chiplet designs presents unique security challenges, requiring secure communication channels between dies and protection against side-channel attacks. Implementations leverage RISC-V security extensions while addressing the additional attack surfaces introduced by multi-die integration.Expand Specific Solutions05 Manufacturing and Testing Methodologies for RISC-V Chiplet SOCs

Specialized manufacturing and testing methodologies have been developed for chiplet-based RISC-V SOCs to address the challenges of multi-die integration. These include known-good-die testing strategies, advanced packaging techniques, and yield optimization approaches that leverage the modular nature of chiplet designs. Post-packaging test methodologies ensure proper communication between RISC-V cores and other chiplets, while design-for-test features enable efficient validation of complex multi-die systems throughout their lifecycle.Expand Specific Solutions

Key Industry Players in RISC-V Chiplet Ecosystem

The chiplet-based RISC-V SoC design market is in its growth phase, characterized by increasing adoption across diverse sectors. The market is expanding rapidly, projected to reach significant scale as RISC-V's open-source architecture disrupts traditional semiconductor paradigms. Key players demonstrate varying levels of technical maturity: Intel and Micron lead with advanced chiplet integration capabilities; Huawei and MediaTek are making strategic investments in RISC-V chiplet ecosystems; while emerging players like Rockchip and Nanjing Qinheng Microelectronics are developing specialized implementations. Academic institutions including Zhejiang University and Fraunhofer-Gesellschaft are contributing foundational research. The technology is approaching mainstream commercial viability, with early adopters already deploying solutions in IoT, automotive, and data center applications, indicating a transition from experimental to production-ready implementations.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei has developed an advanced chiplet-based SoC architecture centered around RISC-V instruction set architecture, primarily through their HiSilicon subsidiary. Their approach utilizes a proprietary die-to-die interconnect technology called "Kirin Direct Connect" that enables high-bandwidth, low-latency communication between chiplets. Huawei's implementation features a modular design with specialized chiplets for AI acceleration, security, communications, and core processing functions. Their RISC-V implementation includes custom extensions for security and telecommunications applications, with reported performance improvements of up to 30% for specific workloads compared to standard implementations. The company has also developed advanced 2.5D and 3D packaging technologies to optimize thermal management and power distribution across multiple chiplets. Huawei's chiplet strategy allows them to mix process nodes, placing memory-intensive components on mature nodes while compute-intensive elements utilize cutting-edge processes, resulting in optimized cost-performance ratios. Their design methodology includes a unified software development framework that abstracts the underlying chiplet architecture, simplifying programming across heterogeneous computing elements.

Strengths: Strong vertical integration from chip design to end products; advanced packaging technology; expertise in telecommunications and networking applications; independence from Western IP. Weaknesses: Limited access to advanced manufacturing technologies due to trade restrictions; potential interoperability challenges with broader ecosystem due to customized interconnect solutions.

Micron Technology, Inc.

Technical Solution: Micron has pioneered an innovative approach to chiplet-based SoCs incorporating RISC-V through their Hybrid Memory Cube (HMC) and subsequent memory-centric computing architectures. Their solution integrates RISC-V processing elements directly with memory chiplets using through-silicon vias (TSVs) and advanced packaging technologies. This architecture significantly reduces memory access latency and improves bandwidth by up to 15x compared to traditional designs. Micron's implementation features specialized memory controllers optimized for RISC-V instruction execution and memory-intensive workloads. Their "Compute Express Link" (CXL) compatible interfaces enable seamless integration with other chiplets in heterogeneous computing environments. Micron has developed custom RISC-V extensions specifically optimized for in-memory and near-memory computing applications, allowing certain operations to be performed directly within memory arrays without data movement to the CPU. Their architecture includes dedicated security chiplets with hardware-based encryption and secure boot capabilities based on RISC-V cores. Micron's approach particularly excels in applications requiring high memory bandwidth and low latency, such as AI inference, database operations, and real-time analytics.

Strengths: Unparalleled expertise in memory technologies; innovative memory-centric computing architecture reduces data movement bottlenecks; strong position in emerging CXL ecosystem. Weaknesses: Less experience in general-purpose computing compared to traditional CPU vendors; higher complexity in programming model for memory-centric computing paradigms.

Critical Patents and Research in RISC-V Chiplet Integration

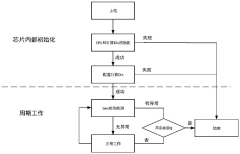

A chip and control method based on chiplet architecture

PatentActiveCN115617739B

Innovation

- Using the Chiplet architecture, the chip is decomposed into multiple small chips (CPU core, IO core, computing core, storage unit, silicon adapter board and substrate), and data is exchanged through the UCIe bus to achieve synchronization and synchronization of computing cores. detection, supports performance, security, single-line and low-power consumption modes, and uses CoWoS packaging technology to reduce costs.

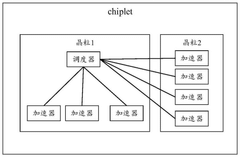

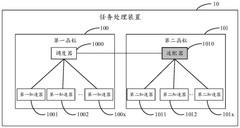

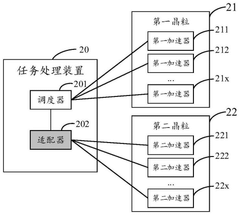

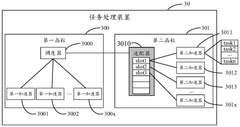

A task processing device, related die, and processing method

PatentPendingCN120256078A

Innovation

- By introducing an adapter into the chiplet to block the solid interface between the scheduler and other die accelerators, decouple the relationship between the scheduler and the accelerator, so that the scheduler can schedule accelerators that cannot be directly scheduled through the adapter, ensuring that all accelerator resources can be effectively utilized.

Standardization Efforts and Interoperability Frameworks

The standardization landscape for chiplet-based RISC-V SoCs has evolved significantly in recent years, with several industry consortia and organizations working to establish common frameworks for interoperability. The CHIPS Alliance, founded in 2019, has been instrumental in developing open-source tools, IP, and design methodologies specifically for RISC-V chiplet integration. Their Universal Chiplet Interconnect Express (UCIe) specification has gained substantial industry adoption, providing a standardized die-to-die interconnect protocol essential for heterogeneous chiplet integration.

Parallel to these efforts, the Open Compute Project (OCP) has established the Open Domain-Specific Architecture (ODSA) subgroup, which focuses on creating specifications for chiplet-based designs. The ODSA has developed the Bunch of Wires (BoW) interface, a simpler alternative to UCIe that offers lower implementation barriers for smaller companies entering the chiplet ecosystem. This diversity of standards reflects the industry's recognition that different applications may require different interconnect solutions.

The RISC-V International organization has responded to the chiplet trend by forming the RISC-V Chiplet Working Group in 2021. This group is specifically tasked with defining standards for RISC-V chiplet interfaces, addressing unique considerations such as coherency protocols and memory models specific to the RISC-V architecture. Their work complements broader industry standards while ensuring optimal performance for RISC-V-based systems.

Interoperability testing frameworks have emerged as critical components of the standardization ecosystem. The Chiplet Design Exchange (CDX), an industry consortium established in 2022, provides reference designs and validation methodologies to ensure compatibility between chiplets from different vendors. These frameworks include standardized test patterns, compliance verification tools, and certification processes that help establish trust in multi-vendor chiplet solutions.

The Common Chiplet Interface (CCI) represents another significant standardization effort, focusing on establishing a unified physical and protocol layer for chiplet communication. CCI 1.0, released in 2023, includes specifications for power management, thermal considerations, and security features—all critical aspects for enterprise-grade RISC-V implementations. This standard has been endorsed by major semiconductor manufacturers and cloud service providers, signaling strong industry alignment.

Looking forward, emerging standards are beginning to address higher-level concerns such as chiplet discovery, configuration, and management. The Chiplet Management Interface (CMI) specification, currently in development, aims to standardize how operating systems and firmware interact with heterogeneous chiplet-based systems, including those built around RISC-V cores. This represents an important evolution from physical interconnect standards toward comprehensive system-level interoperability frameworks.

Parallel to these efforts, the Open Compute Project (OCP) has established the Open Domain-Specific Architecture (ODSA) subgroup, which focuses on creating specifications for chiplet-based designs. The ODSA has developed the Bunch of Wires (BoW) interface, a simpler alternative to UCIe that offers lower implementation barriers for smaller companies entering the chiplet ecosystem. This diversity of standards reflects the industry's recognition that different applications may require different interconnect solutions.

The RISC-V International organization has responded to the chiplet trend by forming the RISC-V Chiplet Working Group in 2021. This group is specifically tasked with defining standards for RISC-V chiplet interfaces, addressing unique considerations such as coherency protocols and memory models specific to the RISC-V architecture. Their work complements broader industry standards while ensuring optimal performance for RISC-V-based systems.

Interoperability testing frameworks have emerged as critical components of the standardization ecosystem. The Chiplet Design Exchange (CDX), an industry consortium established in 2022, provides reference designs and validation methodologies to ensure compatibility between chiplets from different vendors. These frameworks include standardized test patterns, compliance verification tools, and certification processes that help establish trust in multi-vendor chiplet solutions.

The Common Chiplet Interface (CCI) represents another significant standardization effort, focusing on establishing a unified physical and protocol layer for chiplet communication. CCI 1.0, released in 2023, includes specifications for power management, thermal considerations, and security features—all critical aspects for enterprise-grade RISC-V implementations. This standard has been endorsed by major semiconductor manufacturers and cloud service providers, signaling strong industry alignment.

Looking forward, emerging standards are beginning to address higher-level concerns such as chiplet discovery, configuration, and management. The Chiplet Management Interface (CMI) specification, currently in development, aims to standardize how operating systems and firmware interact with heterogeneous chiplet-based systems, including those built around RISC-V cores. This represents an important evolution from physical interconnect standards toward comprehensive system-level interoperability frameworks.

Power and Thermal Management Strategies

Power management in chiplet-based RISC-V SoCs presents unique challenges due to the distributed nature of computing resources across multiple dies. Traditional monolithic SoC power management techniques must be adapted to address the increased complexity of multi-die integration. Current implementations typically employ hierarchical power management architectures where each chiplet maintains local power control while a central management unit coordinates system-wide power states. This approach enables fine-grained power optimization at both the chiplet and system levels.

Thermal management becomes particularly critical in chiplet-based designs due to potential hotspots at die interfaces and varying thermal characteristics across different chiplets. Advanced thermal modeling techniques that account for the three-dimensional heat flow patterns in chiplet packages are essential for accurate thermal prediction. Industry leaders have developed specialized thermal simulation tools that model the unique thermal profiles of chiplet-based systems, enabling designers to identify and mitigate potential thermal issues early in the design process.

Dynamic voltage and frequency scaling (DVFS) strategies for RISC-V chiplet designs require careful coordination across multiple dies. Recent research demonstrates that distributed DVFS controllers with inter-chiplet communication channels can achieve up to 30% better energy efficiency compared to traditional centralized approaches. These systems typically implement fast communication protocols between chiplets to synchronize power state transitions and prevent performance bottlenecks during frequency scaling operations.

Power delivery network (PDN) design presents additional challenges in chiplet architectures. The increased number of power domains and complex current paths necessitate sophisticated PDN modeling and validation. Leading chiplet implementations utilize advanced package-level power distribution techniques, including embedded voltage regulators within the interposer and dedicated power delivery chiplets that optimize power conversion efficiency.

Emerging techniques for chiplet-based RISC-V SoCs include AI-assisted power management that predicts workload patterns across chiplets and proactively adjusts power states. Additionally, heterogeneous chiplet integration enables specialized power management strategies for different functional blocks. For example, accelerator chiplets can implement aggressive power gating during idle periods, while memory chiplets maintain lower power states to preserve data integrity. These advanced approaches demonstrate potential energy efficiency improvements of 40-50% compared to conventional homogeneous power management techniques.

Thermal management becomes particularly critical in chiplet-based designs due to potential hotspots at die interfaces and varying thermal characteristics across different chiplets. Advanced thermal modeling techniques that account for the three-dimensional heat flow patterns in chiplet packages are essential for accurate thermal prediction. Industry leaders have developed specialized thermal simulation tools that model the unique thermal profiles of chiplet-based systems, enabling designers to identify and mitigate potential thermal issues early in the design process.

Dynamic voltage and frequency scaling (DVFS) strategies for RISC-V chiplet designs require careful coordination across multiple dies. Recent research demonstrates that distributed DVFS controllers with inter-chiplet communication channels can achieve up to 30% better energy efficiency compared to traditional centralized approaches. These systems typically implement fast communication protocols between chiplets to synchronize power state transitions and prevent performance bottlenecks during frequency scaling operations.

Power delivery network (PDN) design presents additional challenges in chiplet architectures. The increased number of power domains and complex current paths necessitate sophisticated PDN modeling and validation. Leading chiplet implementations utilize advanced package-level power distribution techniques, including embedded voltage regulators within the interposer and dedicated power delivery chiplets that optimize power conversion efficiency.

Emerging techniques for chiplet-based RISC-V SoCs include AI-assisted power management that predicts workload patterns across chiplets and proactively adjusts power states. Additionally, heterogeneous chiplet integration enables specialized power management strategies for different functional blocks. For example, accelerator chiplets can implement aggressive power gating during idle periods, while memory chiplets maintain lower power states to preserve data integrity. These advanced approaches demonstrate potential energy efficiency improvements of 40-50% compared to conventional homogeneous power management techniques.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!