RISC-V in AUTOSAR and ISO 26262 contexts: safety pathways

AUG 25, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

RISC-V Architecture Evolution and Safety Objectives

RISC-V architecture has evolved significantly since its inception at UC Berkeley in 2010, transforming from an academic project into a global open-source instruction set architecture (ISA) with substantial industry adoption. The initial design focused on simplicity and modularity, with a base integer instruction set (RV32I/RV64I) and optional extensions. This modular approach has proven instrumental in RISC-V's adaptability across various computing domains, from embedded systems to high-performance computing.

In the automotive context, RISC-V's evolution has been marked by increasing emphasis on safety features and deterministic behavior. The architecture has progressively incorporated extensions and specifications that address the rigorous requirements of safety-critical automotive applications. Notable developments include the introduction of privileged architecture specifications, which enable secure isolation between different software components—a critical requirement for AUTOSAR-compliant systems.

The safety objectives for RISC-V in automotive applications are primarily guided by ISO 26262 functional safety standards, which define safety integrity levels (ASILs) and corresponding requirements. For RISC-V to be viable in safety-critical automotive systems, the architecture must support mechanisms for fault detection, isolation, and recovery. This includes features such as error-correcting codes (ECC) for memory protection, lockstep execution for CPU redundancy, and hardware-based isolation mechanisms.

Recent evolution has seen the development of RISC-V extensions specifically targeting safety requirements, such as the "Zicsr" extension for control and status register access, which facilitates monitoring and control of processor state—essential for implementing safety mechanisms. Additionally, the RISC-V foundation has established working groups focused on security and functional safety to standardize approaches across implementations.

The trajectory of RISC-V evolution is increasingly aligned with automotive safety objectives, with a growing emphasis on formal verification and certification pathways. Industry stakeholders are collaborating to develop reference implementations and verification suites that demonstrate compliance with ISO 26262 requirements, establishing clear pathways for certification of RISC-V-based automotive systems.

Looking forward, the RISC-V architecture is expected to continue evolving with enhanced safety features, including standardized fault detection mechanisms, improved temporal isolation capabilities, and more comprehensive verification frameworks. These developments aim to position RISC-V as a compelling alternative to proprietary architectures in safety-critical automotive applications, offering the benefits of openness and customizability without compromising on safety assurance.

In the automotive context, RISC-V's evolution has been marked by increasing emphasis on safety features and deterministic behavior. The architecture has progressively incorporated extensions and specifications that address the rigorous requirements of safety-critical automotive applications. Notable developments include the introduction of privileged architecture specifications, which enable secure isolation between different software components—a critical requirement for AUTOSAR-compliant systems.

The safety objectives for RISC-V in automotive applications are primarily guided by ISO 26262 functional safety standards, which define safety integrity levels (ASILs) and corresponding requirements. For RISC-V to be viable in safety-critical automotive systems, the architecture must support mechanisms for fault detection, isolation, and recovery. This includes features such as error-correcting codes (ECC) for memory protection, lockstep execution for CPU redundancy, and hardware-based isolation mechanisms.

Recent evolution has seen the development of RISC-V extensions specifically targeting safety requirements, such as the "Zicsr" extension for control and status register access, which facilitates monitoring and control of processor state—essential for implementing safety mechanisms. Additionally, the RISC-V foundation has established working groups focused on security and functional safety to standardize approaches across implementations.

The trajectory of RISC-V evolution is increasingly aligned with automotive safety objectives, with a growing emphasis on formal verification and certification pathways. Industry stakeholders are collaborating to develop reference implementations and verification suites that demonstrate compliance with ISO 26262 requirements, establishing clear pathways for certification of RISC-V-based automotive systems.

Looking forward, the RISC-V architecture is expected to continue evolving with enhanced safety features, including standardized fault detection mechanisms, improved temporal isolation capabilities, and more comprehensive verification frameworks. These developments aim to position RISC-V as a compelling alternative to proprietary architectures in safety-critical automotive applications, offering the benefits of openness and customizability without compromising on safety assurance.

Automotive Market Demand for RISC-V Solutions

The automotive industry is witnessing a significant shift towards more sophisticated electronic systems, creating a growing demand for RISC-V based solutions. This demand is primarily driven by the increasing complexity of advanced driver-assistance systems (ADAS), autonomous driving capabilities, and connected vehicle technologies that require more powerful and flexible computing architectures.

Market research indicates that the automotive semiconductor market is projected to grow substantially over the next decade, with a particular emphasis on processors that can deliver high performance while maintaining stringent safety standards. RISC-V, with its open-source instruction set architecture (ISA), presents a compelling alternative to proprietary architectures that have traditionally dominated the automotive sector.

Vehicle manufacturers and tier-1 suppliers are increasingly seeking solutions that offer greater customization options, reduced licensing costs, and enhanced security features. RISC-V addresses these needs through its modular design approach, allowing automotive companies to tailor processor implementations to specific use cases while maintaining compatibility with industry standards.

The demand for RISC-V in automotive applications is further amplified by the industry's push towards software-defined vehicles. These next-generation vehicles require flexible computing platforms that can support over-the-air updates and accommodate evolving software requirements throughout the vehicle's lifecycle. RISC-V's extensible architecture provides the necessary foundation for these capabilities.

Safety-critical automotive systems, including braking, steering, and powertrain control, require processors that can meet the highest Automotive Safety Integrity Levels (ASIL) as defined by ISO 26262. Market analysis shows increasing interest in RISC-V implementations that incorporate robust safety mechanisms and can achieve ASIL-D certification, the most stringent safety level for automotive applications.

The automotive industry's transition to electric vehicles (EVs) and hybrid electric vehicles (HEVs) is creating additional demand for efficient computing solutions. Battery management systems, power electronics controllers, and motor control units in these vehicles benefit from RISC-V's scalable architecture and energy efficiency characteristics.

Regional market analysis reveals that European automotive manufacturers, with their strong focus on safety and standardization through AUTOSAR, are showing particular interest in RISC-V solutions that can seamlessly integrate with existing automotive software architectures while providing pathways to future innovation. Similarly, Asian markets, especially China and Japan, are investing heavily in RISC-V technology for automotive applications as part of broader initiatives to develop domestic semiconductor capabilities.

Market research indicates that the automotive semiconductor market is projected to grow substantially over the next decade, with a particular emphasis on processors that can deliver high performance while maintaining stringent safety standards. RISC-V, with its open-source instruction set architecture (ISA), presents a compelling alternative to proprietary architectures that have traditionally dominated the automotive sector.

Vehicle manufacturers and tier-1 suppliers are increasingly seeking solutions that offer greater customization options, reduced licensing costs, and enhanced security features. RISC-V addresses these needs through its modular design approach, allowing automotive companies to tailor processor implementations to specific use cases while maintaining compatibility with industry standards.

The demand for RISC-V in automotive applications is further amplified by the industry's push towards software-defined vehicles. These next-generation vehicles require flexible computing platforms that can support over-the-air updates and accommodate evolving software requirements throughout the vehicle's lifecycle. RISC-V's extensible architecture provides the necessary foundation for these capabilities.

Safety-critical automotive systems, including braking, steering, and powertrain control, require processors that can meet the highest Automotive Safety Integrity Levels (ASIL) as defined by ISO 26262. Market analysis shows increasing interest in RISC-V implementations that incorporate robust safety mechanisms and can achieve ASIL-D certification, the most stringent safety level for automotive applications.

The automotive industry's transition to electric vehicles (EVs) and hybrid electric vehicles (HEVs) is creating additional demand for efficient computing solutions. Battery management systems, power electronics controllers, and motor control units in these vehicles benefit from RISC-V's scalable architecture and energy efficiency characteristics.

Regional market analysis reveals that European automotive manufacturers, with their strong focus on safety and standardization through AUTOSAR, are showing particular interest in RISC-V solutions that can seamlessly integrate with existing automotive software architectures while providing pathways to future innovation. Similarly, Asian markets, especially China and Japan, are investing heavily in RISC-V technology for automotive applications as part of broader initiatives to develop domestic semiconductor capabilities.

RISC-V Implementation Challenges in Safety-Critical Systems

The implementation of RISC-V architecture in safety-critical automotive systems presents significant challenges that must be addressed to ensure compliance with AUTOSAR standards and ISO 26262 functional safety requirements. These challenges span hardware design, software development, verification methodologies, and certification processes.

Hardware-level challenges include developing RISC-V cores with robust fault detection and containment mechanisms. Traditional safety features like lockstep execution, ECC memory protection, and hardware redundancy must be adapted to the RISC-V architecture while maintaining its performance advantages. The open nature of RISC-V introduces variability in implementations that complicates safety assessments compared to established architectures with standardized safety features.

Software development faces the challenge of creating AUTOSAR-compliant runtime environments optimized for RISC-V. This requires adaptation of existing AUTOSAR basic software components, development of new hardware abstraction layers, and creation of RISC-V-specific device drivers. The relative immaturity of RISC-V toolchains for safety-critical applications presents additional obstacles in generating reliable code with predictable behavior.

Verification and validation processes must be enhanced to address RISC-V's architectural flexibility. Traditional test methodologies may be insufficient due to the customizable nature of RISC-V implementations. Formal verification techniques need adaptation to handle the architectural variations possible with RISC-V cores, requiring new approaches to safety case construction.

Certification challenges are particularly significant as RISC-V lacks the established safety track record of architectures like ARM or PowerPC in automotive applications. Safety assessors and certification bodies have limited experience evaluating RISC-V implementations against ISO 26262 requirements, potentially leading to more stringent evidence demands and longer certification timelines.

Supply chain considerations introduce further complexity, as the ecosystem of safety-qualified RISC-V IP, development tools, and verification environments is still evolving. Automotive manufacturers must carefully evaluate the maturity and sustainability of RISC-V suppliers to ensure long-term support for safety-critical components.

Timing predictability and determinism present technical hurdles, particularly for real-time automotive applications. Features like out-of-order execution and speculative processing in high-performance RISC-V implementations can complicate worst-case execution time analysis, essential for safety-critical systems with strict timing requirements.

Finally, the integration of RISC-V processors into existing automotive architectures requires careful consideration of interfaces with legacy systems, migration strategies, and hybrid approaches during transition periods. This integration challenge extends beyond technical aspects to include organizational and process adaptations within automotive development teams.

Hardware-level challenges include developing RISC-V cores with robust fault detection and containment mechanisms. Traditional safety features like lockstep execution, ECC memory protection, and hardware redundancy must be adapted to the RISC-V architecture while maintaining its performance advantages. The open nature of RISC-V introduces variability in implementations that complicates safety assessments compared to established architectures with standardized safety features.

Software development faces the challenge of creating AUTOSAR-compliant runtime environments optimized for RISC-V. This requires adaptation of existing AUTOSAR basic software components, development of new hardware abstraction layers, and creation of RISC-V-specific device drivers. The relative immaturity of RISC-V toolchains for safety-critical applications presents additional obstacles in generating reliable code with predictable behavior.

Verification and validation processes must be enhanced to address RISC-V's architectural flexibility. Traditional test methodologies may be insufficient due to the customizable nature of RISC-V implementations. Formal verification techniques need adaptation to handle the architectural variations possible with RISC-V cores, requiring new approaches to safety case construction.

Certification challenges are particularly significant as RISC-V lacks the established safety track record of architectures like ARM or PowerPC in automotive applications. Safety assessors and certification bodies have limited experience evaluating RISC-V implementations against ISO 26262 requirements, potentially leading to more stringent evidence demands and longer certification timelines.

Supply chain considerations introduce further complexity, as the ecosystem of safety-qualified RISC-V IP, development tools, and verification environments is still evolving. Automotive manufacturers must carefully evaluate the maturity and sustainability of RISC-V suppliers to ensure long-term support for safety-critical components.

Timing predictability and determinism present technical hurdles, particularly for real-time automotive applications. Features like out-of-order execution and speculative processing in high-performance RISC-V implementations can complicate worst-case execution time analysis, essential for safety-critical systems with strict timing requirements.

Finally, the integration of RISC-V processors into existing automotive architectures requires careful consideration of interfaces with legacy systems, migration strategies, and hybrid approaches during transition periods. This integration challenge extends beyond technical aspects to include organizational and process adaptations within automotive development teams.

Current AUTOSAR Integration Approaches for RISC-V

01 RISC-V Safety Architecture Implementation

RISC-V processors can be designed with specific safety architecture features to ensure reliable operation in critical applications. These implementations include redundant execution units, error detection and correction mechanisms, and safety monitoring circuits. The architecture allows for configurable safety levels depending on the application requirements, with features that can detect and mitigate hardware faults during operation.- RISC-V Safety Architecture Implementation: RISC-V architecture can be implemented with specific safety features to ensure reliable operation in critical systems. These implementations include hardware-level safety mechanisms, redundant execution paths, and specialized instruction sets designed to detect and mitigate faults. The architecture allows for configurable safety features that can be tailored to different safety integrity levels required by various industries such as automotive, medical, and industrial control systems.

- Fault Detection and Isolation in RISC-V Processors: RISC-V processors can incorporate fault detection mechanisms that monitor execution flow and data integrity. These mechanisms include error detection codes, watchdog timers, and specialized exception handling for safety-critical operations. When faults are detected, isolation techniques prevent propagation of errors to other system components, allowing for graceful degradation or safe shutdown procedures. These features are essential for achieving functional safety certification in RISC-V based systems.

- RISC-V Safety Verification and Certification Pathways: Verification methodologies specific to RISC-V safety implementations ensure compliance with safety standards such as ISO 26262, IEC 61508, and DO-254. These pathways include formal verification techniques, safety case development, and systematic testing approaches tailored to the open instruction set architecture. The certification process involves documenting safety mechanisms, performing failure mode analysis, and demonstrating sufficient diagnostic coverage to meet required safety integrity levels.

- Redundancy and Diversity in RISC-V Safety Systems: Safety-critical RISC-V implementations often employ redundancy and diversity strategies to achieve higher reliability. These include dual-core lockstep execution, triple modular redundancy, and diverse implementations of critical functions. By using different hardware or software implementations to perform the same function, common mode failures can be mitigated. The flexible nature of RISC-V architecture allows for efficient implementation of these redundancy schemes while maintaining performance requirements.

- RISC-V Safety Extensions and Custom Instructions: The extensible nature of RISC-V allows for the implementation of safety-specific instruction set extensions. These extensions can include atomic operations for reliable inter-process communication, memory protection instructions, and specialized safety monitoring operations. Custom instructions can be added to accelerate safety-critical functions such as error detection and correction, secure boot processes, and runtime verification. These extensions enable more efficient implementation of safety features while maintaining the core benefits of the RISC-V architecture.

02 Fault Detection and Recovery Mechanisms

Safety pathways in RISC-V processors incorporate various fault detection and recovery mechanisms to maintain system integrity. These include instruction-level redundancy, checkpoint-based recovery systems, and hardware-based error detection circuits. When faults are detected, the processor can initiate recovery procedures such as instruction replay, state rollback, or switching to redundant execution units to ensure continuous safe operation.Expand Specific Solutions03 Safety Certification Compliance Methods

Implementing RISC-V processors in safety-critical applications requires compliance with industry safety standards. Methods to achieve certification include formal verification of the instruction set architecture, systematic documentation of safety features, and development of safety cases. The open nature of RISC-V allows for transparent verification processes and customizable safety extensions that can be tailored to meet specific certification requirements for automotive, industrial, or medical applications.Expand Specific Solutions04 Secure Execution Environment

RISC-V safety pathways include secure execution environments that isolate critical processes from potential security threats. These environments implement privilege separation, memory protection units, and secure boot mechanisms. By establishing trusted execution regions within the processor architecture, safety-critical code can run without interference from less trusted components, enhancing overall system safety and security.Expand Specific Solutions05 Real-time Monitoring and Diagnostics

Safety-oriented RISC-V implementations feature comprehensive real-time monitoring and diagnostic capabilities. These include performance counters, watchdog timers, and built-in self-test mechanisms that continuously verify proper operation. The monitoring systems can detect timing violations, execution anomalies, and hardware degradation before they lead to system failures, enabling preventive maintenance and enhancing the overall safety profile of the system.Expand Specific Solutions

Key Stakeholders in Automotive RISC-V Ecosystem

RISC-V is emerging as a significant player in the automotive safety landscape, particularly within AUTOSAR and ISO 26262 frameworks. The market is in its early growth phase, with increasing adoption driven by the need for open-source architectures in safety-critical applications. Companies like Texas Instruments, Robert Bosch, Mobileye, and NXP Semiconductors are leading implementation efforts, while automotive manufacturers including BMW and GM are exploring integration possibilities. The technology's maturity is advancing rapidly, with semiconductor leaders such as NVIDIA, Infineon, and Qualcomm investing in RISC-V safety certification pathways. The competitive landscape shows a collaborative ecosystem developing between chip manufacturers, automotive suppliers, and OEMs to establish RISC-V as a viable alternative for safety-compliant automotive computing platforms.

Robert Bosch GmbH

Technical Solution: Bosch has developed a comprehensive RISC-V implementation strategy for AUTOSAR-compliant systems that integrates safety mechanisms at multiple levels. Their approach includes hardware-level safety features such as dual-core lockstep configurations with error detection circuits and memory protection units specifically designed for RISC-V cores. Bosch's implementation incorporates AUTOSAR-compliant software components with safety wrappers that monitor execution flow and timing constraints. For ISO 26262 compliance, they've created a specialized safety island architecture using a dedicated RISC-V core that monitors the main application processors and can initiate safe states during detected failures. Their safety documentation package includes detailed Failure Mode and Effects Analysis (FMEA) and fault injection test results demonstrating ASIL-D capability for critical automotive functions.

Strengths: Extensive automotive domain expertise allows for highly optimized safety solutions; established AUTOSAR tool chain integration provides seamless development experience. Weaknesses: Proprietary safety extensions may limit compatibility with standard RISC-V ecosystem; higher implementation complexity compared to traditional architectures increases development overhead.

NVIDIA Corp.

Technical Solution: NVIDIA has implemented a heterogeneous computing architecture that combines RISC-V safety processors with their GPU technology for autonomous driving platforms. Their DRIVE platform incorporates dedicated RISC-V cores as safety processing units that monitor the main application processors and can initiate safe states during detected failures. NVIDIA's implementation features hardware-level isolation between safety-critical and non-safety functions, with formal verification of the isolation mechanisms. For AUTOSAR compatibility, they've developed a specialized hypervisor that enables running AUTOSAR-compliant software alongside other operating systems while maintaining safety properties. Their safety architecture includes redundant execution paths with cross-checking mechanisms and specialized hardware accelerators for safety-critical operations such as sensor data validation. NVIDIA provides a comprehensive safety package including detailed fault models, safety analysis documentation, and diagnostic coverage assessments aligned with ISO 26262 requirements up to ASIL-D for their RISC-V safety processors.

Strengths: Powerful heterogeneous computing capabilities enable advanced driver assistance features; extensive AI expertise enhances safety monitoring capabilities. Weaknesses: Complex architecture increases system integration challenges; higher power requirements may limit applicability in some vehicle platforms.

Critical Safety Mechanisms for RISC-V in ISO 26262

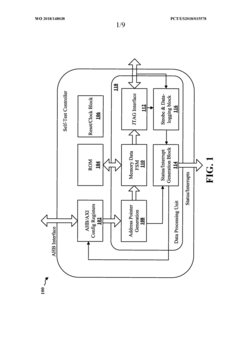

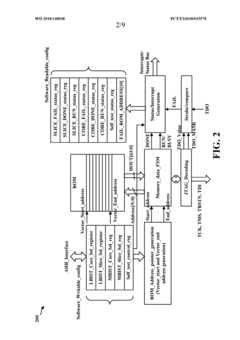

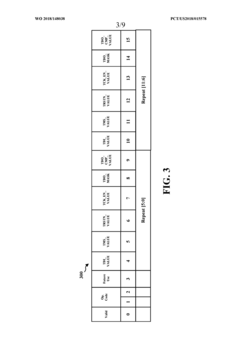

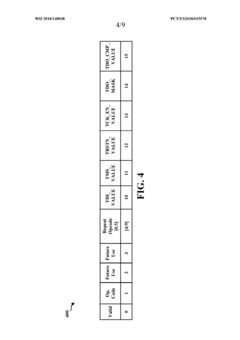

In-field multi core self-test controller with stored test pattern for safety critical automotive use cases

PatentWO2018148038A1

Innovation

- A self-test controller with a memory configured to store test patterns that include test subpatterns for different test cores, using configuration registers to select enabled cores and a memory data component to decode and generate JTAG vectors dynamically, reducing storage needs by assuming all test cores are enabled and using repetition values to eliminate redundant test data.

RF/mm-wave peak detector with high-dynamic range calibration

PatentWO2017070681A1

Innovation

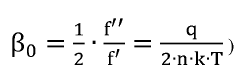

- An integrated circuit with diode-based mm-wave peak voltage detectors employs a multi-point low-frequency calibration and current-voltage sweep to determine AC and DC coefficients, followed by RF correlated double-sampling for precise power measurement, enabling a built-in self-test network for failure mode detection and performance adaptation, while reducing RF test costs.

Regulatory Compliance Framework for RISC-V Adoption

The regulatory landscape for RISC-V adoption in automotive applications is governed by two primary frameworks: AUTOSAR (AUTomotive Open System ARchitecture) and ISO 26262 (Road vehicles - Functional safety). These frameworks establish the compliance requirements that RISC-V implementations must satisfy to ensure safety and reliability in automotive systems.

AUTOSAR provides a standardized software architecture for automotive electronic control units (ECUs), consisting of two main variants: Classic Platform for safety-critical applications and Adaptive Platform for high-performance computing applications. For RISC-V integration, compliance with AUTOSAR specifications requires adherence to the Runtime Environment (RTE) interfaces and Basic Software Module (BSW) implementations that are architecture-independent but must be validated for RISC-V-specific implementations.

ISO 26262 establishes a comprehensive framework for functional safety in automotive systems, categorizing safety requirements through Automotive Safety Integrity Levels (ASIL) ranging from A (lowest) to D (highest). RISC-V implementations must undergo systematic hazard analysis and risk assessment (HARA) to determine appropriate ASIL classifications for specific functions.

The certification pathway for RISC-V processors involves several critical steps. Initially, hardware-specific safety mechanisms must be implemented, including Error Correction Codes (ECC) for memory protection, lockstep execution for core redundancy, and hardware diagnostic features. Subsequently, safety documentation must be developed, encompassing safety manuals, failure mode and effects analysis (FMEA), and fault tree analysis (FTA).

Safety case development represents a crucial element in the compliance framework, requiring comprehensive evidence that the RISC-V implementation meets all applicable safety requirements. This includes verification and validation results, formal proofs of correctness for critical components, and systematic testing documentation.

Tool qualification presents a significant challenge in the RISC-V compliance landscape. Development tools, including compilers, debuggers, and simulation environments, must be qualified according to ISO 26262 standards to ensure they do not introduce systematic faults into the development process. Currently, the ecosystem of qualified tools for RISC-V is still maturing compared to established architectures.

Traceability requirements mandate comprehensive documentation linking safety requirements to implementation details and verification results throughout the development lifecycle. This creates a verifiable chain of evidence demonstrating that all safety requirements have been properly implemented and validated in the final RISC-V-based system.

AUTOSAR provides a standardized software architecture for automotive electronic control units (ECUs), consisting of two main variants: Classic Platform for safety-critical applications and Adaptive Platform for high-performance computing applications. For RISC-V integration, compliance with AUTOSAR specifications requires adherence to the Runtime Environment (RTE) interfaces and Basic Software Module (BSW) implementations that are architecture-independent but must be validated for RISC-V-specific implementations.

ISO 26262 establishes a comprehensive framework for functional safety in automotive systems, categorizing safety requirements through Automotive Safety Integrity Levels (ASIL) ranging from A (lowest) to D (highest). RISC-V implementations must undergo systematic hazard analysis and risk assessment (HARA) to determine appropriate ASIL classifications for specific functions.

The certification pathway for RISC-V processors involves several critical steps. Initially, hardware-specific safety mechanisms must be implemented, including Error Correction Codes (ECC) for memory protection, lockstep execution for core redundancy, and hardware diagnostic features. Subsequently, safety documentation must be developed, encompassing safety manuals, failure mode and effects analysis (FMEA), and fault tree analysis (FTA).

Safety case development represents a crucial element in the compliance framework, requiring comprehensive evidence that the RISC-V implementation meets all applicable safety requirements. This includes verification and validation results, formal proofs of correctness for critical components, and systematic testing documentation.

Tool qualification presents a significant challenge in the RISC-V compliance landscape. Development tools, including compilers, debuggers, and simulation environments, must be qualified according to ISO 26262 standards to ensure they do not introduce systematic faults into the development process. Currently, the ecosystem of qualified tools for RISC-V is still maturing compared to established architectures.

Traceability requirements mandate comprehensive documentation linking safety requirements to implementation details and verification results throughout the development lifecycle. This creates a verifiable chain of evidence demonstrating that all safety requirements have been properly implemented and validated in the final RISC-V-based system.

Risk Assessment Methodologies for RISC-V-Based ECUs

Risk assessment for RISC-V-based Electronic Control Units (ECUs) requires specialized methodologies that address the unique characteristics of this open-source instruction set architecture within automotive safety contexts. These methodologies must align with both AUTOSAR (Automotive Open System Architecture) standards and ISO 26262 functional safety requirements for road vehicles.

The primary risk assessment approach begins with systematic hazard identification specific to RISC-V implementations. This includes analyzing potential failure modes in the instruction set architecture, hardware implementations, and compiler toolchains that may not be present in traditional proprietary architectures. The open-source nature of RISC-V introduces unique verification challenges that must be addressed through comprehensive risk models.

Fault tree analysis (FTA) adapted for RISC-V architectures represents a critical methodology component. This involves constructing hierarchical diagrams that map potential failure paths from system-level hazards down to specific RISC-V hardware or software components. The analysis must account for RISC-V-specific features such as custom extensions and implementation-defined behaviors that may impact safety properties.

Failure Mode and Effects Analysis (FMEA) for RISC-V ECUs requires particular attention to the interface between standardized AUTOSAR software components and the underlying RISC-V hardware. This includes evaluating how hardware exceptions, interrupts, and memory protection mechanisms specific to RISC-V implementations interact with AUTOSAR's safety mechanisms.

Quantitative risk assessment techniques must incorporate RISC-V-specific reliability data, which presents challenges due to the relatively limited deployment history compared to established architectures. Statistical models must be developed that can extrapolate from available data while accounting for the architectural differences of RISC-V.

Safety integrity level (SIL) allocation methodologies for RISC-V-based systems require careful consideration of the verification status of different components. This includes evaluating formal verification coverage of the instruction set implementation and hardware design, as well as the maturity of development tools and runtime environments.

Hardware-software interface analysis takes on heightened importance for RISC-V implementations, as the boundary between hardware and software is more configurable than in traditional architectures. Risk assessment must evaluate how custom instructions or hardware accelerators might impact safety properties and verification strategies.

Continuous risk monitoring frameworks must be established to track emerging vulnerabilities or design issues in the RISC-V ecosystem, ensuring that safety assessments remain valid throughout the vehicle lifecycle. This includes processes for evaluating the impact of updates to open-source components and ensuring appropriate regression testing.

The primary risk assessment approach begins with systematic hazard identification specific to RISC-V implementations. This includes analyzing potential failure modes in the instruction set architecture, hardware implementations, and compiler toolchains that may not be present in traditional proprietary architectures. The open-source nature of RISC-V introduces unique verification challenges that must be addressed through comprehensive risk models.

Fault tree analysis (FTA) adapted for RISC-V architectures represents a critical methodology component. This involves constructing hierarchical diagrams that map potential failure paths from system-level hazards down to specific RISC-V hardware or software components. The analysis must account for RISC-V-specific features such as custom extensions and implementation-defined behaviors that may impact safety properties.

Failure Mode and Effects Analysis (FMEA) for RISC-V ECUs requires particular attention to the interface between standardized AUTOSAR software components and the underlying RISC-V hardware. This includes evaluating how hardware exceptions, interrupts, and memory protection mechanisms specific to RISC-V implementations interact with AUTOSAR's safety mechanisms.

Quantitative risk assessment techniques must incorporate RISC-V-specific reliability data, which presents challenges due to the relatively limited deployment history compared to established architectures. Statistical models must be developed that can extrapolate from available data while accounting for the architectural differences of RISC-V.

Safety integrity level (SIL) allocation methodologies for RISC-V-based systems require careful consideration of the verification status of different components. This includes evaluating formal verification coverage of the instruction set implementation and hardware design, as well as the maturity of development tools and runtime environments.

Hardware-software interface analysis takes on heightened importance for RISC-V implementations, as the boundary between hardware and software is more configurable than in traditional architectures. Risk assessment must evaluate how custom instructions or hardware accelerators might impact safety properties and verification strategies.

Continuous risk monitoring frameworks must be established to track emerging vulnerabilities or design issues in the RISC-V ecosystem, ensuring that safety assessments remain valid throughout the vehicle lifecycle. This includes processes for evaluating the impact of updates to open-source components and ensuring appropriate regression testing.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!