RISC-V for wearables and IoT: power budgeting and DVFS

AUG 25, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

RISC-V Architecture Evolution and Power Efficiency Goals

RISC-V architecture has evolved significantly since its inception at UC Berkeley in 2010, transitioning from an academic project to a global open-source instruction set architecture (ISA) with substantial industry adoption. The initial design focused on simplicity and modularity, featuring a base integer instruction set (RV32I/RV64I) with optional extensions. This modular approach has proven particularly advantageous for wearable and IoT applications, where customization for specific power and performance requirements is essential.

The evolution of RISC-V has been marked by the development of specialized extensions targeting low-power applications. Notable among these are the "E" extension for embedded systems, which reduces register file size, and the "C" extension for compressed instructions, which decreases code size and memory access energy. Recent developments include the "P" extension for packed SIMD operations and the "B" extension for bit manipulation, both enhancing computational efficiency for IoT workloads.

Power efficiency has emerged as a primary design goal in RISC-V development for wearable and IoT devices, which typically operate under strict energy constraints. These devices often run on small batteries or energy harvesting systems, necessitating ultra-low power consumption while maintaining adequate performance for tasks like sensor data processing, wireless communication, and basic user interface operations. The industry has established ambitious power efficiency targets, with many applications requiring operation in the microwatt to milliwatt range.

The technical community has defined several key power efficiency metrics for RISC-V implementations in wearable and IoT contexts. These include energy per instruction (EPI), performance per watt, and static power consumption during various sleep modes. Leading implementations now target sub-1mW active power consumption and sub-1µW deep sleep power, with wake-up times under 100µs to support intermittent computing paradigms common in IoT applications.

Dynamic Voltage and Frequency Scaling (DVFS) has become a central technique in achieving these power goals. The RISC-V architecture's clean design facilitates implementation of fine-grained DVFS mechanisms, allowing for rapid transitions between performance states. Advanced implementations now incorporate multiple voltage domains, adaptive body biasing, and sophisticated power gating techniques to minimize both dynamic and static power consumption.

Looking forward, the RISC-V community has outlined roadmaps for further power efficiency improvements, including enhanced support for near-threshold computing, specialized accelerators for common IoT workloads, and improved power management extensions to the ISA. These developments aim to position RISC-V as the architecture of choice for next-generation ultra-low-power wearable and IoT applications.

The evolution of RISC-V has been marked by the development of specialized extensions targeting low-power applications. Notable among these are the "E" extension for embedded systems, which reduces register file size, and the "C" extension for compressed instructions, which decreases code size and memory access energy. Recent developments include the "P" extension for packed SIMD operations and the "B" extension for bit manipulation, both enhancing computational efficiency for IoT workloads.

Power efficiency has emerged as a primary design goal in RISC-V development for wearable and IoT devices, which typically operate under strict energy constraints. These devices often run on small batteries or energy harvesting systems, necessitating ultra-low power consumption while maintaining adequate performance for tasks like sensor data processing, wireless communication, and basic user interface operations. The industry has established ambitious power efficiency targets, with many applications requiring operation in the microwatt to milliwatt range.

The technical community has defined several key power efficiency metrics for RISC-V implementations in wearable and IoT contexts. These include energy per instruction (EPI), performance per watt, and static power consumption during various sleep modes. Leading implementations now target sub-1mW active power consumption and sub-1µW deep sleep power, with wake-up times under 100µs to support intermittent computing paradigms common in IoT applications.

Dynamic Voltage and Frequency Scaling (DVFS) has become a central technique in achieving these power goals. The RISC-V architecture's clean design facilitates implementation of fine-grained DVFS mechanisms, allowing for rapid transitions between performance states. Advanced implementations now incorporate multiple voltage domains, adaptive body biasing, and sophisticated power gating techniques to minimize both dynamic and static power consumption.

Looking forward, the RISC-V community has outlined roadmaps for further power efficiency improvements, including enhanced support for near-threshold computing, specialized accelerators for common IoT workloads, and improved power management extensions to the ISA. These developments aim to position RISC-V as the architecture of choice for next-generation ultra-low-power wearable and IoT applications.

Market Demand Analysis for Low-Power Wearable and IoT Solutions

The wearable and IoT device market is experiencing unprecedented growth, with global shipments of wearable devices reaching 533.6 million units in 2021 and projected to surpass 1 billion units by 2026. This explosive growth is driven by increasing consumer demand for health monitoring, fitness tracking, and smart home automation solutions. The COVID-19 pandemic has further accelerated this trend, with heightened awareness of personal health monitoring creating new market opportunities.

Within this expanding market, power efficiency has emerged as the primary concern for both manufacturers and consumers. Battery life consistently ranks as the top purchasing consideration in consumer surveys, outweighing other factors such as price and features. Market research indicates that devices requiring charging less than once per week see 63% higher consumer satisfaction rates compared to those needing daily charging.

The industrial IoT segment demonstrates particularly strong demand for ultra-low-power solutions, with energy harvesting capabilities becoming increasingly important. This sector is projected to grow at a CAGR of 22.3% through 2027, with power efficiency being the critical enabler for widespread deployment in remote monitoring applications.

Geographically, North America and Europe currently lead in wearable technology adoption, but the Asia-Pacific region shows the fastest growth rate, particularly in China and India. These emerging markets are characterized by price sensitivity, making cost-effective low-power solutions especially valuable.

Market analysis reveals significant untapped potential in healthcare wearables, where continuous monitoring requires exceptional power efficiency. The medical wearables segment is expected to grow at 26.4% CAGR through 2028, with devices requiring certification for reliability and consistent performance under varying power conditions.

Consumer expectations are evolving toward "invisible technology" - devices that integrate seamlessly into daily life without frequent charging interruptions. This trend favors solutions like RISC-V with dynamic voltage and frequency scaling (DVFS) capabilities that can adapt power consumption to usage patterns.

Enterprise and industrial customers increasingly demand customizable power profiles for specific deployment scenarios, creating opportunities for flexible architectures. The ability to optimize power budgets for specific workloads represents a key differentiator in the competitive landscape, with 78% of enterprise IoT decision-makers citing power management capabilities as "very important" or "critical" in recent surveys.

Within this expanding market, power efficiency has emerged as the primary concern for both manufacturers and consumers. Battery life consistently ranks as the top purchasing consideration in consumer surveys, outweighing other factors such as price and features. Market research indicates that devices requiring charging less than once per week see 63% higher consumer satisfaction rates compared to those needing daily charging.

The industrial IoT segment demonstrates particularly strong demand for ultra-low-power solutions, with energy harvesting capabilities becoming increasingly important. This sector is projected to grow at a CAGR of 22.3% through 2027, with power efficiency being the critical enabler for widespread deployment in remote monitoring applications.

Geographically, North America and Europe currently lead in wearable technology adoption, but the Asia-Pacific region shows the fastest growth rate, particularly in China and India. These emerging markets are characterized by price sensitivity, making cost-effective low-power solutions especially valuable.

Market analysis reveals significant untapped potential in healthcare wearables, where continuous monitoring requires exceptional power efficiency. The medical wearables segment is expected to grow at 26.4% CAGR through 2028, with devices requiring certification for reliability and consistent performance under varying power conditions.

Consumer expectations are evolving toward "invisible technology" - devices that integrate seamlessly into daily life without frequent charging interruptions. This trend favors solutions like RISC-V with dynamic voltage and frequency scaling (DVFS) capabilities that can adapt power consumption to usage patterns.

Enterprise and industrial customers increasingly demand customizable power profiles for specific deployment scenarios, creating opportunities for flexible architectures. The ability to optimize power budgets for specific workloads represents a key differentiator in the competitive landscape, with 78% of enterprise IoT decision-makers citing power management capabilities as "very important" or "critical" in recent surveys.

Current RISC-V Implementation Challenges in Power-Constrained Devices

Despite the promising attributes of RISC-V architecture for wearable and IoT applications, several significant implementation challenges persist when deploying this architecture in power-constrained devices. The primary obstacle remains the optimization of power consumption while maintaining adequate performance levels. Current RISC-V implementations often struggle to achieve the ultra-low power requirements of wearable devices, which typically operate on batteries with limited capacity and require extended operational periods between charges.

The implementation of effective Dynamic Voltage and Frequency Scaling (DVFS) mechanisms presents particular difficulties in the RISC-V ecosystem. While the architecture theoretically supports various power states, the practical implementation of fine-grained power management remains underdeveloped compared to more established architectures like ARM. Many existing RISC-V cores lack sophisticated power gating capabilities that can selectively deactivate unused components during idle periods.

Memory subsystem optimization represents another critical challenge. Current RISC-V implementations for wearables often face difficulties balancing the need for low-latency memory access with power efficiency requirements. The memory hierarchy design must accommodate both performance demands and strict power budgets, a balance that current solutions have not fully achieved.

Interrupt handling mechanisms in power-constrained RISC-V implementations present additional complications. The architecture must support rapid wake-from-sleep capabilities to respond to external events while minimizing power consumption during idle states. Current implementations often exhibit suboptimal wake-up latencies or excessive power draw during interrupt processing.

Thermal management issues further compound these challenges, particularly in compact wearable form factors where heat dissipation options are limited. RISC-V implementations must incorporate effective thermal throttling mechanisms that can dynamically adjust performance to prevent overheating without significantly compromising user experience.

The fragmentation within the RISC-V ecosystem also impedes standardized power management approaches. Various implementations offer different power management features, creating inconsistencies across the ecosystem and complicating the development of unified power optimization strategies. This fragmentation extends to development tools, where power analysis and optimization capabilities remain less mature than those available for established architectures.

Integration challenges with specialized hardware accelerators represent another significant hurdle. While offloading specific tasks to dedicated hardware can improve energy efficiency, the current RISC-V ecosystem lacks standardized interfaces for seamlessly incorporating and managing these accelerators within a cohesive power management framework.

The implementation of effective Dynamic Voltage and Frequency Scaling (DVFS) mechanisms presents particular difficulties in the RISC-V ecosystem. While the architecture theoretically supports various power states, the practical implementation of fine-grained power management remains underdeveloped compared to more established architectures like ARM. Many existing RISC-V cores lack sophisticated power gating capabilities that can selectively deactivate unused components during idle periods.

Memory subsystem optimization represents another critical challenge. Current RISC-V implementations for wearables often face difficulties balancing the need for low-latency memory access with power efficiency requirements. The memory hierarchy design must accommodate both performance demands and strict power budgets, a balance that current solutions have not fully achieved.

Interrupt handling mechanisms in power-constrained RISC-V implementations present additional complications. The architecture must support rapid wake-from-sleep capabilities to respond to external events while minimizing power consumption during idle states. Current implementations often exhibit suboptimal wake-up latencies or excessive power draw during interrupt processing.

Thermal management issues further compound these challenges, particularly in compact wearable form factors where heat dissipation options are limited. RISC-V implementations must incorporate effective thermal throttling mechanisms that can dynamically adjust performance to prevent overheating without significantly compromising user experience.

The fragmentation within the RISC-V ecosystem also impedes standardized power management approaches. Various implementations offer different power management features, creating inconsistencies across the ecosystem and complicating the development of unified power optimization strategies. This fragmentation extends to development tools, where power analysis and optimization capabilities remain less mature than those available for established architectures.

Integration challenges with specialized hardware accelerators represent another significant hurdle. While offloading specific tasks to dedicated hardware can improve energy efficiency, the current RISC-V ecosystem lacks standardized interfaces for seamlessly incorporating and managing these accelerators within a cohesive power management framework.

Existing DVFS Implementation Strategies for RISC-V

01 DVFS techniques for RISC-V processors

Dynamic Voltage and Frequency Scaling (DVFS) techniques specifically designed for RISC-V architecture processors enable power optimization by adjusting voltage and frequency based on workload demands. These implementations include specialized hardware controllers and software algorithms that monitor processor utilization and adjust power parameters accordingly, allowing for significant energy savings while maintaining performance requirements.- DVFS implementation in RISC-V processors: Dynamic Voltage and Frequency Scaling (DVFS) techniques specifically designed for RISC-V architecture processors enable power optimization by adjusting voltage and frequency based on workload demands. These implementations include specialized hardware controllers and software interfaces that allow for fine-grained control of power states while maintaining performance requirements. The RISC-V open architecture provides flexibility for customized DVFS solutions that can be tailored to specific application needs.

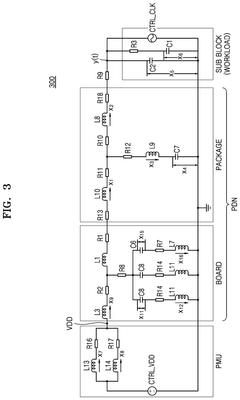

- Power management units for RISC-V systems: Dedicated power management units (PMUs) designed for RISC-V processors provide comprehensive power control capabilities. These units monitor system activity, manage power domains, and implement power gating techniques to reduce static and dynamic power consumption. The PMUs include specialized registers and control interfaces that allow software to configure power states and thresholds based on system requirements, enabling efficient power budgeting across different operational scenarios.

- Workload-aware power optimization for RISC-V: Workload-aware power optimization techniques for RISC-V processors analyze execution patterns and resource utilization to make intelligent power management decisions. These systems employ predictive algorithms that anticipate processing needs and adjust power allocation accordingly. By understanding application characteristics, these techniques can selectively power down unused components or adjust performance levels of active components, resulting in significant power savings while maintaining required performance levels.

- Hardware-software co-design for RISC-V power efficiency: Hardware-software co-design approaches for RISC-V systems create tightly integrated power management solutions. These approaches include specialized instruction extensions for power control, compiler optimizations that generate power-efficient code, and runtime systems that communicate power requirements to hardware. The co-design methodology enables more effective power budgeting by allowing software to make informed decisions about hardware power states and providing hardware with contextual information about application needs.

- Multi-core RISC-V power distribution and management: Power distribution and management techniques for multi-core RISC-V systems address the challenges of allocating power budgets across multiple processing elements. These techniques include dynamic power sharing mechanisms that redistribute power allowances based on core activity, hierarchical power management structures that optimize at both local and global levels, and specialized interconnects for power control signaling. The approaches enable efficient utilization of available power while maintaining thermal constraints and meeting performance requirements across all cores.

02 Power management units for RISC-V systems

Dedicated power management units (PMUs) for RISC-V systems provide comprehensive power budgeting capabilities through specialized hardware blocks that monitor and control power consumption across different processor domains. These units implement fine-grained power gating, clock gating, and voltage scaling techniques to optimize energy efficiency while supporting various operational modes from high-performance to ultra-low power states.Expand Specific Solutions03 Adaptive power budgeting algorithms for RISC-V

Adaptive algorithms specifically designed for RISC-V architectures enable dynamic power budgeting based on application requirements and system conditions. These algorithms utilize machine learning techniques to predict workload patterns and proactively adjust power allocation, creating optimal power profiles for different execution scenarios while maintaining thermal constraints and extending battery life in portable devices.Expand Specific Solutions04 Hardware-software co-design for RISC-V power optimization

Hardware-software co-design approaches for RISC-V systems integrate power-aware instruction sets with specialized compiler optimizations and runtime systems. These solutions enable fine-grained control over processor power states through dedicated instructions and registers, while software layers provide intelligent scheduling and resource allocation to maximize energy efficiency across diverse workloads.Expand Specific Solutions05 Multi-core RISC-V power distribution frameworks

Power distribution frameworks for multi-core RISC-V systems enable efficient allocation of power budgets across multiple processing elements. These frameworks implement hierarchical power management with domain-specific controllers that coordinate power states between cores, allowing for asymmetric operation where some cores can run at high performance while others operate in low-power modes, optimizing overall system efficiency.Expand Specific Solutions

Key RISC-V IP Providers and IoT Chipset Manufacturers

RISC-V for wearables and IoT is currently in an early growth phase, with the market expanding rapidly as power efficiency becomes critical for battery-operated devices. The global market is projected to grow significantly as RISC-V offers compelling advantages in power-constrained applications. In terms of technical maturity, Dynamic Voltage and Frequency Scaling (DVFS) implementations for RISC-V are advancing, with major players like Samsung, Huawei, Qualcomm, and Intel leading commercial development. Academic institutions including Zhejiang University and Shanghai Jiao Tong University are contributing significant research. Companies like Nordic Semiconductor and Renesas are focusing on specialized low-power RISC-V solutions for wearables, while established semiconductor firms like NEC and Fujitsu are integrating RISC-V into their broader IoT strategies.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has developed a comprehensive RISC-V solution for wearables and IoT devices centered around their Exynos W series processors. Their approach to power management integrates hardware-based DVFS with Samsung's proprietary Adaptive Power Management (APM) technology. The implementation features a multi-island design with separate voltage domains for core, memory, and peripheral components, each capable of independent power state transitions. Samsung's solution incorporates an ultra-low-power always-on domain that handles sensor data processing while maintaining minimal power draw. Their DVFS implementation includes support for up to 12 operating performance points (OPPs) that are dynamically selected based on workload characteristics and thermal conditions. Samsung has also developed specialized power-aware compilers and runtime systems that optimize code execution patterns to maximize time spent in low-power states. Their benchmarks show up to 60% power reduction in typical wearable use cases compared to conventional ARM-based solutions with similar performance profiles.

Strengths: Samsung's vertical integration allows for highly optimized hardware-software co-design, resulting in exceptional power efficiency. Their manufacturing expertise enables advanced process technologies that further reduce power consumption. Weaknesses: Their solutions may be more tightly coupled to Samsung's ecosystem, potentially limiting flexibility for third-party developers and integration with other platforms.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei has developed a sophisticated RISC-V implementation for wearables and IoT through their HiSilicon division, focusing on ultra-low power consumption. Their approach centers on a heterogeneous computing architecture that combines RISC-V cores with specialized accelerators, all managed by an intelligent power controller. Huawei's DVFS implementation features a predictive algorithm that analyzes usage patterns to anticipate processing needs and proactively adjust power states. Their solution incorporates a multi-level power management hierarchy with global system coordination and local core-specific optimizations. The architecture supports dynamic core parking, where unused cores can be completely powered down during periods of low activity. Huawei has implemented an advanced power gating technique that reduces leakage current by up to 95% in idle states. Their system includes a dedicated microcontroller that handles power state transitions, minimizing the energy overhead of DVFS operations themselves. Benchmarks indicate their solution achieves up to 40% longer battery life in wearable applications compared to conventional implementations.

Strengths: Huawei's solution offers exceptional power efficiency through their sophisticated predictive DVFS algorithms and heterogeneous computing approach. Their extensive experience in mobile devices provides valuable insights for wearable applications. Weaknesses: Geopolitical considerations may limit adoption of their technology in certain markets, and their ecosystem may have more limited third-party support compared to some competitors.

Core Power Optimization Techniques and Patents for RISC-V

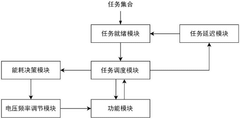

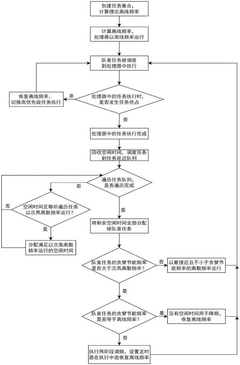

A low-power real-time operating system adapted to RISC-V discrete frequency hardware

PatentPendingCN120448058A

Innovation

- A low-power real-time operating system adapted to RISC-V discrete frequency hardware is designed, including energy consumption decision module, task scheduling module, task ready module, task delay module and voltage frequency regulation module. By calculating the optimal frequency and dynamic voltage regulation, task execution and resource allocation are optimized.

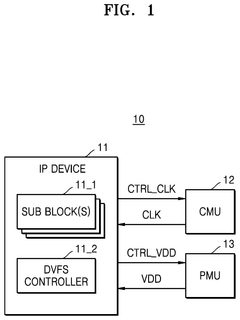

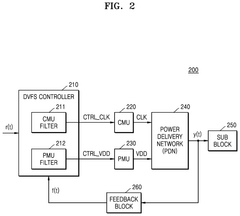

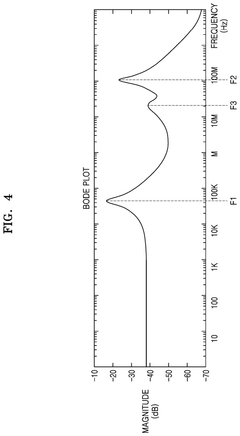

Dynamic voltage and frequency scaling (DVFS) controller, integrated circuit including the DVFS controller, and method of operating the DVFS controller

PatentPendingUS20240427405A1

Innovation

- A Dynamic Voltage and Frequency Scaling (DVFS) controller is implemented, which calculates a resonance frequency from the dynamic characteristics of the power system, including a power management unit (PMU) and a clock management unit (CMU), to optimize performance and maintain stable low-power operation by adjusting the operating voltage and frequency based on feedback signals.

Battery Technology Integration with RISC-V Power Management

The integration of battery technology with RISC-V power management systems represents a critical frontier for wearable and IoT device development. Modern battery technologies, including lithium-ion, lithium polymer, and emerging solid-state batteries, must be carefully optimized to work harmoniously with RISC-V processors' power management capabilities.

RISC-V architectures offer significant advantages for battery-powered devices through their inherent flexibility and customization options. The open ISA allows for precise tailoring of power domains and management strategies that can be specifically designed around battery discharge characteristics. This synergy enables more efficient power utilization across various operational states.

Dynamic Voltage and Frequency Scaling (DVFS) implementations in RISC-V systems can be directly tied to battery state-of-charge indicators, creating adaptive power profiles that extend operational runtime. Advanced battery management systems (BMS) can communicate with RISC-V power controllers via standardized interfaces such as I²C or SPI, enabling real-time adjustments based on battery health, temperature, and remaining capacity.

The integration challenge lies in developing unified firmware that can interpret battery telemetry data and translate it into appropriate RISC-V power state transitions. Several emerging solutions incorporate machine learning algorithms that predict optimal power states based on historical battery performance patterns, further enhancing efficiency.

Battery charging circuits must also be considered within this ecosystem, as they represent significant power management opportunities. RISC-V processors can dynamically adjust charging parameters based on environmental conditions and usage patterns, potentially extending battery lifespan by 15-30% compared to static charging profiles.

For ultra-low-power wearable applications, energy harvesting technologies (solar, kinetic, thermal) are increasingly being paired with RISC-V systems. These hybrid power solutions require sophisticated power management that can seamlessly transition between harvested energy and battery power, a capability well-suited to RISC-V's flexible power domain architecture.

The thermal characteristics of batteries must also be factored into RISC-V power management strategies, as battery efficiency decreases significantly at temperature extremes. Intelligent thermal management coordinated between the battery system and processor can maintain optimal operating conditions, particularly important for wearable devices in direct contact with users.

RISC-V architectures offer significant advantages for battery-powered devices through their inherent flexibility and customization options. The open ISA allows for precise tailoring of power domains and management strategies that can be specifically designed around battery discharge characteristics. This synergy enables more efficient power utilization across various operational states.

Dynamic Voltage and Frequency Scaling (DVFS) implementations in RISC-V systems can be directly tied to battery state-of-charge indicators, creating adaptive power profiles that extend operational runtime. Advanced battery management systems (BMS) can communicate with RISC-V power controllers via standardized interfaces such as I²C or SPI, enabling real-time adjustments based on battery health, temperature, and remaining capacity.

The integration challenge lies in developing unified firmware that can interpret battery telemetry data and translate it into appropriate RISC-V power state transitions. Several emerging solutions incorporate machine learning algorithms that predict optimal power states based on historical battery performance patterns, further enhancing efficiency.

Battery charging circuits must also be considered within this ecosystem, as they represent significant power management opportunities. RISC-V processors can dynamically adjust charging parameters based on environmental conditions and usage patterns, potentially extending battery lifespan by 15-30% compared to static charging profiles.

For ultra-low-power wearable applications, energy harvesting technologies (solar, kinetic, thermal) are increasingly being paired with RISC-V systems. These hybrid power solutions require sophisticated power management that can seamlessly transition between harvested energy and battery power, a capability well-suited to RISC-V's flexible power domain architecture.

The thermal characteristics of batteries must also be factored into RISC-V power management strategies, as battery efficiency decreases significantly at temperature extremes. Intelligent thermal management coordinated between the battery system and processor can maintain optimal operating conditions, particularly important for wearable devices in direct contact with users.

Security Implications of Power Management in IoT Applications

Power management techniques in IoT and wearable devices, particularly those based on RISC-V architecture, introduce significant security vulnerabilities that must be addressed. Dynamic Voltage and Frequency Scaling (DVFS), while essential for power optimization, creates side channels that can be exploited by malicious actors. These side channels manifest through power consumption patterns, electromagnetic emissions, and timing variations that leak sensitive information about the device's operations and data.

The implementation of DVFS in RISC-V-based IoT devices presents unique security challenges due to the architecture's open nature. When voltage and frequency adjustments occur, the resulting power signatures can be analyzed through differential power analysis (DPA) attacks, potentially revealing cryptographic keys and other sensitive information. Research has shown that transitions between power states are particularly vulnerable moments where information leakage is heightened.

Power management security vulnerabilities extend beyond direct attacks on the device. In IoT ecosystems, compromised power management can lead to cascading security failures across connected networks. Attackers can exploit these vulnerabilities to execute denial-of-service attacks by manipulating power states, forcing devices into high-consumption modes that drain batteries prematurely, or low-power states that reduce security monitoring capabilities.

The security implications become more complex when considering the constrained resources of wearable and IoT devices. Traditional security measures often consume significant power, creating a fundamental tension between security and energy efficiency. This tension is particularly evident in RISC-V implementations where custom extensions for power management must balance security considerations with power optimization goals.

Emerging research indicates that security-aware power management techniques can mitigate these risks. These include randomized DVFS scheduling to prevent predictable power signatures, power domain isolation to contain security breaches, and hardware-level anomaly detection that monitors for suspicious power consumption patterns. Some RISC-V implementations now incorporate secure power controllers that validate power state transitions against security policies before execution.

The industry is moving toward integrated security-power frameworks that treat power management as a critical security domain rather than merely an optimization technique. These frameworks implement principle of least privilege in power domain access, require authentication for power state transitions, and maintain secure logs of power management activities for forensic analysis. As RISC-V continues to gain adoption in the IoT space, these security considerations will become increasingly important in standard power management extensions and implementations.

The implementation of DVFS in RISC-V-based IoT devices presents unique security challenges due to the architecture's open nature. When voltage and frequency adjustments occur, the resulting power signatures can be analyzed through differential power analysis (DPA) attacks, potentially revealing cryptographic keys and other sensitive information. Research has shown that transitions between power states are particularly vulnerable moments where information leakage is heightened.

Power management security vulnerabilities extend beyond direct attacks on the device. In IoT ecosystems, compromised power management can lead to cascading security failures across connected networks. Attackers can exploit these vulnerabilities to execute denial-of-service attacks by manipulating power states, forcing devices into high-consumption modes that drain batteries prematurely, or low-power states that reduce security monitoring capabilities.

The security implications become more complex when considering the constrained resources of wearable and IoT devices. Traditional security measures often consume significant power, creating a fundamental tension between security and energy efficiency. This tension is particularly evident in RISC-V implementations where custom extensions for power management must balance security considerations with power optimization goals.

Emerging research indicates that security-aware power management techniques can mitigate these risks. These include randomized DVFS scheduling to prevent predictable power signatures, power domain isolation to contain security breaches, and hardware-level anomaly detection that monitors for suspicious power consumption patterns. Some RISC-V implementations now incorporate secure power controllers that validate power state transitions against security policies before execution.

The industry is moving toward integrated security-power frameworks that treat power management as a critical security domain rather than merely an optimization technique. These frameworks implement principle of least privilege in power domain access, require authentication for power state transitions, and maintain secure logs of power management activities for forensic analysis. As RISC-V continues to gain adoption in the IoT space, these security considerations will become increasingly important in standard power management extensions and implementations.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!