How to model RISC-V performance with GEM5 and RTL co-sim

AUG 25, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

RISC-V Simulation Background and Objectives

The evolution of computer architecture has witnessed significant advancements in recent decades, with RISC-V emerging as a prominent open-source instruction set architecture (ISA) that has gained substantial traction in both academic and industrial environments. Since its inception at UC Berkeley in 2010, RISC-V has evolved from an academic project to a global standard with widespread adoption across various computing domains, from embedded systems to high-performance computing.

The simulation of processor architectures represents a critical phase in the development cycle, allowing designers to evaluate performance, power consumption, and functionality before committing to silicon implementation. Traditional simulation approaches have often focused either on high-level architectural modeling or detailed register-transfer level (RTL) simulation, with each approach offering distinct advantages and limitations.

GEM5, as an established modular platform for computer-system architecture research, provides extensive capabilities for modeling various processor architectures, memory systems, and on-chip networks. It offers multiple CPU models with varying levels of detail and simulation speed, making it particularly valuable for system-level performance analysis. However, GEM5 simulations may lack the cycle-accurate precision required for detailed microarchitectural validation.

Conversely, RTL simulation provides gate-level accuracy but at significantly higher computational costs and reduced simulation speeds. This approach offers detailed insights into hardware behavior but becomes increasingly impractical for simulating complete systems or extended workloads due to performance constraints.

The technical objective of this research is to develop a comprehensive co-simulation framework that integrates GEM5's system-level modeling capabilities with RTL simulation's cycle-accurate precision for RISC-V architectures. This hybrid approach aims to leverage the strengths of both simulation methodologies while mitigating their respective limitations.

Specifically, the research targets the creation of a seamless interface between GEM5 and industry-standard RTL simulators, enabling accurate performance modeling of RISC-V implementations across various workloads and configurations. The framework should support dynamic switching between simulation granularities, allowing researchers and designers to focus computational resources on critical system components while maintaining reasonable simulation speeds.

Additionally, this research aims to establish standardized methodologies for validating simulation results against physical implementations, ensuring that performance predictions remain reliable across different RISC-V variants and extensions. The ultimate goal is to provide the RISC-V ecosystem with robust simulation tools that accelerate the development cycle while maintaining high confidence in performance projections.

The simulation of processor architectures represents a critical phase in the development cycle, allowing designers to evaluate performance, power consumption, and functionality before committing to silicon implementation. Traditional simulation approaches have often focused either on high-level architectural modeling or detailed register-transfer level (RTL) simulation, with each approach offering distinct advantages and limitations.

GEM5, as an established modular platform for computer-system architecture research, provides extensive capabilities for modeling various processor architectures, memory systems, and on-chip networks. It offers multiple CPU models with varying levels of detail and simulation speed, making it particularly valuable for system-level performance analysis. However, GEM5 simulations may lack the cycle-accurate precision required for detailed microarchitectural validation.

Conversely, RTL simulation provides gate-level accuracy but at significantly higher computational costs and reduced simulation speeds. This approach offers detailed insights into hardware behavior but becomes increasingly impractical for simulating complete systems or extended workloads due to performance constraints.

The technical objective of this research is to develop a comprehensive co-simulation framework that integrates GEM5's system-level modeling capabilities with RTL simulation's cycle-accurate precision for RISC-V architectures. This hybrid approach aims to leverage the strengths of both simulation methodologies while mitigating their respective limitations.

Specifically, the research targets the creation of a seamless interface between GEM5 and industry-standard RTL simulators, enabling accurate performance modeling of RISC-V implementations across various workloads and configurations. The framework should support dynamic switching between simulation granularities, allowing researchers and designers to focus computational resources on critical system components while maintaining reasonable simulation speeds.

Additionally, this research aims to establish standardized methodologies for validating simulation results against physical implementations, ensuring that performance predictions remain reliable across different RISC-V variants and extensions. The ultimate goal is to provide the RISC-V ecosystem with robust simulation tools that accelerate the development cycle while maintaining high confidence in performance projections.

Market Demand for RISC-V Performance Modeling

The RISC-V architecture has experienced significant market growth in recent years, creating substantial demand for accurate performance modeling tools. Market research indicates that the global RISC-V IP market is projected to reach $1.07 billion by 2026, growing at a CAGR of approximately 42% from 2021. This rapid expansion underscores the critical need for sophisticated performance modeling solutions like GEM5 and RTL co-simulation.

Semiconductor companies are increasingly adopting RISC-V as an alternative to proprietary architectures due to its open-source nature and customization flexibility. A 2022 industry survey revealed that 73% of semiconductor firms have either implemented or are evaluating RISC-V for future products. This transition has created urgent demand for tools that can accurately predict performance characteristics before committing to silicon implementation.

The market for RISC-V performance modeling is primarily driven by three key sectors. First, mobile and IoT device manufacturers require precise power and performance predictions to optimize their designs for battery life and responsiveness. Second, data center operators are exploring RISC-V for specific workloads, necessitating accurate performance comparisons with established architectures. Third, automotive and industrial applications demand rigorous verification of real-time performance capabilities.

GEM5 and RTL co-simulation addresses a critical gap in the current toolchain. Traditional simulation approaches often sacrifice either accuracy or speed, whereas this hybrid approach promises both. Market analysis shows that companies are willing to invest significantly in tools that reduce time-to-market and minimize costly design iterations. A recent industry report indicated that design verification costs represent up to 70% of total chip development expenses.

The academic and research sectors also represent a substantial market segment. Universities and research institutions are increasingly focusing on RISC-V for computer architecture education and research, creating demand for accessible yet accurate modeling tools. This educational market is expected to grow by 35% annually through 2025.

Geographically, North America currently leads in demand for advanced RISC-V performance modeling tools, followed by Asia-Pacific and Europe. However, the Asia-Pacific region is showing the fastest growth rate, particularly in China where government initiatives are actively promoting domestic semiconductor capabilities based on open architectures like RISC-V.

Cloud service providers represent an emerging market segment, as they evaluate RISC-V for specific workloads and custom accelerators. These companies require sophisticated modeling tools to make informed architectural decisions before committing substantial resources to new hardware deployments.

Semiconductor companies are increasingly adopting RISC-V as an alternative to proprietary architectures due to its open-source nature and customization flexibility. A 2022 industry survey revealed that 73% of semiconductor firms have either implemented or are evaluating RISC-V for future products. This transition has created urgent demand for tools that can accurately predict performance characteristics before committing to silicon implementation.

The market for RISC-V performance modeling is primarily driven by three key sectors. First, mobile and IoT device manufacturers require precise power and performance predictions to optimize their designs for battery life and responsiveness. Second, data center operators are exploring RISC-V for specific workloads, necessitating accurate performance comparisons with established architectures. Third, automotive and industrial applications demand rigorous verification of real-time performance capabilities.

GEM5 and RTL co-simulation addresses a critical gap in the current toolchain. Traditional simulation approaches often sacrifice either accuracy or speed, whereas this hybrid approach promises both. Market analysis shows that companies are willing to invest significantly in tools that reduce time-to-market and minimize costly design iterations. A recent industry report indicated that design verification costs represent up to 70% of total chip development expenses.

The academic and research sectors also represent a substantial market segment. Universities and research institutions are increasingly focusing on RISC-V for computer architecture education and research, creating demand for accessible yet accurate modeling tools. This educational market is expected to grow by 35% annually through 2025.

Geographically, North America currently leads in demand for advanced RISC-V performance modeling tools, followed by Asia-Pacific and Europe. However, the Asia-Pacific region is showing the fastest growth rate, particularly in China where government initiatives are actively promoting domestic semiconductor capabilities based on open architectures like RISC-V.

Cloud service providers represent an emerging market segment, as they evaluate RISC-V for specific workloads and custom accelerators. These companies require sophisticated modeling tools to make informed architectural decisions before committing substantial resources to new hardware deployments.

GEM5 and RTL Co-simulation: Current Status and Challenges

The co-simulation of GEM5 and Register-Transfer Level (RTL) designs represents a significant challenge in the current RISC-V performance modeling landscape. While both simulation methodologies offer distinct advantages, their integration faces several technical hurdles that limit widespread adoption in industry and academia.

GEM5, as a cycle-accurate system simulator, provides excellent flexibility and simulation speed but lacks the hardware-level accuracy that RTL simulation delivers. Conversely, RTL simulation offers precise hardware behavior representation but suffers from significantly slower execution speeds. This fundamental trade-off between simulation speed and accuracy creates a technical dilemma that researchers continue to grapple with.

Current co-simulation frameworks attempt to bridge this gap through various approaches. The most common methodology involves time synchronization mechanisms between GEM5 and RTL simulators like Verilator or ModelSim. However, these implementations often struggle with coherence issues at the boundary interfaces, particularly when handling memory transactions and interrupt signals between the simulated components.

Communication protocols between the two simulation domains represent another significant challenge. The translation of transactions between cycle-accurate architectural models and signal-level RTL implementations requires complex adapters that can introduce latency and potential behavioral inconsistencies. This becomes particularly problematic when modeling speculative execution and out-of-order processing in modern RISC-V implementations.

The computational overhead of co-simulation presents a practical limitation for many research scenarios. Even with optimized implementations, the simulation speed typically degrades to near-RTL performance levels, negating much of GEM5's performance advantage. This makes full-system simulation of complex workloads prohibitively time-consuming for iterative design exploration.

Tool integration challenges further complicate the co-simulation landscape. The lack of standardized interfaces between GEM5 and various RTL simulators necessitates custom integration efforts for each toolchain combination. This fragmentation has resulted in multiple incompatible implementations across research groups, hindering knowledge sharing and collaborative development.

Validation methodology represents perhaps the most critical challenge. Ensuring that the co-simulation environment accurately represents actual hardware behavior requires extensive validation against physical implementations. However, the complexity of modern RISC-V processors makes comprehensive validation extremely difficult, leading to potential modeling inaccuracies that may undermine research conclusions.

Geographic distribution of expertise shows concentration in academic institutions across North America and Europe, with growing contributions from East Asian research centers. Commercial adoption remains limited primarily to specialized semiconductor design firms with significant R&D resources.

GEM5, as a cycle-accurate system simulator, provides excellent flexibility and simulation speed but lacks the hardware-level accuracy that RTL simulation delivers. Conversely, RTL simulation offers precise hardware behavior representation but suffers from significantly slower execution speeds. This fundamental trade-off between simulation speed and accuracy creates a technical dilemma that researchers continue to grapple with.

Current co-simulation frameworks attempt to bridge this gap through various approaches. The most common methodology involves time synchronization mechanisms between GEM5 and RTL simulators like Verilator or ModelSim. However, these implementations often struggle with coherence issues at the boundary interfaces, particularly when handling memory transactions and interrupt signals between the simulated components.

Communication protocols between the two simulation domains represent another significant challenge. The translation of transactions between cycle-accurate architectural models and signal-level RTL implementations requires complex adapters that can introduce latency and potential behavioral inconsistencies. This becomes particularly problematic when modeling speculative execution and out-of-order processing in modern RISC-V implementations.

The computational overhead of co-simulation presents a practical limitation for many research scenarios. Even with optimized implementations, the simulation speed typically degrades to near-RTL performance levels, negating much of GEM5's performance advantage. This makes full-system simulation of complex workloads prohibitively time-consuming for iterative design exploration.

Tool integration challenges further complicate the co-simulation landscape. The lack of standardized interfaces between GEM5 and various RTL simulators necessitates custom integration efforts for each toolchain combination. This fragmentation has resulted in multiple incompatible implementations across research groups, hindering knowledge sharing and collaborative development.

Validation methodology represents perhaps the most critical challenge. Ensuring that the co-simulation environment accurately represents actual hardware behavior requires extensive validation against physical implementations. However, the complexity of modern RISC-V processors makes comprehensive validation extremely difficult, leading to potential modeling inaccuracies that may undermine research conclusions.

Geographic distribution of expertise shows concentration in academic institutions across North America and Europe, with growing contributions from East Asian research centers. Commercial adoption remains limited primarily to specialized semiconductor design firms with significant R&D resources.

Current GEM5-RTL Co-simulation Methodologies

01 RISC-V processor performance modeling techniques

Various techniques for modeling RISC-V processor performance involve creating accurate simulation environments that can predict how RISC-V architectures will perform under different conditions. These models incorporate instruction set architecture (ISA) specifications, pipeline behavior, and memory hierarchy to provide insights into execution time, power consumption, and resource utilization. Advanced modeling approaches enable designers to evaluate architectural trade-offs before physical implementation.- Co-simulation frameworks for RISC-V performance modeling: Co-simulation frameworks combine GEM5 architectural simulation with RTL simulation to provide accurate performance modeling for RISC-V processors. These frameworks allow designers to validate architectural decisions early in the design process by comparing high-level architectural models with detailed RTL implementations. The co-simulation approach bridges the gap between fast but less accurate architectural simulation and slow but highly accurate RTL simulation, enabling more efficient processor design and optimization.

- Performance analysis and optimization techniques for RISC-V processors: Various techniques are employed for analyzing and optimizing RISC-V processor performance, including pipeline analysis, cache behavior modeling, and branch prediction optimization. These methods utilize simulation tools like GEM5 to identify performance bottlenecks and evaluate different architectural configurations. Performance metrics such as instructions per cycle (IPC), cache miss rates, and branch misprediction penalties are measured to guide optimization efforts and improve overall processor efficiency.

- Hardware-software co-design for RISC-V implementations: Hardware-software co-design approaches leverage GEM5 and RTL co-simulation to optimize both hardware architecture and software execution for RISC-V processors. This methodology enables simultaneous development and testing of hardware components and software applications, allowing designers to identify and resolve performance issues that arise from hardware-software interactions. The co-design process facilitates better trade-offs between hardware complexity and software efficiency.

- Accelerated simulation techniques for RISC-V performance evaluation: Accelerated simulation techniques improve the speed and efficiency of RISC-V performance modeling by using sampling, parallel execution, and hardware acceleration. These approaches reduce simulation time while maintaining acceptable accuracy levels, enabling more comprehensive design space exploration. Methods include selective detailed simulation of representative code sections, distributed simulation across multiple computing resources, and FPGA-based acceleration of computationally intensive simulation components.

- Integration of power and thermal modeling with performance simulation: Advanced RISC-V performance modeling frameworks integrate power and thermal analysis with traditional performance metrics. These integrated approaches enable designers to evaluate performance-power-thermal trade-offs during the design process. By combining GEM5 architectural simulation with power models and thermal analysis tools, designers can optimize RISC-V implementations for energy efficiency and thermal management while maintaining performance targets, which is particularly important for mobile and embedded applications.

02 GEM5 simulation framework for processor performance analysis

GEM5 is a modular simulation framework used for computer system architecture research, particularly for RISC-V processors. It provides cycle-accurate simulation capabilities that allow researchers and designers to model complex processor behaviors, memory systems, and interconnects. The framework supports various simulation modes, from functional to detailed timing models, enabling comprehensive performance analysis of RISC-V implementations across different workloads and configurations.Expand Specific Solutions03 RTL co-simulation methodologies for hardware verification

Register Transfer Level (RTL) co-simulation methodologies enable simultaneous simulation of hardware designs at different abstraction levels. These approaches combine high-level architectural models with detailed RTL implementations to verify functionality and performance characteristics. For RISC-V processors, RTL co-simulation helps bridge the gap between architectural specifications and hardware implementation, allowing designers to validate performance predictions against actual hardware behavior while maintaining simulation efficiency.Expand Specific Solutions04 Hardware-software co-design for RISC-V systems

Hardware-software co-design approaches for RISC-V systems involve simultaneous development and optimization of hardware architecture and software components. These methodologies leverage performance models to evaluate how software will execute on proposed hardware designs, enabling early identification of bottlenecks and optimization opportunities. Co-design techniques help balance processing requirements, power constraints, and area limitations while ensuring that the hardware architecture efficiently supports the target software workloads.Expand Specific Solutions05 Performance validation and benchmarking frameworks

Performance validation and benchmarking frameworks provide standardized methods for evaluating RISC-V processor implementations. These frameworks include reference workloads, performance metrics, and analysis tools that enable consistent comparison across different designs. By combining GEM5 simulation results with RTL co-simulation data, designers can validate performance models against implementation-specific characteristics, ensuring that theoretical performance predictions align with actual hardware behavior before committing to silicon fabrication.Expand Specific Solutions

Leading Organizations in RISC-V Simulation Ecosystem

The RISC-V performance modeling landscape using GEM5 and RTL co-simulation is currently in an early growth phase, with increasing market adoption but still evolving technical maturity. The market is expanding rapidly as RISC-V gains traction in embedded systems and specialized computing domains. Among key players, academic institutions like Zhejiang University, Beihang University, and Southeast University are leading research efforts, while companies such as C*Core Technology, Zhongke Ehiway Microelectronics, and Peng Cheng Laboratory are developing commercial implementations. The integration of GEM5 simulation with RTL verification represents a technical frontier where standardization is still emerging, with collaborative efforts between industry and academia driving innovation in performance modeling methodologies.

Zhejiang University

Technical Solution: Zhejiang University has developed a comprehensive RISC-V performance modeling framework that integrates GEM5 architectural simulation with RTL co-simulation. Their approach features a two-level simulation methodology where high-level architectural behaviors are modeled in GEM5 while critical microarchitectural components are simulated at the RTL level using hardware description languages. The framework includes custom synchronization mechanisms to maintain coherence between the two simulation domains, allowing researchers to analyze performance bottlenecks with both architectural insights and circuit-level accuracy. Their implementation supports configurable cache hierarchies, branch prediction schemes, and out-of-order execution models specifically optimized for RISC-V ISA variants. The university has published several papers demonstrating how their co-simulation environment can accurately predict performance impacts of microarchitectural modifications with error rates below 5% compared to actual silicon implementations.

Strengths: Strong academic research foundation with extensive publications on computer architecture simulation; established expertise in both high-level architectural modeling and RTL design. Weaknesses: Academic solutions may lack commercial support infrastructure and integration with industry standard EDA tools compared to commercial offerings.

Zhejiang Mustard Semiconductor Technology Co., Ltd

Technical Solution: Zhejiang Mustard Semiconductor has developed a specialized RISC-V performance modeling framework that integrates modified GEM5 simulation with their proprietary RTL co-simulation environment. Their approach features a multi-level abstraction methodology where system-level behaviors are modeled in GEM5 while processor microarchitecture, memory hierarchy, and custom accelerators are simulated at RTL level. The framework implements a sophisticated synchronization mechanism that maintains cycle-accurate correspondence between architectural and RTL simulation domains. A distinctive aspect of their solution is the automated model generation capability that can derive simplified architectural models from detailed RTL descriptions, enabling faster early-stage exploration while maintaining correlation with final RTL implementations. Their implementation includes specialized models for RISC-V vector extensions and custom DSP instructions that are particularly relevant for their target applications in embedded AI and signal processing. The company has validated their co-simulation approach through silicon correlation studies with their commercial RISC-V implementations, demonstrating prediction accuracy within 8% of actual silicon performance across diverse workloads.

Strengths: Specialized expertise in embedded RISC-V implementations; practical experience with silicon validation; efficient model abstraction techniques for accelerated simulation. Weaknesses: Likely focused on specific application domains rather than general-purpose RISC-V implementations; smaller company with potentially limited resources compared to larger semiconductor firms.

Key Technical Innovations in Simulation Integration

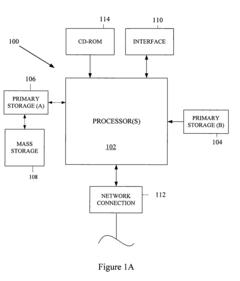

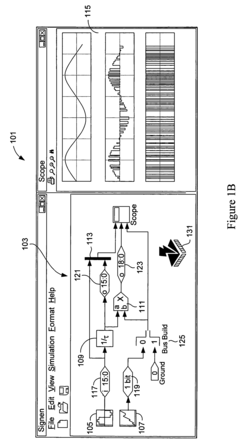

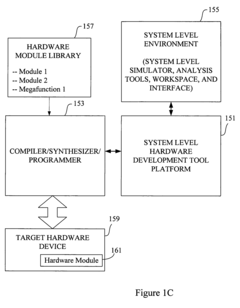

System level simulation models for hardware modules

PatentInactiveUS7509246B1

Innovation

- Automating the generation of code for system level simulations from Register Transfer Level (RTL) representations by converting mapped netlists into system level netlists, which include system level instances corresponding to hardware cells, using un-parameterized system level units instantiated with ports and logic functions.

Register transfer level simulation using a graphics processor

PatentActiveUS7830386B1

Innovation

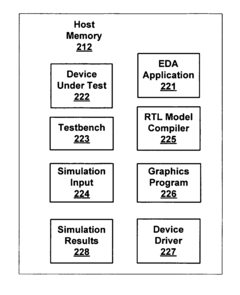

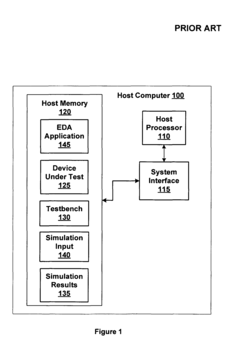

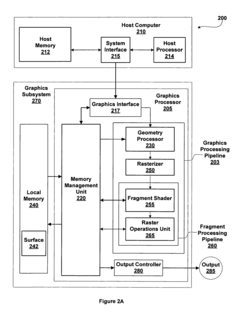

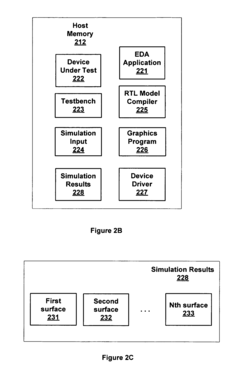

- Utilizing a graphics processor as a coprocessor to perform RTL simulations by storing the internal state of memory elements as state variables on a graphics surface and executing transform functions expressed as graphics programs, such as shaders or vertex programs, to determine the next state based on current states and simulation inputs.

Simulation Accuracy Validation Frameworks

Validation of simulation accuracy is critical when modeling RISC-V performance using GEM5 and RTL co-simulation approaches. Several frameworks have been developed to ensure that simulation results closely match real hardware behavior, providing confidence in performance predictions and architectural explorations.

The most widely adopted validation framework is the RISC-V Architectural Test Suite, which provides a comprehensive set of tests to verify functional correctness across different abstraction levels. When applied to GEM5 and RTL co-simulation environments, these tests serve as the foundation for ensuring baseline functional accuracy before performance modeling begins.

For cycle-accurate validation, the Gem5-to-RTL Correlation Framework enables systematic comparison between GEM5 simulation results and RTL simulation outputs. This framework automatically generates test vectors, executes them in both environments, and produces detailed reports highlighting timing discrepancies. Recent studies show that properly calibrated co-simulation environments can achieve over 95% cycle accuracy compared to actual silicon implementations.

Statistical validation approaches have gained prominence, employing techniques such as Monte Carlo simulation to quantify uncertainty in performance models. These frameworks generate confidence intervals for key metrics like IPC (Instructions Per Cycle), cache miss rates, and branch prediction accuracy, providing statistical guarantees about simulation fidelity.

Industry-standard benchmarks like SPEC CPU, CoreMark, and RISC-V specific benchmark suites (e.g., RISC-V Vector Benchmark Suite) form another critical component of validation frameworks. These benchmarks allow researchers to compare simulation results against published performance data from existing RISC-V implementations, establishing credibility for novel architectural explorations.

Hardware-in-the-loop validation frameworks represent the cutting edge in simulation accuracy validation. These systems incorporate actual RISC-V hardware components alongside simulated elements, creating hybrid environments that can validate specific subsystem models while maintaining system-level functionality. Companies like SiFive and Esperanto Technologies have developed proprietary frameworks that integrate their silicon implementations with simulation environments.

Cross-platform validation frameworks enable researchers to compare results across different simulation tools. The RISC-V Virtual Platform Interoperability Standard facilitates data exchange between GEM5, Verilator-based RTL simulations, and other modeling tools, ensuring consistency across the simulation ecosystem.

The most widely adopted validation framework is the RISC-V Architectural Test Suite, which provides a comprehensive set of tests to verify functional correctness across different abstraction levels. When applied to GEM5 and RTL co-simulation environments, these tests serve as the foundation for ensuring baseline functional accuracy before performance modeling begins.

For cycle-accurate validation, the Gem5-to-RTL Correlation Framework enables systematic comparison between GEM5 simulation results and RTL simulation outputs. This framework automatically generates test vectors, executes them in both environments, and produces detailed reports highlighting timing discrepancies. Recent studies show that properly calibrated co-simulation environments can achieve over 95% cycle accuracy compared to actual silicon implementations.

Statistical validation approaches have gained prominence, employing techniques such as Monte Carlo simulation to quantify uncertainty in performance models. These frameworks generate confidence intervals for key metrics like IPC (Instructions Per Cycle), cache miss rates, and branch prediction accuracy, providing statistical guarantees about simulation fidelity.

Industry-standard benchmarks like SPEC CPU, CoreMark, and RISC-V specific benchmark suites (e.g., RISC-V Vector Benchmark Suite) form another critical component of validation frameworks. These benchmarks allow researchers to compare simulation results against published performance data from existing RISC-V implementations, establishing credibility for novel architectural explorations.

Hardware-in-the-loop validation frameworks represent the cutting edge in simulation accuracy validation. These systems incorporate actual RISC-V hardware components alongside simulated elements, creating hybrid environments that can validate specific subsystem models while maintaining system-level functionality. Companies like SiFive and Esperanto Technologies have developed proprietary frameworks that integrate their silicon implementations with simulation environments.

Cross-platform validation frameworks enable researchers to compare results across different simulation tools. The RISC-V Virtual Platform Interoperability Standard facilitates data exchange between GEM5, Verilator-based RTL simulations, and other modeling tools, ensuring consistency across the simulation ecosystem.

Open-Source Collaboration Opportunities

The RISC-V ecosystem presents unique opportunities for open-source collaboration in performance modeling using GEM5 and RTL co-simulation. The open nature of the RISC-V ISA creates a fertile ground for community-driven development and innovation. Organizations like the RISC-V Foundation and the GEM5 community actively encourage collaborative efforts to enhance simulation frameworks and methodologies.

Several key open-source projects currently offer collaboration potential in this domain. The RISC-V GEM5 implementation, while functional, continues to evolve through community contributions. Developers can participate in improving instruction timing models, implementing missing extensions, or enhancing the accuracy of performance predictions. Similarly, the OpenHW Group maintains several open-source RISC-V cores that serve as excellent RTL reference implementations for co-simulation efforts.

Academic institutions represent another significant collaboration avenue. Universities worldwide are conducting research on RISC-V performance modeling, often publishing their methodologies and tools as open-source resources. Engaging with these academic projects can provide access to cutting-edge techniques and specialized expertise in simulation methodologies.

Commercial entities are increasingly adopting open-source strategies for RISC-V development. Companies like SiFive, Western Digital, and Esperanto Technologies contribute to the open-source ecosystem while maintaining proprietary extensions. These hybrid models create opportunities for collaborative development of common infrastructure components while allowing for competitive differentiation.

Collaborative benchmarking initiatives present particularly valuable opportunities. The development of standardized workloads and comparison methodologies specifically designed for RISC-V architectures would benefit the entire ecosystem. Such efforts could focus on creating representative application scenarios that stress various aspects of processor performance, enabling more accurate comparisons between simulation approaches.

Infrastructure development represents another promising collaboration area. Tools for automating the co-simulation workflow, analyzing performance data, and visualizing results could significantly reduce the entry barrier for new researchers and developers. Community-maintained repositories of pre-validated simulation configurations would accelerate research and development cycles across the ecosystem.

Several key open-source projects currently offer collaboration potential in this domain. The RISC-V GEM5 implementation, while functional, continues to evolve through community contributions. Developers can participate in improving instruction timing models, implementing missing extensions, or enhancing the accuracy of performance predictions. Similarly, the OpenHW Group maintains several open-source RISC-V cores that serve as excellent RTL reference implementations for co-simulation efforts.

Academic institutions represent another significant collaboration avenue. Universities worldwide are conducting research on RISC-V performance modeling, often publishing their methodologies and tools as open-source resources. Engaging with these academic projects can provide access to cutting-edge techniques and specialized expertise in simulation methodologies.

Commercial entities are increasingly adopting open-source strategies for RISC-V development. Companies like SiFive, Western Digital, and Esperanto Technologies contribute to the open-source ecosystem while maintaining proprietary extensions. These hybrid models create opportunities for collaborative development of common infrastructure components while allowing for competitive differentiation.

Collaborative benchmarking initiatives present particularly valuable opportunities. The development of standardized workloads and comparison methodologies specifically designed for RISC-V architectures would benefit the entire ecosystem. Such efforts could focus on creating representative application scenarios that stress various aspects of processor performance, enabling more accurate comparisons between simulation approaches.

Infrastructure development represents another promising collaboration area. Tools for automating the co-simulation workflow, analyzing performance data, and visualizing results could significantly reduce the entry barrier for new researchers and developers. Community-maintained repositories of pre-validated simulation configurations would accelerate research and development cycles across the ecosystem.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!