PCM Backed NVM For Edge Compute: Packaging And Reliability Issues

AUG 29, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

PCM NVM Technology Evolution and Objectives

Phase Change Memory (PCM) technology has evolved significantly over the past two decades, transitioning from theoretical concept to commercial reality. The fundamental principle of PCM leverages the unique properties of chalcogenide materials, which can rapidly switch between amorphous and crystalline states when subjected to electrical pulses. This binary state change enables data storage capabilities with promising characteristics for non-volatile memory applications.

The evolution of PCM began in the early 2000s with basic research into chalcogenide materials, particularly germanium-antimony-tellurium (GST) compounds. By 2010, first-generation PCM devices demonstrated proof-of-concept functionality but suffered from high power consumption, limited endurance, and reliability concerns. The period between 2010-2015 marked significant improvements in cell architecture, resulting in reduced programming currents and enhanced data retention capabilities.

From 2015 onwards, PCM technology entered a more mature phase with Intel and Micron's introduction of 3D XPoint™ technology, representing the first large-scale commercial deployment of PCM-based memory. This milestone demonstrated PCM's potential to bridge the performance gap between DRAM and NAND flash storage, creating a new tier in the memory hierarchy.

The primary technical objectives for PCM in edge computing applications center on addressing several critical parameters. First, reducing power consumption is essential for battery-powered edge devices, requiring innovations in cell design and programming algorithms. Second, improving write endurance beyond the current 10^6-10^7 cycles remains crucial for applications requiring frequent updates. Third, enhancing data retention at elevated temperatures is particularly important for edge devices operating in harsh environments.

Additionally, scaling challenges must be overcome to increase density while maintaining performance. Current objectives include reducing the cell size below 20nm without compromising reliability, and developing multi-level cell (MLC) capabilities to store multiple bits per cell, thereby increasing storage density.

For edge computing specifically, PCM technology aims to provide a balance of performance characteristics: sub-microsecond read latency, write speeds significantly faster than flash memory, and power efficiency suitable for constrained environments. The ultimate goal is to enable new computing paradigms at the edge, including in-memory computing and neuromorphic applications that can process data locally without constant communication with centralized cloud infrastructure.

As edge AI applications proliferate, PCM development increasingly focuses on optimizing memory characteristics for machine learning workloads, particularly inference operations that benefit from PCM's non-volatile nature and relatively high read speeds compared to traditional storage technologies.

The evolution of PCM began in the early 2000s with basic research into chalcogenide materials, particularly germanium-antimony-tellurium (GST) compounds. By 2010, first-generation PCM devices demonstrated proof-of-concept functionality but suffered from high power consumption, limited endurance, and reliability concerns. The period between 2010-2015 marked significant improvements in cell architecture, resulting in reduced programming currents and enhanced data retention capabilities.

From 2015 onwards, PCM technology entered a more mature phase with Intel and Micron's introduction of 3D XPoint™ technology, representing the first large-scale commercial deployment of PCM-based memory. This milestone demonstrated PCM's potential to bridge the performance gap between DRAM and NAND flash storage, creating a new tier in the memory hierarchy.

The primary technical objectives for PCM in edge computing applications center on addressing several critical parameters. First, reducing power consumption is essential for battery-powered edge devices, requiring innovations in cell design and programming algorithms. Second, improving write endurance beyond the current 10^6-10^7 cycles remains crucial for applications requiring frequent updates. Third, enhancing data retention at elevated temperatures is particularly important for edge devices operating in harsh environments.

Additionally, scaling challenges must be overcome to increase density while maintaining performance. Current objectives include reducing the cell size below 20nm without compromising reliability, and developing multi-level cell (MLC) capabilities to store multiple bits per cell, thereby increasing storage density.

For edge computing specifically, PCM technology aims to provide a balance of performance characteristics: sub-microsecond read latency, write speeds significantly faster than flash memory, and power efficiency suitable for constrained environments. The ultimate goal is to enable new computing paradigms at the edge, including in-memory computing and neuromorphic applications that can process data locally without constant communication with centralized cloud infrastructure.

As edge AI applications proliferate, PCM development increasingly focuses on optimizing memory characteristics for machine learning workloads, particularly inference operations that benefit from PCM's non-volatile nature and relatively high read speeds compared to traditional storage technologies.

Edge Computing Market Demand for PCM-Based NVM

The edge computing market is experiencing unprecedented growth, driven by the increasing need for real-time data processing capabilities closer to data sources. This expansion creates significant demand for advanced non-volatile memory solutions, particularly Phase Change Memory (PCM)-based NVM technologies that can withstand the unique challenges of edge environments.

Market research indicates that the global edge computing market is projected to reach $43.4 billion by 2027, growing at a compound annual growth rate of 37.4% from 2022. Within this ecosystem, memory solutions represent a critical component, with PCM-based NVM positioned to capture substantial market share due to its superior performance characteristics compared to traditional storage technologies.

The primary market drivers for PCM-based NVM in edge computing include the proliferation of IoT devices, which is expected to exceed 75 billion connected devices by 2025. These devices generate massive volumes of data requiring local processing to reduce latency and bandwidth consumption. Additionally, the expansion of 5G networks is enabling more sophisticated edge applications that demand higher memory performance and reliability.

Industry verticals showing the strongest demand for PCM-backed NVM include industrial automation, autonomous vehicles, smart cities, and healthcare monitoring systems. These sectors require memory solutions that can operate reliably in harsh environmental conditions while maintaining data integrity and providing fast access times.

The automotive sector represents a particularly promising market, with advanced driver-assistance systems (ADAS) and autonomous driving technologies requiring ultra-reliable, high-performance memory solutions capable of withstanding extreme temperature variations and mechanical stress. Market analysis suggests that automotive-grade PCM memory could command premium pricing, with margins 30-40% higher than consumer-grade alternatives.

Telecommunications infrastructure providers are also emerging as significant consumers of PCM-based NVM, deploying these technologies in edge data centers and base stations to support low-latency applications. This segment is expected to grow at 42% annually through 2026, outpacing the broader edge computing market.

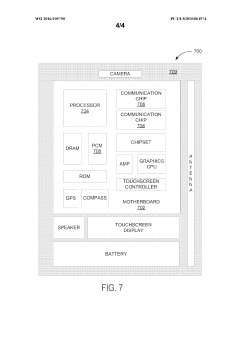

Consumer demand for edge AI applications in smartphones, wearables, and smart home devices is creating another substantial market opportunity. These applications benefit from PCM's combination of DRAM-like speed and non-volatile storage, enabling more efficient AI processing at the edge while conserving battery power.

Despite strong market potential, adoption barriers include cost considerations, with PCM solutions currently commanding a price premium over conventional memory technologies. However, this gap is expected to narrow as manufacturing processes mature and economies of scale are realized. Additionally, concerns about long-term reliability and endurance in challenging edge environments must be addressed to accelerate market penetration.

Market research indicates that the global edge computing market is projected to reach $43.4 billion by 2027, growing at a compound annual growth rate of 37.4% from 2022. Within this ecosystem, memory solutions represent a critical component, with PCM-based NVM positioned to capture substantial market share due to its superior performance characteristics compared to traditional storage technologies.

The primary market drivers for PCM-based NVM in edge computing include the proliferation of IoT devices, which is expected to exceed 75 billion connected devices by 2025. These devices generate massive volumes of data requiring local processing to reduce latency and bandwidth consumption. Additionally, the expansion of 5G networks is enabling more sophisticated edge applications that demand higher memory performance and reliability.

Industry verticals showing the strongest demand for PCM-backed NVM include industrial automation, autonomous vehicles, smart cities, and healthcare monitoring systems. These sectors require memory solutions that can operate reliably in harsh environmental conditions while maintaining data integrity and providing fast access times.

The automotive sector represents a particularly promising market, with advanced driver-assistance systems (ADAS) and autonomous driving technologies requiring ultra-reliable, high-performance memory solutions capable of withstanding extreme temperature variations and mechanical stress. Market analysis suggests that automotive-grade PCM memory could command premium pricing, with margins 30-40% higher than consumer-grade alternatives.

Telecommunications infrastructure providers are also emerging as significant consumers of PCM-based NVM, deploying these technologies in edge data centers and base stations to support low-latency applications. This segment is expected to grow at 42% annually through 2026, outpacing the broader edge computing market.

Consumer demand for edge AI applications in smartphones, wearables, and smart home devices is creating another substantial market opportunity. These applications benefit from PCM's combination of DRAM-like speed and non-volatile storage, enabling more efficient AI processing at the edge while conserving battery power.

Despite strong market potential, adoption barriers include cost considerations, with PCM solutions currently commanding a price premium over conventional memory technologies. However, this gap is expected to narrow as manufacturing processes mature and economies of scale are realized. Additionally, concerns about long-term reliability and endurance in challenging edge environments must be addressed to accelerate market penetration.

PCM Packaging Challenges and Reliability Constraints

Phase Change Memory (PCM) technology faces significant packaging challenges that directly impact its reliability and performance in edge computing applications. The integration of PCM into Non-Volatile Memory (NVM) systems requires addressing thermal management issues due to the high temperatures needed for phase transitions between crystalline and amorphous states. These thermal requirements create mechanical stress at material interfaces, potentially leading to delamination and connection failures over repeated thermal cycles.

The miniaturization demands of edge computing devices further complicate PCM packaging. As form factors shrink, heat dissipation becomes increasingly problematic, creating thermal crosstalk between adjacent memory cells that can cause unintended state changes in neighboring cells. This thermal interference compromises data integrity and reduces the effective storage density achievable in practical implementations.

Material compatibility presents another significant challenge. PCM typically utilizes chalcogenide materials like Ge2Sb2Te5 (GST) that must interface with conventional semiconductor materials and interconnects. The different thermal expansion coefficients between these materials create mechanical stress during operation, particularly problematic during power cycling in intermittently powered edge devices.

Hermetic sealing requirements add complexity to PCM packaging solutions. The chalcogenide materials used in PCM are sensitive to environmental contaminants, particularly oxygen and moisture, which can alter their phase-change properties and accelerate degradation. This necessitates advanced encapsulation techniques that maintain hermeticity while allowing for electrical connections and heat dissipation.

Reliability constraints manifest in several critical areas. Write endurance limitations remain a primary concern, with current PCM technologies typically supporting 10^6 to 10^8 write cycles before failure—significantly lower than DRAM but higher than flash memory. This endurance profile requires careful system-level design to distribute write operations and implement wear-leveling algorithms.

Resistance drift represents another reliability challenge, where the electrical resistance of the amorphous state gradually increases over time, potentially leading to read errors. This phenomenon is temperature-dependent and accelerates in elevated temperature environments typical of edge computing deployments.

Data retention under thermal stress conditions presents particular concerns for edge applications. PCM cells must maintain their programmed state reliably across wide temperature ranges, from sub-zero environments to elevated temperatures exceeding 85°C in industrial applications. The crystallization of the amorphous state can accelerate at higher temperatures, potentially causing data loss in long-term storage scenarios.

The miniaturization demands of edge computing devices further complicate PCM packaging. As form factors shrink, heat dissipation becomes increasingly problematic, creating thermal crosstalk between adjacent memory cells that can cause unintended state changes in neighboring cells. This thermal interference compromises data integrity and reduces the effective storage density achievable in practical implementations.

Material compatibility presents another significant challenge. PCM typically utilizes chalcogenide materials like Ge2Sb2Te5 (GST) that must interface with conventional semiconductor materials and interconnects. The different thermal expansion coefficients between these materials create mechanical stress during operation, particularly problematic during power cycling in intermittently powered edge devices.

Hermetic sealing requirements add complexity to PCM packaging solutions. The chalcogenide materials used in PCM are sensitive to environmental contaminants, particularly oxygen and moisture, which can alter their phase-change properties and accelerate degradation. This necessitates advanced encapsulation techniques that maintain hermeticity while allowing for electrical connections and heat dissipation.

Reliability constraints manifest in several critical areas. Write endurance limitations remain a primary concern, with current PCM technologies typically supporting 10^6 to 10^8 write cycles before failure—significantly lower than DRAM but higher than flash memory. This endurance profile requires careful system-level design to distribute write operations and implement wear-leveling algorithms.

Resistance drift represents another reliability challenge, where the electrical resistance of the amorphous state gradually increases over time, potentially leading to read errors. This phenomenon is temperature-dependent and accelerates in elevated temperature environments typical of edge computing deployments.

Data retention under thermal stress conditions presents particular concerns for edge applications. PCM cells must maintain their programmed state reliably across wide temperature ranges, from sub-zero environments to elevated temperatures exceeding 85°C in industrial applications. The crystallization of the amorphous state can accelerate at higher temperatures, potentially causing data loss in long-term storage scenarios.

Current PCM Packaging Solutions and Approaches

01 PCM cell structure and fabrication techniques

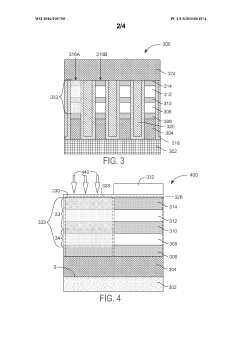

Phase Change Memory (PCM) cell structures are designed to optimize reliability and performance. These structures include various electrode configurations, phase change materials, and isolation techniques to prevent thermal crosstalk. Fabrication techniques focus on creating reliable PCM cells with consistent switching characteristics and long endurance. Advanced manufacturing processes help reduce variability and improve the thermal efficiency of the memory cells, which is crucial for reliable operation in non-volatile memory applications.- PCM device structure and fabrication techniques: Phase Change Memory (PCM) devices are structured with specific materials and fabrication techniques to ensure reliability and performance. These structures typically include chalcogenide materials that change between amorphous and crystalline states. Advanced fabrication methods focus on creating stable interfaces between the phase change material and electrodes, minimizing thermal stress during operation, and ensuring uniform heating during programming operations. These structural optimizations help improve data retention, reduce power consumption, and enhance overall reliability of PCM-based non-volatile memory systems.

- Thermal management in PCM packaging: Thermal management is critical for PCM-backed NVM reliability as phase change operations generate significant heat. Packaging solutions incorporate heat dissipation structures, thermal barriers, and specialized materials to control temperature gradients. Advanced thermal management techniques include optimized heater element designs, thermal isolation structures, and heat-resistant packaging materials. These solutions prevent thermal crosstalk between adjacent memory cells, reduce thermal stress during programming cycles, and extend the operational lifetime of PCM devices by maintaining optimal temperature ranges during write operations.

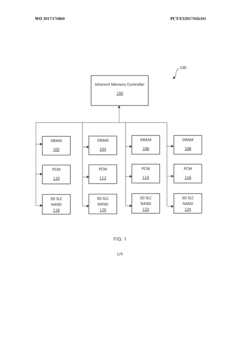

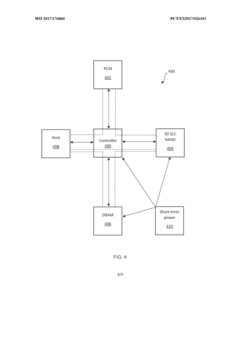

- PCM integration with hybrid memory systems: PCM is increasingly integrated into hybrid memory architectures that combine different non-volatile memory technologies to leverage their complementary strengths. These hybrid systems often pair PCM with DRAM, flash memory, or other emerging memory technologies to create tiered storage solutions. Integration approaches include memory controllers that manage data placement across different memory types, specialized caching algorithms, and hardware-level coherence mechanisms. Such hybrid architectures optimize for both performance and reliability while addressing PCM-specific limitations such as write endurance and latency characteristics.

- Reliability enhancement techniques for PCM: Various techniques are employed to enhance the reliability of PCM-based non-volatile memory systems. These include error correction codes specifically designed for PCM error patterns, wear-leveling algorithms that distribute write operations evenly across memory cells, and adaptive programming schemes that adjust programming parameters based on cell characteristics. Additional reliability features include redundancy mechanisms, self-healing circuits, and drift compensation techniques that account for resistance changes over time. These approaches collectively address common PCM failure modes such as resistance drift, endurance limitations, and data retention issues.

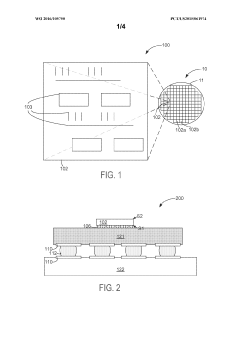

- Advanced packaging solutions for PCM-based memory: Advanced packaging technologies are crucial for PCM-based memory systems to ensure optimal electrical performance, thermal management, and mechanical stability. These include 3D stacking architectures, through-silicon vias (TSVs), and interposer-based designs that enable higher density integration while managing thermal challenges. Specialized packaging approaches incorporate materials with matched thermal expansion coefficients, hermetic sealing techniques to prevent environmental contamination, and stress-relief structures. These packaging innovations help maintain the integrity of phase change materials during assembly processes and throughout the operational lifetime of the memory devices.

02 PCM-backed memory system architecture

Memory system architectures incorporating PCM as backing storage for non-volatile memory systems utilize hybrid approaches that combine PCM with other memory technologies. These architectures implement specific controllers and memory management units to handle the unique characteristics of PCM, such as write endurance limitations and read/write latency differences. The systems often employ caching mechanisms, wear-leveling algorithms, and specialized addressing schemes to optimize performance while maintaining data integrity across power cycles.Expand Specific Solutions03 Reliability enhancement techniques for PCM

Various techniques are employed to enhance the reliability of PCM-based non-volatile memory systems. These include error correction coding (ECC), redundancy schemes, and adaptive programming algorithms that adjust write parameters based on cell conditions. Temperature compensation methods address the sensitivity of phase change materials to thermal variations. Additionally, specialized refresh operations and data migration strategies are implemented to mitigate resistance drift and maintain data integrity over extended periods of use.Expand Specific Solutions04 PCM packaging solutions and thermal management

Packaging solutions for PCM-based memory focus on thermal management to ensure reliable operation. These include specialized heat dissipation structures, thermal isolation techniques, and package designs that minimize thermal interference between adjacent memory cells. Advanced packaging technologies such as through-silicon vias (TSVs) and 3D stacking are utilized to improve density while maintaining thermal performance. The packaging solutions also address issues related to mechanical stress and environmental factors that could affect PCM reliability.Expand Specific Solutions05 Integration of PCM with conventional memory systems

Integration approaches for combining PCM with conventional memory systems focus on creating hybrid memory architectures that leverage the strengths of each technology. These systems typically use PCM as persistent storage while utilizing DRAM or SRAM for frequently accessed data. Memory controllers are designed to manage data movement between different memory tiers, optimizing for both performance and power efficiency. Special attention is given to power failure protection mechanisms to ensure data consistency during unexpected system shutdowns.Expand Specific Solutions

Leading Companies in PCM NVM and Edge Computing

The PCM Backed NVM for edge computing market is in an early growth phase, characterized by significant R&D investment but limited commercial deployment. The market size is expanding as edge computing applications proliferate, with projections suggesting substantial growth over the next five years. Technologically, Phase Change Memory solutions are approaching maturity with companies like Micron Technology, Intel, and Samsung Electronics leading development efforts. Western Digital and Seagate are advancing storage implementations, while Huawei and Microsoft are focusing on system integration. Chinese players including DapuStor and Shandong Sino-Chip are emerging as significant competitors. Reliability and packaging challenges remain key barriers to widespread adoption, with research institutions like NUDT and Huazhong University contributing to fundamental solutions.

Micron Technology, Inc.

Technical Solution: Micron has pioneered advanced PCM solutions for edge computing with their 3D XPoint technology (developed jointly with Intel). Their approach focuses on solving reliability issues through innovative materials engineering and cell architecture. Micron's PCM technology utilizes a chalcogenide glass compound that changes between amorphous and crystalline states to store data. For edge computing applications, they've developed specialized packaging that addresses thermal challenges through multi-layer thermal dissipation structures. Their reliability enhancement techniques include adaptive write algorithms that adjust pulse parameters based on cell characteristics and environmental conditions. Micron has also implemented error correction code (ECC) mechanisms specifically optimized for PCM's unique error patterns. Their packaging solutions incorporate hermetic sealing techniques to protect PCM cells from environmental contaminants that could accelerate degradation, particularly important for edge devices deployed in harsh environments.

Strengths: Excellent data retention characteristics (10+ years), consistent performance across temperature ranges common in edge deployments, and sophisticated error correction capabilities. Weaknesses: Manufacturing complexity leading to higher costs, limited density compared to latest NAND technologies, and challenges with scaling to smaller process nodes while maintaining reliability.

Intel Corp.

Technical Solution: Intel has developed 3D XPoint technology (marketed as Optane), a phase change memory-based non-volatile memory solution specifically engineered for edge computing applications. Their approach addresses packaging challenges through vertical stacking of memory cells, enabling higher density while maintaining reliability. Intel's PCM technology implements a unique cross-point architecture where memory cells are placed at the intersection of word lines and bit lines, eliminating the need for transistors at each cell. For edge computing reliability, Intel has implemented wear-leveling algorithms that distribute write operations evenly across the memory to prevent premature cell degradation. Their packaging solution incorporates thermal management techniques to mitigate the heat-related reliability issues common in PCM technologies, as phase change materials are sensitive to temperature fluctuations that can affect data retention and endurance.

Strengths: Superior endurance (up to 100x more write cycles than NAND), significantly lower latency than flash memory, and byte-addressability that bridges the gap between DRAM and storage. Weaknesses: Higher cost per GB compared to NAND flash, thermal sensitivity requiring sophisticated temperature management systems, and higher power consumption during write operations.

Critical Patents and Research in PCM Reliability

3D stackable hybrid phase change memory with improved endurance and non-volatility

PatentWO2017176860A1

Innovation

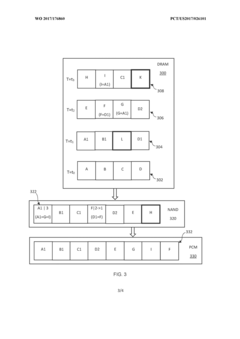

- A multi-tier hybrid memory system using DRAM, NAND flash, and PCM, where data is written to DRAM, merged, and divided into slices with hash calculations to determine duplicates, written to NAND flash, and eventually to PCM, controlling the frequency of PCM writes to extend its endurance.

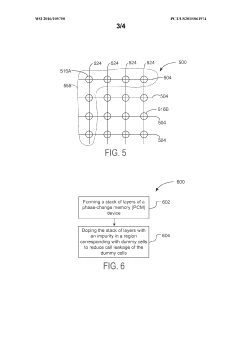

Phase-change memory cell implant for dummy array leakage reduction

PatentWO2016105750A1

Innovation

- Implementing an impurity doping process in the phase-change material and select device layers of dummy cells to shift the threshold voltage and reduce leakage, using techniques like beam line or plasma implantation to introduce impurities such as arsenic, germanium, or silicon, which can reduce vertical leakage by up to 40%.

Thermal Management Strategies for PCM Devices

Effective thermal management is critical for the reliable operation of Phase Change Memory (PCM) devices in edge computing environments. PCM operation fundamentally relies on controlled temperature transitions between amorphous and crystalline states, making thermal considerations paramount to both performance and longevity. Current thermal management strategies for PCM devices can be categorized into device-level, package-level, and system-level approaches.

At the device level, material engineering plays a crucial role in thermal management. Advanced chalcogenide compositions with optimized thermal conductivity properties help contain heat within the active region during programming while facilitating efficient heat dissipation during standby. Thermal interface materials (TIMs) with high thermal conductivity are strategically placed to create efficient thermal pathways away from sensitive PCM cells.

Package-level thermal management incorporates innovative heat spreading techniques. Recent developments include embedded micro heat pipes and vapor chambers within PCM packages that efficiently transport heat away from active memory regions. Three-dimensional thermal modeling has enabled the strategic placement of thermal vias and through-silicon vias (TSVs) that serve as dedicated thermal conduits, significantly improving heat dissipation characteristics.

System-level approaches focus on dynamic thermal management algorithms that adaptively control PCM operation based on temperature conditions. These algorithms implement intelligent write throttling during high-temperature conditions and redistribute memory access patterns to prevent hotspot formation. Advanced cooling solutions including micro-fluidic cooling channels have been demonstrated in laboratory settings, showing promise for high-density PCM implementations in thermally constrained edge devices.

Thermal sensing and feedback mechanisms represent another critical aspect of PCM thermal management. Distributed temperature sensors integrated within PCM arrays provide real-time thermal mapping, enabling precise thermal management responses. These sensors feed into predictive thermal models that anticipate temperature fluctuations based on workload patterns and environmental conditions.

For edge computing applications specifically, passive cooling techniques have gained prominence due to power and form factor constraints. These include phase-change thermal interface materials that absorb heat during peak operation and specialized package designs that maximize surface area for convective cooling without increasing device footprint.

Recent research indicates that thermal management strategies must be tailored to specific edge computing deployment scenarios, as environmental conditions can vary dramatically between industrial, automotive, and consumer applications. This context-aware thermal management represents the frontier of PCM reliability engineering for edge computing implementations.

At the device level, material engineering plays a crucial role in thermal management. Advanced chalcogenide compositions with optimized thermal conductivity properties help contain heat within the active region during programming while facilitating efficient heat dissipation during standby. Thermal interface materials (TIMs) with high thermal conductivity are strategically placed to create efficient thermal pathways away from sensitive PCM cells.

Package-level thermal management incorporates innovative heat spreading techniques. Recent developments include embedded micro heat pipes and vapor chambers within PCM packages that efficiently transport heat away from active memory regions. Three-dimensional thermal modeling has enabled the strategic placement of thermal vias and through-silicon vias (TSVs) that serve as dedicated thermal conduits, significantly improving heat dissipation characteristics.

System-level approaches focus on dynamic thermal management algorithms that adaptively control PCM operation based on temperature conditions. These algorithms implement intelligent write throttling during high-temperature conditions and redistribute memory access patterns to prevent hotspot formation. Advanced cooling solutions including micro-fluidic cooling channels have been demonstrated in laboratory settings, showing promise for high-density PCM implementations in thermally constrained edge devices.

Thermal sensing and feedback mechanisms represent another critical aspect of PCM thermal management. Distributed temperature sensors integrated within PCM arrays provide real-time thermal mapping, enabling precise thermal management responses. These sensors feed into predictive thermal models that anticipate temperature fluctuations based on workload patterns and environmental conditions.

For edge computing applications specifically, passive cooling techniques have gained prominence due to power and form factor constraints. These include phase-change thermal interface materials that absorb heat during peak operation and specialized package designs that maximize surface area for convective cooling without increasing device footprint.

Recent research indicates that thermal management strategies must be tailored to specific edge computing deployment scenarios, as environmental conditions can vary dramatically between industrial, automotive, and consumer applications. This context-aware thermal management represents the frontier of PCM reliability engineering for edge computing implementations.

Supply Chain Considerations for PCM Implementation

The implementation of Phase Change Memory (PCM) technology in edge computing environments necessitates a robust and resilient supply chain framework. Current PCM manufacturing relies heavily on specialized materials including germanium, antimony, and tellurium (GST), which face significant sourcing challenges. Tellurium, in particular, represents a critical bottleneck due to its limited global production—approximately 500-600 metric tons annually—with most extraction occurring as a byproduct of copper refining. This dependency creates inherent supply vulnerabilities, especially considering that over 40% of tellurium production is concentrated in China.

Material qualification processes for PCM components require stringent protocols to ensure consistent performance across varying operational conditions. The industry currently lacks standardized qualification frameworks specifically tailored to PCM technologies, creating potential inconsistencies in component reliability across different suppliers. This gap necessitates the development of comprehensive qualification standards that address the unique thermal cycling and endurance requirements of PCM implementations.

Manufacturing capacity represents another critical consideration in the PCM supply chain. Current global fabrication capabilities for PCM devices remain limited, with only a handful of facilities possessing the specialized equipment and expertise required for high-volume production. This concentration of manufacturing resources creates potential bottlenecks as demand scales, particularly for edge computing applications where deployment volumes may increase rapidly across diverse geographical locations.

Geopolitical factors significantly impact PCM supply chain stability. Trade tensions between major technology-producing nations have already disrupted semiconductor supply chains, with similar vulnerabilities existing for PCM technologies. Strategic stockpiling of critical materials by certain nations further complicates the supply landscape, potentially leading to artificial scarcity and price volatility for essential PCM components.

Alternative material research presents a promising avenue for mitigating supply chain risks. Recent developments in carbon-based phase change materials and silicon-germanium compounds offer potential alternatives to traditional GST formulations, potentially reducing dependency on scarce elements like tellurium. However, these alternative materials remain in early development stages, with significant research required before commercial viability can be established.

Vertical integration strategies are increasingly being adopted by major technology companies to secure PCM supply chains. This approach involves controlling multiple stages of the production process, from material sourcing to device manufacturing, thereby reducing exposure to external supply disruptions. While effective, such strategies require substantial capital investment and may not be feasible for smaller market participants, potentially leading to market consolidation.

Material qualification processes for PCM components require stringent protocols to ensure consistent performance across varying operational conditions. The industry currently lacks standardized qualification frameworks specifically tailored to PCM technologies, creating potential inconsistencies in component reliability across different suppliers. This gap necessitates the development of comprehensive qualification standards that address the unique thermal cycling and endurance requirements of PCM implementations.

Manufacturing capacity represents another critical consideration in the PCM supply chain. Current global fabrication capabilities for PCM devices remain limited, with only a handful of facilities possessing the specialized equipment and expertise required for high-volume production. This concentration of manufacturing resources creates potential bottlenecks as demand scales, particularly for edge computing applications where deployment volumes may increase rapidly across diverse geographical locations.

Geopolitical factors significantly impact PCM supply chain stability. Trade tensions between major technology-producing nations have already disrupted semiconductor supply chains, with similar vulnerabilities existing for PCM technologies. Strategic stockpiling of critical materials by certain nations further complicates the supply landscape, potentially leading to artificial scarcity and price volatility for essential PCM components.

Alternative material research presents a promising avenue for mitigating supply chain risks. Recent developments in carbon-based phase change materials and silicon-germanium compounds offer potential alternatives to traditional GST formulations, potentially reducing dependency on scarce elements like tellurium. However, these alternative materials remain in early development stages, with significant research required before commercial viability can be established.

Vertical integration strategies are increasingly being adopted by major technology companies to secure PCM supply chains. This approach involves controlling multiple stages of the production process, from material sourcing to device manufacturing, thereby reducing exposure to external supply disruptions. While effective, such strategies require substantial capital investment and may not be feasible for smaller market participants, potentially leading to market consolidation.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!