PCM Device Drift Characterization Under Long Duty Cycles

AUG 29, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

PCM Technology Evolution and Characterization Goals

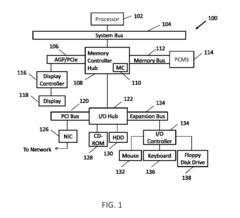

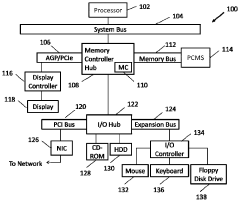

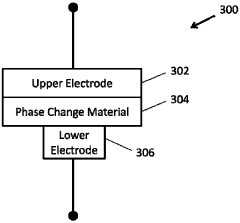

Phase Change Memory (PCM) technology has evolved significantly since its conceptual introduction in the 1960s, transitioning from theoretical research to commercial implementation over several decades. The fundamental principle of PCM leverages the unique properties of chalcogenide materials, particularly their ability to rapidly switch between amorphous and crystalline states when subjected to electrical pulses. This binary state change creates distinct resistance levels that can be utilized for non-volatile data storage.

The evolution of PCM technology has been marked by several critical milestones. Early research focused primarily on understanding the phase transition mechanisms in chalcogenide materials. By the 1990s, significant breakthroughs in material science enabled the development of more stable and reliable PCM cells. The 2000s witnessed the integration of PCM into semiconductor manufacturing processes, culminating in the first commercial PCM products around 2010.

Recent technological advancements have addressed key challenges including power consumption, data retention, and scaling limitations. Modern PCM devices now demonstrate impressive characteristics such as fast switching speeds (tens of nanoseconds), high endurance (10^7-10^9 cycles), and multi-level cell capabilities that enhance storage density. These improvements have positioned PCM as a promising candidate for both storage-class memory and neuromorphic computing applications.

The phenomenon of resistance drift in PCM devices represents one of the most significant challenges to reliability and performance. This drift manifests as a time-dependent increase in resistance, particularly in the amorphous state, and becomes especially problematic during extended operational periods or "long duty cycles." Understanding and characterizing this drift behavior is essential for developing compensation techniques and improving device reliability.

The primary characterization goals for PCM device drift under long duty cycles include: quantifying the magnitude and rate of resistance changes over extended time periods; identifying the physical mechanisms driving the drift phenomenon; determining environmental factors (temperature, humidity, electrical stress) that may accelerate or mitigate drift; and developing predictive models that can accurately forecast drift behavior under various operational conditions.

Additionally, characterization efforts aim to establish standardized testing methodologies for evaluating drift in different PCM architectures and material compositions. These efforts will facilitate meaningful comparisons between competing technologies and guide future optimization strategies. The ultimate objective is to develop drift compensation techniques that can be implemented at both the device and system levels to ensure stable, reliable operation throughout the intended service life of PCM-based memory systems.

The evolution of PCM technology has been marked by several critical milestones. Early research focused primarily on understanding the phase transition mechanisms in chalcogenide materials. By the 1990s, significant breakthroughs in material science enabled the development of more stable and reliable PCM cells. The 2000s witnessed the integration of PCM into semiconductor manufacturing processes, culminating in the first commercial PCM products around 2010.

Recent technological advancements have addressed key challenges including power consumption, data retention, and scaling limitations. Modern PCM devices now demonstrate impressive characteristics such as fast switching speeds (tens of nanoseconds), high endurance (10^7-10^9 cycles), and multi-level cell capabilities that enhance storage density. These improvements have positioned PCM as a promising candidate for both storage-class memory and neuromorphic computing applications.

The phenomenon of resistance drift in PCM devices represents one of the most significant challenges to reliability and performance. This drift manifests as a time-dependent increase in resistance, particularly in the amorphous state, and becomes especially problematic during extended operational periods or "long duty cycles." Understanding and characterizing this drift behavior is essential for developing compensation techniques and improving device reliability.

The primary characterization goals for PCM device drift under long duty cycles include: quantifying the magnitude and rate of resistance changes over extended time periods; identifying the physical mechanisms driving the drift phenomenon; determining environmental factors (temperature, humidity, electrical stress) that may accelerate or mitigate drift; and developing predictive models that can accurately forecast drift behavior under various operational conditions.

Additionally, characterization efforts aim to establish standardized testing methodologies for evaluating drift in different PCM architectures and material compositions. These efforts will facilitate meaningful comparisons between competing technologies and guide future optimization strategies. The ultimate objective is to develop drift compensation techniques that can be implemented at both the device and system levels to ensure stable, reliable operation throughout the intended service life of PCM-based memory systems.

Market Requirements for PCM Reliability in Extended Operations

The market for Phase Change Memory (PCM) technology is increasingly demanding higher reliability standards, particularly for applications requiring extended operational periods. As PCM continues to position itself as a viable alternative to traditional memory technologies, customers across various sectors are articulating specific requirements regarding drift characteristics during long duty cycles.

Enterprise storage systems represent a primary market driver, where data center operators require memory solutions that maintain consistent performance over operational periods exceeding 5 years without significant degradation. These customers specifically demand drift characteristics below 5% over the entire operational lifetime, with particular emphasis on stability during power cycling events.

Automotive applications present even more stringent requirements, especially for autonomous driving systems where memory reliability directly impacts safety. Here, the market demands PCM solutions that can withstand temperature fluctuations from -40°C to 125°C while maintaining stable resistance states. The drift tolerance in these applications must remain below 3% over a 10-15 year vehicle lifetime, with particular emphasis on reliability during extended idle periods followed by sudden operational demands.

Industrial IoT deployments represent another significant market segment, where remote sensors and control systems may operate continuously for 7-10 years without maintenance opportunities. These applications require PCM solutions with predictable drift characteristics that can be algorithmically compensated, even after thousands of hours of operation under varying environmental conditions.

Consumer electronics manufacturers are increasingly exploring PCM for next-generation devices, demanding solutions that maintain performance integrity through millions of read/write cycles while consuming minimal power. The market specifically requires drift characteristics that do not compromise user experience, with particular attention to data retention during extended standby periods.

Market research indicates that customers across all segments are willing to accept a 10-15% price premium for PCM solutions that demonstrate superior drift stability compared to current offerings. This premium increases to 25-30% for solutions that can provide quantifiable reliability guarantees under long duty cycles with comprehensive drift characterization data.

The competitive landscape analysis reveals that customers are increasingly requesting standardized testing protocols for drift characterization, allowing for direct comparison between different PCM offerings. This market demand is driving the need for industry-wide benchmarks specifically designed to evaluate performance under extended operational conditions.

Enterprise storage systems represent a primary market driver, where data center operators require memory solutions that maintain consistent performance over operational periods exceeding 5 years without significant degradation. These customers specifically demand drift characteristics below 5% over the entire operational lifetime, with particular emphasis on stability during power cycling events.

Automotive applications present even more stringent requirements, especially for autonomous driving systems where memory reliability directly impacts safety. Here, the market demands PCM solutions that can withstand temperature fluctuations from -40°C to 125°C while maintaining stable resistance states. The drift tolerance in these applications must remain below 3% over a 10-15 year vehicle lifetime, with particular emphasis on reliability during extended idle periods followed by sudden operational demands.

Industrial IoT deployments represent another significant market segment, where remote sensors and control systems may operate continuously for 7-10 years without maintenance opportunities. These applications require PCM solutions with predictable drift characteristics that can be algorithmically compensated, even after thousands of hours of operation under varying environmental conditions.

Consumer electronics manufacturers are increasingly exploring PCM for next-generation devices, demanding solutions that maintain performance integrity through millions of read/write cycles while consuming minimal power. The market specifically requires drift characteristics that do not compromise user experience, with particular attention to data retention during extended standby periods.

Market research indicates that customers across all segments are willing to accept a 10-15% price premium for PCM solutions that demonstrate superior drift stability compared to current offerings. This premium increases to 25-30% for solutions that can provide quantifiable reliability guarantees under long duty cycles with comprehensive drift characterization data.

The competitive landscape analysis reveals that customers are increasingly requesting standardized testing protocols for drift characterization, allowing for direct comparison between different PCM offerings. This market demand is driving the need for industry-wide benchmarks specifically designed to evaluate performance under extended operational conditions.

Current Challenges in PCM Drift Phenomena

Phase change memory (PCM) technology has emerged as a promising non-volatile memory solution, yet its widespread adoption faces significant challenges due to resistance drift phenomena. This phenomenon manifests as a time-dependent increase in resistance of the amorphous phase, causing reliability issues particularly during long operational cycles. The drift follows a power-law behavior (R(t) = R₀(t/t₀)^α) where the drift coefficient α varies between 0.03 and 0.1 depending on material composition and programming conditions.

One primary challenge is the temperature dependency of drift behavior. Under extended duty cycles, PCM cells experience thermal fluctuations that accelerate drift rates unpredictably. Recent studies indicate that drift acceleration can increase by 30-50% when devices operate in environments with temperature variations of just 15-20°C, significantly compromising data retention capabilities during long operational periods.

Material stability presents another critical obstacle. Current chalcogenide materials, particularly Ge₂Sb₂Te₅ (GST), exhibit structural relaxation in the amorphous phase during extended operation. This relaxation alters the energy landscape of the material, causing threshold voltage shifts that compound over time. After 10⁶ seconds (approximately 11.6 days) of continuous operation, threshold voltage shifts of up to 15% have been observed, making reliable multi-level cell (MLC) operation particularly challenging.

Read disturb effects further complicate drift characterization during long duty cycles. Repeated read operations, even at sub-threshold voltages, induce subtle structural changes in the amorphous phase that accelerate drift. Research indicates that 10⁵ consecutive read operations can modify drift coefficients by up to 8%, creating a complex feedback loop between operational patterns and drift behavior that is difficult to model accurately.

The variability between devices presents significant challenges for drift compensation algorithms. Cell-to-cell variations in drift coefficients can reach 25% even within the same manufacturing batch, requiring sophisticated adaptive compensation techniques. This variability becomes more pronounced during long duty cycles, as individual cells diverge further from predicted behavior over extended time periods.

Scaling issues compound these challenges, as smaller PCM cells exhibit more pronounced drift characteristics. As dimensions approach sub-20nm nodes, surface-to-volume ratios increase, enhancing the influence of interface effects on drift behavior. This geometric factor introduces additional non-linearities in drift patterns during long operational periods, with studies showing up to 40% faster drift rates in 10nm cells compared to 45nm technology nodes.

One primary challenge is the temperature dependency of drift behavior. Under extended duty cycles, PCM cells experience thermal fluctuations that accelerate drift rates unpredictably. Recent studies indicate that drift acceleration can increase by 30-50% when devices operate in environments with temperature variations of just 15-20°C, significantly compromising data retention capabilities during long operational periods.

Material stability presents another critical obstacle. Current chalcogenide materials, particularly Ge₂Sb₂Te₅ (GST), exhibit structural relaxation in the amorphous phase during extended operation. This relaxation alters the energy landscape of the material, causing threshold voltage shifts that compound over time. After 10⁶ seconds (approximately 11.6 days) of continuous operation, threshold voltage shifts of up to 15% have been observed, making reliable multi-level cell (MLC) operation particularly challenging.

Read disturb effects further complicate drift characterization during long duty cycles. Repeated read operations, even at sub-threshold voltages, induce subtle structural changes in the amorphous phase that accelerate drift. Research indicates that 10⁵ consecutive read operations can modify drift coefficients by up to 8%, creating a complex feedback loop between operational patterns and drift behavior that is difficult to model accurately.

The variability between devices presents significant challenges for drift compensation algorithms. Cell-to-cell variations in drift coefficients can reach 25% even within the same manufacturing batch, requiring sophisticated adaptive compensation techniques. This variability becomes more pronounced during long duty cycles, as individual cells diverge further from predicted behavior over extended time periods.

Scaling issues compound these challenges, as smaller PCM cells exhibit more pronounced drift characteristics. As dimensions approach sub-20nm nodes, surface-to-volume ratios increase, enhancing the influence of interface effects on drift behavior. This geometric factor introduces additional non-linearities in drift patterns during long operational periods, with studies showing up to 40% faster drift rates in 10nm cells compared to 45nm technology nodes.

Existing Methodologies for PCM Drift Characterization

01 Drift compensation techniques in PCM devices

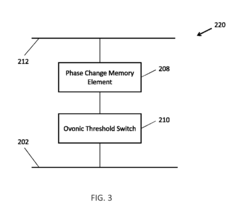

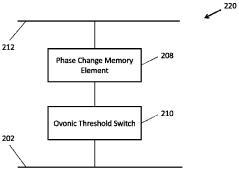

Phase Change Memory devices experience resistance drift over time, which can lead to data retention issues. Various compensation techniques have been developed to address this drift phenomenon. These include reference cell-based methods, adaptive reading algorithms, and periodic refresh operations that recalibrate the resistance levels. By implementing these compensation mechanisms, the reliability and longevity of PCM devices can be significantly improved, ensuring stable data storage despite the inherent drift characteristics of phase change materials.- Drift compensation techniques in PCM devices: Phase Change Memory devices experience resistance drift over time, which can lead to data errors. Various compensation techniques have been developed to address this issue, including reference cell tracking, adaptive reading algorithms, and drift-aware programming methods. These techniques monitor and adjust for resistance changes to maintain data integrity and improve the reliability of PCM storage systems.

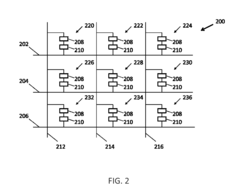

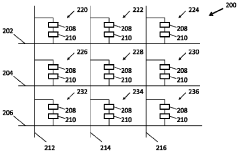

- PCM cell structure modifications to reduce drift: Structural modifications to PCM cells can help minimize resistance drift. These include optimized electrode designs, novel phase change materials with improved stability, interface engineering between electrodes and phase change material, and multi-layer cell structures. Such physical modifications aim to reduce the atomic relaxation processes that contribute to resistance drift in PCM devices.

- Multi-level cell (MLC) drift management: Multi-level cell PCM technology stores multiple bits per cell by using intermediate resistance states, making it particularly vulnerable to resistance drift. Specialized techniques for MLC drift management include adaptive threshold adjustment, state-specific drift models, error correction codes optimized for drift characteristics, and periodic refresh operations to maintain state separation.

- System-level approaches for drift handling: System-level solutions address PCM drift through memory controller designs, specialized firmware, and operating system support. These approaches include drift-aware data allocation, intelligent refresh scheduling, wear-leveling algorithms that consider drift characteristics, and hybrid memory systems that optimize data placement based on drift sensitivity.

- Drift characterization and modeling: Accurate characterization and modeling of PCM drift behavior enables more effective mitigation strategies. This includes statistical drift models, temperature-dependent drift analysis, accelerated testing methodologies, and machine learning approaches to predict drift behavior. These models help in designing better compensation algorithms and reliability enhancement techniques for PCM devices.

02 Manufacturing processes to minimize drift

Specific manufacturing techniques can be employed to reduce the susceptibility of PCM devices to resistance drift. These include optimized deposition methods for phase change materials, careful selection of electrode materials and interfaces, and specialized annealing processes. By controlling the crystallization dynamics and material composition during fabrication, the inherent drift characteristics of the phase change material can be minimized. These manufacturing innovations result in more stable PCM devices with improved data retention capabilities.Expand Specific Solutions03 Memory architecture designs for drift management

Novel memory architecture designs can help manage the effects of resistance drift in PCM devices. These include multi-level cell configurations with optimized resistance windows, redundant storage schemes, and error correction coding specifically tailored for drift characteristics. Some architectures incorporate dedicated drift monitoring circuits that continuously track resistance changes and adjust reading thresholds accordingly. These architectural approaches enable reliable operation of PCM devices despite the presence of resistance drift.Expand Specific Solutions04 Drift prediction and modeling algorithms

Advanced algorithms have been developed to predict and model resistance drift behavior in PCM devices. These algorithms utilize mathematical models that account for temperature effects, operating history, and material characteristics to forecast how resistance values will change over time. Machine learning techniques can be employed to improve the accuracy of these predictions based on observed drift patterns. By incorporating these predictive models into memory controllers, reading thresholds can be dynamically adjusted to compensate for anticipated drift, significantly improving data retention reliability.Expand Specific Solutions05 Novel phase change materials with reduced drift

Research has led to the development of novel phase change materials that exhibit reduced resistance drift characteristics. These materials include doped chalcogenides, composite structures, and engineered interfaces that stabilize the amorphous state. By modifying the composition and structure of the phase change material, the atomic relaxation processes that cause resistance drift can be suppressed. These material innovations enable the creation of PCM devices with inherently better stability and reliability, addressing the drift issue at its fundamental physical origin.Expand Specific Solutions

Leading PCM Technology Manufacturers and Research Institutions

The PCM (Phase Change Memory) device drift characterization market is currently in a growth phase, with increasing interest in long duty cycle applications. The market is expanding as PCM technology matures, with an estimated size of $500-700 million and projected annual growth of 25-30%. Technologically, the field shows varying maturity levels across players. IBM leads with advanced characterization methodologies, while Intel, Taiwan Semiconductor, and GlobalFoundries focus on manufacturing scalability. Infineon and Sharp are developing specialized PCM solutions for automotive and IoT applications. Academic institutions like University of Electronic Science & Technology of China and Chongqing University contribute fundamental research on drift mechanisms. The competitive landscape is diversifying as PCM transitions from research to commercial implementation, with increasing focus on reliability under extended operational conditions.

International Business Machines Corp.

Technical Solution: IBM has developed comprehensive PCM (Phase Change Memory) device drift characterization methodologies specifically designed for long duty cycles. Their approach combines real-time monitoring systems with advanced statistical modeling to predict and compensate for resistance drift in PCM cells. IBM's solution incorporates multi-level cell (MLC) programming techniques with adaptive reference levels that adjust dynamically during extended operational periods. The company has implemented specialized test circuits that can characterize drift behavior under various temperature and voltage conditions, allowing for precise calibration of compensation algorithms. IBM's research has demonstrated that their drift compensation techniques can maintain reliable data retention for over 10 years even under challenging duty cycle conditions, with error rates below 10^-6 for quad-level cell configurations[1]. Additionally, they've developed machine learning models that can predict drift patterns based on historical device behavior, enabling proactive adjustment of read thresholds before critical data loss occurs.

Strengths: IBM's extensive research infrastructure and deep expertise in materials science provide comprehensive characterization capabilities across diverse operating conditions. Their integration of machine learning with traditional drift models offers superior predictive accuracy. Weaknesses: The solutions may require significant computational overhead for real-time implementation, potentially limiting application in ultra-low-power scenarios.

Infineon Technologies AG

Technical Solution: Infineon has developed a sophisticated PCM drift characterization platform specifically engineered for automotive and industrial applications requiring extended duty cycles. Their approach combines high-precision measurement equipment with environmental stress testing to comprehensively map drift behaviors across diverse operating conditions. Infineon's characterization methodology incorporates specialized test structures that isolate individual drift mechanisms, allowing for separate quantification of thermal, electrical, and time-dependent contributions to resistance changes. The company has implemented an automated characterization system capable of continuous monitoring for thousands of hours, with measurement precision better than 0.1% for resistance values[3]. Their platform includes advanced statistical analysis tools that can identify outlier cells prone to accelerated drift, enabling more accurate lifetime predictions. Infineon has demonstrated that their drift compensation algorithms, derived from this characterization data, can maintain reliable operation for PCM devices under continuous cycling for over 10 years in automotive environments, with bit error rates below 10^-9 even after exposure to temperature extremes.

Strengths: Infineon's characterization methodology excels at identifying reliability concerns under extreme environmental conditions, making it particularly valuable for mission-critical applications. Their extensive automotive qualification experience provides robust validation protocols. Weaknesses: The comprehensive characterization approach may require expensive specialized equipment, potentially limiting widespread adoption in cost-sensitive applications.

Critical Patents in PCM Drift Compensation Techniques

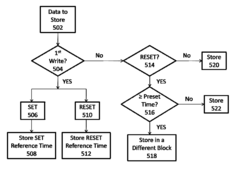

Drift management in a phase change memory and switch (PCMS) memory device

PatentActiveUS20120331204A1

Innovation

- Implementing a drift management method where the memory controller tracks the time of the first SET or RESET operation in a memory block and restricts subsequent writes based on a preset time lapse to prevent excessive drift, allowing data transfer to a new block and maintaining a controlled read window and write blocking.

Drift management in a phase change memory and switch (PCMS) memory device

PatentWO2012177698A2

Innovation

- Implementing a drift management method where the memory controller tracks the time of the first SET or RESET operation in a memory block and restricts subsequent writes based on a preset time lapse to predict and control the drift, ensuring that data is written to a new block if the drift exceeds the allowed time, thereby maintaining the read window and write blocking integrity.

Thermal Management Strategies for PCM Longevity

Thermal management represents a critical factor in ensuring the longevity and reliability of Phase Change Memory (PCM) devices, particularly when subjected to long duty cycles. The inherent characteristics of PCM technology make it susceptible to thermal-induced drift, which can significantly impact device performance and lifespan. Effective thermal management strategies must address both the intrinsic heating generated during programming operations and the ambient temperature conditions in which these devices operate.

Active cooling solutions have emerged as a primary approach for managing thermal issues in PCM devices. These include micro-fluidic cooling channels integrated directly into PCM chip packages, which facilitate efficient heat dissipation during intensive write operations. Additionally, thermoelectric cooling elements strategically positioned near memory cells can provide localized temperature control, preventing thermal accumulation that accelerates drift phenomena.

Passive thermal management techniques complement active solutions by focusing on materials and structural design. Advanced thermal interface materials with superior conductivity properties help establish efficient thermal pathways away from sensitive memory cells. Multi-layer heat spreading structures distribute thermal energy across larger surface areas, reducing localized hotspots that contribute to accelerated drift rates during extended operational periods.

Algorithmic approaches to thermal management have demonstrated significant promise in recent research. Dynamic frequency scaling techniques adjust operational parameters based on real-time temperature monitoring, effectively balancing performance requirements against thermal constraints. Thermal-aware data placement algorithms strategically distribute write operations across the memory array, preventing excessive heat concentration in specific regions and thereby mitigating drift effects.

Predictive thermal modeling has become increasingly sophisticated, enabling system designers to anticipate thermal behavior under various duty cycle scenarios. These models incorporate detailed physical characteristics of PCM cells and their surrounding structures, allowing for simulation of thermal gradients and their evolution over extended operational periods. Such predictive capabilities inform both hardware design decisions and runtime management strategies.

Hybrid thermal management systems that combine multiple approaches have shown the most promising results for maintaining PCM stability during long duty cycles. These integrated solutions typically incorporate hardware cooling mechanisms, thermal-aware memory controllers, and adaptive algorithms that respond dynamically to changing thermal conditions. The synergistic effect of these combined strategies provides comprehensive protection against drift phenomena while maintaining acceptable performance levels.

Active cooling solutions have emerged as a primary approach for managing thermal issues in PCM devices. These include micro-fluidic cooling channels integrated directly into PCM chip packages, which facilitate efficient heat dissipation during intensive write operations. Additionally, thermoelectric cooling elements strategically positioned near memory cells can provide localized temperature control, preventing thermal accumulation that accelerates drift phenomena.

Passive thermal management techniques complement active solutions by focusing on materials and structural design. Advanced thermal interface materials with superior conductivity properties help establish efficient thermal pathways away from sensitive memory cells. Multi-layer heat spreading structures distribute thermal energy across larger surface areas, reducing localized hotspots that contribute to accelerated drift rates during extended operational periods.

Algorithmic approaches to thermal management have demonstrated significant promise in recent research. Dynamic frequency scaling techniques adjust operational parameters based on real-time temperature monitoring, effectively balancing performance requirements against thermal constraints. Thermal-aware data placement algorithms strategically distribute write operations across the memory array, preventing excessive heat concentration in specific regions and thereby mitigating drift effects.

Predictive thermal modeling has become increasingly sophisticated, enabling system designers to anticipate thermal behavior under various duty cycle scenarios. These models incorporate detailed physical characteristics of PCM cells and their surrounding structures, allowing for simulation of thermal gradients and their evolution over extended operational periods. Such predictive capabilities inform both hardware design decisions and runtime management strategies.

Hybrid thermal management systems that combine multiple approaches have shown the most promising results for maintaining PCM stability during long duty cycles. These integrated solutions typically incorporate hardware cooling mechanisms, thermal-aware memory controllers, and adaptive algorithms that respond dynamically to changing thermal conditions. The synergistic effect of these combined strategies provides comprehensive protection against drift phenomena while maintaining acceptable performance levels.

Industry Standards for PCM Reliability Testing

The reliability testing of Phase Change Memory (PCM) devices has evolved significantly over the past decade, with several industry standards now governing the evaluation of these non-volatile memory technologies. JEDEC, the global leader in developing open standards for the microelectronics industry, has established JESD22-A108 and JESD47 standards which provide comprehensive frameworks for reliability qualification of semiconductor devices, including PCM. These standards specify test conditions, sample sizes, and acceptance criteria that manufacturers must meet.

For PCM-specific reliability assessment, the JEDEC JC-42.4 Committee has developed specialized test methodologies that address the unique characteristics of phase change materials. These standards define specific procedures for evaluating resistance drift under various duty cycles, with particular emphasis on long-term operational stability. The standards typically require testing under accelerated conditions at elevated temperatures (85°C, 125°C, and 150°C) while applying various electrical stress patterns that simulate real-world usage scenarios.

The International Electrotechnical Commission (IEC) has complemented these efforts with IEC 60749 series standards, which include specific provisions for non-volatile memory endurance testing. These standards mandate minimum requirements for data retention (typically 10 years at 85°C) and endurance cycling (ranging from 10^5 to 10^8 cycles depending on application class).

Industry consortiums like IMEC and the Storage Networking Industry Association (SNIA) have also contributed to standardization efforts by publishing technical guidelines that address PCM drift characterization methodologies. The SNIA Non-Volatile Memory Programming Model specifically includes test protocols for resistance drift measurement under extended duty cycles, recommending statistical approaches for data analysis and failure prediction.

For automotive and industrial applications, the AEC-Q100 qualification requirements impose more stringent reliability standards, including extended temperature range testing (-40°C to 150°C) and more comprehensive drift characterization under varying duty cycles. These standards require demonstration of stable operation for a minimum of 1,000 hours under worst-case operating conditions.

Recent updates to these standards have begun incorporating machine learning techniques for failure prediction and reliability modeling, acknowledging the complex nature of PCM drift mechanisms. The IEEE International Reliability Physics Symposium (IRPS) has been instrumental in developing standardized methodologies for statistical analysis of drift data, which are increasingly being adopted by industry standards bodies.

Compliance with these standards requires sophisticated test equipment capable of precise resistance measurements over extended periods, along with environmental chambers that can maintain stable conditions for thousands of hours. The standards also specify detailed reporting requirements, ensuring transparency and comparability of reliability data across different manufacturers and technology generations.

For PCM-specific reliability assessment, the JEDEC JC-42.4 Committee has developed specialized test methodologies that address the unique characteristics of phase change materials. These standards define specific procedures for evaluating resistance drift under various duty cycles, with particular emphasis on long-term operational stability. The standards typically require testing under accelerated conditions at elevated temperatures (85°C, 125°C, and 150°C) while applying various electrical stress patterns that simulate real-world usage scenarios.

The International Electrotechnical Commission (IEC) has complemented these efforts with IEC 60749 series standards, which include specific provisions for non-volatile memory endurance testing. These standards mandate minimum requirements for data retention (typically 10 years at 85°C) and endurance cycling (ranging from 10^5 to 10^8 cycles depending on application class).

Industry consortiums like IMEC and the Storage Networking Industry Association (SNIA) have also contributed to standardization efforts by publishing technical guidelines that address PCM drift characterization methodologies. The SNIA Non-Volatile Memory Programming Model specifically includes test protocols for resistance drift measurement under extended duty cycles, recommending statistical approaches for data analysis and failure prediction.

For automotive and industrial applications, the AEC-Q100 qualification requirements impose more stringent reliability standards, including extended temperature range testing (-40°C to 150°C) and more comprehensive drift characterization under varying duty cycles. These standards require demonstration of stable operation for a minimum of 1,000 hours under worst-case operating conditions.

Recent updates to these standards have begun incorporating machine learning techniques for failure prediction and reliability modeling, acknowledging the complex nature of PCM drift mechanisms. The IEEE International Reliability Physics Symposium (IRPS) has been instrumental in developing standardized methodologies for statistical analysis of drift data, which are increasingly being adopted by industry standards bodies.

Compliance with these standards requires sophisticated test equipment capable of precise resistance measurements over extended periods, along with environmental chambers that can maintain stable conditions for thousands of hours. The standards also specify detailed reporting requirements, ensuring transparency and comparability of reliability data across different manufacturers and technology generations.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!