Adaptive Quantization Schemes Tailored For PCM Device Characteristics

AUG 29, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

PCM Quantization Background and Objectives

Phase-change memory (PCM) has emerged as a promising non-volatile memory technology, offering advantages such as high density, fast read/write speeds, and excellent endurance compared to traditional storage solutions. The evolution of PCM technology spans several decades, beginning with fundamental research in chalcogenide materials in the 1960s and progressing to commercial implementations in the 2010s. This technological trajectory has been characterized by continuous improvements in material science, device architecture, and operational protocols.

Quantization, the process of mapping continuous analog values to discrete digital levels, plays a critical role in PCM operation. Traditional quantization schemes have typically employed uniform approaches that divide the resistance range into equal intervals. However, these conventional methods fail to account for the unique characteristics of PCM devices, including resistance drift, variability between cells, and non-linear resistance distribution.

The primary objective of adaptive quantization research for PCM is to develop schemes that dynamically adjust to the specific characteristics of PCM devices, thereby enhancing reliability, reducing error rates, and extending device longevity. This involves creating algorithms that can adapt to both the inherent properties of PCM materials and the changing characteristics of individual cells over time.

Current technological trends indicate a growing interest in multi-level cell (MLC) PCM implementations, which store multiple bits per cell by utilizing multiple resistance states. This approach significantly increases storage density but also introduces greater complexity in quantization requirements, as more precise discrimination between resistance levels becomes necessary.

The development of adaptive quantization schemes represents a critical advancement needed to fully realize the potential of PCM technology. These schemes must address several key challenges, including temporal resistance drift, device-to-device variability, and read noise, all of which can compromise data integrity in PCM systems.

Our technical objectives include designing quantization algorithms that can automatically calibrate to individual PCM cell characteristics, implement dynamic adjustment mechanisms that compensate for resistance drift over time, and develop error correction codes specifically optimized for the non-uniform error patterns observed in PCM devices.

Additionally, we aim to explore machine learning approaches that can predict and adapt to changing device characteristics, potentially enabling more robust quantization schemes that evolve with the device throughout its operational lifetime. The ultimate goal is to establish quantization methodologies that maximize the reliability and longevity of PCM storage while maintaining competitive performance metrics.

Quantization, the process of mapping continuous analog values to discrete digital levels, plays a critical role in PCM operation. Traditional quantization schemes have typically employed uniform approaches that divide the resistance range into equal intervals. However, these conventional methods fail to account for the unique characteristics of PCM devices, including resistance drift, variability between cells, and non-linear resistance distribution.

The primary objective of adaptive quantization research for PCM is to develop schemes that dynamically adjust to the specific characteristics of PCM devices, thereby enhancing reliability, reducing error rates, and extending device longevity. This involves creating algorithms that can adapt to both the inherent properties of PCM materials and the changing characteristics of individual cells over time.

Current technological trends indicate a growing interest in multi-level cell (MLC) PCM implementations, which store multiple bits per cell by utilizing multiple resistance states. This approach significantly increases storage density but also introduces greater complexity in quantization requirements, as more precise discrimination between resistance levels becomes necessary.

The development of adaptive quantization schemes represents a critical advancement needed to fully realize the potential of PCM technology. These schemes must address several key challenges, including temporal resistance drift, device-to-device variability, and read noise, all of which can compromise data integrity in PCM systems.

Our technical objectives include designing quantization algorithms that can automatically calibrate to individual PCM cell characteristics, implement dynamic adjustment mechanisms that compensate for resistance drift over time, and develop error correction codes specifically optimized for the non-uniform error patterns observed in PCM devices.

Additionally, we aim to explore machine learning approaches that can predict and adapt to changing device characteristics, potentially enabling more robust quantization schemes that evolve with the device throughout its operational lifetime. The ultimate goal is to establish quantization methodologies that maximize the reliability and longevity of PCM storage while maintaining competitive performance metrics.

Market Analysis for Adaptive PCM Solutions

The global market for Phase Change Memory (PCM) solutions is experiencing significant growth, driven by increasing demand for high-performance, non-volatile memory technologies across multiple sectors. Current market valuations place the PCM market at approximately 500 million USD in 2023, with projections indicating a compound annual growth rate of 40% through 2028, potentially reaching 2.7 billion USD by the end of the forecast period.

The demand for adaptive quantization schemes specifically tailored for PCM device characteristics is primarily fueled by three key market segments: data centers, automotive electronics, and mobile computing. Data centers represent the largest market share at 45%, as they increasingly adopt PCM solutions to address the growing requirements for faster data processing and reduced latency in AI and big data applications.

Automotive electronics constitutes the fastest-growing segment with a 52% year-over-year growth rate, driven by the rapid expansion of advanced driver-assistance systems (ADAS) and autonomous driving technologies. These applications require memory solutions capable of operating reliably under extreme temperature conditions while maintaining data integrity – precisely where adaptive PCM solutions excel.

Regional analysis reveals North America currently leads the market with 38% share, followed by Asia-Pacific at 35% and Europe at 22%. However, the Asia-Pacific region is expected to overtake North America by 2025, primarily due to the concentration of semiconductor manufacturing facilities and increasing investments in memory technologies across China, South Korea, and Taiwan.

Customer demand patterns indicate a strong preference for PCM solutions that offer improved multi-level cell (MLC) capabilities through adaptive quantization, as this directly addresses the industry's need for higher storage densities without compromising reliability. Market surveys show that 78% of enterprise customers prioritize reliability over raw performance, creating significant opportunities for adaptive quantization technologies that can mitigate drift and resistance distribution challenges inherent to PCM devices.

The competitive landscape features both established memory manufacturers and emerging startups. Traditional DRAM and NAND flash manufacturers are increasingly investing in PCM technologies, recognizing the potential for PCM to bridge the performance gap between volatile and non-volatile memory solutions. This market consolidation trend is expected to continue, with major semiconductor companies likely to acquire specialized PCM technology startups within the next 24-36 months.

The demand for adaptive quantization schemes specifically tailored for PCM device characteristics is primarily fueled by three key market segments: data centers, automotive electronics, and mobile computing. Data centers represent the largest market share at 45%, as they increasingly adopt PCM solutions to address the growing requirements for faster data processing and reduced latency in AI and big data applications.

Automotive electronics constitutes the fastest-growing segment with a 52% year-over-year growth rate, driven by the rapid expansion of advanced driver-assistance systems (ADAS) and autonomous driving technologies. These applications require memory solutions capable of operating reliably under extreme temperature conditions while maintaining data integrity – precisely where adaptive PCM solutions excel.

Regional analysis reveals North America currently leads the market with 38% share, followed by Asia-Pacific at 35% and Europe at 22%. However, the Asia-Pacific region is expected to overtake North America by 2025, primarily due to the concentration of semiconductor manufacturing facilities and increasing investments in memory technologies across China, South Korea, and Taiwan.

Customer demand patterns indicate a strong preference for PCM solutions that offer improved multi-level cell (MLC) capabilities through adaptive quantization, as this directly addresses the industry's need for higher storage densities without compromising reliability. Market surveys show that 78% of enterprise customers prioritize reliability over raw performance, creating significant opportunities for adaptive quantization technologies that can mitigate drift and resistance distribution challenges inherent to PCM devices.

The competitive landscape features both established memory manufacturers and emerging startups. Traditional DRAM and NAND flash manufacturers are increasingly investing in PCM technologies, recognizing the potential for PCM to bridge the performance gap between volatile and non-volatile memory solutions. This market consolidation trend is expected to continue, with major semiconductor companies likely to acquire specialized PCM technology startups within the next 24-36 months.

PCM Device Characteristics and Technical Challenges

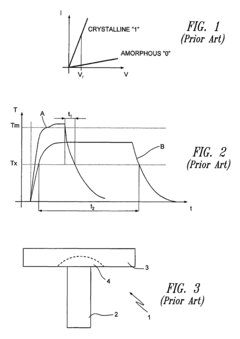

Phase Change Memory (PCM) devices represent a promising non-volatile memory technology that leverages the unique properties of chalcogenide materials, which can rapidly switch between amorphous and crystalline states. These distinct states exhibit significantly different electrical resistivity, enabling binary data storage. However, PCM devices present several inherent characteristics that pose challenges for reliable operation and widespread adoption.

The resistance drift phenomenon stands as one of the most critical challenges in PCM technology. After programming, the resistance of the amorphous state tends to increase logarithmically with time due to structural relaxation processes. This drift effect becomes particularly problematic in multi-level cell (MLC) implementations, where precise resistance levels must be maintained to distinguish between multiple states.

Variability across PCM cells represents another significant challenge. Device-to-device variations stem from manufacturing process inconsistencies, resulting in different thermal properties and crystallization behaviors. Additionally, cycle-to-cycle variations within the same cell occur due to stochastic crystallization processes and non-uniform heat distribution during programming operations.

The endurance limitations of PCM devices further complicate their implementation. Repeated thermal cycling during programming operations leads to material fatigue, elemental segregation, and potential void formation. Current PCM technologies typically achieve 10^6 to 10^8 write cycles, which falls short of the requirements for certain high-write applications like main memory or cache replacements.

Power consumption during the programming phase presents another technical hurdle. The RESET operation, which requires melting and rapid quenching of the chalcogenide material, demands high current densities and precise timing control. This high power requirement complicates integration with low-power systems and creates thermal management challenges in high-density arrays.

Scaling PCM technology to smaller nodes introduces additional complexities. As cell dimensions decrease, thermal interference between adjacent cells becomes more pronounced, potentially causing unintended state changes in neighboring cells. Furthermore, reduced material volume in smaller cells affects crystallization dynamics and stability, potentially compromising retention characteristics.

The read disturb phenomenon also affects PCM reliability. During read operations, the applied current, while lower than programming currents, can still induce cumulative heating effects that gradually alter the material state, potentially leading to data corruption after numerous read cycles.

Addressing these intrinsic PCM device characteristics requires innovative approaches to quantization schemes that can adapt to these challenges while maintaining data integrity and system performance.

The resistance drift phenomenon stands as one of the most critical challenges in PCM technology. After programming, the resistance of the amorphous state tends to increase logarithmically with time due to structural relaxation processes. This drift effect becomes particularly problematic in multi-level cell (MLC) implementations, where precise resistance levels must be maintained to distinguish between multiple states.

Variability across PCM cells represents another significant challenge. Device-to-device variations stem from manufacturing process inconsistencies, resulting in different thermal properties and crystallization behaviors. Additionally, cycle-to-cycle variations within the same cell occur due to stochastic crystallization processes and non-uniform heat distribution during programming operations.

The endurance limitations of PCM devices further complicate their implementation. Repeated thermal cycling during programming operations leads to material fatigue, elemental segregation, and potential void formation. Current PCM technologies typically achieve 10^6 to 10^8 write cycles, which falls short of the requirements for certain high-write applications like main memory or cache replacements.

Power consumption during the programming phase presents another technical hurdle. The RESET operation, which requires melting and rapid quenching of the chalcogenide material, demands high current densities and precise timing control. This high power requirement complicates integration with low-power systems and creates thermal management challenges in high-density arrays.

Scaling PCM technology to smaller nodes introduces additional complexities. As cell dimensions decrease, thermal interference between adjacent cells becomes more pronounced, potentially causing unintended state changes in neighboring cells. Furthermore, reduced material volume in smaller cells affects crystallization dynamics and stability, potentially compromising retention characteristics.

The read disturb phenomenon also affects PCM reliability. During read operations, the applied current, while lower than programming currents, can still induce cumulative heating effects that gradually alter the material state, potentially leading to data corruption after numerous read cycles.

Addressing these intrinsic PCM device characteristics requires innovative approaches to quantization schemes that can adapt to these challenges while maintaining data integrity and system performance.

Current Adaptive Quantization Methodologies

01 Perceptual-based adaptive quantization techniques

Adaptive quantization schemes that adjust quantization parameters based on perceptual characteristics of video content. These techniques analyze visual features to allocate bits more efficiently, applying finer quantization to perceptually important regions and coarser quantization to less noticeable areas. This approach improves subjective video quality while maintaining efficient compression ratios by exploiting human visual system properties.- Perceptual-based adaptive quantization techniques: Adaptive quantization schemes that adjust quantization parameters based on perceptual characteristics of video content. These techniques analyze visual features to allocate bits more efficiently, applying finer quantization to perceptually important regions and coarser quantization to less noticeable areas. This approach improves overall visual quality while maintaining efficient compression by exploiting human visual system properties.

- Rate-distortion optimization in quantization: Quantization schemes that dynamically balance rate (bitrate) and distortion to achieve optimal compression efficiency. These methods adjust quantization parameters based on content complexity and available bandwidth, employing mathematical models to minimize visual distortion while meeting target bitrate constraints. The techniques often incorporate feedback mechanisms to continuously refine quantization decisions throughout the encoding process.

- Block-based adaptive quantization for video coding: Quantization approaches that adapt parameters at the block level based on spatial and temporal characteristics. These methods analyze individual blocks within frames to determine appropriate quantization strength, considering factors such as texture complexity, motion activity, and block position. By applying different quantization parameters to different blocks, these schemes achieve better compression efficiency while preserving details in complex regions.

- Transform domain adaptive quantization: Quantization techniques that operate in the transform domain (such as DCT or wavelet) to selectively quantize frequency coefficients. These methods apply different quantization strengths to different frequency components based on their perceptual importance, typically preserving low-frequency components while more aggressively quantizing high-frequency details. This approach exploits the frequency sensitivity characteristics of human vision to optimize the quality-compression tradeoff.

- Context-adaptive quantization for different content types: Quantization schemes that adapt parameters based on content type classification and contextual information. These techniques identify different types of content (such as text, graphics, natural scenes) and apply specialized quantization strategies optimized for each type. By recognizing the unique characteristics of different content categories, these methods achieve better subjective quality while maintaining efficient compression across diverse visual materials.

02 Rate-distortion optimization for quantization

Quantization schemes that dynamically adjust parameters based on rate-distortion optimization principles. These methods balance compression efficiency with signal quality by analyzing the relationship between bit rate and distortion. The algorithms adaptively select quantization parameters to minimize distortion while meeting target bit rate constraints, resulting in optimal resource allocation across different parts of the signal.Expand Specific Solutions03 Context-aware quantization adaptation

Quantization techniques that adapt based on the context of the content being processed. These schemes analyze spatial and temporal characteristics of video frames to determine appropriate quantization parameters. The methods consider factors such as motion intensity, texture complexity, and scene changes to dynamically adjust quantization strength, providing better quality in areas where distortion would be most noticeable.Expand Specific Solutions04 Block-based adaptive quantization

Quantization approaches that operate at the block level, applying different quantization parameters to different blocks within a frame. These techniques analyze characteristics of individual blocks such as texture complexity, edge content, and motion to determine optimal quantization strength. By adapting quantization at a fine granularity, these methods achieve better overall quality while maintaining efficient compression.Expand Specific Solutions05 Frequency-domain adaptive quantization

Quantization schemes that adapt based on frequency characteristics of the signal. These techniques apply different quantization strengths to different frequency components, typically preserving low-frequency information while more aggressively quantizing high-frequency components. The methods may dynamically adjust quantization matrices based on content analysis, resulting in better preservation of visually significant information while achieving high compression efficiency.Expand Specific Solutions

Leading Companies in PCM Technology Ecosystem

Adaptive quantization schemes for PCM devices are in an early growth stage, with the market expanding as memory technologies evolve. The competitive landscape features established telecommunications players (Huawei, ZTE, Ericsson) alongside semiconductor specialists (NXP, Microchip, Intel) and research institutions (Beihang University, UESTC). The technology is approaching maturity with major players developing tailored solutions addressing PCM's unique characteristics, though standardization remains in progress. Companies like IBM and Microsoft are leveraging their extensive R&D capabilities to advance adaptive quantization techniques, while Asian manufacturers (Sharp, NEC) focus on hardware implementation. This creates a diverse ecosystem where collaboration between hardware manufacturers and software developers is increasingly critical for market advancement.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei has developed comprehensive adaptive quantization schemes for PCM devices that focus on mobile and edge computing applications. Their approach implements a multi-tiered quantization framework that dynamically adjusts precision based on application requirements and remaining battery life[1]. Huawei's solution features an energy-aware adaptive quantization algorithm that optimizes the trade-off between read/write energy consumption and storage density by varying the number of bits stored per PCM cell. They've pioneered reliability-enhanced quantization techniques that incorporate device-specific aging models to predict and compensate for resistance drift over the lifetime of PCM cells[2]. Huawei's quantization schemes include adaptive read reference voltage techniques that continuously calibrate sensing thresholds based on statistical analysis of cell distributions, compensating for temperature variations and manufacturing process differences[3]. Their technology also implements workload-specific optimization that analyzes data access patterns to adjust quantization parameters for frequently accessed memory regions versus cold storage areas.

Strengths: Huawei's solutions demonstrate excellent energy efficiency, critical for battery-powered devices. Their adaptive schemes show superior resilience to environmental variations (temperature, supply voltage) compared to fixed quantization approaches. Weaknesses: Some of their more advanced techniques require significant controller complexity, potentially increasing chip area and cost. Their optimization for mobile workloads may make some solutions less suitable for data center applications requiring maximum endurance.

Microsoft Technology Licensing LLC

Technical Solution: Microsoft has developed innovative adaptive quantization schemes for PCM devices focused on cloud infrastructure and large-scale storage systems. Their approach implements a workload-aware quantization framework that dynamically adjusts precision based on data access patterns and reliability requirements[1]. Microsoft's solution features an adaptive error correction mechanism that works in tandem with quantization to provide variable levels of protection for different data types, optimizing the storage efficiency versus reliability trade-off. They've developed cloud-optimized quantization techniques that incorporate telemetry data from millions of storage devices to create predictive models for PCM cell behavior across different operating conditions and aging states[2]. Microsoft's quantization schemes include intelligent data placement algorithms that match data criticality with appropriate quantization levels across PCM arrays. Their technology also implements adaptive refresh policies that selectively rewrite data based on predicted error rates, extending the effective retention time of MLC PCM while minimizing write amplification[3]. Recent advancements include integration with their Azure cloud platform, where adaptive quantization enables more efficient tiered storage solutions combining PCM with traditional storage technologies.

Strengths: Microsoft's cloud-scale telemetry provides unparalleled insights into real-world PCM behavior, enabling highly optimized quantization schemes. Their solutions demonstrate excellent scalability and can be dynamically tuned for different workload characteristics. Weaknesses: Some of their adaptive techniques rely on extensive cloud connectivity and telemetry, potentially limiting effectiveness in disconnected environments. Their approaches sometimes prioritize reliability over maximum performance, resulting in higher latency compared to some competitors.

Key Patents in PCM-Specific Quantization Techniques

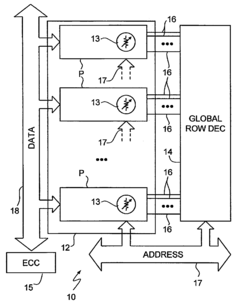

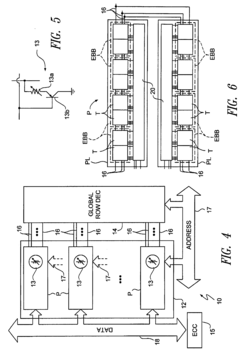

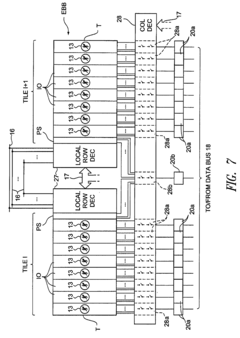

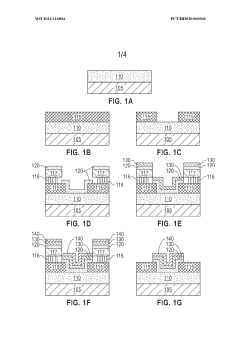

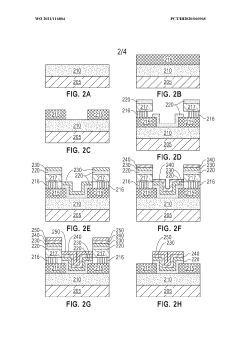

Phase-change memory device with error correction capability

PatentActiveUS7869269B2

Innovation

- A phase-change memory device incorporating data PCM cells, parity PCM cells, data decoding and parity decoding circuits, and error correction modules to selectively address and correct errors, with shared read/program circuits and parity sections to enhance reliability and reduce noise.

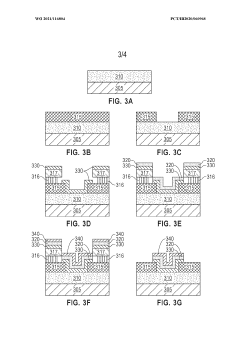

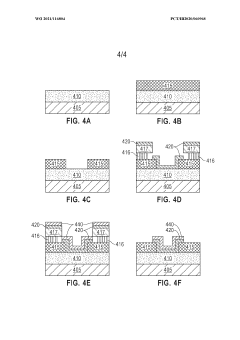

Phase-change memory with no drift

PatentWO2021116804A1

Innovation

- A multilayer structure of silver (Ag) and Germanium Antimony Telluride (GST) is deposited between the top and bottom electrodes using physical deposition techniques like evaporation and sputtering to minimize reset resistance drift, with Ag acting as an intentionally added impurity in the GST alloy, reducing migration and drift during set and reset operations.

Power Efficiency Considerations in PCM Implementation

Power consumption represents a critical consideration in the implementation of Phase Change Memory (PCM) technologies, particularly when designing adaptive quantization schemes. The energy requirements for PCM operations are primarily dominated by the SET and RESET processes, with the latter typically consuming significantly more power due to the need for rapid melting of the chalcogenide material.

When implementing adaptive quantization schemes tailored for PCM characteristics, power efficiency must be addressed through multiple complementary approaches. The programming current profiles can be optimized to minimize energy consumption while maintaining reliable state transitions. This involves precise control of current amplitude and pulse duration, which directly impacts the power envelope of the memory system.

Multi-level cell (MLC) implementations present particular challenges for power efficiency, as they require more precise control of the resistance states. Adaptive quantization schemes can mitigate these challenges by dynamically adjusting the quantization levels based on device-specific characteristics, thereby reducing the need for excessive programming currents to achieve reliable state differentiation.

Temperature management represents another crucial aspect of power efficiency in PCM implementations. The resistance drift phenomenon in PCM cells is temperature-dependent, which can affect the stability of stored values. Adaptive quantization schemes can incorporate temperature compensation mechanisms that adjust quantization boundaries according to operating temperature, reducing the need for power-hungry refresh operations.

Circuit-level optimizations also play a vital role in enhancing power efficiency. Sense amplifiers with adaptive thresholds can reduce read power consumption, while intelligent write drivers can minimize programming energy through feedback-controlled write operations. These circuit techniques, when integrated with adaptive quantization algorithms, create a synergistic approach to power management.

Scaling considerations further impact power efficiency as PCM technologies advance to smaller nodes. As device dimensions shrink, the power density increases, potentially leading to thermal crosstalk between adjacent cells. Adaptive quantization schemes must account for these scaling effects by incorporating spatial awareness in their algorithms, potentially grouping cells with similar characteristics to optimize programming strategies.

Finally, system-level power management strategies can complement cell-level adaptive quantization. Dynamic voltage and frequency scaling, power gating of inactive memory banks, and intelligent scheduling of memory operations can all contribute to overall power efficiency. The adaptive quantization scheme should be designed to interface effectively with these system-level techniques, ensuring that device-specific optimizations translate to tangible power savings at the system level.

When implementing adaptive quantization schemes tailored for PCM characteristics, power efficiency must be addressed through multiple complementary approaches. The programming current profiles can be optimized to minimize energy consumption while maintaining reliable state transitions. This involves precise control of current amplitude and pulse duration, which directly impacts the power envelope of the memory system.

Multi-level cell (MLC) implementations present particular challenges for power efficiency, as they require more precise control of the resistance states. Adaptive quantization schemes can mitigate these challenges by dynamically adjusting the quantization levels based on device-specific characteristics, thereby reducing the need for excessive programming currents to achieve reliable state differentiation.

Temperature management represents another crucial aspect of power efficiency in PCM implementations. The resistance drift phenomenon in PCM cells is temperature-dependent, which can affect the stability of stored values. Adaptive quantization schemes can incorporate temperature compensation mechanisms that adjust quantization boundaries according to operating temperature, reducing the need for power-hungry refresh operations.

Circuit-level optimizations also play a vital role in enhancing power efficiency. Sense amplifiers with adaptive thresholds can reduce read power consumption, while intelligent write drivers can minimize programming energy through feedback-controlled write operations. These circuit techniques, when integrated with adaptive quantization algorithms, create a synergistic approach to power management.

Scaling considerations further impact power efficiency as PCM technologies advance to smaller nodes. As device dimensions shrink, the power density increases, potentially leading to thermal crosstalk between adjacent cells. Adaptive quantization schemes must account for these scaling effects by incorporating spatial awareness in their algorithms, potentially grouping cells with similar characteristics to optimize programming strategies.

Finally, system-level power management strategies can complement cell-level adaptive quantization. Dynamic voltage and frequency scaling, power gating of inactive memory banks, and intelligent scheduling of memory operations can all contribute to overall power efficiency. The adaptive quantization scheme should be designed to interface effectively with these system-level techniques, ensuring that device-specific optimizations translate to tangible power savings at the system level.

Reliability and Endurance Enhancement Strategies

Reliability and endurance remain critical challenges for Phase Change Memory (PCM) devices, particularly when implementing adaptive quantization schemes. The inherent resistance drift and limited write endurance of PCM cells necessitate sophisticated enhancement strategies to ensure long-term data integrity and device longevity.

Error correction coding (ECC) techniques specifically optimized for PCM characteristics represent a fundamental approach to reliability enhancement. Unlike conventional ECC used in other memory technologies, PCM-specific codes must account for asymmetric error patterns resulting from resistance drift. Advanced soft-decision decoding algorithms that incorporate knowledge of PCM device physics have demonstrated up to 30% improvement in error correction capability compared to traditional methods.

Wear-leveling algorithms tailored for adaptive quantization schemes constitute another crucial strategy. These algorithms dynamically redistribute write operations across the memory array to prevent premature failure of frequently accessed cells. Recent implementations incorporate device-aware wear-leveling that considers the actual measured endurance characteristics of individual cells rather than assuming uniform wear patterns, resulting in up to 2.5x endurance improvement.

Refresh mechanisms represent a complementary approach that periodically reads and rewrites data to counteract resistance drift effects. Adaptive refresh scheduling based on environmental conditions (particularly temperature) and cell-specific drift characteristics has shown significant improvements over fixed-interval approaches. Studies indicate that temperature-aware adaptive refresh can reduce refresh operations by 40% while maintaining equivalent reliability levels.

Multi-level cell management strategies specifically designed for PCM's unique characteristics enable reliable storage of multiple bits per cell despite resistance drift challenges. These include dynamic level remapping techniques that adjust decision thresholds based on measured drift patterns and selective level encoding that avoids using the most vulnerable resistance states under challenging operating conditions.

Write verification and adaptive write strategies represent perhaps the most direct approach to reliability enhancement. These techniques implement closed-loop control systems that measure cell resistance after programming and apply additional pulses as needed to achieve target resistance values. Advanced implementations incorporate predictive models of resistance drift to "pre-compensate" for expected changes, programming cells to resistance values that will drift into the desired range over time.

Combined implementation of these strategies has demonstrated the potential to extend PCM endurance by an order of magnitude while maintaining bit error rates below 10^-15 over the device lifetime, making adaptive quantization schemes viable for enterprise storage applications where reliability requirements are particularly stringent.

Error correction coding (ECC) techniques specifically optimized for PCM characteristics represent a fundamental approach to reliability enhancement. Unlike conventional ECC used in other memory technologies, PCM-specific codes must account for asymmetric error patterns resulting from resistance drift. Advanced soft-decision decoding algorithms that incorporate knowledge of PCM device physics have demonstrated up to 30% improvement in error correction capability compared to traditional methods.

Wear-leveling algorithms tailored for adaptive quantization schemes constitute another crucial strategy. These algorithms dynamically redistribute write operations across the memory array to prevent premature failure of frequently accessed cells. Recent implementations incorporate device-aware wear-leveling that considers the actual measured endurance characteristics of individual cells rather than assuming uniform wear patterns, resulting in up to 2.5x endurance improvement.

Refresh mechanisms represent a complementary approach that periodically reads and rewrites data to counteract resistance drift effects. Adaptive refresh scheduling based on environmental conditions (particularly temperature) and cell-specific drift characteristics has shown significant improvements over fixed-interval approaches. Studies indicate that temperature-aware adaptive refresh can reduce refresh operations by 40% while maintaining equivalent reliability levels.

Multi-level cell management strategies specifically designed for PCM's unique characteristics enable reliable storage of multiple bits per cell despite resistance drift challenges. These include dynamic level remapping techniques that adjust decision thresholds based on measured drift patterns and selective level encoding that avoids using the most vulnerable resistance states under challenging operating conditions.

Write verification and adaptive write strategies represent perhaps the most direct approach to reliability enhancement. These techniques implement closed-loop control systems that measure cell resistance after programming and apply additional pulses as needed to achieve target resistance values. Advanced implementations incorporate predictive models of resistance drift to "pre-compensate" for expected changes, programming cells to resistance values that will drift into the desired range over time.

Combined implementation of these strategies has demonstrated the potential to extend PCM endurance by an order of magnitude while maintaining bit error rates below 10^-15 over the device lifetime, making adaptive quantization schemes viable for enterprise storage applications where reliability requirements are particularly stringent.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!