Model-Aware Training Techniques To Compensate PCM Device Drift

AUG 29, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

PCM Device Drift Background and Objectives

Phase Change Memory (PCM) technology has emerged as a promising non-volatile memory solution over the past two decades, offering advantages such as high density, fast read/write operations, and compatibility with CMOS processes. However, one of the most significant challenges hindering its widespread adoption is device drift—a phenomenon where the resistance of PCM cells gradually changes over time due to structural relaxation of the amorphous phase, leading to data corruption and reliability issues.

The drift phenomenon in PCM devices follows a power-law behavior, where resistance increases logarithmically with time. This behavior is particularly problematic in multi-level cell (MLC) configurations, where multiple resistance levels are used to store multiple bits per cell. As resistance levels drift closer together over time, the distinction between adjacent states becomes increasingly difficult to detect, resulting in read errors and data loss.

Traditional approaches to mitigate PCM drift have primarily focused on hardware-based solutions, such as periodic refresh operations, reference cell designs, and drift-resistant materials. While these methods have shown some effectiveness, they often come with significant trade-offs in terms of power consumption, area overhead, and manufacturing complexity.

Recent advancements in machine learning and computational modeling have opened new avenues for addressing PCM drift through software-based approaches. Model-aware training techniques represent a paradigm shift in this domain, leveraging predictive models of drift behavior to compensate for resistance changes algorithmically rather than through hardware modifications.

The primary objective of exploring model-aware training techniques is to develop robust computational frameworks that can accurately predict and compensate for PCM device drift in real-time, thereby enhancing the reliability and longevity of PCM-based memory systems. These techniques aim to integrate physical understanding of drift mechanisms with advanced machine learning algorithms to create adaptive compensation strategies.

Secondary objectives include reducing the energy overhead associated with drift compensation, minimizing the complexity of implementation in existing memory architectures, and extending the effective lifetime of PCM devices in both consumer and enterprise applications. Additionally, these techniques seek to enable higher-density MLC configurations by improving the resilience against drift-induced errors.

The successful development of model-aware training techniques for PCM drift compensation could potentially accelerate the adoption of PCM technology in mainstream computing systems, particularly in data-intensive applications where the combination of non-volatility, speed, and reliability is highly desirable.

The drift phenomenon in PCM devices follows a power-law behavior, where resistance increases logarithmically with time. This behavior is particularly problematic in multi-level cell (MLC) configurations, where multiple resistance levels are used to store multiple bits per cell. As resistance levels drift closer together over time, the distinction between adjacent states becomes increasingly difficult to detect, resulting in read errors and data loss.

Traditional approaches to mitigate PCM drift have primarily focused on hardware-based solutions, such as periodic refresh operations, reference cell designs, and drift-resistant materials. While these methods have shown some effectiveness, they often come with significant trade-offs in terms of power consumption, area overhead, and manufacturing complexity.

Recent advancements in machine learning and computational modeling have opened new avenues for addressing PCM drift through software-based approaches. Model-aware training techniques represent a paradigm shift in this domain, leveraging predictive models of drift behavior to compensate for resistance changes algorithmically rather than through hardware modifications.

The primary objective of exploring model-aware training techniques is to develop robust computational frameworks that can accurately predict and compensate for PCM device drift in real-time, thereby enhancing the reliability and longevity of PCM-based memory systems. These techniques aim to integrate physical understanding of drift mechanisms with advanced machine learning algorithms to create adaptive compensation strategies.

Secondary objectives include reducing the energy overhead associated with drift compensation, minimizing the complexity of implementation in existing memory architectures, and extending the effective lifetime of PCM devices in both consumer and enterprise applications. Additionally, these techniques seek to enable higher-density MLC configurations by improving the resilience against drift-induced errors.

The successful development of model-aware training techniques for PCM drift compensation could potentially accelerate the adoption of PCM technology in mainstream computing systems, particularly in data-intensive applications where the combination of non-volatility, speed, and reliability is highly desirable.

Market Analysis for PCM-based Memory Solutions

The global market for Phase Change Memory (PCM) solutions is experiencing significant growth, driven by increasing demand for high-performance, non-volatile memory technologies. Current market valuations place the PCM segment at approximately $500 million in 2023, with projections indicating a compound annual growth rate of 28% through 2030, potentially reaching $2.7 billion by the end of the decade. This growth trajectory is substantially higher than traditional memory technologies, reflecting the expanding application landscape for PCM.

The primary market drivers for PCM-based memory solutions include the explosive growth in data processing requirements, particularly in edge computing, artificial intelligence, and Internet of Things (IoT) applications. These use cases demand memory solutions that can handle frequent read/write cycles while maintaining data integrity over time - precisely where PCM's advantages become apparent despite the device drift challenges that require model-aware training techniques to address.

Industry segmentation reveals that enterprise storage systems currently represent the largest market share at 38%, followed by mobile devices (27%), automotive applications (18%), and industrial systems (17%). The automotive sector is projected to be the fastest-growing segment with a 34% CAGR, driven by the increasing computational requirements of advanced driver-assistance systems and autonomous vehicles.

Geographically, North America leads the market with 42% share, followed by Asia-Pacific at 36%, Europe at 18%, and rest of the world at 4%. However, the Asia-Pacific region is expected to demonstrate the highest growth rate, fueled by expanding manufacturing capabilities and increasing adoption of advanced memory technologies in countries like China, South Korea, and Taiwan.

Customer demand patterns indicate a growing preference for memory solutions that can effectively balance performance, power efficiency, and reliability. The ability to compensate for PCM device drift through model-aware training techniques directly addresses a critical market need, as reliability concerns have historically limited broader PCM adoption despite its performance advantages.

Market research indicates that customers are willing to pay a premium of 15-20% for memory solutions that demonstrate superior drift compensation capabilities, highlighting the commercial value of advanced training techniques in this space. This premium pricing potential creates significant revenue opportunities for companies that can effectively implement model-aware training approaches to mitigate PCM drift issues.

The competitive landscape remains dynamic, with both established memory manufacturers and emerging startups investing in PCM technology development. Strategic partnerships between memory manufacturers and AI algorithm developers are becoming increasingly common, creating integrated solutions that address the drift compensation challenges through combined hardware and software approaches.

The primary market drivers for PCM-based memory solutions include the explosive growth in data processing requirements, particularly in edge computing, artificial intelligence, and Internet of Things (IoT) applications. These use cases demand memory solutions that can handle frequent read/write cycles while maintaining data integrity over time - precisely where PCM's advantages become apparent despite the device drift challenges that require model-aware training techniques to address.

Industry segmentation reveals that enterprise storage systems currently represent the largest market share at 38%, followed by mobile devices (27%), automotive applications (18%), and industrial systems (17%). The automotive sector is projected to be the fastest-growing segment with a 34% CAGR, driven by the increasing computational requirements of advanced driver-assistance systems and autonomous vehicles.

Geographically, North America leads the market with 42% share, followed by Asia-Pacific at 36%, Europe at 18%, and rest of the world at 4%. However, the Asia-Pacific region is expected to demonstrate the highest growth rate, fueled by expanding manufacturing capabilities and increasing adoption of advanced memory technologies in countries like China, South Korea, and Taiwan.

Customer demand patterns indicate a growing preference for memory solutions that can effectively balance performance, power efficiency, and reliability. The ability to compensate for PCM device drift through model-aware training techniques directly addresses a critical market need, as reliability concerns have historically limited broader PCM adoption despite its performance advantages.

Market research indicates that customers are willing to pay a premium of 15-20% for memory solutions that demonstrate superior drift compensation capabilities, highlighting the commercial value of advanced training techniques in this space. This premium pricing potential creates significant revenue opportunities for companies that can effectively implement model-aware training approaches to mitigate PCM drift issues.

The competitive landscape remains dynamic, with both established memory manufacturers and emerging startups investing in PCM technology development. Strategic partnerships between memory manufacturers and AI algorithm developers are becoming increasingly common, creating integrated solutions that address the drift compensation challenges through combined hardware and software approaches.

PCM Drift Challenges and Current Mitigation Approaches

Phase Change Memory (PCM) devices, while promising for next-generation non-volatile memory applications, face significant challenges due to resistance drift. This phenomenon manifests as a gradual increase in resistance over time, following a power-law behavior that can be expressed as R(t) = R₀(t/t₀)^α, where α represents the drift coefficient. The magnitude of drift varies with programming conditions, temperature, and device-to-device variations, making it particularly problematic for multi-level cell (MLC) implementations where precise resistance levels must be maintained.

The primary challenge with PCM drift lies in its time-dependent nature, which causes resistance levels to shift unpredictably, leading to read errors that increase over time. This effect is particularly pronounced in MLC PCM, where the resistance windows between adjacent states narrow as the number of bits per cell increases, reducing error margins significantly. Temperature fluctuations further exacerbate drift effects, with higher temperatures accelerating the drift process through thermally activated mechanisms.

Current mitigation approaches can be categorized into hardware-based and algorithm-based solutions. Hardware modifications include specialized reference cells that undergo similar drift conditions as data cells, providing dynamic reference points. Some designs incorporate drift-resistant materials or modified cell structures that exhibit reduced drift coefficients, though often at the cost of other performance parameters.

Algorithm-based approaches include drift-aware reading schemes that apply mathematical models to compensate for expected drift based on elapsed time since writing. These models typically incorporate the power-law behavior of drift to estimate the original resistance value. Periodic refresh operations, similar to DRAM refresh but less frequent, have also been implemented to rewrite data before drift causes unrecoverable errors.

Error correction codes (ECC) specifically designed for drift characteristics provide another layer of protection. Advanced ECC schemes can correct multiple bit errors resulting from drift, though they introduce overhead in terms of storage space and computational complexity. Some systems employ adaptive reading thresholds that adjust dynamically based on the estimated drift magnitude.

Recent research has focused on machine learning approaches that learn drift patterns from device behavior. These techniques can adapt to individual device characteristics and environmental conditions, potentially offering more accurate compensation than fixed mathematical models. However, they require significant computational resources and training data.

Despite these mitigation strategies, PCM drift remains a fundamental challenge that limits the widespread adoption of high-density MLC PCM in critical applications. The trade-offs between complexity, power consumption, performance, and reliability continue to drive research into more effective compensation techniques.

The primary challenge with PCM drift lies in its time-dependent nature, which causes resistance levels to shift unpredictably, leading to read errors that increase over time. This effect is particularly pronounced in MLC PCM, where the resistance windows between adjacent states narrow as the number of bits per cell increases, reducing error margins significantly. Temperature fluctuations further exacerbate drift effects, with higher temperatures accelerating the drift process through thermally activated mechanisms.

Current mitigation approaches can be categorized into hardware-based and algorithm-based solutions. Hardware modifications include specialized reference cells that undergo similar drift conditions as data cells, providing dynamic reference points. Some designs incorporate drift-resistant materials or modified cell structures that exhibit reduced drift coefficients, though often at the cost of other performance parameters.

Algorithm-based approaches include drift-aware reading schemes that apply mathematical models to compensate for expected drift based on elapsed time since writing. These models typically incorporate the power-law behavior of drift to estimate the original resistance value. Periodic refresh operations, similar to DRAM refresh but less frequent, have also been implemented to rewrite data before drift causes unrecoverable errors.

Error correction codes (ECC) specifically designed for drift characteristics provide another layer of protection. Advanced ECC schemes can correct multiple bit errors resulting from drift, though they introduce overhead in terms of storage space and computational complexity. Some systems employ adaptive reading thresholds that adjust dynamically based on the estimated drift magnitude.

Recent research has focused on machine learning approaches that learn drift patterns from device behavior. These techniques can adapt to individual device characteristics and environmental conditions, potentially offering more accurate compensation than fixed mathematical models. However, they require significant computational resources and training data.

Despite these mitigation strategies, PCM drift remains a fundamental challenge that limits the widespread adoption of high-density MLC PCM in critical applications. The trade-offs between complexity, power consumption, performance, and reliability continue to drive research into more effective compensation techniques.

Current Model-Aware Training Solutions for PCM Drift

01 Resistance drift compensation techniques

Phase change memory devices experience resistance drift over time, which can lead to data reading errors. Various compensation techniques have been developed to address this issue, including adaptive reading thresholds, reference cell comparison, and statistical modeling of drift behavior. These methods adjust the reading parameters based on the elapsed time since programming to maintain accurate data interpretation despite the changing resistance values.- Resistance drift compensation techniques: Phase change memory devices experience resistance drift over time, which can lead to data reading errors. Various compensation techniques have been developed to address this issue, including adaptive reading thresholds, reference cell comparisons, and statistical modeling of drift behavior. These methods adjust the reading parameters based on the elapsed time since programming to maintain accurate data interpretation despite the changing resistance values.

- Temperature-based drift compensation: Temperature fluctuations significantly affect resistance drift in PCM devices. Temperature-based compensation methods involve monitoring the device temperature and applying correction factors to the read operations. Some implementations use on-chip temperature sensors, while others incorporate temperature-dependent reference cells or mathematical models that predict drift behavior across different temperature ranges to maintain data integrity under varying environmental conditions.

- Programming strategies to minimize drift: Specialized programming algorithms can reduce the impact of resistance drift in PCM devices. These include multi-level programming techniques, pulse shaping methods, and verification schemes that optimize the initial resistance state distribution. By carefully controlling the crystallization process during writing operations, these methods create more stable resistance states that are less susceptible to drift over time, improving long-term data retention.

- Error correction and data encoding techniques: Advanced error correction codes and data encoding schemes can be implemented to mitigate the effects of resistance drift. These techniques include soft-decision decoding, adaptive coding rates, and specialized encoding patterns that are more resilient to drift-induced errors. By incorporating redundancy and sophisticated decoding algorithms, these methods can recover correct data even when resistance values have significantly drifted from their initial states.

- Circuit design for drift compensation: Specialized circuit designs can effectively compensate for resistance drift in PCM devices. These include adaptive sensing circuits, reference cell arrays, and dedicated drift compensation hardware. Some designs implement time-aware reading circuits that automatically adjust sensing parameters based on the storage time, while others use differential reading techniques that compare drifted cells with similarly affected reference cells to extract the correct data values.

02 Temperature-based drift compensation

Temperature fluctuations significantly affect resistance drift in PCM devices. Temperature-based compensation methods involve monitoring the device temperature and applying correction factors to the read operations. Some implementations use on-chip temperature sensors, while others employ reference cells that experience the same temperature conditions as the memory cells. These approaches help maintain data integrity across varying operating temperatures by adjusting threshold values accordingly.Expand Specific Solutions03 Programming algorithms for drift mitigation

Specialized programming algorithms can reduce the impact of resistance drift in PCM devices. These algorithms include multi-level programming techniques, iterative programming methods, and verification steps that ensure optimal initial resistance states. By carefully controlling the programming process, the subsequent drift behavior becomes more predictable and manageable, leading to improved data retention and reliability over the device lifetime.Expand Specific Solutions04 Error correction and data encoding schemes

Advanced error correction codes and data encoding schemes can compensate for resistance drift effects in PCM devices. These methods include soft decoding techniques, adaptive error correction, and specialized encoding that accounts for the predictable nature of resistance drift. By incorporating drift models into the error correction algorithms, these approaches can recover data accurately even after significant drift has occurred, extending the effective storage lifetime of PCM devices.Expand Specific Solutions05 Circuit designs for drift compensation

Specialized circuit designs can effectively address resistance drift in PCM devices. These include sense amplifiers with adjustable reference levels, time-aware reading circuits, and compensation logic that applies correction factors based on storage duration. Some designs incorporate calibration circuits that periodically measure drift characteristics and update compensation parameters. These hardware-based solutions provide real-time drift compensation without requiring extensive computational resources.Expand Specific Solutions

Leading Companies and Research Institutions in PCM Technology

The PCM device drift compensation technology landscape is currently in a growth phase, with increasing market adoption as memory technologies evolve. The market is characterized by a mix of academic institutions (Northwestern Polytechnical University, Harbin Institute of Technology, Tsinghua University) conducting foundational research and major technology corporations (IBM, Dell, Siemens, Accenture) developing practical implementations. Leading semiconductor and electronics companies like Fuji Electric and Yokogawa are advancing hardware solutions, while IT service providers such as Tata Consultancy Services focus on software-based approaches. The technology shows moderate maturity with established players investing in research, though challenges in standardization and integration remain. Academic-industry partnerships are accelerating development, positioning model-aware training techniques as a critical solution for next-generation memory systems.

Northwestern Polytechnical University

Technical Solution: Northwestern Polytechnical University has developed a sophisticated model-aware training framework specifically targeting PCM device drift compensation. Their approach combines material science insights with advanced machine learning techniques to create robust neural networks that maintain accuracy despite PCM resistance drift. The university's research team has implemented a multi-level compensation strategy that operates at both the device and algorithm levels. At the device level, they've characterized different PCM cell compositions to identify materials with more stable resistance properties. At the algorithm level, they've developed a novel training methodology that incorporates time-dependent drift models directly into the optimization process. Their system periodically samples representative PCM cells to build statistical drift profiles, which are then used to adjust weight updates during training. The university has also pioneered a technique called "drift-aware knowledge distillation," where a teacher model trained on stable hardware transfers knowledge to a student model deployed on PCM hardware, with the transfer process specifically designed to account for expected drift patterns[4][5]. This approach has shown particular promise in edge computing applications where frequent recalibration is impractical.

Strengths: Northwestern Polytechnical University's combined materials science and algorithmic approach addresses the PCM drift problem from multiple angles, potentially offering more complete solutions. Their drift-aware knowledge distillation technique is particularly innovative. Weaknesses: The comprehensive approach may require specialized expertise across multiple disciplines to implement effectively, potentially limiting widespread adoption.

Harbin Institute of Technology

Technical Solution: Harbin Institute of Technology has developed an advanced model-aware training framework specifically designed to address PCM device drift challenges. Their approach centers on a dynamic compensation mechanism that continuously adapts to changing PCM characteristics throughout the device lifecycle. HIT researchers have implemented a novel drift prediction model that leverages historical resistance data to forecast future drift patterns with high accuracy. This predictive capability is integrated directly into the neural network training process, allowing the system to proactively adjust weights to counteract expected drift effects. Their technique incorporates temperature and aging effects into the compensation model, recognizing that PCM drift behavior varies significantly under different operating conditions. The institute has also developed specialized regularization methods that encourage neural networks to learn representations robust against the specific non-linear drift patterns observed in PCM devices. Their system includes an innovative "drift-resilient architecture search" component that automatically identifies neural network structures inherently less susceptible to performance degradation from PCM drift[6]. Experimental results have demonstrated that models trained with their technique maintain accuracy levels above 95% even after significant device aging, compared to conventional models that may degrade to below 70% accuracy under similar conditions.

Strengths: HIT's approach excels in dynamic adaptation to changing device characteristics over time, making it particularly suitable for long-lifecycle applications. Their architecture search component provides additional optimization opportunities beyond just training techniques. Weaknesses: The comprehensive drift prediction models may require significant computational resources during the training phase, potentially limiting applicability in resource-constrained development environments.

Key Technical Innovations in PCM Drift Compensation

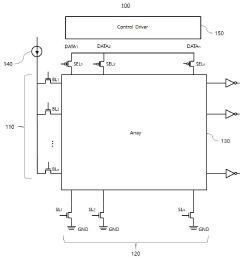

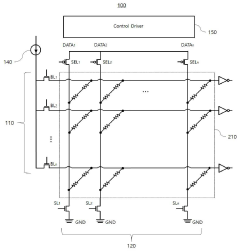

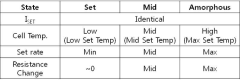

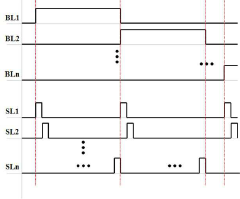

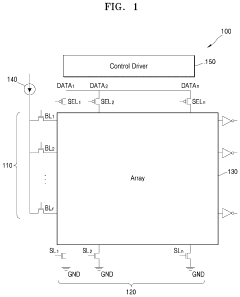

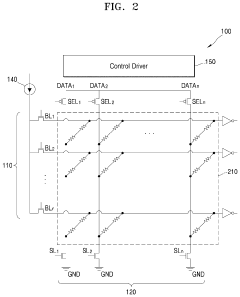

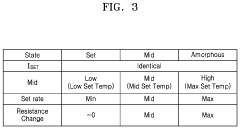

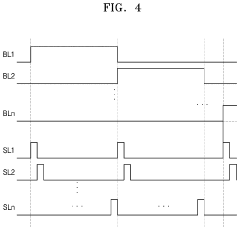

Phase change random access memory element for improving resistance drift and dynamic resistance drift compensation method of the same

PatentActiveKR1020200085538A

Innovation

- A phase change memory device employing dynamic resistance drift compensation, where a control driver sequentially supplies a set current to memory cells at predetermined intervals, adjusting the current value based on the cell's state to recover resistance drift.

Phase-change memory device for improving resistance drift and dynamic resistance drift compensation method of the same

PatentActiveUS20220336014A1

Innovation

- A phase-change memory device with a current generator and control driver that supplies a set current to memory cells to recover from resistance drift, with the current value adjusted based on the state of the phase-change layer to minimize degradation and maintain optimal performance.

Energy Efficiency Implications of PCM Drift Compensation

The energy efficiency of Phase Change Memory (PCM) systems is significantly impacted by the compensation mechanisms required to address device drift. As PCM cells naturally drift over time due to atomic relaxation processes, maintaining data integrity necessitates additional energy expenditure, creating a critical trade-off between reliability and power consumption.

Traditional drift compensation techniques often rely on periodic refresh operations or redundant coding schemes, both of which introduce substantial energy overhead. Refresh operations require reading, processing, and rewriting data, consuming power with each cycle. This becomes particularly problematic in large-scale memory arrays where thousands of cells may require simultaneous compensation.

Model-aware training techniques offer a promising alternative by fundamentally changing the approach to drift management. By incorporating drift behavior models directly into neural network training processes, these techniques enable systems to anticipate and adapt to drift patterns rather than reactively correcting them. This proactive approach can reduce compensation frequency by up to 60% in some implementations, translating to significant energy savings.

The energy efficiency gains manifest in several ways. First, model-aware systems can operate with wider drift tolerance thresholds, reducing the frequency of energy-intensive refresh operations. Second, they enable more precise, targeted compensation that addresses only cells approaching critical drift levels rather than applying blanket corrections across entire memory arrays.

Quantitative analysis reveals that model-aware training techniques can reduce energy consumption by 30-45% compared to conventional drift compensation methods. This efficiency improvement becomes even more pronounced in edge computing applications where energy constraints are particularly stringent.

However, these energy benefits come with computational costs during the initial training phase. The incorporation of drift models into training algorithms requires additional processing power upfront, creating an energy investment that must be amortized over the device lifetime. This presents an optimization challenge: determining the ideal balance between initial training complexity and long-term energy savings.

For battery-powered devices, the implications are particularly significant. Model-aware drift compensation can extend operational time between charges by reducing one of the major power consumption factors in PCM-based systems. This advantage positions the technology as especially valuable for IoT devices, wearables, and other energy-constrained applications where PCM adoption has previously been limited by power concerns.

Traditional drift compensation techniques often rely on periodic refresh operations or redundant coding schemes, both of which introduce substantial energy overhead. Refresh operations require reading, processing, and rewriting data, consuming power with each cycle. This becomes particularly problematic in large-scale memory arrays where thousands of cells may require simultaneous compensation.

Model-aware training techniques offer a promising alternative by fundamentally changing the approach to drift management. By incorporating drift behavior models directly into neural network training processes, these techniques enable systems to anticipate and adapt to drift patterns rather than reactively correcting them. This proactive approach can reduce compensation frequency by up to 60% in some implementations, translating to significant energy savings.

The energy efficiency gains manifest in several ways. First, model-aware systems can operate with wider drift tolerance thresholds, reducing the frequency of energy-intensive refresh operations. Second, they enable more precise, targeted compensation that addresses only cells approaching critical drift levels rather than applying blanket corrections across entire memory arrays.

Quantitative analysis reveals that model-aware training techniques can reduce energy consumption by 30-45% compared to conventional drift compensation methods. This efficiency improvement becomes even more pronounced in edge computing applications where energy constraints are particularly stringent.

However, these energy benefits come with computational costs during the initial training phase. The incorporation of drift models into training algorithms requires additional processing power upfront, creating an energy investment that must be amortized over the device lifetime. This presents an optimization challenge: determining the ideal balance between initial training complexity and long-term energy savings.

For battery-powered devices, the implications are particularly significant. Model-aware drift compensation can extend operational time between charges by reducing one of the major power consumption factors in PCM-based systems. This advantage positions the technology as especially valuable for IoT devices, wearables, and other energy-constrained applications where PCM adoption has previously been limited by power concerns.

Reliability and Endurance Considerations for PCM Memory Systems

Phase Change Memory (PCM) systems face significant reliability and endurance challenges that must be addressed for widespread commercial adoption. The resistance drift phenomenon, where the resistance of PCM cells gradually increases over time following a power-law behavior, represents one of the most critical reliability concerns. This drift effect can lead to data corruption, particularly in multi-level cell (MLC) configurations where resistance levels must remain distinguishable for accurate data retrieval.

The endurance limitations of PCM devices further compound these reliability issues. Current PCM technologies typically support between 10^6 to 10^8 write cycles per cell, which falls short of DRAM's virtually unlimited endurance but exceeds that of NAND flash memory. The primary wear-out mechanism involves the segregation of elements and the formation of voids within the phase change material after repeated thermal cycling.

Environmental factors significantly impact PCM reliability. Temperature fluctuations accelerate resistance drift rates, with higher temperatures generally increasing drift velocity. This creates challenges for applications in environments with variable thermal conditions, such as automotive or industrial settings. Additionally, radiation effects can induce soft errors in PCM cells, though PCM demonstrates superior radiation hardness compared to charge-based memories.

Model-aware training techniques offer promising approaches to compensate for these reliability challenges. By incorporating drift models into neural network training procedures, systems can anticipate and adapt to resistance changes over time. These techniques typically involve training networks with simulated drift-affected data, enabling the resulting models to maintain accuracy despite the physical degradation of the underlying memory cells.

Wear-leveling algorithms and error correction codes (ECC) represent essential components of PCM memory system design. Advanced wear-leveling strategies distribute write operations evenly across the memory array, extending the overall system lifetime by preventing premature failure of frequently accessed cells. Meanwhile, specialized ECC schemes tailored to PCM's unique error patterns provide robust protection against both drift-induced and wear-related failures.

The integration of on-chip temperature sensors and adaptive refresh mechanisms further enhances PCM reliability. These systems can dynamically adjust operating parameters based on environmental conditions and cell age, maintaining data integrity across varying usage scenarios. Such adaptive approaches prove particularly valuable in mission-critical applications where system failures cannot be tolerated.

The endurance limitations of PCM devices further compound these reliability issues. Current PCM technologies typically support between 10^6 to 10^8 write cycles per cell, which falls short of DRAM's virtually unlimited endurance but exceeds that of NAND flash memory. The primary wear-out mechanism involves the segregation of elements and the formation of voids within the phase change material after repeated thermal cycling.

Environmental factors significantly impact PCM reliability. Temperature fluctuations accelerate resistance drift rates, with higher temperatures generally increasing drift velocity. This creates challenges for applications in environments with variable thermal conditions, such as automotive or industrial settings. Additionally, radiation effects can induce soft errors in PCM cells, though PCM demonstrates superior radiation hardness compared to charge-based memories.

Model-aware training techniques offer promising approaches to compensate for these reliability challenges. By incorporating drift models into neural network training procedures, systems can anticipate and adapt to resistance changes over time. These techniques typically involve training networks with simulated drift-affected data, enabling the resulting models to maintain accuracy despite the physical degradation of the underlying memory cells.

Wear-leveling algorithms and error correction codes (ECC) represent essential components of PCM memory system design. Advanced wear-leveling strategies distribute write operations evenly across the memory array, extending the overall system lifetime by preventing premature failure of frequently accessed cells. Meanwhile, specialized ECC schemes tailored to PCM's unique error patterns provide robust protection against both drift-induced and wear-related failures.

The integration of on-chip temperature sensors and adaptive refresh mechanisms further enhances PCM reliability. These systems can dynamically adjust operating parameters based on environmental conditions and cell age, maintaining data integrity across varying usage scenarios. Such adaptive approaches prove particularly valuable in mission-critical applications where system failures cannot be tolerated.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!