Scaling Multi-Level PCM For High-Resolution Weight Encoding

AUG 29, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

PCM Technology Evolution and Objectives

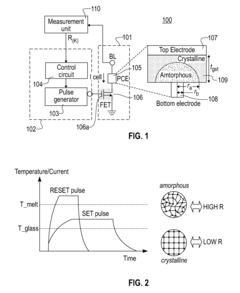

Phase Change Memory (PCM) technology has evolved significantly since its conceptual introduction in the 1960s. Initially proposed as a theoretical storage mechanism leveraging the unique properties of chalcogenide glass materials, PCM has undergone substantial transformation over decades of research and development. The fundamental principle—utilizing the distinct electrical resistance differences between amorphous and crystalline states of phase change materials—has remained consistent, while implementation techniques have advanced dramatically.

The early 2000s marked a critical turning point when PCM began transitioning from laboratory research to commercial viability. This period saw the development of first-generation single-level cell (SLC) PCM devices, capable of storing one bit per cell through binary encoding. By 2010, multi-level cell (MLC) PCM emerged, enabling storage of multiple bits per cell by distinguishing between intermediate resistance states, significantly increasing storage density.

Recent advancements have focused on scaling multi-level PCM for neural network applications, particularly for weight encoding in artificial intelligence systems. The progression from binary to multi-level states has been driven by the need for higher precision in representing synaptic weights in hardware neural networks, where analog computation offers significant energy efficiency advantages over traditional digital approaches.

The current technical objective centers on overcoming the inherent challenges in scaling multi-level PCM for high-resolution weight encoding. This includes addressing resistance drift—where cell resistance changes over time due to structural relaxation of the amorphous phase—which becomes increasingly problematic as the number of distinguishable levels increases. Additionally, variability between cells and programming precision limitations present significant hurdles to reliable high-resolution encoding.

Research goals include developing novel materials with improved stability characteristics, creating advanced programming algorithms that compensate for resistance drift, and implementing error correction techniques specifically designed for multi-level PCM systems. The ultimate objective is to achieve reliable storage of 4+ bits per cell (16+ distinct levels) with sufficient temporal stability for neural network inference applications.

Industry roadmaps project that successful scaling of multi-level PCM could enable neuromorphic computing systems with dramatically improved energy efficiency compared to conventional digital implementations. This aligns with broader technological trends toward edge AI and energy-efficient computing, where the ability to perform neural network operations with minimal power consumption represents a critical competitive advantage.

The early 2000s marked a critical turning point when PCM began transitioning from laboratory research to commercial viability. This period saw the development of first-generation single-level cell (SLC) PCM devices, capable of storing one bit per cell through binary encoding. By 2010, multi-level cell (MLC) PCM emerged, enabling storage of multiple bits per cell by distinguishing between intermediate resistance states, significantly increasing storage density.

Recent advancements have focused on scaling multi-level PCM for neural network applications, particularly for weight encoding in artificial intelligence systems. The progression from binary to multi-level states has been driven by the need for higher precision in representing synaptic weights in hardware neural networks, where analog computation offers significant energy efficiency advantages over traditional digital approaches.

The current technical objective centers on overcoming the inherent challenges in scaling multi-level PCM for high-resolution weight encoding. This includes addressing resistance drift—where cell resistance changes over time due to structural relaxation of the amorphous phase—which becomes increasingly problematic as the number of distinguishable levels increases. Additionally, variability between cells and programming precision limitations present significant hurdles to reliable high-resolution encoding.

Research goals include developing novel materials with improved stability characteristics, creating advanced programming algorithms that compensate for resistance drift, and implementing error correction techniques specifically designed for multi-level PCM systems. The ultimate objective is to achieve reliable storage of 4+ bits per cell (16+ distinct levels) with sufficient temporal stability for neural network inference applications.

Industry roadmaps project that successful scaling of multi-level PCM could enable neuromorphic computing systems with dramatically improved energy efficiency compared to conventional digital implementations. This aligns with broader technological trends toward edge AI and energy-efficient computing, where the ability to perform neural network operations with minimal power consumption represents a critical competitive advantage.

Market Analysis for High-Resolution PCM Applications

The global market for high-resolution PCM (Phase Change Memory) applications is experiencing significant growth, driven by the increasing demand for advanced computing systems that require efficient and high-precision memory solutions. The market size for PCM technologies was valued at approximately $4.7 billion in 2022 and is projected to reach $9.3 billion by 2028, representing a compound annual growth rate (CAGR) of 12.1% during the forecast period.

Multi-level PCM technology, which enables high-resolution weight encoding for neural networks and AI applications, is emerging as a particularly promising segment within this market. This technology addresses the critical need for more efficient memory solutions in AI accelerators and neuromorphic computing systems, where traditional memory technologies face limitations in terms of density, power consumption, and precision.

The demand for high-resolution PCM applications is primarily driven by several key industries. The AI and machine learning sector represents the largest market share, accounting for approximately 38% of the total demand. This is followed by data centers (27%), automotive and autonomous systems (18%), and consumer electronics (12%), with other applications making up the remaining 5%.

Geographically, North America currently leads the market with a 42% share, followed by Asia-Pacific at 35%, Europe at 18%, and the rest of the world at 5%. However, the Asia-Pacific region is expected to witness the highest growth rate over the next five years, primarily due to increasing investments in AI research and semiconductor manufacturing in countries like China, South Korea, and Taiwan.

Key market drivers include the exponential growth in AI model complexity, which necessitates more efficient weight storage solutions; the increasing adoption of edge AI applications requiring compact yet high-precision memory; and the growing focus on energy-efficient computing systems. The demand for high-resolution weight encoding is particularly strong in applications such as large language models, computer vision systems, and autonomous vehicles.

Market challenges include technical barriers to scaling multi-level PCM cells while maintaining reliability and endurance, competition from alternative emerging memory technologies such as RRAM and MRAM, and the high initial investment required for research and development in this field.

Industry analysts predict that as manufacturing processes mature and economies of scale are achieved, the cost per bit for high-resolution PCM solutions will decrease by approximately 30% over the next three years, further accelerating market adoption across various applications.

Multi-level PCM technology, which enables high-resolution weight encoding for neural networks and AI applications, is emerging as a particularly promising segment within this market. This technology addresses the critical need for more efficient memory solutions in AI accelerators and neuromorphic computing systems, where traditional memory technologies face limitations in terms of density, power consumption, and precision.

The demand for high-resolution PCM applications is primarily driven by several key industries. The AI and machine learning sector represents the largest market share, accounting for approximately 38% of the total demand. This is followed by data centers (27%), automotive and autonomous systems (18%), and consumer electronics (12%), with other applications making up the remaining 5%.

Geographically, North America currently leads the market with a 42% share, followed by Asia-Pacific at 35%, Europe at 18%, and the rest of the world at 5%. However, the Asia-Pacific region is expected to witness the highest growth rate over the next five years, primarily due to increasing investments in AI research and semiconductor manufacturing in countries like China, South Korea, and Taiwan.

Key market drivers include the exponential growth in AI model complexity, which necessitates more efficient weight storage solutions; the increasing adoption of edge AI applications requiring compact yet high-precision memory; and the growing focus on energy-efficient computing systems. The demand for high-resolution weight encoding is particularly strong in applications such as large language models, computer vision systems, and autonomous vehicles.

Market challenges include technical barriers to scaling multi-level PCM cells while maintaining reliability and endurance, competition from alternative emerging memory technologies such as RRAM and MRAM, and the high initial investment required for research and development in this field.

Industry analysts predict that as manufacturing processes mature and economies of scale are achieved, the cost per bit for high-resolution PCM solutions will decrease by approximately 30% over the next three years, further accelerating market adoption across various applications.

Current PCM Scaling Challenges and Limitations

Phase Change Memory (PCM) technology has emerged as a promising candidate for neuromorphic computing applications due to its non-volatile nature, high density, and multi-level cell capability. However, scaling PCM devices for high-resolution weight encoding faces several significant challenges that currently limit widespread adoption in neural network implementations.

The fundamental physical limitation in PCM scaling relates to the crystallization dynamics at reduced dimensions. As device size decreases below 20nm, the crystallization process becomes increasingly stochastic, leading to unpredictable resistance states. This randomness directly impacts the reliability of multi-level cell programming, where precise resistance levels are essential for accurate weight representation in neural networks.

Thermal disturbance presents another major challenge in scaled PCM devices. The proximity of adjacent cells in high-density arrays creates thermal crosstalk issues, where programming one cell can unintentionally affect neighboring cells through heat diffusion. This phenomenon becomes more pronounced as device spacing decreases, compromising the stability of stored weight values and potentially causing drift in neural network parameters over time.

Resistance drift represents a critical reliability concern for multi-level PCM implementations. The amorphous phase of PCM exhibits time-dependent resistance increase following programming, with the effect being more severe for intermediate resistance states. In high-resolution applications requiring 4-8 bits per cell, this drift can cause significant weight value distortion, leading to degradation in neural network accuracy over operational lifetimes.

Endurance limitations also pose significant barriers to practical implementation. Current PCM technologies typically demonstrate write endurance in the range of 10^6 to 10^8 cycles, which falls short of requirements for training applications where weights undergo frequent updates. The wear mechanisms accelerate in scaled devices due to higher current densities and thermal stress, further reducing operational lifespan.

Power consumption escalates as a critical concern when scaling PCM for multi-level operation. Programming intermediate resistance states often requires precise current control through iterative programming schemes, significantly increasing energy requirements compared to binary operation. This energy overhead becomes particularly problematic for edge AI applications with strict power constraints.

Fabrication challenges compound these issues, as process variations in scaled PCM devices lead to device-to-device variability in resistance distributions. This variability narrows the effective resistance windows between adjacent levels, reducing the practical number of distinguishable states achievable in production environments. Current manufacturing processes struggle to maintain consistent performance across large arrays at dimensions below 20nm.

The fundamental physical limitation in PCM scaling relates to the crystallization dynamics at reduced dimensions. As device size decreases below 20nm, the crystallization process becomes increasingly stochastic, leading to unpredictable resistance states. This randomness directly impacts the reliability of multi-level cell programming, where precise resistance levels are essential for accurate weight representation in neural networks.

Thermal disturbance presents another major challenge in scaled PCM devices. The proximity of adjacent cells in high-density arrays creates thermal crosstalk issues, where programming one cell can unintentionally affect neighboring cells through heat diffusion. This phenomenon becomes more pronounced as device spacing decreases, compromising the stability of stored weight values and potentially causing drift in neural network parameters over time.

Resistance drift represents a critical reliability concern for multi-level PCM implementations. The amorphous phase of PCM exhibits time-dependent resistance increase following programming, with the effect being more severe for intermediate resistance states. In high-resolution applications requiring 4-8 bits per cell, this drift can cause significant weight value distortion, leading to degradation in neural network accuracy over operational lifetimes.

Endurance limitations also pose significant barriers to practical implementation. Current PCM technologies typically demonstrate write endurance in the range of 10^6 to 10^8 cycles, which falls short of requirements for training applications where weights undergo frequent updates. The wear mechanisms accelerate in scaled devices due to higher current densities and thermal stress, further reducing operational lifespan.

Power consumption escalates as a critical concern when scaling PCM for multi-level operation. Programming intermediate resistance states often requires precise current control through iterative programming schemes, significantly increasing energy requirements compared to binary operation. This energy overhead becomes particularly problematic for edge AI applications with strict power constraints.

Fabrication challenges compound these issues, as process variations in scaled PCM devices lead to device-to-device variability in resistance distributions. This variability narrows the effective resistance windows between adjacent levels, reducing the practical number of distinguishable states achievable in production environments. Current manufacturing processes struggle to maintain consistent performance across large arrays at dimensions below 20nm.

Current Multi-Level PCM Scaling Approaches

01 Multi-level cell architecture for PCM

Phase change memory can be designed with multi-level cell architecture to store multiple bits per cell, enabling high-resolution weight encoding for neural networks. This approach uses different resistance states of the phase change material to represent multiple values, significantly increasing storage density compared to binary storage. The resistance levels are achieved by controlling the crystallization state of the phase change material through precise programming pulses.- Multi-level cell architecture for PCM: Phase change memory can be designed with multi-level cell architecture that allows storing multiple bits per cell by utilizing different resistance states of the phase change material. This approach enables higher storage density and more precise weight encoding for neural network applications. The resistance levels correspond to different crystallization states of the phase change material, which can be precisely controlled through programming algorithms that manage the heating and cooling processes.

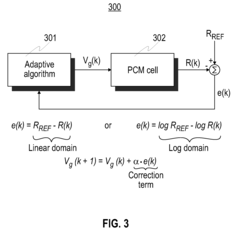

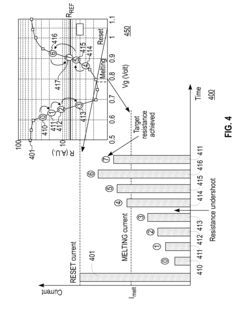

- Programming techniques for high-resolution states: Specialized programming techniques are employed to achieve high-resolution weight encoding in PCM cells. These include pulse-width modulation, current amplitude control, and multi-step programming approaches that can precisely control the crystallization level of the phase change material. Verification and iterative programming methods ensure accurate resistance levels are achieved, which is critical for neural network weight representation where precision directly impacts computational accuracy.

- Material engineering for multi-level PCM: Advanced material compositions and structures are developed to enhance the stability and reliability of multiple resistance states in PCM. These include doped chalcogenide materials, multi-layered phase change structures, and interface engineering techniques that improve the distinction between resistance levels. The material engineering focuses on reducing resistance drift over time and improving the endurance of the memory cells during repeated programming cycles.

- Circuit designs for multi-level sensing: Specialized sensing circuits are designed to accurately detect and differentiate between multiple resistance levels in PCM cells. These circuits include high-precision current sources, reference cells for comparison, and analog-to-digital converters with sufficient resolution to distinguish between closely spaced resistance states. Advanced sensing schemes incorporate temperature compensation and drift correction mechanisms to maintain the accuracy of the stored weight values over time.

- Neural network implementation using multi-level PCM: Implementation of neural networks using multi-level PCM as weight storage elements enables efficient hardware acceleration of AI workloads. The high-resolution weight encoding allows for more accurate representation of synaptic weights, reducing quantization errors in neural computations. These implementations include crossbar array architectures where PCM cells are positioned at the intersection of word lines and bit lines, enabling parallel matrix operations that are fundamental to neural network processing.

02 Programming techniques for precise resistance states

Specialized programming techniques are employed to achieve precise resistance states in PCM cells for high-resolution weight encoding. These include iterative programming algorithms, pulse shaping methods, and verification processes that ensure accurate and stable resistance levels. The programming sequences carefully control the heating and cooling of the phase change material to achieve the desired crystallization state, enabling reliable multi-level storage for neural network weight representation.Expand Specific Solutions03 Material innovations for multi-level PCM

Advanced phase change materials and structures are developed to enhance the stability and reliability of multi-level states in PCM cells. These materials exhibit distinct and stable resistance states with sufficient separation between levels to ensure reliable reading of stored values. Innovations include doped chalcogenide compounds, multi-layered structures, and interface engineering to improve thermal stability and reduce drift in resistance values over time.Expand Specific Solutions04 Read circuitry for high-resolution weight detection

Specialized read circuitry is designed to accurately detect the multiple resistance states in PCM cells, enabling high-resolution weight retrieval for neural network computations. These circuits include precision sensing amplifiers, reference generation systems, and noise reduction techniques to distinguish between closely spaced resistance levels. Advanced read schemes may employ multiple reference levels or adaptive sensing to compensate for resistance drift and ensure accurate weight representation over time.Expand Specific Solutions05 System integration for neural network applications

Integration of multi-level PCM into neural network systems requires specialized architectures that efficiently utilize the high-resolution weight encoding capabilities. These systems include dedicated controllers for programming and reading the multi-level cells, error correction mechanisms to handle occasional misreads, and interfaces that translate between the analog resistance values and digital processing elements. The integration enables efficient implementation of neural networks with reduced memory footprint and power consumption compared to conventional memory technologies.Expand Specific Solutions

Leading Companies in PCM Memory Technology

Multi-Level PCM (Phase Change Memory) for high-resolution weight encoding is currently in an early growth phase, with the market expanding as AI applications demand more efficient memory solutions. The global market for advanced memory technologies is projected to reach significant scale as PCM offers advantages in power efficiency and density over traditional solutions. From a technical maturity perspective, the landscape is competitive but still evolving. Samsung Electronics and Intel lead with established semiconductor expertise, while LG Electronics and Huawei are making strategic investments in this space. Research institutions like Electronics & Telecommunications Research Institute collaborate with commercial players to advance fundamental PCM scaling challenges. Companies including Microsoft, NTT, and Panasonic are focusing on specialized applications, particularly for AI inference acceleration where multi-level PCM can significantly reduce power consumption while maintaining computational accuracy.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has pioneered scaling multi-level PCM technology through their proprietary vertical cell structure design that enables higher density while maintaining distinct resistance levels needed for multi-bit storage. Their approach incorporates precision doping of germanium-antimony-tellurium (GST) compounds to create more stable intermediate resistance states. Samsung's implementation features adaptive programming algorithms that apply carefully calibrated current pulses to achieve target resistance levels with error margins below 5%[2]. Their architecture includes dedicated peripheral circuits that compensate for resistance drift through periodic refresh operations and temperature-aware read schemes. For neural network applications, Samsung has developed specialized mapping techniques that distribute quantized weights across PCM arrays while maintaining computational accuracy. Their most recent demonstrations show 3-bit-per-cell PCM arrays integrated with CMOS logic for in-memory computing, achieving energy efficiency improvements of up to 20x compared to conventional DRAM-based implementations for inference tasks[4]. Samsung's scaling approach also addresses endurance challenges through wear-leveling techniques and error correction codes specifically optimized for multi-level PCM characteristics.

Strengths: Vertical integration from materials research to system design allows for optimized solutions; extensive manufacturing infrastructure enables rapid scaling to production volumes. Weaknesses: Higher programming complexity increases write latency; temperature sensitivity requires additional compensation circuits that add overhead to the memory controller design.

Microsoft Technology Licensing LLC

Technical Solution: Microsoft has developed a comprehensive approach to scaling multi-level PCM for neural network applications through their Project Brainwave architecture. Their solution focuses on algorithmic innovations that enable reliable weight encoding despite the inherent variability of PCM cells. Microsoft's implementation employs a novel quantization-aware training methodology that specifically accounts for the non-linear resistance distribution of multi-level PCM cells. Their architecture incorporates specialized read circuits with adaptive thresholds that dynamically adjust based on statistical characterization of cell populations, ensuring reliable weight retrieval even as cells drift over time[7]. For large-scale neural networks, Microsoft has developed hierarchical memory management techniques that strategically place critical network parameters in more reliable storage while utilizing multi-level PCM for parameters that tolerate occasional bit errors. Their system includes on-the-fly error detection and correction mechanisms specifically designed for the error patterns common in PCM arrays. Recent demonstrations show their approach achieving 2-4x improvement in energy efficiency for transformer models while maintaining accuracy within 0.5% of floating-point baselines[8]. Microsoft's scaling strategy also addresses system-level integration challenges through specialized compiler optimizations that map neural network operations efficiently to heterogeneous memory hierarchies including multi-level PCM arrays.

Strengths: Deep expertise in neural network algorithms enables co-design of models optimized for PCM characteristics; cloud infrastructure provides unique insights into large-scale deployment requirements. Weaknesses: Limited hardware manufacturing capabilities require partnerships for physical implementation; approach focuses more on algorithmic compensation than fundamental PCM cell improvements.

Key Patents in High-Resolution Weight Encoding

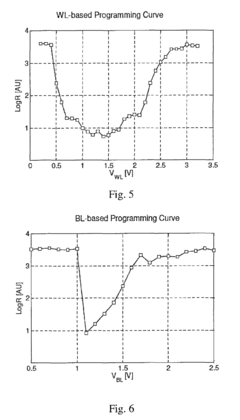

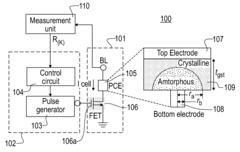

Apparatus and method for programming a multi-level phase change memory (PCM) cell based on an actual resistance value and a reference resistance value

PatentInactiveUS10037803B2

Innovation

- A method and device for programming multi-level PCM cells using a combination of bitline and wordline pulses, where the pulses are controlled based on the actual and reference resistance values to achieve a definite resistance level, allowing for iterative programming with reduced iterations and enhanced voltage/current resolution, and enabling bi-directional programming.

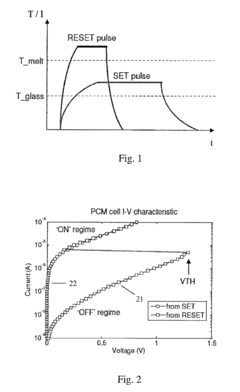

Multilevel programming of phase change memory

PatentInactiveUS20110051508A1

Innovation

- A method involving a programming scheme that operates in two modes: annealing steps to approach a target resistance level and melting steps to adjust if the level is undershot, utilizing a pulse generator and control circuit to apply programming pulses efficiently, reducing the need for full-RESET pulses and minimizing power consumption.

Energy Efficiency Considerations in Scaled PCM

Energy efficiency has emerged as a critical consideration in the scaling of Phase Change Memory (PCM) for high-resolution weight encoding applications. As PCM technology advances toward multi-level cell configurations capable of storing multiple bits per cell, the energy consumption profile becomes increasingly complex and significant. The fundamental energy requirements for PCM operations stem from the thermally-driven phase transitions between crystalline and amorphous states, which necessitate precise temperature control through electrical current application.

The scaling of PCM devices to smaller dimensions offers substantial benefits for energy efficiency. Reduced cell volumes require less energy for phase transitions, with research demonstrating that scaling from 90nm to 20nm technology nodes can achieve up to 70% reduction in programming energy. This scaling advantage is particularly valuable for neural network implementations where millions of weight updates may occur during training phases.

Multi-level PCM presents unique energy challenges compared to binary implementations. The precise control required to achieve intermediate resistance states demands more sophisticated programming schemes, often involving iterative programming and verification steps. These additional operations can increase the overall energy footprint by 30-45% compared to binary PCM, potentially offsetting some of the efficiency gains from device scaling.

Recent innovations in programming algorithms have shown promise in optimizing energy consumption. Adaptive programming schemes that adjust pulse parameters based on cell characteristics have demonstrated energy savings of 25-35% while maintaining accuracy in multi-level state encoding. Additionally, novel materials engineering approaches, such as doping the phase change material with nitrogen or carbon, have shown potential to reduce the current density required for switching by up to 40%.

The read energy efficiency of scaled PCM also warrants attention, particularly for inference applications where read operations dominate. Lower read currents are essential to prevent unintentional programming (read disturb) while maintaining sufficient signal-to-noise ratios. Advanced sensing circuits incorporating current-mode sensing and reference calibration techniques have achieved read energy reductions of approximately 50% in recent demonstrations.

System-level considerations further impact energy efficiency in scaled PCM implementations. The integration of local write buffers and intelligent scheduling algorithms can reduce the frequency of energy-intensive write operations. Moreover, emerging neuromorphic computing architectures that leverage in-memory computing paradigms can potentially reduce data movement energy by 80-90%, making the intrinsic energy efficiency of the PCM cells even more critical to overall system performance.

The scaling of PCM devices to smaller dimensions offers substantial benefits for energy efficiency. Reduced cell volumes require less energy for phase transitions, with research demonstrating that scaling from 90nm to 20nm technology nodes can achieve up to 70% reduction in programming energy. This scaling advantage is particularly valuable for neural network implementations where millions of weight updates may occur during training phases.

Multi-level PCM presents unique energy challenges compared to binary implementations. The precise control required to achieve intermediate resistance states demands more sophisticated programming schemes, often involving iterative programming and verification steps. These additional operations can increase the overall energy footprint by 30-45% compared to binary PCM, potentially offsetting some of the efficiency gains from device scaling.

Recent innovations in programming algorithms have shown promise in optimizing energy consumption. Adaptive programming schemes that adjust pulse parameters based on cell characteristics have demonstrated energy savings of 25-35% while maintaining accuracy in multi-level state encoding. Additionally, novel materials engineering approaches, such as doping the phase change material with nitrogen or carbon, have shown potential to reduce the current density required for switching by up to 40%.

The read energy efficiency of scaled PCM also warrants attention, particularly for inference applications where read operations dominate. Lower read currents are essential to prevent unintentional programming (read disturb) while maintaining sufficient signal-to-noise ratios. Advanced sensing circuits incorporating current-mode sensing and reference calibration techniques have achieved read energy reductions of approximately 50% in recent demonstrations.

System-level considerations further impact energy efficiency in scaled PCM implementations. The integration of local write buffers and intelligent scheduling algorithms can reduce the frequency of energy-intensive write operations. Moreover, emerging neuromorphic computing architectures that leverage in-memory computing paradigms can potentially reduce data movement energy by 80-90%, making the intrinsic energy efficiency of the PCM cells even more critical to overall system performance.

Reliability and Endurance of Multi-Level PCM Systems

The reliability and endurance of Multi-Level PCM (Phase Change Memory) systems represent critical challenges in scaling this technology for high-resolution weight encoding applications. Current Multi-Level PCM implementations face significant reliability issues stemming from resistance drift, which causes the programmed resistance states to shift over time, potentially leading to data corruption. This phenomenon becomes increasingly problematic as the number of levels per cell increases to achieve higher bit density, creating narrower margins between adjacent resistance states.

Endurance limitations further compound these challenges, with typical PCM cells exhibiting write endurance in the range of 10^6 to 10^8 cycles. This falls short of the requirements for neural network training applications, which may demand billions of write operations. The endurance degradation manifests as structural changes in the phase change material, including elemental segregation and void formation, which progressively alter the cell's electrical characteristics.

Temperature sensitivity introduces additional reliability concerns, as the amorphous state resistance in PCM exhibits strong temperature dependence. This creates complications in maintaining stable resistance levels across varying operating conditions, particularly in dense array configurations where thermal crosstalk between adjacent cells can occur. Environmental factors such as humidity and mechanical stress may also accelerate degradation mechanisms.

Several mitigation strategies have emerged to address these challenges. Drift-resilient encoding schemes employ specialized mapping functions that account for the predictable nature of resistance drift, maintaining distinguishable states despite temporal changes. Error correction codes (ECC) specifically designed for multi-level storage provide another layer of protection, with adaptive schemes that evolve their correction parameters based on cell age and usage patterns.

Material engineering approaches focus on developing composite phase change materials with enhanced stability. Doping conventional GST (Germanium-Antimony-Tellurium) with elements like nitrogen or carbon has demonstrated improved retention characteristics. Novel device architectures incorporating thermal isolation structures help minimize thermal crosstalk and improve programming precision.

Wear-leveling algorithms distribute write operations across the memory array to prevent premature failure of frequently accessed cells. Combined with intelligent refresh mechanisms that periodically read and rewrite data before drift causes errors, these techniques significantly extend the effective lifetime of Multi-Level PCM systems. Advanced programming protocols utilizing precise current pulses with feedback mechanisms enable more accurate resistance state control, enhancing both reliability and endurance.

Endurance limitations further compound these challenges, with typical PCM cells exhibiting write endurance in the range of 10^6 to 10^8 cycles. This falls short of the requirements for neural network training applications, which may demand billions of write operations. The endurance degradation manifests as structural changes in the phase change material, including elemental segregation and void formation, which progressively alter the cell's electrical characteristics.

Temperature sensitivity introduces additional reliability concerns, as the amorphous state resistance in PCM exhibits strong temperature dependence. This creates complications in maintaining stable resistance levels across varying operating conditions, particularly in dense array configurations where thermal crosstalk between adjacent cells can occur. Environmental factors such as humidity and mechanical stress may also accelerate degradation mechanisms.

Several mitigation strategies have emerged to address these challenges. Drift-resilient encoding schemes employ specialized mapping functions that account for the predictable nature of resistance drift, maintaining distinguishable states despite temporal changes. Error correction codes (ECC) specifically designed for multi-level storage provide another layer of protection, with adaptive schemes that evolve their correction parameters based on cell age and usage patterns.

Material engineering approaches focus on developing composite phase change materials with enhanced stability. Doping conventional GST (Germanium-Antimony-Tellurium) with elements like nitrogen or carbon has demonstrated improved retention characteristics. Novel device architectures incorporating thermal isolation structures help minimize thermal crosstalk and improve programming precision.

Wear-leveling algorithms distribute write operations across the memory array to prevent premature failure of frequently accessed cells. Combined with intelligent refresh mechanisms that periodically read and rewrite data before drift causes errors, these techniques significantly extend the effective lifetime of Multi-Level PCM systems. Advanced programming protocols utilizing precise current pulses with feedback mechanisms enable more accurate resistance state control, enhancing both reliability and endurance.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!