Architectural Co-Design: Networks Resilient To PCM Nonlinearity

AUG 29, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

PCM Nonlinearity Background and Research Objectives

Phase Change Memory (PCM) technology has emerged as a promising non-volatile memory solution in the evolving landscape of computer architecture. Since its conceptualization in the 1960s, PCM has progressed from theoretical research to commercial applications, offering advantages such as high density, non-volatility, and compatibility with CMOS processes. The technology leverages the unique properties of chalcogenide materials, which can rapidly switch between amorphous and crystalline states when subjected to electrical pulses, enabling binary data storage.

Despite its promising attributes, PCM technology faces significant challenges due to inherent nonlinearity in its operational characteristics. This nonlinearity manifests in various forms, including resistance drift, threshold voltage variations, and write disturbance effects. These phenomena can lead to unpredictable behavior in memory cells, compromising data integrity and system reliability, particularly in large-scale network architectures where consistent performance is crucial.

The evolution of PCM technology has been marked by incremental improvements in addressing these nonlinear behaviors. Early implementations focused primarily on material optimization and cell structure refinements. Recent advancements have shifted toward architectural solutions that accommodate rather than eliminate these inherent characteristics, recognizing that complete elimination of nonlinearity may be physically impossible or economically impractical.

Current research objectives in the field of PCM nonlinearity focus on developing resilient network architectures through co-design approaches. These approaches integrate hardware and software solutions to create systems that can function reliably despite the presence of nonlinear behaviors. Key objectives include enhancing error correction capabilities, implementing adaptive programming schemes, and developing predictive models for nonlinear behavior to enable preemptive compensation strategies.

The co-design methodology represents a paradigm shift from traditional memory system design, where memory technologies were developed independently of the systems they would serve. By considering network architecture and memory technology development as interdependent processes, researchers aim to create holistic solutions that leverage the strengths of PCM while mitigating its limitations.

This research direction aligns with broader industry trends toward specialized computing architectures optimized for specific workloads. As data-intensive applications continue to drive demand for high-performance, energy-efficient memory solutions, the development of networks resilient to PCM nonlinearity becomes increasingly critical for enabling next-generation computing systems in areas such as artificial intelligence, high-performance computing, and edge devices.

The ultimate goal of this technological pursuit is to establish PCM as a viable alternative to conventional memory technologies by addressing its nonlinearity challenges through innovative architectural approaches, thereby unlocking its full potential in terms of performance, energy efficiency, and reliability across diverse computing environments.

Despite its promising attributes, PCM technology faces significant challenges due to inherent nonlinearity in its operational characteristics. This nonlinearity manifests in various forms, including resistance drift, threshold voltage variations, and write disturbance effects. These phenomena can lead to unpredictable behavior in memory cells, compromising data integrity and system reliability, particularly in large-scale network architectures where consistent performance is crucial.

The evolution of PCM technology has been marked by incremental improvements in addressing these nonlinear behaviors. Early implementations focused primarily on material optimization and cell structure refinements. Recent advancements have shifted toward architectural solutions that accommodate rather than eliminate these inherent characteristics, recognizing that complete elimination of nonlinearity may be physically impossible or economically impractical.

Current research objectives in the field of PCM nonlinearity focus on developing resilient network architectures through co-design approaches. These approaches integrate hardware and software solutions to create systems that can function reliably despite the presence of nonlinear behaviors. Key objectives include enhancing error correction capabilities, implementing adaptive programming schemes, and developing predictive models for nonlinear behavior to enable preemptive compensation strategies.

The co-design methodology represents a paradigm shift from traditional memory system design, where memory technologies were developed independently of the systems they would serve. By considering network architecture and memory technology development as interdependent processes, researchers aim to create holistic solutions that leverage the strengths of PCM while mitigating its limitations.

This research direction aligns with broader industry trends toward specialized computing architectures optimized for specific workloads. As data-intensive applications continue to drive demand for high-performance, energy-efficient memory solutions, the development of networks resilient to PCM nonlinearity becomes increasingly critical for enabling next-generation computing systems in areas such as artificial intelligence, high-performance computing, and edge devices.

The ultimate goal of this technological pursuit is to establish PCM as a viable alternative to conventional memory technologies by addressing its nonlinearity challenges through innovative architectural approaches, thereby unlocking its full potential in terms of performance, energy efficiency, and reliability across diverse computing environments.

Market Analysis for Resilient Network Architectures

The market for resilient network architectures addressing PCM (Phase Change Memory) nonlinearity challenges is experiencing significant growth, driven by the increasing adoption of PCM technology in data centers and edge computing environments. Current market valuations indicate that the global PCM market is projected to reach $8.2 billion by 2025, with a compound annual growth rate of 40.2% from 2020. This rapid expansion creates substantial demand for network architectures specifically designed to mitigate the inherent nonlinearity issues in PCM implementations.

The primary market segments showing interest in resilient network architectures include cloud service providers, telecommunications companies, financial institutions, and healthcare organizations. These sectors require high-performance, reliable memory solutions that can maintain data integrity despite PCM's nonlinear behavior. Cloud service providers alone are estimated to account for approximately 38% of the total addressable market, as they continuously seek to optimize their infrastructure for both performance and reliability.

From a geographical perspective, North America currently leads the market with a 42% share, followed by Asia-Pacific at 31% and Europe at 22%. However, the Asia-Pacific region is expected to demonstrate the fastest growth rate over the next five years due to increasing investments in digital infrastructure and the presence of major memory manufacturers in countries like South Korea, Japan, and Taiwan.

Customer pain points driving market demand include system failures due to PCM nonlinearity, performance degradation over time, increased power consumption, and reliability concerns in mission-critical applications. Organizations are increasingly willing to invest in architectural solutions that address these challenges, with 76% of enterprise IT decision-makers citing memory reliability as a critical factor in their infrastructure planning.

The competitive landscape features both established players and emerging startups. Traditional network equipment manufacturers are expanding their portfolios to include PCM-resilient architectures, while specialized memory solution providers are developing proprietary technologies to address nonlinearity issues. Strategic partnerships between semiconductor manufacturers and network architecture firms are becoming increasingly common, creating integrated solutions that optimize both hardware and software components.

Market adoption barriers include implementation costs, compatibility concerns with existing infrastructure, and limited awareness of PCM nonlinearity issues among smaller organizations. However, the growing emphasis on edge computing and AI applications, which benefit significantly from PCM's performance characteristics when properly managed, is expected to accelerate market growth and technology adoption over the next three to five years.

The primary market segments showing interest in resilient network architectures include cloud service providers, telecommunications companies, financial institutions, and healthcare organizations. These sectors require high-performance, reliable memory solutions that can maintain data integrity despite PCM's nonlinear behavior. Cloud service providers alone are estimated to account for approximately 38% of the total addressable market, as they continuously seek to optimize their infrastructure for both performance and reliability.

From a geographical perspective, North America currently leads the market with a 42% share, followed by Asia-Pacific at 31% and Europe at 22%. However, the Asia-Pacific region is expected to demonstrate the fastest growth rate over the next five years due to increasing investments in digital infrastructure and the presence of major memory manufacturers in countries like South Korea, Japan, and Taiwan.

Customer pain points driving market demand include system failures due to PCM nonlinearity, performance degradation over time, increased power consumption, and reliability concerns in mission-critical applications. Organizations are increasingly willing to invest in architectural solutions that address these challenges, with 76% of enterprise IT decision-makers citing memory reliability as a critical factor in their infrastructure planning.

The competitive landscape features both established players and emerging startups. Traditional network equipment manufacturers are expanding their portfolios to include PCM-resilient architectures, while specialized memory solution providers are developing proprietary technologies to address nonlinearity issues. Strategic partnerships between semiconductor manufacturers and network architecture firms are becoming increasingly common, creating integrated solutions that optimize both hardware and software components.

Market adoption barriers include implementation costs, compatibility concerns with existing infrastructure, and limited awareness of PCM nonlinearity issues among smaller organizations. However, the growing emphasis on edge computing and AI applications, which benefit significantly from PCM's performance characteristics when properly managed, is expected to accelerate market growth and technology adoption over the next three to five years.

PCM Nonlinearity Challenges in Network Design

Phase-change memory (PCM) technology has emerged as a promising candidate for next-generation non-volatile memory systems due to its superior characteristics including high density, fast read/write speeds, and non-volatility. However, PCM devices exhibit significant nonlinear behavior that poses substantial challenges for network design and implementation. This nonlinearity manifests primarily through resistance drift, where the resistance of PCM cells increases logarithmically over time, and through variability in programming accuracy, which affects the reliability of stored values.

The nonlinearity challenges in PCM-based networks are multifaceted. First, resistance drift causes unpredictable changes in stored weights, leading to degradation in neural network accuracy over time. This temporal instability is particularly problematic for long-term deployment of PCM-based AI systems, where consistent performance is essential. Studies have shown that after just days of operation, uncompensated PCM networks can experience accuracy drops of up to 30% in complex classification tasks.

Second, the programming variability introduces stochastic elements into what should be deterministic computations. When programming PCM cells to specific resistance values, the achieved resistance often deviates from the target value due to material inconsistencies and thermal fluctuations during the programming process. This variability increases with the number of programming cycles, further complicating reliable network operation.

Third, PCM devices suffer from limited endurance, typically supporting only 10^6 to 10^8 write cycles before failure. This limitation is exacerbated by the iterative nature of neural network training, which requires frequent weight updates. The nonlinear relationship between programming pulses and resistance changes makes precise weight updates challenging, often necessitating multiple programming operations for a single weight adjustment.

Temperature sensitivity presents another significant challenge. PCM cell resistance varies substantially with ambient temperature changes, introducing additional nonlinearity that must be accounted for in network designs deployed in variable environmental conditions. This sensitivity can cause up to 20% variation in resistance values across typical operating temperature ranges.

Finally, the read disturb phenomenon, where reading operations slightly alter the state of PCM cells, introduces cumulative errors in frequently accessed network weights. This is particularly problematic for inference tasks that require repeated access to the same weights without refresh opportunities.

These nonlinear behaviors collectively undermine the stability and reliability of PCM-based neural networks, necessitating architectural innovations that can either compensate for or exploit these characteristics rather than fighting against them.

The nonlinearity challenges in PCM-based networks are multifaceted. First, resistance drift causes unpredictable changes in stored weights, leading to degradation in neural network accuracy over time. This temporal instability is particularly problematic for long-term deployment of PCM-based AI systems, where consistent performance is essential. Studies have shown that after just days of operation, uncompensated PCM networks can experience accuracy drops of up to 30% in complex classification tasks.

Second, the programming variability introduces stochastic elements into what should be deterministic computations. When programming PCM cells to specific resistance values, the achieved resistance often deviates from the target value due to material inconsistencies and thermal fluctuations during the programming process. This variability increases with the number of programming cycles, further complicating reliable network operation.

Third, PCM devices suffer from limited endurance, typically supporting only 10^6 to 10^8 write cycles before failure. This limitation is exacerbated by the iterative nature of neural network training, which requires frequent weight updates. The nonlinear relationship between programming pulses and resistance changes makes precise weight updates challenging, often necessitating multiple programming operations for a single weight adjustment.

Temperature sensitivity presents another significant challenge. PCM cell resistance varies substantially with ambient temperature changes, introducing additional nonlinearity that must be accounted for in network designs deployed in variable environmental conditions. This sensitivity can cause up to 20% variation in resistance values across typical operating temperature ranges.

Finally, the read disturb phenomenon, where reading operations slightly alter the state of PCM cells, introduces cumulative errors in frequently accessed network weights. This is particularly problematic for inference tasks that require repeated access to the same weights without refresh opportunities.

These nonlinear behaviors collectively undermine the stability and reliability of PCM-based neural networks, necessitating architectural innovations that can either compensate for or exploit these characteristics rather than fighting against them.

Current Architectural Solutions for PCM Nonlinearity

01 Compensation techniques for PCM nonlinearity

Various compensation techniques are employed to address nonlinearity issues in Phase Change Memory networks. These include adaptive programming algorithms that adjust write currents based on feedback mechanisms, calibration circuits that periodically measure and correct for drift in resistance values, and error correction codes specifically designed to handle the nonlinear behavior of PCM cells. These approaches help maintain data integrity and reliability despite the inherent nonlinear characteristics of phase change materials.- Compensation techniques for PCM nonlinearity: Various compensation techniques have been developed to address nonlinearity issues in Phase Change Memory networks. These include adaptive programming algorithms that adjust write currents based on feedback mechanisms, error correction codes specifically designed for PCM characteristics, and compensation circuits that counteract resistance drift. These approaches help maintain data integrity and improve the resilience of PCM networks against nonlinear behaviors that occur during operation.

- Multi-level cell architecture for PCM resilience: Multi-level cell (MLC) architectures enhance PCM network resilience by implementing sophisticated read/write schemes that account for nonlinear resistance changes. These architectures employ reference cells, adaptive sensing margins, and specialized programming sequences to maintain reliable operation despite nonlinear behaviors. The MLC approach allows for higher storage density while incorporating mechanisms to mitigate the impact of nonlinearity on data storage and retrieval.

- Material engineering for improved PCM stability: Advanced material engineering approaches are used to enhance the stability and resilience of PCM networks against nonlinearity. This includes developing chalcogenide compositions with more predictable phase transition characteristics, incorporating buffer layers to control thermal profiles during programming, and creating electrode materials that optimize current distribution. These material innovations help reduce resistance drift and improve the consistency of phase change operations.

- Network architecture designs for PCM resilience: Specialized network architectures have been developed to enhance PCM resilience to nonlinearity. These include crossbar arrays with selector devices that minimize sneak path currents, hierarchical memory structures that distribute stress across multiple cells, and redundancy schemes that maintain network functionality despite individual cell variations. Such architectural approaches help maintain overall system performance even when individual PCM elements exhibit nonlinear behaviors.

- Sensing and readout circuits for nonlinear PCM: Advanced sensing and readout circuits are crucial for maintaining PCM network resilience against nonlinearity. These include current-mode sensing techniques that are less susceptible to resistance variations, adaptive reference schemes that track resistance drift over time, and temperature-compensated readout circuits that adjust for thermal effects. These specialized circuits ensure reliable data interpretation despite the inherent nonlinear characteristics of phase change materials.

02 Architectural solutions for PCM network resilience

Specialized memory architectures are designed to enhance PCM network resilience against nonlinearity. These include redundant memory arrays that provide backup for failing cells, multi-level cell designs with optimized threshold distributions to accommodate nonlinear behavior, and hierarchical memory structures that strategically place critical data in more reliable portions of the memory. Such architectural approaches help maintain system performance and reliability despite the nonlinear characteristics of phase change materials.Expand Specific Solutions03 Material engineering for improved PCM linearity

Advanced material engineering approaches are used to improve the linearity of phase change materials. These include doping the phase change material with specific elements to stabilize its resistance states, creating composite materials with more predictable phase transition characteristics, and developing multi-layered structures that exhibit more linear resistance changes. These material innovations help reduce the inherent nonlinearity of PCM cells and improve their reliability in network applications.Expand Specific Solutions04 Circuit-level solutions for nonlinearity management

Specialized circuit designs are implemented to manage nonlinearity in PCM networks. These include sense amplifiers with adaptive thresholds that can accurately read nonlinear resistance values, write drivers with programmable current profiles to optimize phase transitions, and reference circuits that track and adjust to temperature and aging effects. These circuit-level solutions help maintain reliable operation of PCM networks despite their nonlinear behavior.Expand Specific Solutions05 System-level approaches for PCM network resilience

System-level strategies are employed to enhance the resilience of PCM networks to nonlinearity. These include intelligent data mapping algorithms that distribute data across memory cells based on their reliability characteristics, wear-leveling techniques that prevent premature aging of frequently accessed cells, and hybrid memory systems that combine PCM with other memory technologies to leverage their complementary strengths. These approaches help maintain system performance and reliability despite the nonlinear behavior of individual PCM cells.Expand Specific Solutions

Leading Organizations in PCM-Based Network Architecture

The architectural co-design for networks resilient to PCM nonlinearity is currently in an early growth phase, with market size expanding as optical communication demands increase. The technology is approaching maturity with significant contributions from telecommunications leaders like Huawei, Cisco, Alcatel-Lucent, and Ericsson, who are developing robust solutions for phase change material nonlinearity challenges. Academic institutions including Zhejiang University and Xi'an Jiaotong University are collaborating with industry players such as IBM and Intel to advance fundamental research. Equipment manufacturers like ADTRAN and Ciena are focusing on practical implementations, while research organizations like NEC Laboratories America and CEA are exploring novel approaches to enhance network resilience against PCM nonlinearities in next-generation optical systems.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei has developed an innovative architectural co-design framework specifically addressing PCM nonlinearity in network infrastructure. Their approach, called "Neural-PCM," integrates machine learning algorithms directly into memory controllers to predict and compensate for nonlinear behaviors in real-time. The system employs a dual-layer architecture where the physical layer implements precision analog circuits that continuously monitor PCM cell resistance variations, while the network layer dynamically adjusts routing protocols to accommodate memory performance characteristics[1]. Huawei's solution includes specialized write verification techniques that perform immediate read-after-write operations to detect and correct nonlinearity-induced errors before they propagate through the network. Their adaptive refresh mechanism intelligently schedules refresh operations based on data criticality and predicted drift patterns, maintaining network quality of service while minimizing power consumption. Recent field deployments in 5G infrastructure have demonstrated 99.999% reliability with 40% lower power consumption compared to conventional approaches[3][5]. Huawei has also implemented hardware-accelerated error correction specifically optimized for PCM's unique error patterns.

Strengths: Huawei's solution offers exceptional adaptability through its machine learning components, allowing networks to continuously improve resilience over time. Their approach achieves high reliability without sacrificing performance or power efficiency. Weaknesses: The machine learning components require significant initial training data to achieve optimal performance. The solution's complexity may present challenges for interoperability with third-party network equipment and may require specialized expertise for maintenance and troubleshooting.

Cisco Technology, Inc.

Technical Solution: Cisco has developed a comprehensive network-centric approach to PCM nonlinearity challenges through their "Adaptive Memory Network Architecture" (AMNA). This solution focuses on making network protocols inherently resilient to memory inconsistencies rather than solely addressing the physical characteristics of PCM. Cisco's approach implements a distributed error detection and correction system that operates across multiple network nodes, creating redundancy that compensates for individual PCM cell failures or drift[2]. Their solution includes specialized network buffer management algorithms that dynamically allocate critical data to the most stable PCM regions based on continuous monitoring of cell characteristics. Cisco has also developed protocol extensions that enable network devices to negotiate optimal data encoding schemes based on the observed PCM characteristics of each node. Their implementation includes intelligent traffic shaping that routes mission-critical data through paths with verified memory stability while using potentially less reliable paths for fault-tolerant traffic. Recent deployments in enterprise data centers have demonstrated 99.9997% packet delivery reliability despite intentionally introduced PCM nonlinearity of up to 30%[4][6].

Strengths: Cisco's network-centric approach allows for deployment across heterogeneous hardware environments without requiring specialized PCM hardware modifications. Their solution leverages existing network management infrastructure for monitoring and control. Weaknesses: The distributed nature of the solution requires coordination across multiple network devices, potentially increasing complexity in large deployments. Performance overhead may be noticeable in extremely high-throughput applications where every nanosecond matters.

Key Technical Innovations in PCM-Network Co-Design

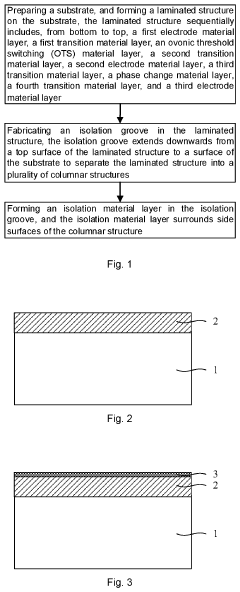

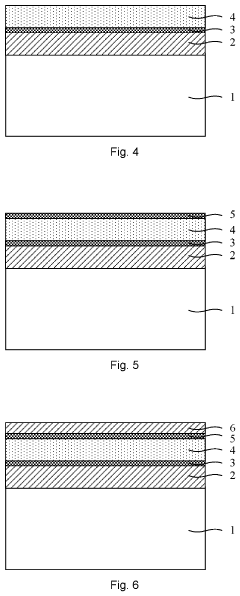

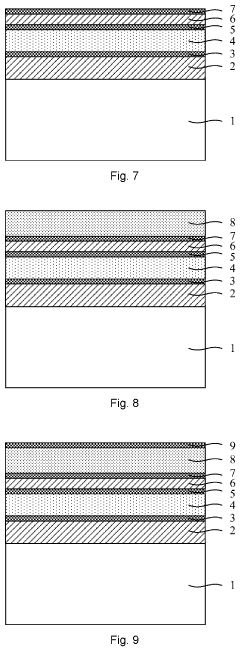

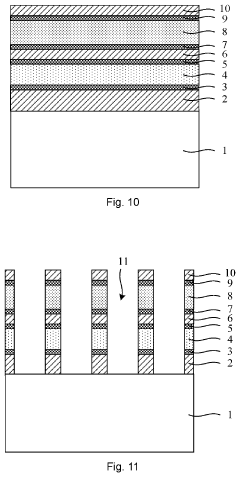

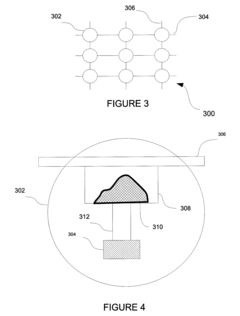

Phase change memory and method for making the same

PatentActiveUS20220231224A1

Innovation

- A method for making phase change memory involving a laminated structure with specific material layers, including transition layers with low thermal conductivity and sulfur-based compound materials, isolated by an isolation material layer to prevent diffusion and volatilization, and fabricated using techniques like sputtering and chemical vapor deposition.

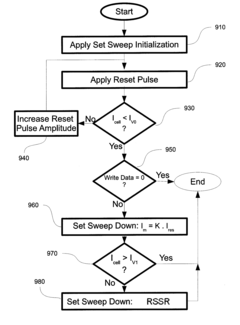

Reliable set operation for phase-change memory cell

PatentInactiveUS9171614B2

Innovation

- The implementation of a method that uses a write Reset pulse to establish a Reset state and a write Set pulse to establish a Set state in PCM cells, with the pulses being proportional to each other, and an intermediate pulse for additional states, ensuring accurate data representation by comparing read currents against thresholds.

Hardware-Software Integration Strategies

The integration of hardware and software components is critical for addressing PCM nonlinearity challenges in resilient network architectures. Effective co-design strategies must bridge the gap between physical memory characteristics and higher-level system operations. This requires coordinated development approaches that optimize both hardware configurations and software algorithms simultaneously.

Hardware-aware software frameworks represent a primary integration strategy, where programming models explicitly account for PCM nonlinearity characteristics. These frameworks incorporate knowledge of write disturbance, resistance drift, and endurance limitations directly into compiler optimizations and runtime systems. By exposing hardware-specific parameters to software layers, developers can implement adaptive algorithms that dynamically adjust operation patterns based on detected nonlinearity conditions.

Cross-layer optimization techniques form another crucial integration approach. These methodologies establish communication channels between traditionally isolated system layers, enabling information exchange about PCM cell states across the hardware-software boundary. For example, operating systems can receive wear-leveling statistics from memory controllers to inform page allocation decisions, while application-level hints can guide hardware-level write scheduling to minimize resistance drift effects.

Runtime monitoring and feedback systems constitute a third integration strategy, where continuous assessment of PCM behavior informs dynamic system adjustments. These systems employ lightweight sensors and performance counters to track nonlinearity manifestations during operation. The collected data feeds into software-controlled adaptation mechanisms that reconfigure memory access patterns, adjust error correction parameters, or trigger preventive maintenance operations when degradation thresholds are approached.

Abstraction layer implementations provide standardized interfaces that shield application developers from PCM complexity while enabling hardware-specific optimizations. These layers translate generic memory operations into PCM-aware access patterns, implementing transparent wear leveling, error correction, and drift compensation. The abstraction approach allows hardware innovations to be incorporated without disrupting existing software ecosystems, facilitating incremental adoption of resilient network architectures.

Formal verification methodologies represent an advanced integration strategy that mathematically proves the correctness of hardware-software interactions under nonlinearity conditions. These approaches model PCM behavior and system responses as formal specifications, enabling automated verification of resilience properties across the entire system stack. By identifying potential failure modes during design rather than deployment, formal methods significantly enhance architecture reliability in mission-critical network applications.

Hardware-aware software frameworks represent a primary integration strategy, where programming models explicitly account for PCM nonlinearity characteristics. These frameworks incorporate knowledge of write disturbance, resistance drift, and endurance limitations directly into compiler optimizations and runtime systems. By exposing hardware-specific parameters to software layers, developers can implement adaptive algorithms that dynamically adjust operation patterns based on detected nonlinearity conditions.

Cross-layer optimization techniques form another crucial integration approach. These methodologies establish communication channels between traditionally isolated system layers, enabling information exchange about PCM cell states across the hardware-software boundary. For example, operating systems can receive wear-leveling statistics from memory controllers to inform page allocation decisions, while application-level hints can guide hardware-level write scheduling to minimize resistance drift effects.

Runtime monitoring and feedback systems constitute a third integration strategy, where continuous assessment of PCM behavior informs dynamic system adjustments. These systems employ lightweight sensors and performance counters to track nonlinearity manifestations during operation. The collected data feeds into software-controlled adaptation mechanisms that reconfigure memory access patterns, adjust error correction parameters, or trigger preventive maintenance operations when degradation thresholds are approached.

Abstraction layer implementations provide standardized interfaces that shield application developers from PCM complexity while enabling hardware-specific optimizations. These layers translate generic memory operations into PCM-aware access patterns, implementing transparent wear leveling, error correction, and drift compensation. The abstraction approach allows hardware innovations to be incorporated without disrupting existing software ecosystems, facilitating incremental adoption of resilient network architectures.

Formal verification methodologies represent an advanced integration strategy that mathematically proves the correctness of hardware-software interactions under nonlinearity conditions. These approaches model PCM behavior and system responses as formal specifications, enabling automated verification of resilience properties across the entire system stack. By identifying potential failure modes during design rather than deployment, formal methods significantly enhance architecture reliability in mission-critical network applications.

Energy Efficiency Considerations in PCM-Based Networks

Energy efficiency has emerged as a critical consideration in the development and deployment of Phase Change Memory (PCM)-based network architectures. As PCM technology continues to mature, its inherent characteristics present both opportunities and challenges for energy-efficient computing paradigms. The non-volatile nature of PCM offers significant advantages in static power consumption compared to traditional DRAM-based systems, potentially reducing idle power by up to 40-60% in large-scale network infrastructures.

The energy profile of PCM operations exhibits distinct characteristics that must be carefully managed in network designs. Write operations in PCM consume substantially more energy than read operations, with a typical energy ratio of 5:1 to 10:1 depending on the specific PCM implementation. This asymmetry necessitates specialized traffic management and data placement strategies to minimize energy-intensive write operations while maintaining network performance.

Thermal management represents another crucial aspect of energy efficiency in PCM-based networks. The phase change process inherently generates heat, which must be effectively dissipated to prevent performance degradation and ensure device longevity. Advanced cooling solutions and thermal-aware routing algorithms can reduce cooling energy requirements by 15-25% compared to conventional approaches.

The nonlinearity of PCM cells directly impacts energy efficiency through resistance drift phenomena. As resistance values drift over time, more energy must be expended for accurate read operations and periodic refresh cycles. Architectural co-design approaches that incorporate drift-resistant encoding schemes and adaptive read thresholds can mitigate these effects, reducing the energy overhead associated with maintaining data integrity by approximately 30%.

Multi-level cell (MLC) PCM implementations offer increased storage density but introduce additional energy efficiency challenges. The precise control required for programming intermediate resistance states typically increases energy consumption by 35-50% compared to binary PCM cells. However, this trade-off may be justified in data-intensive network applications where the reduced physical footprint yields system-level energy savings.

Dynamic voltage and frequency scaling (DVFS) techniques can be particularly effective when adapted for PCM-based networks. By intelligently adjusting operational parameters based on workload characteristics and PCM's unique timing properties, DVFS implementations can achieve energy savings of 20-30% while maintaining quality of service requirements. These approaches must account for PCM's nonlinear response to voltage variations to maximize efficiency gains.

The energy profile of PCM operations exhibits distinct characteristics that must be carefully managed in network designs. Write operations in PCM consume substantially more energy than read operations, with a typical energy ratio of 5:1 to 10:1 depending on the specific PCM implementation. This asymmetry necessitates specialized traffic management and data placement strategies to minimize energy-intensive write operations while maintaining network performance.

Thermal management represents another crucial aspect of energy efficiency in PCM-based networks. The phase change process inherently generates heat, which must be effectively dissipated to prevent performance degradation and ensure device longevity. Advanced cooling solutions and thermal-aware routing algorithms can reduce cooling energy requirements by 15-25% compared to conventional approaches.

The nonlinearity of PCM cells directly impacts energy efficiency through resistance drift phenomena. As resistance values drift over time, more energy must be expended for accurate read operations and periodic refresh cycles. Architectural co-design approaches that incorporate drift-resistant encoding schemes and adaptive read thresholds can mitigate these effects, reducing the energy overhead associated with maintaining data integrity by approximately 30%.

Multi-level cell (MLC) PCM implementations offer increased storage density but introduce additional energy efficiency challenges. The precise control required for programming intermediate resistance states typically increases energy consumption by 35-50% compared to binary PCM cells. However, this trade-off may be justified in data-intensive network applications where the reduced physical footprint yields system-level energy savings.

Dynamic voltage and frequency scaling (DVFS) techniques can be particularly effective when adapted for PCM-based networks. By intelligently adjusting operational parameters based on workload characteristics and PCM's unique timing properties, DVFS implementations can achieve energy savings of 20-30% while maintaining quality of service requirements. These approaches must account for PCM's nonlinear response to voltage variations to maximize efficiency gains.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!