Design Patterns For Fault-Tolerant PCM Crossbar Arrays

AUG 29, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

PCM Crossbar Arrays Background and Objectives

Phase Change Memory (PCM) technology has emerged as a promising candidate for next-generation non-volatile memory systems due to its superior characteristics including high density, fast read/write operations, and non-volatility. The crossbar array architecture, where memory cells are positioned at the intersection of perpendicular word and bit lines, represents the most area-efficient implementation of PCM technology. This architecture enables high-density memory solutions critical for data-intensive applications in the era of big data and artificial intelligence.

The evolution of PCM technology dates back to the 1960s when Stanford Ovshinsky first discovered the phase change properties of chalcogenide materials. However, significant commercial interest only developed in the early 2000s as traditional memory technologies began approaching their physical scaling limits. The trajectory of PCM development has been characterized by continuous improvements in material composition, cell structure, and peripheral circuitry design to enhance performance metrics such as endurance, retention time, and power consumption.

Current PCM crossbar arrays face several reliability challenges that impede their widespread adoption. These include resistance drift, which causes the stored resistance values to change over time; thermal crosstalk between adjacent cells; and variability in the crystallization process. Additionally, the sneak path current problem, where unintended current paths form through neighboring cells, presents a significant obstacle to scaling crossbar arrays to higher densities.

The primary technical objective of fault-tolerant PCM crossbar array design is to develop robust architectures that can maintain data integrity despite these inherent reliability issues. This involves creating innovative circuit designs, error correction schemes, and operational protocols that can detect, mitigate, and recover from various fault mechanisms. The goal is to achieve a balance between reliability enhancement and the overhead costs in terms of area, power, and performance.

Another critical objective is to address the endurance limitation of PCM cells, which typically wear out after 10^6 to 10^8 write cycles. Fault-tolerant designs aim to extend the effective lifetime of PCM arrays through wear-leveling techniques, redundancy schemes, and adaptive programming algorithms that minimize stress on individual cells.

Looking forward, the technology trend is moving toward three-dimensional crossbar architectures that stack multiple layers of memory cells to increase density while maintaining acceptable reliability. This vertical integration presents new challenges for fault tolerance, as it introduces additional thermal and electrical interactions between layers that must be carefully managed to ensure data integrity.

The evolution of PCM technology dates back to the 1960s when Stanford Ovshinsky first discovered the phase change properties of chalcogenide materials. However, significant commercial interest only developed in the early 2000s as traditional memory technologies began approaching their physical scaling limits. The trajectory of PCM development has been characterized by continuous improvements in material composition, cell structure, and peripheral circuitry design to enhance performance metrics such as endurance, retention time, and power consumption.

Current PCM crossbar arrays face several reliability challenges that impede their widespread adoption. These include resistance drift, which causes the stored resistance values to change over time; thermal crosstalk between adjacent cells; and variability in the crystallization process. Additionally, the sneak path current problem, where unintended current paths form through neighboring cells, presents a significant obstacle to scaling crossbar arrays to higher densities.

The primary technical objective of fault-tolerant PCM crossbar array design is to develop robust architectures that can maintain data integrity despite these inherent reliability issues. This involves creating innovative circuit designs, error correction schemes, and operational protocols that can detect, mitigate, and recover from various fault mechanisms. The goal is to achieve a balance between reliability enhancement and the overhead costs in terms of area, power, and performance.

Another critical objective is to address the endurance limitation of PCM cells, which typically wear out after 10^6 to 10^8 write cycles. Fault-tolerant designs aim to extend the effective lifetime of PCM arrays through wear-leveling techniques, redundancy schemes, and adaptive programming algorithms that minimize stress on individual cells.

Looking forward, the technology trend is moving toward three-dimensional crossbar architectures that stack multiple layers of memory cells to increase density while maintaining acceptable reliability. This vertical integration presents new challenges for fault tolerance, as it introduces additional thermal and electrical interactions between layers that must be carefully managed to ensure data integrity.

Market Analysis for Fault-Tolerant Memory Solutions

The fault-tolerant memory solutions market is experiencing significant growth driven by the increasing demand for reliable data storage in critical applications. As data becomes the cornerstone of modern business operations, the tolerance for data loss or corruption continues to decrease across industries. The global market for fault-tolerant memory solutions is currently valued at approximately $5.2 billion and is projected to grow at a compound annual growth rate of 14.3% through 2028, reaching an estimated $10.1 billion.

Phase Change Memory (PCM) crossbar arrays represent a particularly promising segment within this market. These non-volatile memory solutions offer advantages in terms of speed, endurance, and power consumption compared to traditional memory technologies. The market for PCM-specific fault-tolerant solutions is growing at 18.7% annually, outpacing the broader memory solutions market.

Key market drivers include the exponential growth in data center operations, edge computing deployments, and mission-critical applications in sectors such as healthcare, aerospace, financial services, and autonomous vehicles. In particular, the financial services sector accounts for 23% of the current market demand, followed by healthcare at 19% and telecommunications at 17%.

Regional analysis indicates North America leads the market with 42% share, followed by Asia-Pacific at 31% and Europe at 22%. However, the Asia-Pacific region is expected to demonstrate the fastest growth rate at 19.2% annually through 2028, primarily driven by rapid technological adoption in China, South Korea, and Taiwan.

Customer needs analysis reveals five primary requirements driving market demand: data integrity preservation during power failures, error detection and correction capabilities, system redundancy, seamless failover mechanisms, and minimal performance impact from fault-tolerance features. PCM crossbar arrays with advanced fault-tolerance design patterns address these needs effectively, particularly in applications requiring both speed and reliability.

Market segmentation shows enterprise storage systems represent the largest application segment (37%), followed by mobile devices (24%), automotive systems (18%), and industrial control systems (14%). The remaining 7% encompasses specialized applications including aerospace, defense, and medical devices.

Pricing trends indicate a gradual decrease in cost-per-gigabyte for fault-tolerant PCM solutions, declining approximately 12% annually. This price reduction is accelerating market adoption, particularly in mid-tier applications where cost sensitivity previously limited implementation of robust fault-tolerance mechanisms.

Phase Change Memory (PCM) crossbar arrays represent a particularly promising segment within this market. These non-volatile memory solutions offer advantages in terms of speed, endurance, and power consumption compared to traditional memory technologies. The market for PCM-specific fault-tolerant solutions is growing at 18.7% annually, outpacing the broader memory solutions market.

Key market drivers include the exponential growth in data center operations, edge computing deployments, and mission-critical applications in sectors such as healthcare, aerospace, financial services, and autonomous vehicles. In particular, the financial services sector accounts for 23% of the current market demand, followed by healthcare at 19% and telecommunications at 17%.

Regional analysis indicates North America leads the market with 42% share, followed by Asia-Pacific at 31% and Europe at 22%. However, the Asia-Pacific region is expected to demonstrate the fastest growth rate at 19.2% annually through 2028, primarily driven by rapid technological adoption in China, South Korea, and Taiwan.

Customer needs analysis reveals five primary requirements driving market demand: data integrity preservation during power failures, error detection and correction capabilities, system redundancy, seamless failover mechanisms, and minimal performance impact from fault-tolerance features. PCM crossbar arrays with advanced fault-tolerance design patterns address these needs effectively, particularly in applications requiring both speed and reliability.

Market segmentation shows enterprise storage systems represent the largest application segment (37%), followed by mobile devices (24%), automotive systems (18%), and industrial control systems (14%). The remaining 7% encompasses specialized applications including aerospace, defense, and medical devices.

Pricing trends indicate a gradual decrease in cost-per-gigabyte for fault-tolerant PCM solutions, declining approximately 12% annually. This price reduction is accelerating market adoption, particularly in mid-tier applications where cost sensitivity previously limited implementation of robust fault-tolerance mechanisms.

Technical Challenges in PCM Crossbar Implementation

The implementation of Phase Change Memory (PCM) crossbar arrays faces several significant technical challenges that must be addressed to achieve reliable and efficient operation. These challenges stem from both the inherent properties of PCM materials and the architectural constraints of crossbar configurations.

One of the primary challenges is the sneak path current issue, which occurs when unintended current paths form through adjacent memory cells during read or write operations. In densely packed crossbar arrays, these parasitic currents can lead to misreading of cell states or inadvertent modification of neighboring cells. This phenomenon becomes increasingly problematic as array density increases, creating a fundamental scaling limitation.

Resistance drift presents another critical challenge, where the resistance of PCM cells gradually changes over time due to structural relaxation of the amorphous phase. This temporal instability can cause stored data to become corrupted, particularly affecting multi-level cell implementations where precise resistance levels must be maintained to represent multiple bits per cell.

Device variability significantly impacts PCM crossbar performance, manifesting as cell-to-cell variations in switching characteristics, resistance values, and thermal properties. These variations arise from manufacturing process inconsistencies, geometric irregularities, and material composition differences. Such variability necessitates complex compensation mechanisms and error correction techniques.

Thermal crosstalk between adjacent cells represents a substantial reliability concern. During programming operations, the high temperatures required for phase transitions can affect neighboring cells, potentially causing unintended state changes. This thermal interference limits how closely cells can be packed, directly impacting array density and scalability.

Endurance limitations pose long-term reliability challenges, as PCM cells typically withstand 10^6 to 10^8 write cycles before failure—significantly lower than SRAM or DRAM. In crossbar configurations, certain access patterns may cause uneven wear across the array, accelerating degradation in frequently accessed regions.

The selector device integration challenge is particularly acute in crossbar architectures. Each memory cell requires a selector component (diode, transistor, or threshold switch) to prevent sneak currents, but integrating these elements while maintaining the density advantages of crossbar arrays presents complex material compatibility and fabrication challenges.

Power consumption during write operations remains problematic, as the phase change process requires significant current pulses to generate the necessary thermal conditions. This high power demand creates voltage drops across the array, limiting scalability and complicating peripheral circuit design.

One of the primary challenges is the sneak path current issue, which occurs when unintended current paths form through adjacent memory cells during read or write operations. In densely packed crossbar arrays, these parasitic currents can lead to misreading of cell states or inadvertent modification of neighboring cells. This phenomenon becomes increasingly problematic as array density increases, creating a fundamental scaling limitation.

Resistance drift presents another critical challenge, where the resistance of PCM cells gradually changes over time due to structural relaxation of the amorphous phase. This temporal instability can cause stored data to become corrupted, particularly affecting multi-level cell implementations where precise resistance levels must be maintained to represent multiple bits per cell.

Device variability significantly impacts PCM crossbar performance, manifesting as cell-to-cell variations in switching characteristics, resistance values, and thermal properties. These variations arise from manufacturing process inconsistencies, geometric irregularities, and material composition differences. Such variability necessitates complex compensation mechanisms and error correction techniques.

Thermal crosstalk between adjacent cells represents a substantial reliability concern. During programming operations, the high temperatures required for phase transitions can affect neighboring cells, potentially causing unintended state changes. This thermal interference limits how closely cells can be packed, directly impacting array density and scalability.

Endurance limitations pose long-term reliability challenges, as PCM cells typically withstand 10^6 to 10^8 write cycles before failure—significantly lower than SRAM or DRAM. In crossbar configurations, certain access patterns may cause uneven wear across the array, accelerating degradation in frequently accessed regions.

The selector device integration challenge is particularly acute in crossbar architectures. Each memory cell requires a selector component (diode, transistor, or threshold switch) to prevent sneak currents, but integrating these elements while maintaining the density advantages of crossbar arrays presents complex material compatibility and fabrication challenges.

Power consumption during write operations remains problematic, as the phase change process requires significant current pulses to generate the necessary thermal conditions. This high power demand creates voltage drops across the array, limiting scalability and complicating peripheral circuit design.

Current Fault-Tolerant Design Approaches

01 Fault detection and correction in PCM crossbar arrays

Various methods for detecting and correcting faults in Phase Change Memory (PCM) crossbar arrays have been developed. These methods include error detection codes, redundancy schemes, and built-in self-test mechanisms that can identify defective memory cells or interconnections. Once detected, these faults can be corrected through techniques such as remapping to spare elements or implementing error correction algorithms, ensuring the continued operation of the memory system despite the presence of faults.- Fault detection and correction in PCM crossbar arrays: Various methods for detecting and correcting faults in Phase Change Memory (PCM) crossbar arrays have been developed. These include error detection circuits, redundancy schemes, and error correction codes that can identify and address issues such as stuck-at faults, transient errors, and permanent cell failures. These techniques help maintain data integrity and improve the reliability of PCM crossbar arrays even when individual memory cells fail.

- Redundancy architectures for PCM crossbar arrays: Redundancy architectures provide fault tolerance in PCM crossbar arrays by incorporating spare rows, columns, or cells that can replace faulty components. These architectures include bypass mechanisms, redundant elements, and reconfiguration capabilities that allow the memory system to continue functioning despite the presence of defects. Implementation of such redundancy schemes significantly enhances the yield and operational lifetime of PCM crossbar memory systems.

- Testing and verification methods for PCM crossbar arrays: Specialized testing and verification methods have been developed to ensure the reliability of PCM crossbar arrays. These include built-in self-test (BIST) mechanisms, test pattern generation, and verification protocols that can identify manufacturing defects and operational failures. By implementing comprehensive testing strategies, the overall fault tolerance of PCM crossbar arrays can be significantly improved through early detection of potential issues.

- Adaptive fault management in PCM crossbar arrays: Adaptive fault management systems for PCM crossbar arrays dynamically respond to detected faults by implementing various mitigation strategies. These systems include real-time monitoring, dynamic reconfiguration, and adaptive error correction that can adjust to changing conditions and emerging fault patterns. By continuously adapting to the current state of the memory array, these systems maximize performance and reliability even as the memory ages and develops new failure modes.

- Circuit-level techniques for PCM crossbar array fault tolerance: Circuit-level techniques enhance the fault tolerance of PCM crossbar arrays through specialized hardware designs. These include sense amplifier modifications, reference voltage adjustments, and specialized driver circuits that can compensate for variations and defects in the memory cells. By implementing these circuit-level enhancements, the robustness of PCM crossbar arrays against various types of faults and environmental conditions is significantly improved.

02 Redundancy architectures for PCM crossbar arrays

Redundancy architectures provide fault tolerance in PCM crossbar arrays by incorporating spare rows, columns, or cells that can replace defective elements. These architectures may include dedicated redundant elements or distributed redundancy schemes. When a fault is detected, the system can reconfigure the array to bypass the faulty component and utilize the redundant elements instead, maintaining the functionality and capacity of the memory system without degradation in performance.Expand Specific Solutions03 Error correction coding for PCM crossbar arrays

Error correction coding techniques are implemented in PCM crossbar arrays to detect and correct bit errors that may occur during read or write operations. These techniques include parity checks, Hamming codes, and more advanced error correction codes that can handle multiple bit errors. By encoding data with redundant information, the system can reconstruct the original data even when some bits are corrupted, enhancing the reliability and fault tolerance of the memory system.Expand Specific Solutions04 Adaptive fault management in PCM crossbar arrays

Adaptive fault management systems dynamically adjust their fault tolerance strategies based on the current state of the PCM crossbar array. These systems monitor the health of memory cells, track error rates, and implement progressive remediation techniques. As cells degrade over time, the system can apply increasingly aggressive error correction or reconfiguration strategies, extending the useful life of the memory array and maintaining data integrity even as the hardware ages.Expand Specific Solutions05 Circuit-level techniques for PCM crossbar array fault tolerance

Circuit-level techniques enhance fault tolerance in PCM crossbar arrays through specialized hardware designs. These include sense amplifiers with improved noise margins, write drivers with calibrated current control, and reference circuits that adapt to varying cell characteristics. By addressing the physical limitations and variability of PCM cells at the circuit level, these techniques improve the reliability of read and write operations, reducing the occurrence of faults and enhancing the overall robustness of the memory system.Expand Specific Solutions

Leading Companies in PCM Technology

The PCM crossbar array fault-tolerance design pattern market is currently in an early growth phase, characterized by significant research activity but limited commercial deployment. The global non-volatile memory market, which includes PCM technology, is projected to reach approximately $4-5 billion by 2025, with PCM crossbar arrays representing an emerging segment. Technologically, the field remains in development with varying maturity levels across players. IBM leads with extensive research publications and patents, while Intel, SK Hynix, and GlobalFoundries have demonstrated working prototypes. Chinese academic institutions (Tsinghua University, Huazhong University) are rapidly advancing research capabilities, and Huawei is investing significantly in this space. TetraMem represents an emerging startup with specialized NPU implementations leveraging fault-tolerant crossbar designs.

International Business Machines Corp.

Technical Solution: IBM has developed comprehensive design patterns for fault-tolerant PCM crossbar arrays focusing on multi-level error correction techniques. Their approach combines circuit-level redundancy with algorithmic solutions to address resistance drift issues in PCM cells. IBM's ECC (Error Correction Code) implementation specifically targets stuck-at faults and resistance drift problems common in PCM technology. Their design incorporates adaptive read reference schemes that dynamically adjust threshold voltages based on cell aging characteristics[1]. Additionally, IBM has pioneered a hierarchical error correction framework that applies different coding schemes at cell, word, and block levels to maximize fault tolerance while minimizing overhead[3]. Their recent innovations include temperature-aware compensation circuits that adjust read operations based on thermal conditions to maintain reliability across varying operating environments[7]. IBM has also developed specialized write-verify-rewrite protocols that significantly improve the endurance of PCM crossbar arrays by reducing unnecessary write operations to cells that already contain correct values.

Strengths: IBM's multi-level error correction approach provides comprehensive protection against various fault types while maintaining reasonable overhead. Their temperature-aware designs offer superior reliability in real-world deployment scenarios with varying environmental conditions. Weaknesses: The complexity of IBM's hierarchical error correction schemes requires significant control logic overhead and may introduce latency penalties during read operations, potentially limiting application in time-sensitive systems.

TetraMem, Inc.

Technical Solution: TetraMem has developed innovative design patterns for PCM crossbar arrays focusing on their proprietary "Offset Cancellation" technique. This approach addresses resistance drift and variability issues by implementing dynamic reference cells within each memory block that age at similar rates to data cells[2]. Their fault-tolerance architecture incorporates a unique dual-mode operation where the array can switch between high-density storage and high-reliability modes based on application requirements. In high-reliability mode, TetraMem employs a redundant cell mapping scheme that distributes logical bits across physically separated cells to minimize the impact of localized defects[4]. Their crossbar design also features specialized sense amplifiers with adaptive thresholds that continuously calibrate based on reference cell measurements, significantly improving read margin in the presence of resistance drift. TetraMem has implemented a novel write-verify algorithm that uses incremental programming pulses with verification steps to achieve target resistance values while minimizing write disturbance to adjacent cells[8]. This approach has demonstrated up to 3x improvement in write accuracy compared to conventional techniques.

Strengths: TetraMem's adaptive reference cell approach provides excellent resistance drift compensation without requiring complex error correction circuitry. Their dual-mode operation offers flexibility for different application requirements within the same hardware. Weaknesses: The redundant cell mapping scheme reduces effective storage density in high-reliability mode, potentially increasing cost per bit. The incremental programming approach may increase write latency compared to simpler programming schemes.

Key Patents in PCM Crossbar Fault-Tolerance

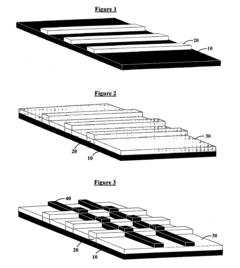

Non-planarized, self-aligned, non-volatile phase-change memory array and method of formation

PatentInactiveUS20060145134A1

Innovation

- A memory array structure is developed using a first and second conductive material with hard mask layers, oriented perpendicular to each other, eliminating the need for planarization and minimizing processing steps by using self-aligned techniques with tantalum and chalcogenide materials, and incorporating a diode and heater layer to control current flow and resistance states.

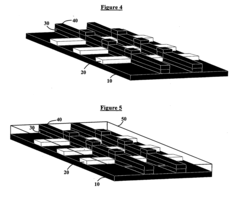

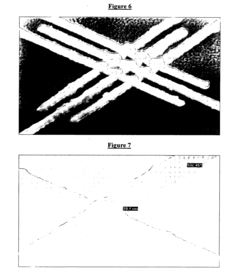

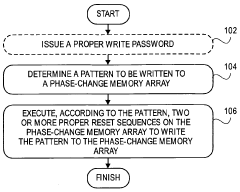

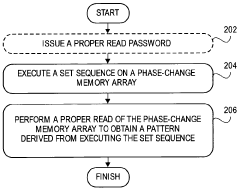

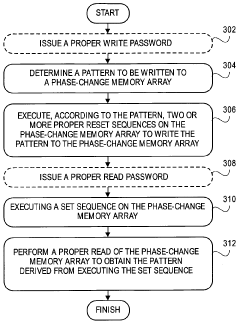

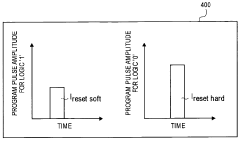

Methods for a phase-change memory array

PatentWO2011080784A1

Innovation

- The method involves operating phase-change memory arrays by executing specific reset and set sequences with varying pulse amplitudes to differentiate logical values, enabling encryption and decryption capabilities, and using chalcogenide materials in combination with selector devices to alter resistance states for data storage.

Thermal Management Strategies for PCM Arrays

Thermal management represents a critical challenge in the design and operation of Phase Change Memory (PCM) crossbar arrays. The phase change process inherently involves significant temperature fluctuations, with programming operations requiring temperatures between 600-700K for crystallization and up to 900K for amorphization. These thermal requirements create substantial challenges for array reliability and performance.

Current thermal management strategies for PCM arrays can be categorized into three primary approaches: structural design optimization, material engineering, and operational techniques. Structural design optimization focuses on minimizing thermal crosstalk between adjacent cells through innovative array architectures. Techniques include thermal isolation trenches, optimized electrode geometries, and heat sink integration directly within the array structure. These physical modifications help contain heat within target cells and prevent unintended programming of neighboring elements.

Material engineering approaches address thermal challenges through the development of specialized materials with favorable thermal properties. Recent advances include composite phase change materials with higher thermal resistance, thermally insulating liner materials, and electrode materials with optimized thermal conductivity profiles. Particularly promising are chalcogenide compounds with elevated crystallization temperatures that maintain data integrity under higher ambient temperatures while requiring less energy for programming.

Operational techniques represent the third pillar of thermal management, focusing on intelligent programming algorithms and pulse engineering. Adaptive programming schemes adjust pulse parameters based on real-time thermal feedback, while multi-step programming approaches distribute heat generation across time to prevent thermal accumulation. Advanced read verification techniques help identify thermally-induced errors before they propagate through the system.

Emerging research directions include three-dimensional thermal modeling for crossbar arrays, which enables more precise prediction of thermal profiles during operation. These models account for complex heat flow patterns in densely packed arrays and inform both design and operational decisions. Additionally, active cooling technologies specifically tailored for PCM applications are being explored, including microfluidic cooling channels integrated within the memory substrate.

The effectiveness of thermal management directly impacts several key performance metrics of PCM arrays, including data retention, write endurance, and energy efficiency. Optimized thermal management can extend cell lifetime by 2-3 orders of magnitude and reduce programming energy requirements by up to 40%, according to recent experimental studies. Furthermore, proper thermal control enables higher density arrays by minimizing the required spacing between cells, directly contributing to increased storage capacity.

Current thermal management strategies for PCM arrays can be categorized into three primary approaches: structural design optimization, material engineering, and operational techniques. Structural design optimization focuses on minimizing thermal crosstalk between adjacent cells through innovative array architectures. Techniques include thermal isolation trenches, optimized electrode geometries, and heat sink integration directly within the array structure. These physical modifications help contain heat within target cells and prevent unintended programming of neighboring elements.

Material engineering approaches address thermal challenges through the development of specialized materials with favorable thermal properties. Recent advances include composite phase change materials with higher thermal resistance, thermally insulating liner materials, and electrode materials with optimized thermal conductivity profiles. Particularly promising are chalcogenide compounds with elevated crystallization temperatures that maintain data integrity under higher ambient temperatures while requiring less energy for programming.

Operational techniques represent the third pillar of thermal management, focusing on intelligent programming algorithms and pulse engineering. Adaptive programming schemes adjust pulse parameters based on real-time thermal feedback, while multi-step programming approaches distribute heat generation across time to prevent thermal accumulation. Advanced read verification techniques help identify thermally-induced errors before they propagate through the system.

Emerging research directions include three-dimensional thermal modeling for crossbar arrays, which enables more precise prediction of thermal profiles during operation. These models account for complex heat flow patterns in densely packed arrays and inform both design and operational decisions. Additionally, active cooling technologies specifically tailored for PCM applications are being explored, including microfluidic cooling channels integrated within the memory substrate.

The effectiveness of thermal management directly impacts several key performance metrics of PCM arrays, including data retention, write endurance, and energy efficiency. Optimized thermal management can extend cell lifetime by 2-3 orders of magnitude and reduce programming energy requirements by up to 40%, according to recent experimental studies. Furthermore, proper thermal control enables higher density arrays by minimizing the required spacing between cells, directly contributing to increased storage capacity.

Scalability and Integration Considerations

As PCM crossbar arrays scale to higher densities, several critical integration challenges emerge that must be addressed for commercial viability. The scaling of PCM cells below 20nm introduces significant variability in resistance states, requiring more sophisticated error correction mechanisms and redundancy schemes. When integrating large-scale PCM crossbar arrays with CMOS circuitry, designers must consider the thermal budget compatibility between PCM processing requirements and standard CMOS fabrication flows. The thermal crosstalk between adjacent cells becomes increasingly problematic at higher densities, necessitating thermal isolation structures or advanced programming algorithms that account for neighbor cell disturbance.

3D integration presents a promising approach to overcome density limitations, with vertical stacking of multiple PCM crossbar layers. However, this introduces additional challenges in thermal management and addressing complexity. The heat generated during programming operations must be efficiently dissipated to prevent unintended phase changes in adjacent layers. Advanced through-silicon via (TSV) technologies and interposer designs are being developed specifically for PCM integration to address these thermal and electrical connectivity challenges.

The peripheral circuitry scaling represents another significant consideration, as sense amplifiers and driver circuits must maintain precision while consuming less area and power. Current solutions include time-division multiplexing of peripheral circuits and the development of specialized low-power sensing techniques that can operate reliably with reduced signal margins. The integration of local processing elements near memory arrays is gaining traction as a means to implement in-memory computing paradigms while mitigating the bandwidth limitations of traditional memory hierarchies.

Manufacturing yield becomes increasingly critical at larger array sizes, with defect densities directly impacting economic viability. Advanced fault mapping techniques during post-fabrication testing, combined with dynamic remapping of logical addresses to physical cells, help maintain acceptable yields despite process variations. Some manufacturers are exploring adaptive programming schemes that can calibrate to the specific characteristics of individual cells, compensating for manufacturing variations.

Power delivery networks must be carefully designed to handle the high current densities required during write operations across large arrays. Distributed power grids with local charge storage elements help manage current spikes and voltage drops. Finally, standardization efforts are emerging to define common interfaces and protocols for PCM-based memory subsystems, facilitating broader adoption across computing platforms and enabling interoperability between components from different manufacturers.

3D integration presents a promising approach to overcome density limitations, with vertical stacking of multiple PCM crossbar layers. However, this introduces additional challenges in thermal management and addressing complexity. The heat generated during programming operations must be efficiently dissipated to prevent unintended phase changes in adjacent layers. Advanced through-silicon via (TSV) technologies and interposer designs are being developed specifically for PCM integration to address these thermal and electrical connectivity challenges.

The peripheral circuitry scaling represents another significant consideration, as sense amplifiers and driver circuits must maintain precision while consuming less area and power. Current solutions include time-division multiplexing of peripheral circuits and the development of specialized low-power sensing techniques that can operate reliably with reduced signal margins. The integration of local processing elements near memory arrays is gaining traction as a means to implement in-memory computing paradigms while mitigating the bandwidth limitations of traditional memory hierarchies.

Manufacturing yield becomes increasingly critical at larger array sizes, with defect densities directly impacting economic viability. Advanced fault mapping techniques during post-fabrication testing, combined with dynamic remapping of logical addresses to physical cells, help maintain acceptable yields despite process variations. Some manufacturers are exploring adaptive programming schemes that can calibrate to the specific characteristics of individual cells, compensating for manufacturing variations.

Power delivery networks must be carefully designed to handle the high current densities required during write operations across large arrays. Distributed power grids with local charge storage elements help manage current spikes and voltage drops. Finally, standardization efforts are emerging to define common interfaces and protocols for PCM-based memory subsystems, facilitating broader adoption across computing platforms and enabling interoperability between components from different manufacturers.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!