Modeling PCM Nonidealities For Accurate Network Training Simulations

AUG 29, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

PCM Technology Background and Objectives

Phase Change Memory (PCM) technology has emerged as a promising candidate for next-generation non-volatile memory systems due to its favorable characteristics including high density, scalability, and compatibility with CMOS processes. PCM operates by utilizing the significant electrical resistivity difference between amorphous and crystalline states of chalcogenide materials, typically Ge-Sb-Te (GST) compounds. The technology's development traces back to the 1960s, but significant commercial viability has only been achieved in the past decade with advancements in manufacturing processes and material science.

The evolution of PCM technology has been marked by continuous improvements in endurance, retention time, and switching speed. Early implementations suffered from reliability issues, particularly related to resistance drift and limited write endurance. However, recent innovations in cell architecture, interface engineering, and programming schemes have substantially mitigated these limitations, making PCM increasingly attractive for various applications beyond traditional storage.

A particularly promising application domain for PCM technology is neuromorphic computing, where PCM devices can serve as artificial synapses in hardware neural networks. The analog nature of PCM resistance states enables the implementation of multi-level storage capabilities, which aligns well with the weighted connections required in neural networks. This synergy has accelerated research interest in PCM-based neuromorphic systems over the past five years.

Despite these advancements, accurately modeling PCM behavior in neural network simulations remains challenging due to various non-idealities inherent to the technology. These include resistance drift, read noise, programming variability, and limited endurance. These non-idealities can significantly impact the performance and reliability of PCM-based neural networks, creating a gap between theoretical models and practical implementations.

The primary objective of modeling PCM non-idealities for accurate network training simulations is to develop comprehensive mathematical frameworks that capture the complex physical behaviors of PCM devices during neural network operations. Such models must account for temporal variations in device characteristics, statistical distributions of programming outcomes, and cumulative effects of repeated operations.

Additionally, these models aim to enable more realistic simulations of PCM-based neural networks, allowing researchers and engineers to predict performance degradation, develop compensation techniques, and optimize network architectures specifically for PCM implementation. The ultimate goal is to bridge the gap between idealized neural network algorithms and their physical realization in PCM hardware, facilitating the development of more efficient and reliable neuromorphic computing systems.

The evolution of PCM technology has been marked by continuous improvements in endurance, retention time, and switching speed. Early implementations suffered from reliability issues, particularly related to resistance drift and limited write endurance. However, recent innovations in cell architecture, interface engineering, and programming schemes have substantially mitigated these limitations, making PCM increasingly attractive for various applications beyond traditional storage.

A particularly promising application domain for PCM technology is neuromorphic computing, where PCM devices can serve as artificial synapses in hardware neural networks. The analog nature of PCM resistance states enables the implementation of multi-level storage capabilities, which aligns well with the weighted connections required in neural networks. This synergy has accelerated research interest in PCM-based neuromorphic systems over the past five years.

Despite these advancements, accurately modeling PCM behavior in neural network simulations remains challenging due to various non-idealities inherent to the technology. These include resistance drift, read noise, programming variability, and limited endurance. These non-idealities can significantly impact the performance and reliability of PCM-based neural networks, creating a gap between theoretical models and practical implementations.

The primary objective of modeling PCM non-idealities for accurate network training simulations is to develop comprehensive mathematical frameworks that capture the complex physical behaviors of PCM devices during neural network operations. Such models must account for temporal variations in device characteristics, statistical distributions of programming outcomes, and cumulative effects of repeated operations.

Additionally, these models aim to enable more realistic simulations of PCM-based neural networks, allowing researchers and engineers to predict performance degradation, develop compensation techniques, and optimize network architectures specifically for PCM implementation. The ultimate goal is to bridge the gap between idealized neural network algorithms and their physical realization in PCM hardware, facilitating the development of more efficient and reliable neuromorphic computing systems.

Market Analysis for PCM-Based Neural Networks

The global market for PCM-based neural networks is experiencing significant growth, driven by increasing demand for energy-efficient computing solutions in artificial intelligence applications. Current market valuations indicate that the neuromorphic computing sector, which includes PCM-based solutions, is projected to reach approximately 8.9 billion USD by 2025, with a compound annual growth rate exceeding 20% from 2020 to 2025.

The primary market segments for PCM-based neural networks include edge computing devices, data centers, autonomous vehicles, and advanced robotics. Edge computing represents the fastest-growing segment due to the increasing need for real-time processing capabilities in IoT devices and mobile applications. The ability of PCM-based solutions to perform computations with significantly lower power consumption compared to traditional CMOS-based processors makes them particularly attractive for battery-powered edge devices.

Market research indicates that North America currently holds the largest market share at approximately 42%, followed by Asia-Pacific at 31% and Europe at 24%. However, the Asia-Pacific region is expected to witness the highest growth rate over the next five years, primarily driven by substantial investments in AI infrastructure in China, Japan, and South Korea.

Key market drivers include the exponential growth in data generation requiring efficient processing solutions, increasing adoption of AI across industries, and the push for more energy-efficient computing architectures. The limitations of traditional von Neumann architectures in handling AI workloads efficiently have created a significant market opportunity for alternative computing paradigms like PCM-based neural networks.

Customer segments show varying adoption patterns, with research institutions and technology giants leading early adoption, while broader commercial applications are expected to follow as the technology matures. Financial services, healthcare, and automotive sectors demonstrate the highest willingness to invest in these advanced computing solutions due to their data-intensive operations and need for real-time processing capabilities.

Market barriers include concerns about PCM reliability and endurance, particularly regarding the nonidealities that affect training accuracy. The modeling of these nonidealities for accurate network training simulations represents a critical factor influencing market adoption rates. Additionally, competition from alternative neuromorphic computing technologies such as RRAM and MRAM creates a fragmented market landscape.

Industry analysts predict that successful commercialization of PCM-based neural networks will depend heavily on addressing these nonidealities through improved modeling techniques, which would significantly expand the addressable market by enabling more reliable and accurate implementations across diverse application domains.

The primary market segments for PCM-based neural networks include edge computing devices, data centers, autonomous vehicles, and advanced robotics. Edge computing represents the fastest-growing segment due to the increasing need for real-time processing capabilities in IoT devices and mobile applications. The ability of PCM-based solutions to perform computations with significantly lower power consumption compared to traditional CMOS-based processors makes them particularly attractive for battery-powered edge devices.

Market research indicates that North America currently holds the largest market share at approximately 42%, followed by Asia-Pacific at 31% and Europe at 24%. However, the Asia-Pacific region is expected to witness the highest growth rate over the next five years, primarily driven by substantial investments in AI infrastructure in China, Japan, and South Korea.

Key market drivers include the exponential growth in data generation requiring efficient processing solutions, increasing adoption of AI across industries, and the push for more energy-efficient computing architectures. The limitations of traditional von Neumann architectures in handling AI workloads efficiently have created a significant market opportunity for alternative computing paradigms like PCM-based neural networks.

Customer segments show varying adoption patterns, with research institutions and technology giants leading early adoption, while broader commercial applications are expected to follow as the technology matures. Financial services, healthcare, and automotive sectors demonstrate the highest willingness to invest in these advanced computing solutions due to their data-intensive operations and need for real-time processing capabilities.

Market barriers include concerns about PCM reliability and endurance, particularly regarding the nonidealities that affect training accuracy. The modeling of these nonidealities for accurate network training simulations represents a critical factor influencing market adoption rates. Additionally, competition from alternative neuromorphic computing technologies such as RRAM and MRAM creates a fragmented market landscape.

Industry analysts predict that successful commercialization of PCM-based neural networks will depend heavily on addressing these nonidealities through improved modeling techniques, which would significantly expand the addressable market by enabling more reliable and accurate implementations across diverse application domains.

PCM Nonidealities: Current Challenges

Phase change memory (PCM) technology has emerged as a promising candidate for neuromorphic computing applications due to its non-volatile nature, high density, and analog storage capabilities. However, several non-idealities inherent to PCM devices present significant challenges for accurate network training simulations. The primary non-ideality is device-to-device variability, where nominally identical PCM cells exhibit different resistance characteristics due to manufacturing process variations, resulting in inconsistent weight representations across the network.

Temporal drift represents another critical challenge, as the resistance of PCM cells gradually increases over time following a power-law behavior. This phenomenon causes weight values to shift unpredictably during operation, introducing errors that compound over extended training periods. The magnitude of drift varies with programming conditions and environmental factors, making it particularly difficult to model accurately in large-scale simulations.

Limited endurance poses a substantial obstacle for training applications that require numerous weight updates. PCM cells typically withstand 10^6 to 10^8 programming cycles before failure, which falls short of the requirements for deep learning models that may need billions of weight updates during training. This limitation necessitates sophisticated wear-leveling algorithms or hybrid architectures that are computationally expensive to simulate.

Read noise introduces stochasticity during weight retrieval operations, as the measured resistance values fluctuate around their true values. This variability compounds with other non-idealities, creating a complex error landscape that impacts training convergence. Additionally, the asymmetric and nonlinear conductance response to programming pulses makes it challenging to implement precise weight updates required by gradient-based learning algorithms.

The limited dynamic range of PCM devices constrains the precision of weight representation, typically offering only 4-6 bits of effective resolution. This quantization effect introduces significant errors during backpropagation, particularly for networks requiring high precision. Furthermore, the programming energy increases exponentially for finer conductance states, creating an unfavorable trade-off between precision and power efficiency.

Temperature sensitivity further complicates modeling efforts, as PCM resistance characteristics vary significantly with operating temperature. This dependency introduces additional variability in deployed systems operating across different environmental conditions. Current simulation frameworks struggle to incorporate these temperature effects accurately, leading to discrepancies between simulated and real-world performance.

Addressing these challenges requires sophisticated multi-physics models that capture the interplay between electrical, thermal, and material properties of PCM devices. However, such comprehensive models are computationally intensive, creating a tension between simulation accuracy and computational efficiency that remains unresolved in current research.

Temporal drift represents another critical challenge, as the resistance of PCM cells gradually increases over time following a power-law behavior. This phenomenon causes weight values to shift unpredictably during operation, introducing errors that compound over extended training periods. The magnitude of drift varies with programming conditions and environmental factors, making it particularly difficult to model accurately in large-scale simulations.

Limited endurance poses a substantial obstacle for training applications that require numerous weight updates. PCM cells typically withstand 10^6 to 10^8 programming cycles before failure, which falls short of the requirements for deep learning models that may need billions of weight updates during training. This limitation necessitates sophisticated wear-leveling algorithms or hybrid architectures that are computationally expensive to simulate.

Read noise introduces stochasticity during weight retrieval operations, as the measured resistance values fluctuate around their true values. This variability compounds with other non-idealities, creating a complex error landscape that impacts training convergence. Additionally, the asymmetric and nonlinear conductance response to programming pulses makes it challenging to implement precise weight updates required by gradient-based learning algorithms.

The limited dynamic range of PCM devices constrains the precision of weight representation, typically offering only 4-6 bits of effective resolution. This quantization effect introduces significant errors during backpropagation, particularly for networks requiring high precision. Furthermore, the programming energy increases exponentially for finer conductance states, creating an unfavorable trade-off between precision and power efficiency.

Temperature sensitivity further complicates modeling efforts, as PCM resistance characteristics vary significantly with operating temperature. This dependency introduces additional variability in deployed systems operating across different environmental conditions. Current simulation frameworks struggle to incorporate these temperature effects accurately, leading to discrepancies between simulated and real-world performance.

Addressing these challenges requires sophisticated multi-physics models that capture the interplay between electrical, thermal, and material properties of PCM devices. However, such comprehensive models are computationally intensive, creating a tension between simulation accuracy and computational efficiency that remains unresolved in current research.

Current PCM Nonideality Modeling Approaches

01 Multi-level cell programming techniques for PCM accuracy

Phase Change Memory (PCM) accuracy can be improved through multi-level cell programming techniques. These methods involve precise control of resistance states in PCM cells to store multiple bits per cell. By implementing sophisticated programming algorithms that carefully manage the crystallization process, the accuracy and reliability of data storage can be significantly enhanced. These techniques often include iterative programming approaches and verification steps to ensure the desired resistance levels are achieved consistently.- Multi-level cell programming techniques for PCM accuracy: Phase Change Memory (PCM) accuracy can be improved through multi-level cell programming techniques. These methods involve precise control of resistance states in PCM cells to store multiple bits per cell. By implementing sophisticated programming algorithms that carefully manage the crystallization process, the accuracy and reliability of data storage can be significantly enhanced. These techniques often include iterative programming approaches and verification steps to ensure precise resistance levels are achieved.

- Temperature compensation methods for PCM: Temperature fluctuations can significantly affect the accuracy of Phase Change Memory devices. Various temperature compensation methods have been developed to maintain consistent performance across different operating conditions. These include temperature-aware programming schemes, adaptive read reference techniques, and thermal management systems that adjust operational parameters based on temperature measurements. By implementing these compensation methods, PCM devices can maintain high accuracy and reliability even in environments with varying temperatures.

- Material composition optimization for PCM accuracy: The accuracy of Phase Change Memory devices can be significantly improved through optimization of material compositions. By carefully engineering the chalcogenide materials used in PCM cells, researchers have developed compositions that offer more distinct resistance states, better stability, and improved endurance. These optimized materials provide clearer transitions between amorphous and crystalline states, reducing read errors and improving overall accuracy. Advanced doping techniques and multi-layer structures further enhance the precision of state transitions.

- Error correction and detection systems for PCM: Error correction and detection systems play a crucial role in enhancing the accuracy of Phase Change Memory. These systems employ sophisticated algorithms to identify and correct errors that may occur during read and write operations. Advanced error correction codes (ECC), data verification techniques, and redundancy schemes help maintain data integrity despite the inherent variability in PCM cells. By implementing these error management systems, the effective accuracy of PCM devices can be significantly improved, making them suitable for applications requiring high reliability.

- Novel cell architectures for improved PCM accuracy: Innovative cell architectures have been developed to enhance the accuracy of Phase Change Memory devices. These designs include confined cell structures, selector devices for precise current control, and novel electrode configurations that improve thermal efficiency. By optimizing the physical structure of PCM cells, these architectures provide more uniform heating and cooling processes, resulting in more consistent state transitions. Some designs also incorporate multiple phase change elements within a single cell to improve reliability and precision in multi-level storage applications.

02 Temperature compensation methods for PCM

Temperature fluctuations can significantly affect the accuracy of Phase Change Memory devices. Various temperature compensation methods have been developed to maintain consistent performance across different operating conditions. These include temperature-aware programming schemes, adaptive read algorithms that adjust threshold values based on temperature measurements, and specialized circuit designs that can compensate for temperature-induced drift in resistance values. Such methods help ensure reliable data storage and retrieval regardless of environmental temperature variations.Expand Specific Solutions03 Drift compensation and error correction for PCM

Resistance drift in Phase Change Memory cells can lead to accuracy issues over time. Advanced drift compensation techniques and error correction methods have been developed to address this challenge. These include predictive models that anticipate resistance changes, adaptive read thresholds that adjust based on cell age, and sophisticated error correction codes specifically designed for PCM characteristics. By implementing these techniques, the long-term accuracy and data retention capabilities of PCM devices can be substantially improved.Expand Specific Solutions04 Novel cell structures and materials for enhanced PCM accuracy

Innovative cell structures and material compositions can significantly improve the accuracy of Phase Change Memory devices. These include confined cell geometries that provide better thermal isolation, doped phase change materials with enhanced stability characteristics, and multi-layer structures that offer more precise control over the phase change process. By optimizing the physical design and material properties of PCM cells, manufacturers can achieve more consistent resistance states and improved switching reliability, leading to higher overall accuracy.Expand Specific Solutions05 Advanced sensing and readout circuits for PCM

Specialized sensing and readout circuits play a crucial role in achieving high accuracy in Phase Change Memory systems. These circuits include precision current sources for reliable cell programming, sensitive amplifiers for accurate resistance measurement, and advanced comparator designs for reliable state detection. Additionally, calibration techniques and reference cell architectures help compensate for process variations and device non-uniformities. By implementing these advanced circuit techniques, PCM systems can achieve higher read accuracy and better distinguish between different resistance states.Expand Specific Solutions

Leading Organizations in PCM Research

The PCM nonidealities modeling market is currently in a growth phase, with increasing demand for accurate network training simulations across various industries. The competitive landscape features established technology giants like Siemens AG, Samsung Electronics, and Robert Bosch GmbH leading commercial applications, while research institutions such as Hefei University of Technology and Southeast University drive academic innovation. The technology is approaching maturity in power grid applications, evidenced by State Grid Corp. of China and Guangdong Power Grid's implementations, but remains developing in automotive and telecommunications sectors where Nissan and Orange SA are making significant investments. MediaTek and Applied Materials are advancing semiconductor-specific modeling solutions, creating a diverse ecosystem of approximately $3.5 billion that bridges hardware limitations and software optimization.

Siemens AG

Technical Solution: Siemens has developed a comprehensive PCM nonideality modeling framework focused on industrial automation and control systems applications. Their approach addresses the unique challenges of using PCM in mission-critical industrial environments where reliability and predictability are paramount. Siemens' modeling incorporates detailed characterization of PCM behavior under varying temperature and operating conditions typical in industrial settings. Their framework includes models for resistance drift, read/write noise, and endurance limitations, with particular attention to long-term stability requirements of industrial systems. Siemens has integrated these models into their digital twin simulation environment, allowing engineers to accurately predict how PCM-based neural networks will perform over the extended lifecycle of industrial equipment. A key innovation in their approach is the development of fault-tolerance techniques that maintain neural network performance even as PCM cells degrade over time. Their modeling framework supports hardware-aware training methodologies that optimize neural network weights to be robust against PCM nonidealities while maintaining inference accuracy for critical control applications.

Strengths: Siemens' models excel in addressing the long-term reliability requirements critical for industrial applications with extended deployment lifetimes. Their approach integrates well with existing industrial automation frameworks. Weaknesses: Their modeling approach may be overly conservative for consumer applications where maximum performance is prioritized over long-term stability.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has developed advanced PCM (Phase Change Memory) modeling techniques that accurately capture nonidealities for network training simulations. Their approach incorporates drift compensation algorithms that address resistance drift issues in PCM cells over time. Samsung's solution includes a comprehensive model that accounts for read noise, write variability, and endurance limitations of PCM devices. They've implemented a multi-level cell (MLC) architecture that enables storing multiple bits per cell while maintaining accuracy through sophisticated error correction techniques. Their modeling framework integrates with neural network training pipelines, allowing for hardware-aware training that anticipates and compensates for PCM-specific behaviors. Samsung has demonstrated this technology in neuromorphic computing applications, showing how accurate PCM modeling can lead to more efficient AI hardware implementations with reduced power consumption compared to conventional DRAM-based systems.

Strengths: Samsung's extensive manufacturing expertise in memory technologies provides them with deep insights into real-world PCM behavior. Their models benefit from direct access to hardware characterization data. Weaknesses: Their modeling approach may be optimized specifically for Samsung's PCM implementations, potentially limiting applicability to other manufacturers' devices.

Key PCM Simulation Technologies

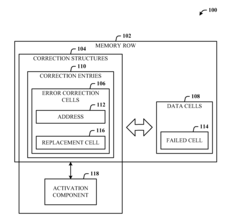

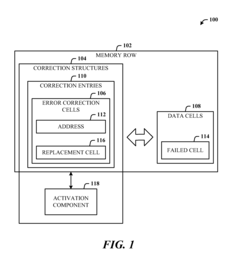

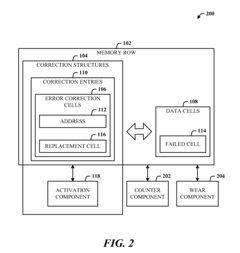

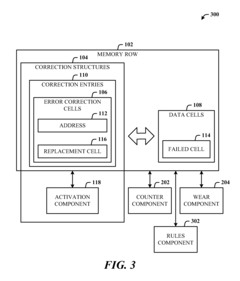

Error correcting pointers for non-volatile storage

PatentActiveUS20110296258A1

Innovation

- The implementation of error correcting pointers (ECPs) within a memory row that point to failed cells and pair them with replacement cells, along with wear-leveling mechanisms, to correct faults and extend memory lifetimes without significant performance impact or additional power consumption.

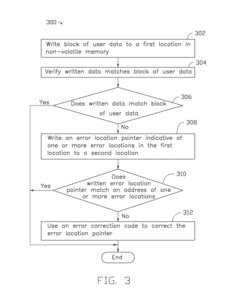

Error location pointers for nvm

PatentActiveUS20170116060A1

Innovation

- A method that writes data to a first location in non-volatile memory, verifies the written data, and if errors are found, writes an error location pointer to a second location, ensuring the pointer's integrity, thereby increasing data rate and reducing read latency and data loss.

Hardware-Software Co-Design Strategies

Hardware-software co-design approaches are essential for addressing the challenges posed by Phase Change Memory (PCM) nonidealities in neural network training simulations. Effective co-design strategies bridge the gap between PCM's physical characteristics and the algorithmic requirements of neural network training. These strategies typically involve simultaneous optimization of hardware configurations and software algorithms to mitigate the impact of PCM nonidealities.

At the hardware level, circuit-level techniques can be implemented to compensate for PCM's nonlinear conductance response. Adaptive programming schemes that adjust write pulses based on real-time resistance measurements help achieve more precise weight updates. Additionally, specialized peripheral circuits can be designed to handle the unique characteristics of PCM cells, including drift compensation circuits and read-verify-write schemes that improve the accuracy of weight storage.

On the software side, algorithm modifications can significantly enhance training robustness against PCM nonidealities. Training algorithms can be adapted to incorporate awareness of device-specific behaviors, such as implementing stochastic rounding techniques that account for programming variability. Regularization methods specifically designed for PCM-based implementations help maintain network performance despite device limitations. Furthermore, quantization-aware training approaches can be tailored to match the discrete conductance levels available in PCM arrays.

The co-design process often involves iterative optimization using hardware-in-the-loop simulations. These simulations incorporate detailed PCM device models into the training process, allowing developers to evaluate the impact of various compensation techniques in real-time. This approach enables fine-tuning of both hardware parameters and software algorithms simultaneously, leading to more effective solutions than addressing either aspect in isolation.

Recent advances in this field include the development of hybrid architectures that strategically distribute computational tasks between PCM arrays and conventional digital processors. Critical operations that are particularly sensitive to PCM nonidealities can be offloaded to digital hardware, while leveraging PCM's advantages for other aspects of neural network computation. This balanced approach maximizes system performance while minimizing the impact of device limitations.

Successful hardware-software co-design strategies also incorporate feedback mechanisms that continuously monitor PCM device characteristics during operation. These mechanisms enable dynamic adjustment of both hardware parameters and software algorithms to adapt to changing device behaviors over time, such as resistance drift and endurance degradation. This adaptive approach ensures sustained performance throughout the system's operational lifetime.

At the hardware level, circuit-level techniques can be implemented to compensate for PCM's nonlinear conductance response. Adaptive programming schemes that adjust write pulses based on real-time resistance measurements help achieve more precise weight updates. Additionally, specialized peripheral circuits can be designed to handle the unique characteristics of PCM cells, including drift compensation circuits and read-verify-write schemes that improve the accuracy of weight storage.

On the software side, algorithm modifications can significantly enhance training robustness against PCM nonidealities. Training algorithms can be adapted to incorporate awareness of device-specific behaviors, such as implementing stochastic rounding techniques that account for programming variability. Regularization methods specifically designed for PCM-based implementations help maintain network performance despite device limitations. Furthermore, quantization-aware training approaches can be tailored to match the discrete conductance levels available in PCM arrays.

The co-design process often involves iterative optimization using hardware-in-the-loop simulations. These simulations incorporate detailed PCM device models into the training process, allowing developers to evaluate the impact of various compensation techniques in real-time. This approach enables fine-tuning of both hardware parameters and software algorithms simultaneously, leading to more effective solutions than addressing either aspect in isolation.

Recent advances in this field include the development of hybrid architectures that strategically distribute computational tasks between PCM arrays and conventional digital processors. Critical operations that are particularly sensitive to PCM nonidealities can be offloaded to digital hardware, while leveraging PCM's advantages for other aspects of neural network computation. This balanced approach maximizes system performance while minimizing the impact of device limitations.

Successful hardware-software co-design strategies also incorporate feedback mechanisms that continuously monitor PCM device characteristics during operation. These mechanisms enable dynamic adjustment of both hardware parameters and software algorithms to adapt to changing device behaviors over time, such as resistance drift and endurance degradation. This adaptive approach ensures sustained performance throughout the system's operational lifetime.

Energy Efficiency Considerations

Energy efficiency has emerged as a critical consideration in the implementation of Phase Change Memory (PCM) for neural network training simulations. The non-volatile nature of PCM offers significant power advantages over conventional DRAM-based solutions, particularly in reducing static power consumption during idle periods. When modeling PCM nonidealities for accurate network training simulations, energy consumption patterns must be carefully analyzed across different operational phases including read, write, and retention operations.

PCM devices typically consume 10-100 times less energy during read operations compared to write operations, creating an asymmetric energy profile that must be accounted for in training algorithms. This asymmetry becomes particularly important when considering the frequent weight updates that occur during neural network training. Innovative techniques such as sparse updates and approximate computing can be leveraged to minimize the energy impact of these write-intensive operations while maintaining acceptable accuracy levels.

Thermal management represents another crucial energy efficiency consideration when modeling PCM nonidealities. The phase change process inherently involves temperature transitions, and inadequate thermal modeling can lead to both accuracy degradation and excessive energy consumption. Recent research indicates that optimized pulse shapes for programming PCM cells can reduce energy requirements by up to 30% while maintaining reliability metrics. These energy-optimized programming schemes must be incorporated into simulation frameworks to accurately predict real-world performance.

The endurance-energy tradeoff presents a complex optimization challenge in PCM-based neural network implementations. Higher programming currents may improve reliability but at the cost of increased energy consumption and accelerated device wear. Sophisticated models must account for this relationship, particularly when simulating long-running training processes where cumulative energy consumption becomes significant. Some research groups have demonstrated adaptive programming schemes that dynamically adjust energy levels based on cell-specific characteristics, achieving up to 40% energy savings compared to fixed programming approaches.

When scaling to large neural network architectures, the peripheral circuitry surrounding PCM arrays contributes substantially to the overall energy footprint. Accurate simulation frameworks must model not only the PCM cells themselves but also the energy consumed by sensing amplifiers, write drivers, and address decoders. Recent architectural innovations such as in-memory computing paradigms can reduce data movement energy by performing certain operations directly within the PCM array, potentially offering 5-10x improvements in energy efficiency for specific neural network operations.

PCM devices typically consume 10-100 times less energy during read operations compared to write operations, creating an asymmetric energy profile that must be accounted for in training algorithms. This asymmetry becomes particularly important when considering the frequent weight updates that occur during neural network training. Innovative techniques such as sparse updates and approximate computing can be leveraged to minimize the energy impact of these write-intensive operations while maintaining acceptable accuracy levels.

Thermal management represents another crucial energy efficiency consideration when modeling PCM nonidealities. The phase change process inherently involves temperature transitions, and inadequate thermal modeling can lead to both accuracy degradation and excessive energy consumption. Recent research indicates that optimized pulse shapes for programming PCM cells can reduce energy requirements by up to 30% while maintaining reliability metrics. These energy-optimized programming schemes must be incorporated into simulation frameworks to accurately predict real-world performance.

The endurance-energy tradeoff presents a complex optimization challenge in PCM-based neural network implementations. Higher programming currents may improve reliability but at the cost of increased energy consumption and accelerated device wear. Sophisticated models must account for this relationship, particularly when simulating long-running training processes where cumulative energy consumption becomes significant. Some research groups have demonstrated adaptive programming schemes that dynamically adjust energy levels based on cell-specific characteristics, achieving up to 40% energy savings compared to fixed programming approaches.

When scaling to large neural network architectures, the peripheral circuitry surrounding PCM arrays contributes substantially to the overall energy footprint. Accurate simulation frameworks must model not only the PCM cells themselves but also the energy consumed by sensing amplifiers, write drivers, and address decoders. Recent architectural innovations such as in-memory computing paradigms can reduce data movement energy by performing certain operations directly within the PCM array, potentially offering 5-10x improvements in energy efficiency for specific neural network operations.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!