Noise Characterization In PCM Arrays: Measurement Methods And Impacts

AUG 29, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

PCM Noise Characterization Background and Objectives

Phase Change Memory (PCM) technology has emerged as a promising non-volatile memory solution over the past two decades, offering advantages in scalability, endurance, and power consumption compared to traditional memory technologies. The evolution of PCM has been marked by significant advancements in material science, device architecture, and manufacturing processes, enabling its integration into various computing systems and storage applications.

The noise characteristics in PCM arrays represent a critical aspect of this technology that directly impacts reliability, performance, and scalability. Historically, as PCM cell dimensions have decreased to accommodate higher storage densities, the signal-to-noise ratio has become increasingly challenging to maintain. This evolution has necessitated sophisticated noise characterization methodologies to ensure reliable operation across diverse operating conditions.

Current technological trends indicate a growing interest in multi-level cell (MLC) PCM implementations, which require even more precise noise characterization due to the reduced margins between resistance states. Additionally, the integration of PCM in neuromorphic computing applications has introduced new requirements for understanding noise behavior in analog computing contexts.

The primary objective of this technical research is to comprehensively analyze the measurement methods for noise characterization in PCM arrays and evaluate their impacts on device performance and reliability. Specifically, we aim to identify the predominant noise sources in current PCM implementations, assess the effectiveness of existing measurement techniques, and determine how various noise components affect read/write operations across different application scenarios.

Furthermore, this research seeks to establish standardized methodologies for noise measurement that can be consistently applied across different PCM architectures and manufacturing processes. By developing a deeper understanding of noise mechanisms, we intend to provide insights that could lead to improved circuit designs, more robust error correction schemes, and enhanced reliability models for PCM-based systems.

The scope of this investigation encompasses both intrinsic noise sources (such as resistance drift, 1/f noise, and random telegraph noise) and extrinsic factors (including read/write circuitry noise, thermal fluctuations, and cross-talk between adjacent cells). Through systematic analysis of these noise components, we aim to create a comprehensive framework for noise characterization that supports the continued advancement of PCM technology toward higher densities, improved performance, and broader application domains.

This research is particularly timely as PCM transitions from specialized applications to mainstream computing environments, where reliability requirements become increasingly stringent and the economic implications of noise-induced failures grow more significant.

The noise characteristics in PCM arrays represent a critical aspect of this technology that directly impacts reliability, performance, and scalability. Historically, as PCM cell dimensions have decreased to accommodate higher storage densities, the signal-to-noise ratio has become increasingly challenging to maintain. This evolution has necessitated sophisticated noise characterization methodologies to ensure reliable operation across diverse operating conditions.

Current technological trends indicate a growing interest in multi-level cell (MLC) PCM implementations, which require even more precise noise characterization due to the reduced margins between resistance states. Additionally, the integration of PCM in neuromorphic computing applications has introduced new requirements for understanding noise behavior in analog computing contexts.

The primary objective of this technical research is to comprehensively analyze the measurement methods for noise characterization in PCM arrays and evaluate their impacts on device performance and reliability. Specifically, we aim to identify the predominant noise sources in current PCM implementations, assess the effectiveness of existing measurement techniques, and determine how various noise components affect read/write operations across different application scenarios.

Furthermore, this research seeks to establish standardized methodologies for noise measurement that can be consistently applied across different PCM architectures and manufacturing processes. By developing a deeper understanding of noise mechanisms, we intend to provide insights that could lead to improved circuit designs, more robust error correction schemes, and enhanced reliability models for PCM-based systems.

The scope of this investigation encompasses both intrinsic noise sources (such as resistance drift, 1/f noise, and random telegraph noise) and extrinsic factors (including read/write circuitry noise, thermal fluctuations, and cross-talk between adjacent cells). Through systematic analysis of these noise components, we aim to create a comprehensive framework for noise characterization that supports the continued advancement of PCM technology toward higher densities, improved performance, and broader application domains.

This research is particularly timely as PCM transitions from specialized applications to mainstream computing environments, where reliability requirements become increasingly stringent and the economic implications of noise-induced failures grow more significant.

Market Demand Analysis for Low-Noise PCM Memory Solutions

The global memory market is witnessing a significant shift towards advanced non-volatile memory solutions, with Phase Change Memory (PCM) emerging as a promising technology. Current market analysis indicates that the demand for low-noise PCM solutions is primarily driven by data centers, edge computing applications, and the burgeoning Internet of Things (IoT) ecosystem. These sectors require memory technologies that can deliver reliability, speed, and energy efficiency simultaneously.

Data centers are experiencing exponential growth in computational demands, with global data creation projected to reach 175 zettabytes by 2025. This massive data explosion necessitates memory solutions that can handle high-density storage while maintaining signal integrity. Low-noise PCM arrays address this critical need by offering superior resistance to interference, thereby enhancing data reliability in high-density storage environments.

The automotive industry represents another substantial market for low-noise PCM solutions. Advanced driver-assistance systems (ADAS) and autonomous vehicles require memory components that can operate reliably under varying temperature conditions and electromagnetic interference. The automotive memory market segment is expected to grow at a compound annual growth rate of 23% through 2026, with noise-resistant memory technologies positioned to capture a significant portion of this growth.

Consumer electronics manufacturers are increasingly incorporating PCM technology into smartphones, tablets, and wearable devices. These applications benefit from PCM's fast read/write speeds and non-volatility, but are particularly sensitive to noise issues that can compromise user experience. Market research indicates that consumers are willing to pay premium prices for devices offering improved performance and reliability, creating a substantial value proposition for low-noise PCM solutions.

Industrial IoT applications present another expanding market opportunity. Manufacturing systems, smart grid infrastructure, and industrial automation rely on memory components that can function reliably in electrically noisy environments. The industrial memory market is projected to expand as Industry 4.0 initiatives accelerate globally, with particular emphasis on components that maintain data integrity under challenging operational conditions.

Healthcare technology represents an emerging but rapidly growing market segment for low-noise PCM solutions. Medical devices, particularly implantable and wearable health monitors, require memory components that can operate with minimal interference in environments with multiple electronic devices. The stringent regulatory requirements in healthcare further emphasize the need for highly reliable, low-noise memory solutions.

The geographical distribution of market demand shows concentration in North America and Asia-Pacific regions, with Europe following closely. China and Taiwan lead in manufacturing capacity, while North American companies dominate in intellectual property and design innovation for noise reduction techniques in PCM arrays.

Data centers are experiencing exponential growth in computational demands, with global data creation projected to reach 175 zettabytes by 2025. This massive data explosion necessitates memory solutions that can handle high-density storage while maintaining signal integrity. Low-noise PCM arrays address this critical need by offering superior resistance to interference, thereby enhancing data reliability in high-density storage environments.

The automotive industry represents another substantial market for low-noise PCM solutions. Advanced driver-assistance systems (ADAS) and autonomous vehicles require memory components that can operate reliably under varying temperature conditions and electromagnetic interference. The automotive memory market segment is expected to grow at a compound annual growth rate of 23% through 2026, with noise-resistant memory technologies positioned to capture a significant portion of this growth.

Consumer electronics manufacturers are increasingly incorporating PCM technology into smartphones, tablets, and wearable devices. These applications benefit from PCM's fast read/write speeds and non-volatility, but are particularly sensitive to noise issues that can compromise user experience. Market research indicates that consumers are willing to pay premium prices for devices offering improved performance and reliability, creating a substantial value proposition for low-noise PCM solutions.

Industrial IoT applications present another expanding market opportunity. Manufacturing systems, smart grid infrastructure, and industrial automation rely on memory components that can function reliably in electrically noisy environments. The industrial memory market is projected to expand as Industry 4.0 initiatives accelerate globally, with particular emphasis on components that maintain data integrity under challenging operational conditions.

Healthcare technology represents an emerging but rapidly growing market segment for low-noise PCM solutions. Medical devices, particularly implantable and wearable health monitors, require memory components that can operate with minimal interference in environments with multiple electronic devices. The stringent regulatory requirements in healthcare further emphasize the need for highly reliable, low-noise memory solutions.

The geographical distribution of market demand shows concentration in North America and Asia-Pacific regions, with Europe following closely. China and Taiwan lead in manufacturing capacity, while North American companies dominate in intellectual property and design innovation for noise reduction techniques in PCM arrays.

Current Challenges in PCM Array Noise Measurement

Despite significant advancements in Phase Change Memory (PCM) technology, noise characterization in PCM arrays remains a formidable challenge that impedes both research progress and commercial deployment. Current measurement methodologies struggle with several fundamental limitations that affect the accuracy and reliability of noise assessments in these complex memory structures.

One of the primary challenges is the multi-level noise coupling that occurs within densely packed PCM arrays. As array densities increase to meet storage demands, the proximity between cells creates complex electromagnetic interference patterns that are difficult to isolate and quantify. Traditional noise measurement techniques developed for single-cell characterization fail to capture these array-specific noise interactions, leading to incomplete noise profiles.

Temporal variations present another significant obstacle. PCM cells exhibit drift phenomena where resistance values change over time due to structural relaxation of the amorphous phase. Current measurement systems lack the capability to continuously monitor these temporal fluctuations while simultaneously characterizing other noise components, resulting in snapshot measurements that may not represent the dynamic noise landscape of operational arrays.

The temperature dependence of noise characteristics in PCM arrays further complicates measurement efforts. PCM operation inherently involves significant temperature gradients during programming and reading operations. Existing measurement tools struggle to account for these thermal variations, which can dramatically alter noise profiles across the array. The lack of in-situ temperature-controlled measurement capabilities represents a critical gap in current methodologies.

Signal-to-noise ratio challenges become particularly acute when measuring noise in multi-bit PCM cells. As the industry pushes toward multi-level cell configurations to increase storage density, the resistance windows between adjacent states narrow significantly. Current instrumentation often lacks the sensitivity to reliably distinguish between intrinsic cell noise and measurement system noise at these reduced margins.

Parasitic elements in the measurement path introduce additional complications. The access devices, interconnects, and sensing circuitry all contribute their own noise signatures, which can mask or distort the intrinsic PCM cell noise characteristics. Current deconvolution techniques are insufficient for accurately separating these various noise sources, particularly at high frequencies relevant to modern high-speed memory operations.

Finally, there exists a fundamental trade-off between measurement throughput and accuracy. Comprehensive noise characterization requires extensive statistical sampling across multiple cells, conditions, and time periods. However, current measurement systems that offer high precision typically sacrifice throughput, making array-level noise studies prohibitively time-consuming for practical technology development cycles.

One of the primary challenges is the multi-level noise coupling that occurs within densely packed PCM arrays. As array densities increase to meet storage demands, the proximity between cells creates complex electromagnetic interference patterns that are difficult to isolate and quantify. Traditional noise measurement techniques developed for single-cell characterization fail to capture these array-specific noise interactions, leading to incomplete noise profiles.

Temporal variations present another significant obstacle. PCM cells exhibit drift phenomena where resistance values change over time due to structural relaxation of the amorphous phase. Current measurement systems lack the capability to continuously monitor these temporal fluctuations while simultaneously characterizing other noise components, resulting in snapshot measurements that may not represent the dynamic noise landscape of operational arrays.

The temperature dependence of noise characteristics in PCM arrays further complicates measurement efforts. PCM operation inherently involves significant temperature gradients during programming and reading operations. Existing measurement tools struggle to account for these thermal variations, which can dramatically alter noise profiles across the array. The lack of in-situ temperature-controlled measurement capabilities represents a critical gap in current methodologies.

Signal-to-noise ratio challenges become particularly acute when measuring noise in multi-bit PCM cells. As the industry pushes toward multi-level cell configurations to increase storage density, the resistance windows between adjacent states narrow significantly. Current instrumentation often lacks the sensitivity to reliably distinguish between intrinsic cell noise and measurement system noise at these reduced margins.

Parasitic elements in the measurement path introduce additional complications. The access devices, interconnects, and sensing circuitry all contribute their own noise signatures, which can mask or distort the intrinsic PCM cell noise characteristics. Current deconvolution techniques are insufficient for accurately separating these various noise sources, particularly at high frequencies relevant to modern high-speed memory operations.

Finally, there exists a fundamental trade-off between measurement throughput and accuracy. Comprehensive noise characterization requires extensive statistical sampling across multiple cells, conditions, and time periods. However, current measurement systems that offer high precision typically sacrifice throughput, making array-level noise studies prohibitively time-consuming for practical technology development cycles.

Established Noise Characterization Methods for PCM Arrays

01 Noise reduction techniques in PCM arrays

Various noise reduction techniques can be applied to Pulse Code Modulation (PCM) arrays to improve signal quality. These techniques include filtering algorithms, signal processing methods, and specialized circuit designs that minimize interference and background noise. By implementing these noise reduction strategies, the signal-to-noise ratio in PCM arrays can be significantly improved, resulting in clearer data transmission and more accurate signal reproduction.- Noise reduction techniques in PCM arrays: Various techniques can be employed to reduce noise in PCM (Phase Change Memory) arrays. These include implementing specialized filtering algorithms, using differential signaling, and employing noise cancellation circuits. These methods help to improve the signal-to-noise ratio in PCM arrays, resulting in more reliable data storage and retrieval operations.

- Thermal management for PCM array noise control: Thermal management is crucial for controlling noise in PCM arrays as temperature fluctuations can affect the phase change process and introduce noise. Techniques include implementing thermal isolation structures, temperature compensation circuits, and active cooling systems. Proper thermal management ensures stable operation of PCM arrays and minimizes noise caused by thermal variations.

- Signal processing algorithms for PCM array noise mitigation: Advanced signal processing algorithms can be used to mitigate noise in PCM arrays. These include adaptive filtering, error correction codes, and machine learning-based noise prediction. By implementing these algorithms, the system can identify and filter out noise patterns, improving the accuracy of data reading and writing operations in PCM arrays.

- Circuit design optimization for PCM array noise reduction: Optimizing circuit design is essential for reducing noise in PCM arrays. This includes using low-noise amplifiers, implementing proper grounding techniques, and designing specialized sensing circuits. These circuit optimizations help to minimize electrical interference and improve the signal integrity in PCM array operations.

- Multi-level cell architecture for noise-resistant PCM arrays: Multi-level cell architectures can be implemented to make PCM arrays more resistant to noise. These architectures use multiple resistance states to represent data, providing greater separation between states and thus higher noise immunity. Additionally, specialized reading and writing protocols can be employed to ensure reliable operation even in noisy environments.

02 Thermal management in PCM arrays

Thermal noise in PCM (Phase Change Memory) arrays can be managed through specialized cooling systems and thermal isolation techniques. These approaches help maintain optimal operating temperatures, reducing thermal-induced noise that can affect data integrity. Advanced materials and structural designs can be implemented to dissipate heat efficiently and prevent thermal interference between array elements.Expand Specific Solutions03 PCM array architecture for noise immunity

Specific architectural designs for PCM arrays can inherently reduce susceptibility to noise. These designs include optimized layout patterns, shielding structures, and isolation techniques that minimize crosstalk between array elements. By implementing noise-resistant architectures, PCM arrays can maintain signal integrity even in environments with significant electromagnetic interference.Expand Specific Solutions04 Signal processing algorithms for PCM noise reduction

Advanced signal processing algorithms can be applied to PCM array outputs to identify and remove noise components. These algorithms may include adaptive filtering, statistical noise analysis, and machine learning approaches that can distinguish between signal and noise patterns. Real-time processing techniques allow for dynamic noise suppression that adjusts to changing environmental conditions.Expand Specific Solutions05 Electromagnetic interference mitigation in PCM arrays

Electromagnetic interference (EMI) can significantly impact PCM array performance. Mitigation techniques include specialized shielding materials, grounding designs, and circuit isolation methods that protect sensitive components from external electromagnetic sources. Additionally, active cancellation systems can be implemented to counteract persistent EMI sources, ensuring stable operation in electromagnetically noisy environments.Expand Specific Solutions

Leading Companies and Research Institutions in PCM Technology

The PCM array noise characterization market is currently in a growth phase, with increasing demand driven by memory technology advancements. The competitive landscape features established test equipment manufacturers like Agilent Technologies and Hitachi High-Tech America providing sophisticated measurement solutions, alongside semiconductor leaders such as QUALCOMM, Sony, and Murata Manufacturing developing proprietary noise reduction technologies. Research institutions including Fraunhofer-Gesellschaft, Beihang University, and University of Florida contribute fundamental measurement methodologies. The market is characterized by a blend of commercial solutions and academic research, with technology maturity varying across applications. Companies like ASML and Applied Biosystems are leveraging their precision measurement expertise to address the increasingly critical noise characterization challenges as PCM arrays scale to higher densities.

Sony Group Corp.

Technical Solution: Sony has pioneered advanced noise characterization techniques for PCM arrays focused on consumer electronics applications. Their approach centers on a multi-tiered noise analysis framework that examines both intrinsic material noise and system-level noise contributions. Sony's technology incorporates specialized test structures integrated directly into PCM arrays that allow for isolation and measurement of specific noise components without disrupting normal memory operation. Their methodology includes time-domain noise analysis that can capture transient noise events during programming and reading operations, providing insights into how noise impacts write/read reliability. Sony has developed proprietary algorithms that can distinguish between reversible noise fluctuations and permanent resistance changes in PCM cells, enabling more accurate lifetime predictions. Additionally, their noise characterization system includes machine learning components that correlate specific noise signatures with particular failure modes, allowing for predictive maintenance in memory systems[5][7].

Strengths: Sony's integrated test structures provide non-invasive noise monitoring capabilities without compromising normal memory operation. Their machine learning approach enables predictive failure analysis that can improve system reliability. Weaknesses: The complex algorithms require significant computational resources for real-time implementation, potentially limiting application in power-constrained devices.

Hitachi High-Tech America, Inc.

Technical Solution: Hitachi High-Tech America has developed specialized instrumentation for PCM noise characterization focusing on high-precision measurement capabilities. Their solution features ultra-low-noise amplification systems capable of detecting sub-nanovolt noise signals in PCM cells, essential for identifying subtle resistance fluctuations that impact data retention. The company's approach incorporates temperature-controlled measurement environments (ranging from -40°C to 125°C) to characterize noise behavior across operational conditions. Their measurement methodology includes frequency-domain analysis tools that can identify specific noise signatures associated with different PCM failure mechanisms, including resistance drift, element segregation, and structural relaxation. Hitachi High-Tech's systems employ automated testing protocols that can rapidly characterize thousands of PCM cells to develop statistical models of noise distribution across arrays[2][4].

Strengths: Exceptional measurement precision with sub-nanovolt sensitivity enables detection of subtle noise phenomena that might be missed by conventional testing. Comprehensive temperature control allows for realistic operational condition testing. Weaknesses: The high-precision instrumentation requires specialized expertise to operate effectively and represents significant capital investment for memory manufacturers.

Critical Patents and Literature on PCM Noise Measurement

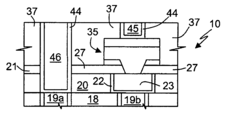

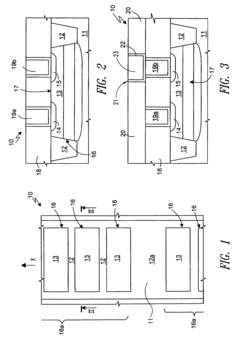

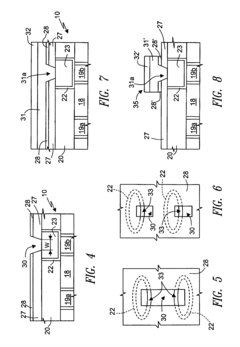

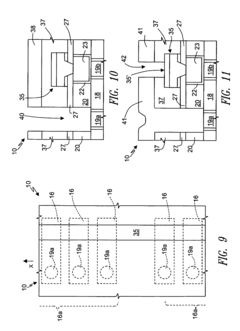

Process for manufacturing a phase change memory array in Cu-damascene technology and phase change memory array manufactured thereby

PatentInactiveUS7259040B2

Innovation

- The Cu-damascene technology is employed to simplify the etching process by substituting AlCu with copper lines, which are formed after shaping the resistive bit lines, and using a dual Damascene technique to improve thermal budget and precision, thereby overcoming the compatibility issues and increasing yield.

Reliability and Performance Impact of Noise in PCM Systems

Noise in Phase Change Memory (PCM) arrays significantly impacts both the reliability and performance of these systems. The inherent variability in PCM cell characteristics, combined with environmental factors, creates a complex noise profile that must be thoroughly understood to ensure optimal system operation.

The reliability of PCM systems is directly affected by various noise sources. Thermal noise, particularly critical due to PCM's temperature-dependent operation, can cause unintended phase transitions when thermal fluctuations exceed critical thresholds. This results in bit errors that accumulate over time, degrading data integrity. Additionally, resistance drift—where cell resistance gradually changes after programming—introduces temporal instability that complicates multi-level cell implementations.

Device-to-device variability presents another significant challenge. Manufacturing variations in cell dimensions, material composition, and contact interfaces create inconsistent resistance distributions across arrays. This variability necessitates wider sensing margins, effectively reducing the usable resistance range and limiting multi-level cell capabilities.

Performance implications of noise in PCM systems manifest in several ways. Read operations require increasingly sophisticated sensing schemes to distinguish between resistance states accurately, adding latency to data access operations. The need for error correction codes (ECC) to mitigate noise-induced errors introduces computational overhead that impacts system throughput.

Power consumption is also adversely affected by noise considerations. Higher programming currents may be required to ensure reliable state transitions despite noise, increasing energy requirements. Additionally, refresh operations become necessary to counteract resistance drift, further increasing power demands and reducing the energy efficiency advantage of PCM's non-volatile nature.

System architects must implement various compensation techniques to address these challenges. Adaptive reading thresholds that adjust based on cell age and environmental conditions can improve reliability. Advanced error correction schemes specifically designed for PCM's unique error patterns help maintain data integrity without excessive performance penalties.

The long-term reliability implications are particularly concerning for enterprise and critical applications. Noise-induced failures may manifest only after extended operation periods, making qualification testing and accelerated aging studies essential components of PCM system development and deployment strategies.

The reliability of PCM systems is directly affected by various noise sources. Thermal noise, particularly critical due to PCM's temperature-dependent operation, can cause unintended phase transitions when thermal fluctuations exceed critical thresholds. This results in bit errors that accumulate over time, degrading data integrity. Additionally, resistance drift—where cell resistance gradually changes after programming—introduces temporal instability that complicates multi-level cell implementations.

Device-to-device variability presents another significant challenge. Manufacturing variations in cell dimensions, material composition, and contact interfaces create inconsistent resistance distributions across arrays. This variability necessitates wider sensing margins, effectively reducing the usable resistance range and limiting multi-level cell capabilities.

Performance implications of noise in PCM systems manifest in several ways. Read operations require increasingly sophisticated sensing schemes to distinguish between resistance states accurately, adding latency to data access operations. The need for error correction codes (ECC) to mitigate noise-induced errors introduces computational overhead that impacts system throughput.

Power consumption is also adversely affected by noise considerations. Higher programming currents may be required to ensure reliable state transitions despite noise, increasing energy requirements. Additionally, refresh operations become necessary to counteract resistance drift, further increasing power demands and reducing the energy efficiency advantage of PCM's non-volatile nature.

System architects must implement various compensation techniques to address these challenges. Adaptive reading thresholds that adjust based on cell age and environmental conditions can improve reliability. Advanced error correction schemes specifically designed for PCM's unique error patterns help maintain data integrity without excessive performance penalties.

The long-term reliability implications are particularly concerning for enterprise and critical applications. Noise-induced failures may manifest only after extended operation periods, making qualification testing and accelerated aging studies essential components of PCM system development and deployment strategies.

Standardization Efforts for PCM Noise Measurement Protocols

The standardization of PCM (Phase Change Memory) noise measurement protocols represents a critical advancement in ensuring reliability and comparability across the industry. Currently, several international organizations are actively working to establish unified frameworks for characterizing noise in PCM arrays. The IEEE Non-Volatile Memory Standards Committee has initiated a working group specifically focused on developing standardized measurement methodologies for PCM noise characterization, with their P2408 standard draft expected to be finalized by late 2023.

JEDEC, another key standards body, has incorporated PCM noise measurement protocols into their JEP173 specification, which addresses reliability evaluation procedures for emerging non-volatile memory technologies. This standard provides detailed guidelines for noise floor determination, signal-to-noise ratio calculation, and statistical analysis of noise distribution in PCM arrays.

The International Electrotechnical Commission (IEC) has also contributed significantly through its Technical Committee 47, which is developing the IEC 63267 standard focusing on test methods for PCM devices, including comprehensive noise characterization procedures. This standard emphasizes reproducibility of measurements across different testing environments and equipment.

Industry consortia play an equally important role in standardization efforts. The PCM Alliance, comprising major memory manufacturers and testing equipment providers, has published a white paper outlining best practices for noise measurement in multi-level cell PCM implementations. Their recommendations include specific temperature control parameters, measurement frequency considerations, and reference calibration procedures.

Academic institutions have collaborated with industry partners to validate these emerging standards. The Stanford Non-Volatile Memory Technology Research Initiative has conducted round-robin testing across multiple laboratories to verify the reproducibility of proposed measurement protocols, with results indicating a significant improvement in cross-lab measurement consistency when standardized procedures are followed.

The standardization efforts particularly focus on addressing the unique challenges of PCM noise characterization, including drift compensation techniques, resistance distribution modeling, and threshold voltage variation measurements. These standards typically specify minimum sample sizes, confidence intervals, and statistical methods for noise quantification to ensure scientific rigor.

Implementation of these standards is expected to accelerate PCM technology development by enabling more meaningful comparisons between different architectural approaches and materials innovations. Furthermore, standardized protocols will likely reduce qualification time for new PCM products by establishing clear benchmarks for acceptable noise levels across various application domains.

JEDEC, another key standards body, has incorporated PCM noise measurement protocols into their JEP173 specification, which addresses reliability evaluation procedures for emerging non-volatile memory technologies. This standard provides detailed guidelines for noise floor determination, signal-to-noise ratio calculation, and statistical analysis of noise distribution in PCM arrays.

The International Electrotechnical Commission (IEC) has also contributed significantly through its Technical Committee 47, which is developing the IEC 63267 standard focusing on test methods for PCM devices, including comprehensive noise characterization procedures. This standard emphasizes reproducibility of measurements across different testing environments and equipment.

Industry consortia play an equally important role in standardization efforts. The PCM Alliance, comprising major memory manufacturers and testing equipment providers, has published a white paper outlining best practices for noise measurement in multi-level cell PCM implementations. Their recommendations include specific temperature control parameters, measurement frequency considerations, and reference calibration procedures.

Academic institutions have collaborated with industry partners to validate these emerging standards. The Stanford Non-Volatile Memory Technology Research Initiative has conducted round-robin testing across multiple laboratories to verify the reproducibility of proposed measurement protocols, with results indicating a significant improvement in cross-lab measurement consistency when standardized procedures are followed.

The standardization efforts particularly focus on addressing the unique challenges of PCM noise characterization, including drift compensation techniques, resistance distribution modeling, and threshold voltage variation measurements. These standards typically specify minimum sample sizes, confidence intervals, and statistical methods for noise quantification to ensure scientific rigor.

Implementation of these standards is expected to accelerate PCM technology development by enabling more meaningful comparisons between different architectural approaches and materials innovations. Furthermore, standardized protocols will likely reduce qualification time for new PCM products by establishing clear benchmarks for acceptable noise levels across various application domains.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!