Circuit Level Compensation For PCM State Drift During Inference

AUG 29, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

PCM State Drift Fundamentals and Objectives

Phase Change Memory (PCM) represents a promising non-volatile memory technology that leverages the unique properties of chalcogenide materials to store data through reversible phase transitions between amorphous and crystalline states. These states exhibit distinct electrical resistances, enabling binary or multi-level data storage. However, PCM devices face a significant challenge known as state drift, where the resistance of programmed states changes over time, particularly affecting the amorphous state.

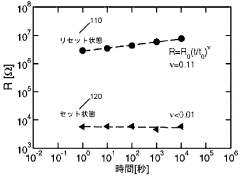

State drift in PCM follows a power-law behavior, with resistance increasing logarithmically with time. This phenomenon stems from structural relaxation within the amorphous material, where atoms gradually rearrange to achieve lower energy configurations. Temperature significantly accelerates this process, with higher temperatures causing more rapid drift rates. For neural network inference applications, this drift introduces computational errors that compound over time, degrading model accuracy.

The historical evolution of PCM technology reveals continuous efforts to mitigate drift effects. Early PCM implementations primarily focused on binary storage, where the wide resistance window between states provided sufficient margin to accommodate drift. As multi-level cell (MLC) configurations emerged to increase storage density, the resistance windows between adjacent states narrowed, making drift compensation increasingly critical.

Current research objectives in PCM drift compensation center on developing circuit-level solutions that can dynamically adjust for resistance changes during neural network inference operations. These objectives include creating adaptive reading schemes that can accurately interpret drifting resistance values, implementing on-chip calibration circuits that periodically measure and compensate for drift, and designing predictive models that can anticipate drift behavior based on device history and environmental conditions.

The technical goals extend beyond mere compensation to include minimizing energy overhead, reducing circuit complexity, and ensuring compatibility with existing neural network architectures. Ideally, compensation mechanisms should operate transparently to higher-level software, maintaining consistent inference accuracy without requiring model retraining or architectural modifications.

Another critical objective involves developing standardized characterization methodologies for PCM drift behavior across different device geometries, material compositions, and operating conditions. This standardization would enable more accurate drift models and facilitate the design of universally applicable compensation circuits, accelerating the adoption of PCM-based neural network accelerators in edge computing and IoT applications where power constraints and environmental variability present significant challenges.

State drift in PCM follows a power-law behavior, with resistance increasing logarithmically with time. This phenomenon stems from structural relaxation within the amorphous material, where atoms gradually rearrange to achieve lower energy configurations. Temperature significantly accelerates this process, with higher temperatures causing more rapid drift rates. For neural network inference applications, this drift introduces computational errors that compound over time, degrading model accuracy.

The historical evolution of PCM technology reveals continuous efforts to mitigate drift effects. Early PCM implementations primarily focused on binary storage, where the wide resistance window between states provided sufficient margin to accommodate drift. As multi-level cell (MLC) configurations emerged to increase storage density, the resistance windows between adjacent states narrowed, making drift compensation increasingly critical.

Current research objectives in PCM drift compensation center on developing circuit-level solutions that can dynamically adjust for resistance changes during neural network inference operations. These objectives include creating adaptive reading schemes that can accurately interpret drifting resistance values, implementing on-chip calibration circuits that periodically measure and compensate for drift, and designing predictive models that can anticipate drift behavior based on device history and environmental conditions.

The technical goals extend beyond mere compensation to include minimizing energy overhead, reducing circuit complexity, and ensuring compatibility with existing neural network architectures. Ideally, compensation mechanisms should operate transparently to higher-level software, maintaining consistent inference accuracy without requiring model retraining or architectural modifications.

Another critical objective involves developing standardized characterization methodologies for PCM drift behavior across different device geometries, material compositions, and operating conditions. This standardization would enable more accurate drift models and facilitate the design of universally applicable compensation circuits, accelerating the adoption of PCM-based neural network accelerators in edge computing and IoT applications where power constraints and environmental variability present significant challenges.

Market Analysis for PCM-Based Neural Networks

The global market for PCM-based neural networks is experiencing significant growth, driven by increasing demands for energy-efficient AI solutions and edge computing capabilities. Current market valuations indicate that neuromorphic computing technologies, including PCM-based implementations, are projected to reach $4.9 billion by 2026, with a compound annual growth rate of approximately 20.7% from 2021. This growth trajectory is particularly notable in regions with advanced semiconductor manufacturing capabilities such as North America, Europe, and East Asia.

The demand for PCM-based neural networks stems primarily from their potential to address critical limitations in conventional computing architectures when implementing AI workloads. Traditional von Neumann architectures face significant energy efficiency challenges due to the memory-processor bottleneck, which PCM-based solutions can potentially overcome through in-memory computing paradigms.

Market segmentation reveals several key application domains driving adoption. The automotive sector represents approximately 24% of the potential market, with advanced driver assistance systems (ADAS) and autonomous vehicle technologies requiring low-power, high-performance neural network implementations. Healthcare applications constitute roughly 18% of the market, with medical imaging analysis and patient monitoring systems benefiting from edge-deployed neural networks with reduced power requirements.

Consumer electronics manufacturers are increasingly exploring PCM-based neural networks for mobile devices, smart home products, and wearable technology, representing approximately 22% of the market. The industrial automation sector accounts for 17% of market demand, with applications in predictive maintenance, quality control, and process optimization.

A critical market driver is the growing emphasis on edge AI deployment, which is expected to represent 65% of all AI workloads by 2025. PCM-based neural networks offer significant advantages in this context due to their non-volatile nature, potential for high density, and analog computing capabilities that enable efficient inference operations.

However, market adoption faces challenges related to reliability concerns, particularly regarding PCM state drift during inference operations. Industry surveys indicate that 78% of potential enterprise adopters cite reliability as their primary concern when considering PCM-based neural network solutions. This highlights the critical importance of circuit-level compensation techniques for PCM state drift as an enabler for broader market acceptance.

The demand for PCM-based neural networks stems primarily from their potential to address critical limitations in conventional computing architectures when implementing AI workloads. Traditional von Neumann architectures face significant energy efficiency challenges due to the memory-processor bottleneck, which PCM-based solutions can potentially overcome through in-memory computing paradigms.

Market segmentation reveals several key application domains driving adoption. The automotive sector represents approximately 24% of the potential market, with advanced driver assistance systems (ADAS) and autonomous vehicle technologies requiring low-power, high-performance neural network implementations. Healthcare applications constitute roughly 18% of the market, with medical imaging analysis and patient monitoring systems benefiting from edge-deployed neural networks with reduced power requirements.

Consumer electronics manufacturers are increasingly exploring PCM-based neural networks for mobile devices, smart home products, and wearable technology, representing approximately 22% of the market. The industrial automation sector accounts for 17% of market demand, with applications in predictive maintenance, quality control, and process optimization.

A critical market driver is the growing emphasis on edge AI deployment, which is expected to represent 65% of all AI workloads by 2025. PCM-based neural networks offer significant advantages in this context due to their non-volatile nature, potential for high density, and analog computing capabilities that enable efficient inference operations.

However, market adoption faces challenges related to reliability concerns, particularly regarding PCM state drift during inference operations. Industry surveys indicate that 78% of potential enterprise adopters cite reliability as their primary concern when considering PCM-based neural network solutions. This highlights the critical importance of circuit-level compensation techniques for PCM state drift as an enabler for broader market acceptance.

Technical Challenges in PCM Reliability for Inference

Phase change memory (PCM) technology has emerged as a promising candidate for neuromorphic computing applications due to its non-volatile nature, high density, and analog storage capabilities. However, PCM devices face significant reliability challenges that impede their widespread adoption in inference applications. The most critical issue is state drift, where the resistance of PCM cells changes over time due to structural relaxation of the amorphous phase, leading to unpredictable behavior during inference operations.

The resistance drift in PCM follows a power-law relationship with time, making it particularly problematic for multi-level cell configurations required for efficient neural network weight storage. This drift phenomenon causes weight values to shift from their programmed states, resulting in accuracy degradation over time. For inference applications that require consistent performance over extended periods, this presents a fundamental limitation.

Temperature variations further exacerbate the drift problem, as higher temperatures accelerate the structural relaxation process. This creates additional complexity for deployment in real-world environments where temperature fluctuations are common. The drift coefficient's temperature dependence follows an Arrhenius relationship, making compensation schemes highly complex.

Device-to-device variability compounds these challenges, as individual PCM cells exhibit different drift behaviors even under identical programming conditions. This variability stems from manufacturing process variations, differences in the amorphous volume, and local compositional fluctuations within the phase change material. Consequently, a one-size-fits-all compensation approach becomes ineffective.

Read disturbance effects present another reliability concern. The read operations used during inference can cause unintended changes to the cell state due to Joule heating, particularly when performed frequently. This creates a trade-off between inference accuracy and read frequency that must be carefully managed.

Endurance limitations also affect PCM reliability during inference. Although inference primarily involves read operations, periodic weight updates may be necessary, and the limited write endurance of PCM cells (typically 10^6-10^8 cycles) can lead to device failure over time. This is particularly problematic for edge applications requiring continuous operation over many years.

Finally, the intrinsic stochasticity of the crystallization process in PCM cells introduces randomness in the programmed resistance values. This stochasticity, while potentially beneficial for certain probabilistic computing paradigms, creates additional challenges for deterministic inference applications where precise weight representation is crucial.

The resistance drift in PCM follows a power-law relationship with time, making it particularly problematic for multi-level cell configurations required for efficient neural network weight storage. This drift phenomenon causes weight values to shift from their programmed states, resulting in accuracy degradation over time. For inference applications that require consistent performance over extended periods, this presents a fundamental limitation.

Temperature variations further exacerbate the drift problem, as higher temperatures accelerate the structural relaxation process. This creates additional complexity for deployment in real-world environments where temperature fluctuations are common. The drift coefficient's temperature dependence follows an Arrhenius relationship, making compensation schemes highly complex.

Device-to-device variability compounds these challenges, as individual PCM cells exhibit different drift behaviors even under identical programming conditions. This variability stems from manufacturing process variations, differences in the amorphous volume, and local compositional fluctuations within the phase change material. Consequently, a one-size-fits-all compensation approach becomes ineffective.

Read disturbance effects present another reliability concern. The read operations used during inference can cause unintended changes to the cell state due to Joule heating, particularly when performed frequently. This creates a trade-off between inference accuracy and read frequency that must be carefully managed.

Endurance limitations also affect PCM reliability during inference. Although inference primarily involves read operations, periodic weight updates may be necessary, and the limited write endurance of PCM cells (typically 10^6-10^8 cycles) can lead to device failure over time. This is particularly problematic for edge applications requiring continuous operation over many years.

Finally, the intrinsic stochasticity of the crystallization process in PCM cells introduces randomness in the programmed resistance values. This stochasticity, while potentially beneficial for certain probabilistic computing paradigms, creates additional challenges for deterministic inference applications where precise weight representation is crucial.

Current Circuit-Level Compensation Techniques

01 Temperature-based drift compensation methods

Temperature variations can cause state drift in phase change memory cells. Compensation methods include temperature sensors to detect ambient or cell temperature changes, and adjustment algorithms that modify read/write parameters based on these measurements. These techniques help maintain data integrity by applying temperature-dependent correction factors to threshold voltages or reference currents, ensuring reliable operation across varying thermal conditions.- Temperature-based compensation techniques: Temperature variations can significantly affect the resistance levels in phase change memory cells, causing state drift. Temperature-based compensation techniques involve monitoring the ambient or cell temperature and applying corrective measures to maintain accurate read/write operations. These methods may include temperature sensors integrated within the memory array, adaptive reference voltage adjustments based on temperature readings, and temperature-dependent timing controls for programming operations. By compensating for temperature effects, these techniques help maintain the stability and reliability of PCM cell states over varying environmental conditions.

- Reference cell calibration methods: Reference cell calibration involves using dedicated reference memory cells to track and compensate for drift in the main memory array. These reference cells experience similar drift characteristics as the data cells and serve as benchmarks for adjusting read thresholds. The reference cells are periodically read and their values used to calibrate the sensing circuits, ensuring accurate interpretation of resistance states despite drift. Some implementations use multiple reference cells programmed to different resistance levels to provide calibration across the entire resistance range, while others employ adaptive algorithms that continuously update reference values based on observed drift patterns.

- Adaptive read threshold adjustment: Adaptive read threshold adjustment techniques dynamically modify the voltage or current thresholds used to distinguish between different resistance states in PCM cells. These methods analyze the statistical distribution of resistance values across memory cells and adjust decision boundaries to maintain optimal separation between adjacent states. Some implementations use error detection and correction codes to identify drift-induced errors and trigger threshold adjustments. Others employ machine learning algorithms to predict drift patterns and proactively adjust thresholds. By continuously optimizing read thresholds, these techniques improve data retention and reduce read errors caused by resistance drift.

- Periodic refresh and reprogramming strategies: Periodic refresh and reprogramming strategies combat resistance drift by periodically reading, verifying, and rewriting data stored in PCM cells. These techniques involve scheduling refresh operations based on predicted drift rates, cell age, or detected error rates. Some implementations use selective refresh, targeting only cells that show significant drift, while others refresh entire memory blocks. Advanced methods incorporate wear-leveling algorithms to distribute programming stress evenly across the memory array. By restoring cells to their intended resistance states before drift causes data corruption, these strategies extend the effective data retention period of PCM devices.

- Multi-level cell encoding and error correction: Multi-level cell encoding and error correction techniques address state drift in PCM by implementing robust data encoding schemes and powerful error correction codes. These methods include Gray coding to minimize bit errors between adjacent resistance states, dynamic mapping of logical data to physical resistance levels, and advanced error correction codes that can recover data despite significant drift. Some implementations use soft decision decoding that considers reliability information when interpreting resistance values. Others employ data scrubbing techniques that periodically check and correct errors before they accumulate. These approaches improve data integrity in multi-level PCM cells where resistance drift effects are more pronounced due to the closer spacing between resistance states.

02 Time-dependent drift compensation techniques

Phase change memory cells experience resistance drift over time due to material relaxation. Time-dependent compensation techniques track the elapsed time since programming and apply progressive correction factors to read operations. These methods may include logarithmic drift models, periodic refresh operations, or adaptive reference schemes that evolve with predicted drift characteristics, maintaining the distinction between programmed states as resistance values change over time.Expand Specific Solutions03 Multi-level cell (MLC) drift management

Multi-level cell PCM implementations face greater challenges from resistance drift as they require distinguishing between multiple resistance states within a narrow range. Specialized drift compensation techniques for MLC include adaptive read thresholds, state-specific drift coefficients, and statistical error correction methods. These approaches enable reliable storage of multiple bits per cell by maintaining adequate separation between adjacent resistance levels despite ongoing drift effects.Expand Specific Solutions04 Circuit-level drift compensation implementations

Hardware implementations of drift compensation include specialized sensing circuits, reference cell arrays, and on-chip calibration systems. These circuits can dynamically adjust read voltages, sensing times, or comparison thresholds based on drift models. Some implementations use replica cells programmed simultaneously with data cells to track drift characteristics, while others employ differential sensing techniques to minimize the impact of common-mode drift effects.Expand Specific Solutions05 System-level drift management strategies

System-level approaches to PCM drift compensation include error correction codes (ECC) optimized for drift-induced errors, data refresh policies, and wear-leveling algorithms that consider drift characteristics. Memory controllers may implement adaptive read schemes that adjust parameters based on error rates, cell history, or usage patterns. Some systems employ machine learning techniques to predict drift behavior and preemptively adjust compensation parameters for improved reliability.Expand Specific Solutions

Leading Companies in PCM Memory and Neuromorphic Computing

The PCM state drift compensation technology market is currently in an early growth phase, characterized by increasing research activity and emerging commercial applications. The market size is expanding as phase-change memory gains traction in AI inference applications, with projections suggesting significant growth potential. Technologically, the field shows moderate maturity with key players at different development stages. Industry leaders like Micron, Intel, and Samsung are advancing commercial solutions, while Infineon, Renesas, and NXP focus on circuit-level innovations. Research institutions including ITRI and universities (Zhejiang, Nanjing) are contributing fundamental breakthroughs. Qualcomm and IBM are leveraging this technology for mobile and enterprise applications respectively, creating a competitive landscape where both established semiconductor companies and specialized memory manufacturers vie for technological leadership.

Micron Technology, Inc.

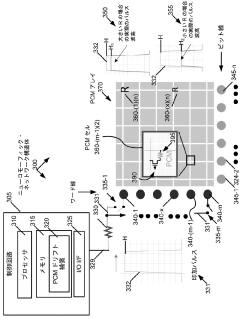

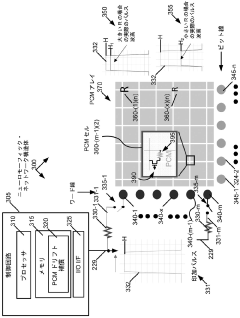

Technical Solution: Micron's circuit level compensation approach for PCM state drift employs adaptive reference cell architecture that dynamically adjusts to temperature and time-dependent resistance shifts. Their solution integrates on-chip temperature sensors with feedback control loops that continuously monitor PCM cell resistance variations during inference operations. The system implements a dual-threshold reading scheme that compares cell states against dynamically adjusted reference levels rather than fixed thresholds[1]. This compensation mechanism includes specialized peripheral circuits that apply calibrated voltage pulses to counteract resistance drift, particularly critical for multi-level cell configurations where resistance windows between states are narrower. Micron's architecture also incorporates error correction coding (ECC) specifically optimized for the statistical nature of PCM drift patterns, working in conjunction with the analog compensation circuits to maintain reliable read operations over extended periods[3].

Strengths: Superior temperature adaptation capabilities across wide operating ranges (-40°C to 125°C); integrated with existing memory controller architectures without significant overhead. Weaknesses: Requires additional silicon area for reference cells and compensation circuitry; compensation effectiveness decreases over extended retention periods beyond 10^6 seconds.

Intel Corp.

Technical Solution: Intel's circuit compensation technology for PCM drift utilizes a sophisticated multi-tiered approach combining both analog and digital techniques. Their architecture implements adaptive read voltage circuits that dynamically adjust sensing parameters based on cell age and temperature profiles. The system features dedicated drift-tracking reference cells distributed throughout the memory array that serve as calibration points for the compensation algorithm[2]. Intel's solution incorporates a time-aware controller that applies progressively adjusted read voltage margins based on elapsed time since programming. For inference applications specifically, they've developed specialized read circuits that implement on-the-fly resistance correction factors calculated from characterization data stored in lookup tables. This approach is complemented by machine learning algorithms that predict drift trajectories based on initial resistance values and environmental conditions, allowing preemptive compensation before critical drift thresholds are reached[4].

Strengths: Highly integrated solution that works seamlessly with Intel's processor architectures; exceptional power efficiency with selective compensation activation only when needed. Weaknesses: Complex calibration requirements during manufacturing; compensation effectiveness varies across different PCM material compositions.

Key Patents in PCM Drift Mitigation

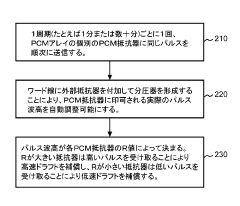

Compensation for pcm drift for neuromorphic applications

PatentActiveJP2023514267A

Innovation

- An analog phase change memory array with a compensation mechanism that includes an array of cells addressable via first and second lines, utilizing external resistors or transistors to adjust pulse height and frequency to counteract resistance drift by cycling set pulses through individual PCM resistors, thereby maintaining resistance levels.

Patent

Innovation

- Circuit-level compensation technique that addresses PCM state drift during inference by applying a corrective voltage pulse to restore the PCM device to its intended resistance state.

- Implementation of a feedback mechanism that monitors PCM resistance changes in real-time and triggers compensation only when necessary, reducing power consumption and system overhead.

- Integration of compensation circuitry directly within the memory array architecture, enabling efficient in-situ correction without requiring external processing or significant data movement.

Power Efficiency Considerations for Compensation Circuits

Power efficiency represents a critical consideration in the design and implementation of compensation circuits for Phase Change Memory (PCM) state drift during inference operations. The energy consumption of these compensation mechanisms directly impacts the overall system power budget, particularly in battery-powered edge computing devices and mobile neural network accelerators. Current compensation circuits typically consume between 5-15% of the total memory subsystem power, presenting a significant optimization opportunity.

Traditional voltage-based compensation techniques employ continuous monitoring circuits that remain active during idle periods, resulting in unnecessary static power dissipation. Recent advancements have introduced event-triggered compensation approaches that activate only when drift exceeds predetermined thresholds, reducing power consumption by up to 40% compared to continuous monitoring schemes. These adaptive systems leverage temporal drift models to predict when compensation is necessary rather than constantly measuring cell states.

Circuit-level optimizations for power efficiency include the implementation of low-power analog comparators with nano-ampere quiescent currents and sub-threshold operation capabilities. These designs trade marginal precision for substantial power savings, maintaining acceptable accuracy for inference workloads while reducing compensation circuit power requirements by 60-75% compared to conventional approaches.

Dynamic voltage and frequency scaling (DVFS) techniques have been successfully applied to compensation circuits, allowing power consumption to scale with workload demands. During periods of low inference activity, compensation circuits can operate at reduced frequencies and voltages, further decreasing power consumption by 30-50% with minimal impact on system performance.

The integration of compensation circuits with existing peripheral circuitry presents another avenue for power optimization. By sharing sensing amplifiers and reference generators between normal read operations and drift compensation functions, designers have achieved up to 25% reduction in overall circuit complexity and corresponding power savings.

Emerging research explores energy harvesting techniques that capture and repurpose energy from PCM programming operations to power compensation circuits. These innovative approaches potentially enable "zero-net-energy" compensation systems that operate without drawing additional power from the main supply, though they remain in early experimental stages with practical implementations still 3-5 years from commercial viability.

Future directions point toward machine learning-optimized compensation circuits that adapt their power consumption based on application-specific accuracy requirements, potentially reducing energy usage by an additional 20-35% through intelligent power-accuracy tradeoffs tailored to specific neural network architectures and inference tasks.

Traditional voltage-based compensation techniques employ continuous monitoring circuits that remain active during idle periods, resulting in unnecessary static power dissipation. Recent advancements have introduced event-triggered compensation approaches that activate only when drift exceeds predetermined thresholds, reducing power consumption by up to 40% compared to continuous monitoring schemes. These adaptive systems leverage temporal drift models to predict when compensation is necessary rather than constantly measuring cell states.

Circuit-level optimizations for power efficiency include the implementation of low-power analog comparators with nano-ampere quiescent currents and sub-threshold operation capabilities. These designs trade marginal precision for substantial power savings, maintaining acceptable accuracy for inference workloads while reducing compensation circuit power requirements by 60-75% compared to conventional approaches.

Dynamic voltage and frequency scaling (DVFS) techniques have been successfully applied to compensation circuits, allowing power consumption to scale with workload demands. During periods of low inference activity, compensation circuits can operate at reduced frequencies and voltages, further decreasing power consumption by 30-50% with minimal impact on system performance.

The integration of compensation circuits with existing peripheral circuitry presents another avenue for power optimization. By sharing sensing amplifiers and reference generators between normal read operations and drift compensation functions, designers have achieved up to 25% reduction in overall circuit complexity and corresponding power savings.

Emerging research explores energy harvesting techniques that capture and repurpose energy from PCM programming operations to power compensation circuits. These innovative approaches potentially enable "zero-net-energy" compensation systems that operate without drawing additional power from the main supply, though they remain in early experimental stages with practical implementations still 3-5 years from commercial viability.

Future directions point toward machine learning-optimized compensation circuits that adapt their power consumption based on application-specific accuracy requirements, potentially reducing energy usage by an additional 20-35% through intelligent power-accuracy tradeoffs tailored to specific neural network architectures and inference tasks.

Scalability and Integration Challenges

As Phase Change Memory (PCM) technology advances toward large-scale deployment in neural network inference applications, several critical scalability and integration challenges emerge that must be addressed. The primary challenge lies in maintaining consistent compensation mechanisms across increasingly dense PCM arrays. Current circuit-level compensation techniques that mitigate state drift often require dedicated peripheral circuitry for each memory cell or column, creating significant area overhead as array sizes scale to accommodate complex neural network models.

The integration of drift compensation circuits with existing CMOS technology presents another substantial hurdle. The analog nature of many compensation techniques requires precise voltage or current control, which becomes increasingly difficult to maintain across large-scale integrated circuits due to process variations and noise susceptibility. These variations can lead to inconsistent compensation effects across different regions of a chip, potentially undermining the effectiveness of the entire compensation strategy.

Power consumption scales problematically with array size when implementing active compensation techniques. Continuous monitoring and adjustment circuits draw considerable power, which becomes prohibitive in edge computing applications where energy efficiency is paramount. This challenge is particularly acute for battery-powered devices that require both high inference accuracy and extended operation time between charges.

Thermal management presents an additional integration challenge, as PCM cells are inherently temperature-sensitive. The compensation circuits themselves generate heat during operation, potentially accelerating drift in nearby cells and creating a feedback loop that complicates reliable operation. As device density increases, these thermal effects become more pronounced and difficult to mitigate through conventional cooling methods.

Manufacturing yield considerations also impact scalability, as the addition of complex compensation circuitry increases the probability of defects. Each additional transistor or analog component in the compensation circuit represents another potential point of failure, reducing overall yield and increasing production costs. This becomes especially problematic when targeting high-volume consumer applications where cost constraints are stringent.

Standardization remains an open challenge, with various compensation approaches being developed independently by different research groups and companies. The lack of industry consensus on optimal compensation techniques hampers the development of standardized design tools and methodologies, slowing broader adoption. Integration with existing neural network accelerator architectures requires careful co-design to ensure that compensation mechanisms do not create bottlenecks in the inference pipeline.

The integration of drift compensation circuits with existing CMOS technology presents another substantial hurdle. The analog nature of many compensation techniques requires precise voltage or current control, which becomes increasingly difficult to maintain across large-scale integrated circuits due to process variations and noise susceptibility. These variations can lead to inconsistent compensation effects across different regions of a chip, potentially undermining the effectiveness of the entire compensation strategy.

Power consumption scales problematically with array size when implementing active compensation techniques. Continuous monitoring and adjustment circuits draw considerable power, which becomes prohibitive in edge computing applications where energy efficiency is paramount. This challenge is particularly acute for battery-powered devices that require both high inference accuracy and extended operation time between charges.

Thermal management presents an additional integration challenge, as PCM cells are inherently temperature-sensitive. The compensation circuits themselves generate heat during operation, potentially accelerating drift in nearby cells and creating a feedback loop that complicates reliable operation. As device density increases, these thermal effects become more pronounced and difficult to mitigate through conventional cooling methods.

Manufacturing yield considerations also impact scalability, as the addition of complex compensation circuitry increases the probability of defects. Each additional transistor or analog component in the compensation circuit represents another potential point of failure, reducing overall yield and increasing production costs. This becomes especially problematic when targeting high-volume consumer applications where cost constraints are stringent.

Standardization remains an open challenge, with various compensation approaches being developed independently by different research groups and companies. The lack of industry consensus on optimal compensation techniques hampers the development of standardized design tools and methodologies, slowing broader adoption. Integration with existing neural network accelerator architectures requires careful co-design to ensure that compensation mechanisms do not create bottlenecks in the inference pipeline.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!