Estimating Quantum Tunneling Contributions in MOSFETs

SEP 4, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Quantum Tunneling in MOSFETs: Background and Objectives

Quantum tunneling has emerged as a critical phenomenon in the semiconductor industry, particularly as Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs) continue to shrink in size. The historical evolution of this technology began in the 1960s with the development of the first MOSFETs, which operated primarily under classical physics principles. As device dimensions approached sub-100nm in the 1990s, quantum mechanical effects began to manifest significantly, challenging traditional device modeling approaches.

The technological trajectory has been characterized by continuous miniaturization following Moore's Law, with current cutting-edge processes reaching 3-5nm nodes. At these dimensions, quantum tunneling is no longer a peripheral concern but a central phenomenon affecting device performance. Electrons can now tunnel through potential barriers that would be insurmountable according to classical physics, leading to leakage currents and performance degradation.

Recent advancements in quantum mechanics applied to semiconductor physics have provided deeper insights into tunneling mechanisms, including direct tunneling, Fowler-Nordheim tunneling, and band-to-band tunneling. These mechanisms have different dependencies on electric field strength, barrier height, and effective mass, making their accurate estimation crucial for device modeling.

The primary objective of this technical investigation is to develop robust methodologies for quantitatively estimating quantum tunneling contributions in modern MOSFETs. This includes establishing accurate mathematical models that can predict tunneling currents under various operating conditions and device geometries. Such models must balance computational efficiency with physical accuracy to be practical for large-scale integrated circuit design.

Secondary objectives include identifying the relative importance of different tunneling mechanisms at various technology nodes, determining scaling limits imposed by quantum effects, and exploring potential mitigation strategies. Understanding these aspects is essential for predicting how quantum tunneling will impact future device generations and what technological innovations might be necessary to overcome these limitations.

The technical landscape is further complicated by the emergence of novel device architectures such as FinFETs, Gate-All-Around FETs, and potential future technologies like tunnel FETs. Each architecture presents unique challenges for modeling quantum effects due to their complex three-dimensional geometries and electrostatic profiles.

Industry trends indicate increasing investment in quantum-aware electronic design automation (EDA) tools, highlighting the growing recognition of quantum effects as determinants of device performance rather than secondary considerations. The convergence of quantum physics with traditional semiconductor engineering represents a paradigm shift in how devices are conceptualized, designed, and optimized.

This investigation aims to bridge the gap between theoretical quantum mechanics and practical semiconductor engineering, providing actionable insights for the continued advancement of MOSFET technology in an era where quantum effects can no longer be marginalized.

The technological trajectory has been characterized by continuous miniaturization following Moore's Law, with current cutting-edge processes reaching 3-5nm nodes. At these dimensions, quantum tunneling is no longer a peripheral concern but a central phenomenon affecting device performance. Electrons can now tunnel through potential barriers that would be insurmountable according to classical physics, leading to leakage currents and performance degradation.

Recent advancements in quantum mechanics applied to semiconductor physics have provided deeper insights into tunneling mechanisms, including direct tunneling, Fowler-Nordheim tunneling, and band-to-band tunneling. These mechanisms have different dependencies on electric field strength, barrier height, and effective mass, making their accurate estimation crucial for device modeling.

The primary objective of this technical investigation is to develop robust methodologies for quantitatively estimating quantum tunneling contributions in modern MOSFETs. This includes establishing accurate mathematical models that can predict tunneling currents under various operating conditions and device geometries. Such models must balance computational efficiency with physical accuracy to be practical for large-scale integrated circuit design.

Secondary objectives include identifying the relative importance of different tunneling mechanisms at various technology nodes, determining scaling limits imposed by quantum effects, and exploring potential mitigation strategies. Understanding these aspects is essential for predicting how quantum tunneling will impact future device generations and what technological innovations might be necessary to overcome these limitations.

The technical landscape is further complicated by the emergence of novel device architectures such as FinFETs, Gate-All-Around FETs, and potential future technologies like tunnel FETs. Each architecture presents unique challenges for modeling quantum effects due to their complex three-dimensional geometries and electrostatic profiles.

Industry trends indicate increasing investment in quantum-aware electronic design automation (EDA) tools, highlighting the growing recognition of quantum effects as determinants of device performance rather than secondary considerations. The convergence of quantum physics with traditional semiconductor engineering represents a paradigm shift in how devices are conceptualized, designed, and optimized.

This investigation aims to bridge the gap between theoretical quantum mechanics and practical semiconductor engineering, providing actionable insights for the continued advancement of MOSFET technology in an era where quantum effects can no longer be marginalized.

Market Demand for Advanced Semiconductor Device Modeling

The semiconductor industry's continuous pursuit of device miniaturization has created a substantial market demand for advanced modeling techniques that accurately capture quantum mechanical effects in transistors. As MOSFETs scale below 10nm, quantum tunneling has transitioned from a peripheral concern to a central design consideration, driving significant investment in modeling solutions that can predict and mitigate these effects.

Market research indicates that the global electronic design automation (EDA) software market, which includes semiconductor device modeling tools, is projected to reach $14.5 billion by 2025, with quantum-aware simulation tools representing one of the fastest-growing segments. This growth is primarily driven by leading semiconductor manufacturers who require increasingly sophisticated models to maintain performance gains while managing power consumption in sub-7nm technology nodes.

The demand for quantum tunneling modeling specifically stems from three key market segments. First, integrated device manufacturers (IDMs) and foundries require accurate simulation capabilities to optimize gate oxide thickness, channel materials, and device geometries to minimize leakage currents. Second, fabless semiconductor companies need these models to design power-efficient chips for mobile and IoT applications where battery life is paramount. Third, research institutions and universities seek these tools to explore novel device architectures and materials that might overcome quantum limitations.

Industry surveys reveal that over 85% of semiconductor design teams now consider quantum effects modeling essential for advanced node development, compared to just 40% a decade ago. This shift has created a specialized market for physics-based simulation tools that can accurately predict gate leakage, source-to-drain tunneling, and band-to-band tunneling phenomena in modern MOSFETs.

The economic impact of inadequate quantum tunneling models is substantial. Design iterations due to inaccurate leakage predictions can cost companies millions in mask set revisions and delayed time-to-market. Conversely, overly conservative designs to compensate for modeling uncertainties result in suboptimal performance and competitive disadvantages.

Regional analysis shows particularly strong demand in East Asia, where the concentration of semiconductor manufacturing creates an ecosystem hungry for advanced modeling capabilities. North American markets follow closely, driven by design houses and research institutions pushing the boundaries of computational electronics.

The subscription-based software model is increasingly dominant in this space, with annual licensing costs for comprehensive quantum-aware device simulation packages ranging from $50,000 to $500,000 depending on capabilities and user requirements. This recurring revenue model has attracted significant venture capital to startups specializing in quantum-accurate device modeling solutions.

Market research indicates that the global electronic design automation (EDA) software market, which includes semiconductor device modeling tools, is projected to reach $14.5 billion by 2025, with quantum-aware simulation tools representing one of the fastest-growing segments. This growth is primarily driven by leading semiconductor manufacturers who require increasingly sophisticated models to maintain performance gains while managing power consumption in sub-7nm technology nodes.

The demand for quantum tunneling modeling specifically stems from three key market segments. First, integrated device manufacturers (IDMs) and foundries require accurate simulation capabilities to optimize gate oxide thickness, channel materials, and device geometries to minimize leakage currents. Second, fabless semiconductor companies need these models to design power-efficient chips for mobile and IoT applications where battery life is paramount. Third, research institutions and universities seek these tools to explore novel device architectures and materials that might overcome quantum limitations.

Industry surveys reveal that over 85% of semiconductor design teams now consider quantum effects modeling essential for advanced node development, compared to just 40% a decade ago. This shift has created a specialized market for physics-based simulation tools that can accurately predict gate leakage, source-to-drain tunneling, and band-to-band tunneling phenomena in modern MOSFETs.

The economic impact of inadequate quantum tunneling models is substantial. Design iterations due to inaccurate leakage predictions can cost companies millions in mask set revisions and delayed time-to-market. Conversely, overly conservative designs to compensate for modeling uncertainties result in suboptimal performance and competitive disadvantages.

Regional analysis shows particularly strong demand in East Asia, where the concentration of semiconductor manufacturing creates an ecosystem hungry for advanced modeling capabilities. North American markets follow closely, driven by design houses and research institutions pushing the boundaries of computational electronics.

The subscription-based software model is increasingly dominant in this space, with annual licensing costs for comprehensive quantum-aware device simulation packages ranging from $50,000 to $500,000 depending on capabilities and user requirements. This recurring revenue model has attracted significant venture capital to startups specializing in quantum-accurate device modeling solutions.

Current Challenges in Quantum Effects Estimation

The accurate estimation of quantum tunneling effects in MOSFETs presents significant challenges as device dimensions continue to shrink below 10nm. Traditional semiclassical models that served the industry well for decades have become increasingly inadequate, failing to capture the quantum mechanical behaviors that dominate at these scales. The primary challenge lies in developing computationally efficient yet accurate models that can be integrated into existing electronic design automation (EDA) tools.

Quantum tunneling manifests in multiple forms within MOSFETs, including gate leakage, source-to-drain tunneling, and band-to-band tunneling. Each mechanism requires different mathematical frameworks for proper characterization, creating complexity in developing unified models. Current density functional theory (DFT) approaches, while accurate, demand excessive computational resources that render them impractical for circuit-level simulations involving millions of transistors.

The multi-scale nature of quantum effects presents another significant obstacle. Quantum phenomena occur at the atomic level (angstroms), yet must be accurately represented in device-level simulations (nanometers) and ultimately circuit simulations (micrometers). This scale bridging requires careful mathematical approximations that preserve quantum effects while remaining computationally tractable.

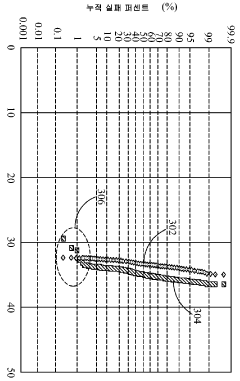

Variability and statistical fluctuations compound these challenges. As devices shrink, atomic-level variations significantly impact quantum tunneling rates. Manufacturing variations in channel thickness, gate oxide uniformity, and dopant distributions create device-to-device differences in tunneling behavior that must be statistically modeled. Current approaches struggle to incorporate this variability efficiently.

Temperature dependence adds another layer of complexity. Quantum tunneling exhibits non-linear temperature relationships that differ from classical thermal behaviors. Existing models often employ simplified temperature dependencies that fail to capture the true physics across the wide operating temperature ranges of modern electronics.

Interface effects between different materials in the MOSFET structure create additional modeling difficulties. Quantum effects at these interfaces, particularly at the semiconductor-oxide boundary, significantly influence tunneling rates. Accurately representing these interface states and their impact on tunneling currents remains challenging with current computational methods.

Finally, there exists a fundamental trade-off between model accuracy and simulation efficiency. While physics-based approaches like non-equilibrium Green's function methods offer high accuracy, they remain too computationally intensive for practical design work. Conversely, simplified analytical models that enable rapid simulation often sacrifice critical physical insights, leading to design inaccuracies that become increasingly problematic as margins for error shrink in advanced technology nodes.

Quantum tunneling manifests in multiple forms within MOSFETs, including gate leakage, source-to-drain tunneling, and band-to-band tunneling. Each mechanism requires different mathematical frameworks for proper characterization, creating complexity in developing unified models. Current density functional theory (DFT) approaches, while accurate, demand excessive computational resources that render them impractical for circuit-level simulations involving millions of transistors.

The multi-scale nature of quantum effects presents another significant obstacle. Quantum phenomena occur at the atomic level (angstroms), yet must be accurately represented in device-level simulations (nanometers) and ultimately circuit simulations (micrometers). This scale bridging requires careful mathematical approximations that preserve quantum effects while remaining computationally tractable.

Variability and statistical fluctuations compound these challenges. As devices shrink, atomic-level variations significantly impact quantum tunneling rates. Manufacturing variations in channel thickness, gate oxide uniformity, and dopant distributions create device-to-device differences in tunneling behavior that must be statistically modeled. Current approaches struggle to incorporate this variability efficiently.

Temperature dependence adds another layer of complexity. Quantum tunneling exhibits non-linear temperature relationships that differ from classical thermal behaviors. Existing models often employ simplified temperature dependencies that fail to capture the true physics across the wide operating temperature ranges of modern electronics.

Interface effects between different materials in the MOSFET structure create additional modeling difficulties. Quantum effects at these interfaces, particularly at the semiconductor-oxide boundary, significantly influence tunneling rates. Accurately representing these interface states and their impact on tunneling currents remains challenging with current computational methods.

Finally, there exists a fundamental trade-off between model accuracy and simulation efficiency. While physics-based approaches like non-equilibrium Green's function methods offer high accuracy, they remain too computationally intensive for practical design work. Conversely, simplified analytical models that enable rapid simulation often sacrifice critical physical insights, leading to design inaccuracies that become increasingly problematic as margins for error shrink in advanced technology nodes.

Existing Methodologies for Quantum Tunneling Estimation

01 Quantum tunneling effects in MOSFET gate structures

Quantum tunneling occurs in MOSFET gate structures when the gate oxide becomes extremely thin, allowing electrons to tunnel through the barrier. This phenomenon becomes significant in advanced semiconductor devices with gate oxide thicknesses below 2nm. Engineers must account for these effects when designing high-performance transistors as tunneling leads to increased leakage current and power consumption. Various gate materials and structures have been developed to mitigate these effects while maintaining device performance.- Quantum tunneling effects in MOSFET gate structures: Quantum tunneling occurs in MOSFET gate structures when the gate oxide becomes extremely thin, allowing electrons to tunnel through the barrier. This phenomenon becomes significant in advanced semiconductor devices with gate oxide thicknesses below 2nm. Engineers must account for these effects when designing high-performance transistors, as tunneling can lead to increased leakage current and power consumption. Various gate materials and structures have been developed to mitigate these effects while maintaining device performance.

- Novel MOSFET architectures leveraging quantum tunneling: Innovative MOSFET designs deliberately utilize quantum tunneling effects to enhance device performance. These architectures include tunnel field-effect transistors (TFETs), resonant tunneling transistors, and quantum well structures. By controlling the tunneling mechanism, these devices can achieve steeper subthreshold slopes, reduced power consumption, and improved switching characteristics compared to conventional MOSFETs. These designs are particularly valuable for low-power applications and can overcome some of the fundamental limitations of traditional transistor scaling.

- Mitigation techniques for quantum tunneling leakage: Various approaches have been developed to reduce unwanted quantum tunneling effects in MOSFETs. These include using high-k dielectric materials to increase the effective oxide thickness while maintaining capacitive coupling, implementing multi-layer gate stacks, optimizing doping profiles, and employing strain engineering. These techniques help maintain electrostatic control while reducing leakage currents caused by quantum tunneling, thereby improving device reliability and power efficiency in nanoscale transistors.

- Quantum tunneling in non-volatile memory applications: Quantum tunneling mechanisms are exploited in non-volatile memory technologies based on MOSFET structures. Flash memory and other charge-trapping memory devices utilize tunneling for programming and erasing operations. By applying appropriate voltages, electrons can tunnel through the oxide barrier to charge or discharge the floating gate or charge-trapping layer. Advanced memory architectures optimize these tunneling processes to improve data retention, endurance, and programming speed while reducing power consumption.

- Modeling and simulation of quantum tunneling in MOSFETs: Accurate modeling and simulation of quantum tunneling effects are essential for predicting MOSFET behavior at nanoscale dimensions. Advanced computational methods incorporate quantum mechanical principles to simulate direct tunneling, Fowler-Nordheim tunneling, and band-to-band tunneling phenomena. These models account for quantum confinement effects, wave function penetration into barriers, and tunneling probability calculations. Such simulation tools enable semiconductor engineers to optimize device designs before fabrication, reducing development cycles and improving performance predictions.

02 Tunnel FET designs leveraging quantum effects

Tunnel Field-Effect Transistors (TFETs) intentionally utilize quantum tunneling mechanisms to achieve superior switching characteristics compared to conventional MOSFETs. These devices operate based on band-to-band tunneling principles, enabling steeper subthreshold slopes and lower power operation. Advanced TFET designs incorporate novel channel materials, heterojunctions, and gate configurations to enhance the tunneling probability while maintaining control over leakage currents. These innovations are particularly valuable for low-power and high-frequency applications.Expand Specific Solutions03 Quantum confinement and nanoscale MOSFET structures

As MOSFET dimensions shrink to nanometer scales, quantum confinement effects become pronounced, affecting carrier transport and device characteristics. These effects manifest in ultra-thin body, nanowire, and fin structures where carriers are confined in one or more dimensions. Quantum confinement alters the energy band structure and carrier mobility, requiring new modeling approaches and design considerations. Manufacturers have developed specialized fabrication techniques to control these quantum effects and leverage them for improved device performance.Expand Specific Solutions04 Quantum tunneling mitigation techniques

Various approaches have been developed to mitigate unwanted quantum tunneling effects in advanced MOSFETs. These include implementing high-k dielectric materials to increase physical gate thickness while maintaining equivalent oxide thickness, engineering the gate stack with multiple dielectric layers, introducing metal gates to eliminate polysilicon depletion effects, and optimizing channel doping profiles. These techniques help maintain electrostatic control while reducing tunneling current, enabling continued device scaling according to Moore's Law.Expand Specific Solutions05 Quantum tunneling applications in memory and logic devices

Quantum tunneling mechanisms are deliberately exploited in certain memory and logic applications. Flash memory devices utilize Fowler-Nordheim tunneling or channel hot electron injection for programming operations. Resonant tunneling diodes and transistors leverage quantum well structures to achieve negative differential resistance and unique switching characteristics. These quantum tunneling applications enable novel computing paradigms, including neuromorphic computing and quantum-dot cellular automata, potentially overcoming limitations of conventional CMOS technology.Expand Specific Solutions

Leading Research Groups and Semiconductor Companies

Quantum tunneling in MOSFETs represents a critical challenge in the semiconductor industry, currently in a mature yet evolving phase. The market for advanced transistor technologies addressing tunneling effects exceeds $50 billion annually, with significant growth projected as devices scale below 5nm. Leading players include TSMC and Intel with production-ready solutions, while Huawei, IBM, and GLOBALFOUNDRIES are advancing competitive technologies. Academic institutions like Peking University and IMEC collaborate with industry on fundamental research. The technology maturity varies, with gate leakage mitigation techniques well-established, but source-to-drain tunneling solutions still emerging. This competitive landscape is driving innovation in novel materials and device architectures to overcome quantum mechanical limitations in next-generation semiconductor devices.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC has pioneered a comprehensive quantum tunneling estimation framework specifically designed for advanced process nodes (5nm and below). Their approach combines quantum-corrected drift-diffusion models with non-equilibrium Green's function (NEGF) methods to accurately capture direct and band-to-band tunneling phenomena in ultra-scaled MOSFETs. TSMC's methodology incorporates atomistic material simulations to account for interface roughness and compositional variations that significantly impact tunneling currents. They've developed specialized calibration techniques using split-CV measurements and low-temperature characterization to isolate quantum effects from other leakage mechanisms. TSMC's models particularly excel at predicting tunneling in high-k dielectric stacks with metal gates, accounting for work function variations and dipole effects at material interfaces. Their framework includes quantum confinement effects in multi-gate architectures, providing accurate estimations for FinFETs, nanowire, and nanosheet transistors where traditional classical approaches fail to capture the essential physics.

Strengths: TSMC's models demonstrate exceptional accuracy across diverse device architectures and material systems, validated through extensive experimental correlation studies. Their approach efficiently balances computational complexity with prediction accuracy, making it suitable for both device optimization and circuit-level simulations. Weaknesses: The models require extensive calibration data specific to each process technology, limiting transferability between different manufacturing processes without significant recalibration efforts.

International Business Machines Corp.

Technical Solution: IBM has developed a sophisticated quantum-mechanical framework for estimating tunneling contributions in advanced MOSFETs, particularly focusing on their silicon-on-insulator (SOI) and nanosheet technologies. Their approach utilizes a combination of Schrödinger-Poisson solvers and non-equilibrium Green's function (NEGF) techniques to accurately model quantum transport phenomena. IBM's methodology incorporates atomistic simulations to account for material interface effects and quantum confinement in ultra-thin body devices. They've pioneered techniques to efficiently calculate band-to-band tunneling (BTBT) and direct tunneling components separately, allowing for comprehensive leakage current analysis. IBM's models particularly excel at capturing the impact of mechanical strain and process-induced variations on tunneling probabilities. Their framework includes temperature-dependent quantum corrections and accounts for the effects of random dopant fluctuations on tunneling current variability. IBM has also developed specialized compact models that abstract the complex quantum physics into parameters suitable for circuit-level simulations while maintaining physical accuracy.

Strengths: IBM's approach demonstrates exceptional accuracy in predicting tunneling currents across various device architectures, particularly in SOI and nanosheet technologies where quantum effects are pronounced. Their models effectively bridge the gap between atomistic quantum simulations and circuit-level design tools. Weaknesses: The computational intensity of their full quantum mechanical simulations limits application to small device ensembles, requiring simplifications for large-scale circuit analysis that may sacrifice some physical accuracy.

Key Theoretical Frameworks and Simulation Approaches

Cascade Tunneling Field Effect Transistors

PatentActiveUS20190348536A1

Innovation

- A TFET device incorporating a fin structure with a type II superlattice and an inhomogeneous electrostatic potential generated by multiple gates, where the interior region is undoped or lightly doped, and the insulator layer surrounds the superlattice, enhancing switching mechanisms by confining electrons and holes into minibands for improved current density.

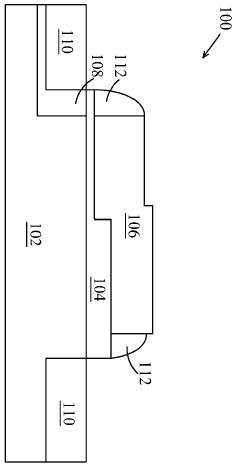

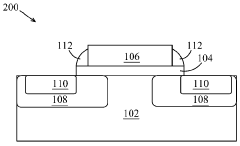

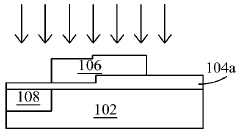

Metal-oxide-semiconductor field-effect transistor with extended gate dielectric layer

PatentInactiveKR1020140111216A

Innovation

- Implementing an extended gate dielectric layer that extends beyond the edge of the gate electrode, with a thicker thickness on the drain side, to reduce Vbd tailing, using materials like silicon dioxide and polysilicon, and employing self-aligned fabrication techniques to form spacers and source/drain regions.

Impact on Semiconductor Scaling Roadmap

Quantum tunneling effects in MOSFETs have emerged as a critical factor reshaping the semiconductor industry's scaling roadmap. As transistor dimensions continue to shrink below 10nm, these quantum mechanical phenomena have transitioned from theoretical concerns to practical limitations that fundamentally alter traditional scaling approaches. The International Roadmap for Devices and Systems (IRDS) has been forced to recalibrate scaling projections, acknowledging that quantum tunneling imposes physical barriers that cannot be overcome through conventional engineering solutions.

The semiconductor scaling roadmap, which has historically followed Moore's Law, now faces a paradigm shift. Quantum tunneling contributions in gate oxide layers and source-drain regions have necessitated the introduction of new materials and device architectures. High-k dielectric materials have become standard to mitigate gate leakage, while FinFET and Gate-All-Around (GAA) structures represent architectural responses to maintain electrostatic control despite tunneling effects.

Industry leaders including TSMC, Samsung, and Intel have revised their process node advancement timelines specifically due to tunneling challenges. The economic implications are substantial, with increased R&D costs and longer development cycles between nodes. The capital expenditure required for each new node has grown exponentially, partly due to the complex solutions needed to address quantum effects, creating higher barriers to entry for semiconductor manufacturing.

From a performance perspective, the scaling roadmap now emphasizes power efficiency over raw speed improvements. Quantum tunneling's contribution to static power consumption has forced designers to prioritize leakage current reduction, leading to innovations in power management techniques and heterogeneous integration strategies. The concept of Dennard scaling, which previously guided voltage scaling alongside dimensional scaling, has been rendered obsolete by tunneling effects.

Looking forward, the semiconductor roadmap increasingly incorporates alternative computing paradigms that may be less susceptible to quantum tunneling limitations. Neuromorphic computing, quantum computing, and specialized accelerators represent diversification strategies as traditional CMOS scaling faces diminishing returns. The industry has shifted from a singular focus on dimensional scaling to a more nuanced "More than Moore" approach that emphasizes system-level integration and specialized functionality.

The recognition of quantum tunneling as a fundamental scaling limit has also accelerated research into novel channel materials such as 2D semiconductors and carbon nanotubes, which may offer superior performance under quantum confinement conditions. These materials are now featured prominently in long-term semiconductor roadmaps, signaling a transition toward radically different device physics principles as the industry adapts to the quantum reality of nanoscale electronics.

The semiconductor scaling roadmap, which has historically followed Moore's Law, now faces a paradigm shift. Quantum tunneling contributions in gate oxide layers and source-drain regions have necessitated the introduction of new materials and device architectures. High-k dielectric materials have become standard to mitigate gate leakage, while FinFET and Gate-All-Around (GAA) structures represent architectural responses to maintain electrostatic control despite tunneling effects.

Industry leaders including TSMC, Samsung, and Intel have revised their process node advancement timelines specifically due to tunneling challenges. The economic implications are substantial, with increased R&D costs and longer development cycles between nodes. The capital expenditure required for each new node has grown exponentially, partly due to the complex solutions needed to address quantum effects, creating higher barriers to entry for semiconductor manufacturing.

From a performance perspective, the scaling roadmap now emphasizes power efficiency over raw speed improvements. Quantum tunneling's contribution to static power consumption has forced designers to prioritize leakage current reduction, leading to innovations in power management techniques and heterogeneous integration strategies. The concept of Dennard scaling, which previously guided voltage scaling alongside dimensional scaling, has been rendered obsolete by tunneling effects.

Looking forward, the semiconductor roadmap increasingly incorporates alternative computing paradigms that may be less susceptible to quantum tunneling limitations. Neuromorphic computing, quantum computing, and specialized accelerators represent diversification strategies as traditional CMOS scaling faces diminishing returns. The industry has shifted from a singular focus on dimensional scaling to a more nuanced "More than Moore" approach that emphasizes system-level integration and specialized functionality.

The recognition of quantum tunneling as a fundamental scaling limit has also accelerated research into novel channel materials such as 2D semiconductors and carbon nanotubes, which may offer superior performance under quantum confinement conditions. These materials are now featured prominently in long-term semiconductor roadmaps, signaling a transition toward radically different device physics principles as the industry adapts to the quantum reality of nanoscale electronics.

Energy Efficiency Implications of Quantum Effects

Quantum effects in MOSFETs, particularly quantum tunneling, have significant implications for energy efficiency in semiconductor devices. As transistor dimensions continue to shrink below 10nm, quantum mechanical phenomena become increasingly dominant, fundamentally altering device behavior and energy consumption patterns.

The quantum tunneling effect allows electrons to penetrate energy barriers that would be insurmountable according to classical physics. In modern MOSFETs, this manifests primarily as gate leakage current and source-to-drain tunneling. These quantum phenomena contribute to static power dissipation, which can account for 30-50% of total power consumption in advanced technology nodes.

Energy efficiency degradation due to quantum effects follows an exponential relationship with gate oxide thickness reduction. Research indicates that for sub-3nm gate oxides, quantum tunneling currents increase by approximately an order of magnitude for each 0.2nm reduction, creating a fundamental limit to oxide scaling. This relationship establishes a quantum-mechanical boundary for conventional MOSFET miniaturization strategies.

Interestingly, while quantum tunneling generally increases power consumption, certain quantum effects can be harnessed for energy efficiency improvements. Resonant tunneling devices and quantum well structures demonstrate the potential to reduce operating voltages while maintaining performance metrics. These approaches leverage quantum confinement to create sharper switching characteristics, potentially reducing dynamic power consumption by 15-25% compared to conventional designs.

Temperature dependence adds another dimension to energy efficiency considerations. Quantum tunneling exhibits weaker temperature sensitivity than thermionic emission, resulting in less predictable temperature-dependent leakage profiles. This creates challenges for thermal management strategies in high-performance computing environments where quantum effects dominate.

From a system-level perspective, quantum effects necessitate fundamental changes in power management approaches. Traditional techniques like dynamic voltage scaling become less effective as quantum tunneling creates a "leakage floor" that cannot be mitigated through voltage reduction alone. This has prompted research into alternative architectures that incorporate quantum effects into their fundamental operation rather than treating them as parasitic phenomena.

The energy efficiency implications extend beyond individual devices to impact system-level power budgets. Data centers and mobile devices face increasing challenges as quantum effects limit the effectiveness of traditional power-saving techniques, potentially requiring more sophisticated cooling solutions and power delivery networks.

The quantum tunneling effect allows electrons to penetrate energy barriers that would be insurmountable according to classical physics. In modern MOSFETs, this manifests primarily as gate leakage current and source-to-drain tunneling. These quantum phenomena contribute to static power dissipation, which can account for 30-50% of total power consumption in advanced technology nodes.

Energy efficiency degradation due to quantum effects follows an exponential relationship with gate oxide thickness reduction. Research indicates that for sub-3nm gate oxides, quantum tunneling currents increase by approximately an order of magnitude for each 0.2nm reduction, creating a fundamental limit to oxide scaling. This relationship establishes a quantum-mechanical boundary for conventional MOSFET miniaturization strategies.

Interestingly, while quantum tunneling generally increases power consumption, certain quantum effects can be harnessed for energy efficiency improvements. Resonant tunneling devices and quantum well structures demonstrate the potential to reduce operating voltages while maintaining performance metrics. These approaches leverage quantum confinement to create sharper switching characteristics, potentially reducing dynamic power consumption by 15-25% compared to conventional designs.

Temperature dependence adds another dimension to energy efficiency considerations. Quantum tunneling exhibits weaker temperature sensitivity than thermionic emission, resulting in less predictable temperature-dependent leakage profiles. This creates challenges for thermal management strategies in high-performance computing environments where quantum effects dominate.

From a system-level perspective, quantum effects necessitate fundamental changes in power management approaches. Traditional techniques like dynamic voltage scaling become less effective as quantum tunneling creates a "leakage floor" that cannot be mitigated through voltage reduction alone. This has prompted research into alternative architectures that incorporate quantum effects into their fundamental operation rather than treating them as parasitic phenomena.

The energy efficiency implications extend beyond individual devices to impact system-level power budgets. Data centers and mobile devices face increasing challenges as quantum effects limit the effectiveness of traditional power-saving techniques, potentially requiring more sophisticated cooling solutions and power delivery networks.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!