Neuromorphic Chip Design: Synapse Circuits, Plasticity Models and Noise Robustness

AUG 20, 202510 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Neuromorphic Chip Evolution and Objectives

Neuromorphic computing, inspired by the structure and function of biological neural networks, has evolved significantly since its inception in the late 1980s. The field aims to create hardware systems that mimic the brain's efficiency in processing and learning from complex data. The evolution of neuromorphic chip design has been driven by advancements in neuroscience, materials science, and semiconductor technology.

In the early stages, neuromorphic chips focused on implementing basic neural network architectures using analog circuits. These designs aimed to replicate the parallel processing capabilities of biological neurons and synapses. As the field progressed, researchers began incorporating more sophisticated models of neural dynamics and synaptic plasticity.

The development of neuromorphic chips has been closely tied to the advancement of artificial intelligence and machine learning. As these fields have grown, so too has the demand for more efficient and specialized hardware to support neural network computations. This has led to increased interest in neuromorphic computing as a potential solution to the limitations of traditional von Neumann architectures.

One of the key objectives in neuromorphic chip design is to create synapse circuits that accurately model the behavior of biological synapses. This includes implementing various forms of synaptic plasticity, such as spike-timing-dependent plasticity (STDP), which is crucial for learning and memory formation in biological neural networks. Researchers aim to develop circuits that can efficiently implement these plasticity models while maintaining low power consumption and high scalability.

Another important goal is to improve the noise robustness of neuromorphic systems. Biological neural networks are remarkably resilient to noise and variability, a feature that artificial systems struggle to replicate. Enhancing the noise tolerance of neuromorphic chips is essential for their practical application in real-world environments where signal integrity may be compromised.

The ultimate objective of neuromorphic chip design is to create systems that can approach or even surpass the energy efficiency and computational capabilities of the human brain. This involves developing architectures that can process information in a highly parallel and event-driven manner, similar to biological neural networks. Such systems have the potential to revolutionize fields such as robotics, autonomous vehicles, and edge computing, where real-time processing of sensory data is critical.

As the field continues to evolve, researchers are exploring novel materials and fabrication techniques to overcome the limitations of traditional CMOS technology. This includes investigating the use of memristive devices, which can more closely mimic the behavior of biological synapses, and exploring three-dimensional chip architectures to increase connectivity and computational density.

In the early stages, neuromorphic chips focused on implementing basic neural network architectures using analog circuits. These designs aimed to replicate the parallel processing capabilities of biological neurons and synapses. As the field progressed, researchers began incorporating more sophisticated models of neural dynamics and synaptic plasticity.

The development of neuromorphic chips has been closely tied to the advancement of artificial intelligence and machine learning. As these fields have grown, so too has the demand for more efficient and specialized hardware to support neural network computations. This has led to increased interest in neuromorphic computing as a potential solution to the limitations of traditional von Neumann architectures.

One of the key objectives in neuromorphic chip design is to create synapse circuits that accurately model the behavior of biological synapses. This includes implementing various forms of synaptic plasticity, such as spike-timing-dependent plasticity (STDP), which is crucial for learning and memory formation in biological neural networks. Researchers aim to develop circuits that can efficiently implement these plasticity models while maintaining low power consumption and high scalability.

Another important goal is to improve the noise robustness of neuromorphic systems. Biological neural networks are remarkably resilient to noise and variability, a feature that artificial systems struggle to replicate. Enhancing the noise tolerance of neuromorphic chips is essential for their practical application in real-world environments where signal integrity may be compromised.

The ultimate objective of neuromorphic chip design is to create systems that can approach or even surpass the energy efficiency and computational capabilities of the human brain. This involves developing architectures that can process information in a highly parallel and event-driven manner, similar to biological neural networks. Such systems have the potential to revolutionize fields such as robotics, autonomous vehicles, and edge computing, where real-time processing of sensory data is critical.

As the field continues to evolve, researchers are exploring novel materials and fabrication techniques to overcome the limitations of traditional CMOS technology. This includes investigating the use of memristive devices, which can more closely mimic the behavior of biological synapses, and exploring three-dimensional chip architectures to increase connectivity and computational density.

Market Demand for Brain-Inspired Computing

The market demand for brain-inspired computing, particularly neuromorphic chip design, has been steadily growing in recent years. This surge in interest is driven by the increasing need for more efficient and powerful computing solutions that can handle complex cognitive tasks, such as pattern recognition, natural language processing, and decision-making in real-time environments.

The global neuromorphic computing market is experiencing significant expansion, with projections indicating substantial growth in the coming years. This growth is fueled by the rising adoption of artificial intelligence and machine learning technologies across various industries, including healthcare, automotive, robotics, and consumer electronics.

One of the key drivers of market demand is the potential for neuromorphic chips to overcome the limitations of traditional von Neumann architecture. These brain-inspired chips offer the promise of lower power consumption, faster processing speeds, and improved parallel computing capabilities. As energy efficiency becomes increasingly critical in data centers and edge computing applications, neuromorphic chips present an attractive solution for reducing power consumption while maintaining or enhancing computational performance.

The automotive industry has emerged as a significant market for neuromorphic computing, particularly in the development of advanced driver assistance systems (ADAS) and autonomous vehicles. These applications require real-time processing of vast amounts of sensory data, making neuromorphic chips an ideal fit due to their ability to efficiently handle parallel processing and pattern recognition tasks.

In the healthcare sector, neuromorphic computing is gaining traction for applications such as brain-computer interfaces, prosthetics, and medical imaging analysis. The ability of neuromorphic chips to process complex biological signals and mimic neural networks makes them particularly suited for these applications, driving demand in the medical technology market.

The Internet of Things (IoT) and edge computing sectors are also contributing to the growing demand for neuromorphic chips. As the number of connected devices continues to increase, there is a pressing need for low-power, high-performance computing solutions that can process data locally, reducing latency and bandwidth requirements. Neuromorphic chips, with their energy-efficient design and ability to perform complex computations at the edge, are well-positioned to meet this demand.

Despite the promising market outlook, challenges remain in the widespread adoption of neuromorphic computing. These include the need for standardization, scalability issues, and the development of software ecosystems that can fully leverage the capabilities of neuromorphic hardware. However, ongoing research and development efforts, coupled with increasing investment from both established tech giants and innovative startups, are addressing these challenges and driving the market forward.

The global neuromorphic computing market is experiencing significant expansion, with projections indicating substantial growth in the coming years. This growth is fueled by the rising adoption of artificial intelligence and machine learning technologies across various industries, including healthcare, automotive, robotics, and consumer electronics.

One of the key drivers of market demand is the potential for neuromorphic chips to overcome the limitations of traditional von Neumann architecture. These brain-inspired chips offer the promise of lower power consumption, faster processing speeds, and improved parallel computing capabilities. As energy efficiency becomes increasingly critical in data centers and edge computing applications, neuromorphic chips present an attractive solution for reducing power consumption while maintaining or enhancing computational performance.

The automotive industry has emerged as a significant market for neuromorphic computing, particularly in the development of advanced driver assistance systems (ADAS) and autonomous vehicles. These applications require real-time processing of vast amounts of sensory data, making neuromorphic chips an ideal fit due to their ability to efficiently handle parallel processing and pattern recognition tasks.

In the healthcare sector, neuromorphic computing is gaining traction for applications such as brain-computer interfaces, prosthetics, and medical imaging analysis. The ability of neuromorphic chips to process complex biological signals and mimic neural networks makes them particularly suited for these applications, driving demand in the medical technology market.

The Internet of Things (IoT) and edge computing sectors are also contributing to the growing demand for neuromorphic chips. As the number of connected devices continues to increase, there is a pressing need for low-power, high-performance computing solutions that can process data locally, reducing latency and bandwidth requirements. Neuromorphic chips, with their energy-efficient design and ability to perform complex computations at the edge, are well-positioned to meet this demand.

Despite the promising market outlook, challenges remain in the widespread adoption of neuromorphic computing. These include the need for standardization, scalability issues, and the development of software ecosystems that can fully leverage the capabilities of neuromorphic hardware. However, ongoing research and development efforts, coupled with increasing investment from both established tech giants and innovative startups, are addressing these challenges and driving the market forward.

Current Challenges in Neuromorphic Hardware

Neuromorphic hardware faces several significant challenges that impede its widespread adoption and performance optimization. One of the primary obstacles is the scalability of synapse circuits. As neuromorphic systems aim to emulate the vast interconnectivity of biological neural networks, designing and implementing efficient, compact, and low-power synapse circuits at scale remains a formidable task. Current technologies struggle to achieve the density and energy efficiency required for large-scale neuromorphic systems comparable to biological brains.

Another critical challenge lies in the implementation of biologically plausible plasticity models. While various learning rules and plasticity mechanisms have been proposed in computational neuroscience, translating these models into hardware-compatible implementations presents significant difficulties. The complexity of these models often conflicts with the constraints of hardware design, particularly in terms of area and power consumption. Striking a balance between biological fidelity and hardware efficiency remains an ongoing challenge for neuromorphic chip designers.

Noise robustness is a crucial aspect that demands attention in neuromorphic hardware development. Biological neural systems exhibit remarkable resilience to noise and variability, a feature that artificial systems struggle to replicate. The inherent variability in semiconductor manufacturing processes, coupled with the sensitivity of analog circuits to environmental factors, poses challenges for maintaining consistent and reliable performance in neuromorphic chips. Developing noise-tolerant architectures and circuits is essential for ensuring the stability and reliability of neuromorphic systems in real-world applications.

The integration of memory and processing elements in neuromorphic chips presents another significant hurdle. Traditional von Neumann architectures separate memory and processing units, leading to the well-known memory bottleneck. Neuromorphic designs aim to overcome this limitation by closely coupling memory and computation, similar to biological neural networks. However, implementing this integration efficiently while maintaining the desired computational capabilities and energy efficiency is a complex task that requires innovative circuit designs and architectures.

Power consumption remains a critical concern in neuromorphic hardware development. While biological brains are incredibly energy-efficient, current neuromorphic systems struggle to achieve comparable levels of performance per watt. Reducing power consumption while maintaining or improving computational capabilities is crucial for the practical deployment of neuromorphic systems, especially in edge computing and mobile applications.

Lastly, the lack of standardized benchmarks and evaluation metrics for neuromorphic hardware poses challenges in comparing different approaches and assessing progress in the field. Unlike traditional computing systems, where well-established benchmarks exist, neuromorphic systems often target diverse applications and operate on different principles, making direct comparisons difficult. Developing comprehensive and widely accepted benchmarks that capture the unique characteristics and potential advantages of neuromorphic computing is essential for driving innovation and facilitating the adoption of these technologies in various domains.

Another critical challenge lies in the implementation of biologically plausible plasticity models. While various learning rules and plasticity mechanisms have been proposed in computational neuroscience, translating these models into hardware-compatible implementations presents significant difficulties. The complexity of these models often conflicts with the constraints of hardware design, particularly in terms of area and power consumption. Striking a balance between biological fidelity and hardware efficiency remains an ongoing challenge for neuromorphic chip designers.

Noise robustness is a crucial aspect that demands attention in neuromorphic hardware development. Biological neural systems exhibit remarkable resilience to noise and variability, a feature that artificial systems struggle to replicate. The inherent variability in semiconductor manufacturing processes, coupled with the sensitivity of analog circuits to environmental factors, poses challenges for maintaining consistent and reliable performance in neuromorphic chips. Developing noise-tolerant architectures and circuits is essential for ensuring the stability and reliability of neuromorphic systems in real-world applications.

The integration of memory and processing elements in neuromorphic chips presents another significant hurdle. Traditional von Neumann architectures separate memory and processing units, leading to the well-known memory bottleneck. Neuromorphic designs aim to overcome this limitation by closely coupling memory and computation, similar to biological neural networks. However, implementing this integration efficiently while maintaining the desired computational capabilities and energy efficiency is a complex task that requires innovative circuit designs and architectures.

Power consumption remains a critical concern in neuromorphic hardware development. While biological brains are incredibly energy-efficient, current neuromorphic systems struggle to achieve comparable levels of performance per watt. Reducing power consumption while maintaining or improving computational capabilities is crucial for the practical deployment of neuromorphic systems, especially in edge computing and mobile applications.

Lastly, the lack of standardized benchmarks and evaluation metrics for neuromorphic hardware poses challenges in comparing different approaches and assessing progress in the field. Unlike traditional computing systems, where well-established benchmarks exist, neuromorphic systems often target diverse applications and operate on different principles, making direct comparisons difficult. Developing comprehensive and widely accepted benchmarks that capture the unique characteristics and potential advantages of neuromorphic computing is essential for driving innovation and facilitating the adoption of these technologies in various domains.

Existing Synapse Circuit Implementations

01 Noise reduction techniques in neuromorphic circuits

Various techniques are employed to reduce noise in neuromorphic circuits, enhancing their robustness. These methods include implementing noise-cancellation algorithms, using specialized circuit designs, and incorporating adaptive filtering mechanisms. By minimizing noise, these approaches improve the overall performance and reliability of neuromorphic chips in processing and transmitting signals.- Noise reduction techniques in neuromorphic circuits: Various techniques are employed to reduce noise in neuromorphic circuits, enhancing their robustness. These methods include implementing noise-cancellation algorithms, using specialized circuit designs, and incorporating feedback mechanisms to minimize the impact of noise on signal processing and data transmission within the chip.

- Adaptive learning algorithms for noise tolerance: Neuromorphic chips utilize adaptive learning algorithms to improve their noise tolerance. These algorithms enable the chip to dynamically adjust its parameters and synaptic weights in response to varying noise levels, allowing for more robust performance in noisy environments and enhancing overall system reliability.

- Stochastic computing for noise-robust neuromorphic systems: Stochastic computing techniques are implemented in neuromorphic chips to enhance their robustness against noise. By representing and processing information probabilistically, these systems can better handle uncertainties and fluctuations in input signals, leading to improved performance in noisy conditions.

- Analog-digital hybrid architectures for noise mitigation: Neuromorphic chips employ hybrid analog-digital architectures to mitigate noise effects. These designs combine the energy efficiency of analog circuits with the precision of digital processing, allowing for better noise handling in different stages of signal processing and improving overall system robustness.

- Noise-aware training and optimization techniques: Specialized training and optimization techniques are developed for neuromorphic chips to enhance their noise robustness. These methods involve incorporating noise models during the training process, optimizing network architectures for noise tolerance, and implementing noise-aware learning rules to improve the chip's performance in real-world, noisy environments.

02 Stochastic computing for noise tolerance

Stochastic computing techniques are utilized in neuromorphic chip design to enhance noise robustness. This approach involves representing and processing data as probabilities, which inherently provides better tolerance to noise and variability. By implementing stochastic computing elements, neuromorphic chips can maintain accuracy and reliability even in noisy environments.Expand Specific Solutions03 Adaptive learning algorithms for noise handling

Neuromorphic chips incorporate adaptive learning algorithms to improve their ability to handle noise. These algorithms allow the chip to dynamically adjust its parameters and processing strategies based on the input data and environmental conditions. This adaptability enables the chip to maintain high performance and accuracy even in the presence of varying noise levels.Expand Specific Solutions04 Hardware-level noise mitigation strategies

Various hardware-level strategies are implemented to mitigate noise in neuromorphic chips. These include using specialized materials and fabrication techniques, implementing shielding and isolation mechanisms, and designing optimized chip architectures. Such hardware-level approaches help to minimize the impact of noise on the chip's performance and reliability.Expand Specific Solutions05 Bio-inspired noise handling mechanisms

Neuromorphic chips incorporate bio-inspired mechanisms for handling noise, mimicking the robustness of biological neural systems. These mechanisms include implementing redundancy, utilizing parallel processing, and incorporating feedback loops. By emulating the noise-handling capabilities of biological systems, neuromorphic chips can achieve improved resilience to various types of noise and disturbances.Expand Specific Solutions

Key Players in Neuromorphic Chip Industry

The neuromorphic chip design market is in a nascent but rapidly evolving stage, with growing interest from both academia and industry. The market size is expanding, driven by potential applications in AI, edge computing, and IoT. While still relatively small, it's projected to grow significantly in the coming years. Technologically, neuromorphic chips are progressing but remain in early stages of maturity. Key players like IBM, Intel, and Qualcomm are investing heavily in R&D, while startups like Innatera Nanosystems are bringing innovative approaches. Academic institutions such as MIT, KAIST, and Zhejiang University are also contributing significantly to advancing the field. The focus is on improving synapse circuits, developing more accurate plasticity models, and enhancing noise robustness to create more efficient and brain-like computing systems.

International Business Machines Corp.

Technical Solution: IBM has made significant strides in neuromorphic chip design, particularly with their TrueNorth architecture. This chip emulates the brain's neurons and synapses using a network of 1 million programmable neurons and 256 million configurable synapses[1]. IBM's approach focuses on low-power, event-driven computation, which allows for efficient processing of sensory data. The chip incorporates advanced synapse circuits that can adapt their strength based on the frequency and timing of signals, mimicking biological synaptic plasticity[2]. To address noise robustness, IBM has implemented stochastic computing techniques, allowing the chip to function reliably in the presence of hardware variations and environmental noise[3].

Strengths: Low power consumption, high scalability, and bio-inspired architecture. Weaknesses: Limited to specific types of neural network architectures and potentially challenging to program for traditional computing tasks.

Massachusetts Institute of Technology

Technical Solution: MIT's research in neuromorphic chip design has focused on developing novel materials and circuit designs for more efficient and brain-like computing. Their approach includes the use of memristive devices for synaptic circuits, which can naturally emulate synaptic plasticity[9]. MIT researchers have developed plasticity models that incorporate both short-term and long-term memory effects, closely mimicking biological synapses. To address noise robustness, MIT has explored the use of stochastic resonance phenomena, where a certain level of noise can actually enhance signal detection and processing in neuromorphic systems[10].

Strengths: Cutting-edge materials research, bio-inspired plasticity models, and innovative approaches to noise handling. Weaknesses: Many technologies still in early research stages, potentially challenging to scale up to large-scale production.

Core Innovations in Plasticity Models

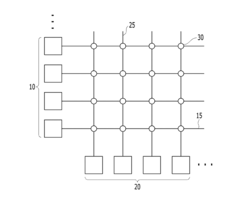

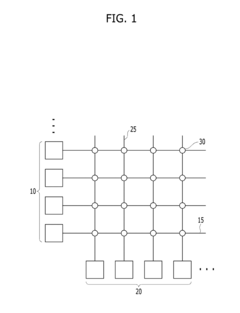

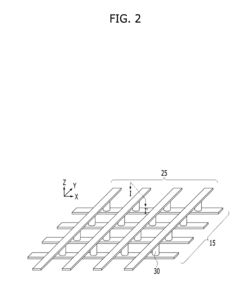

Neuromorphic device including synapses having carrier traps distributed at multiple energy levels

PatentActiveUS20170193357A1

Innovation

- Incorporating a variable resistive layer with carrier traps distributed at multiple energy levels, along with blocking and barrier layers, to enable synapses to change resistance states in response to learning processes, allowing for multiple resistance levels and current changes.

Neuromorphic synapses

PatentWO2016067139A1

Innovation

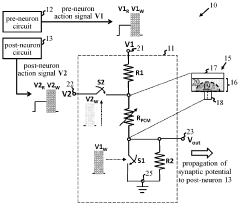

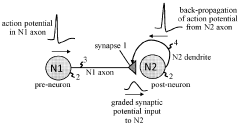

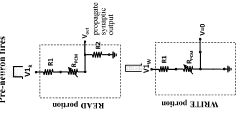

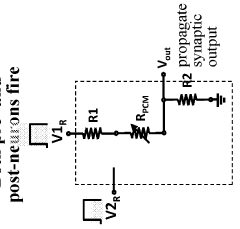

- A neuromorphic synapse with a three-terminal cell circuit that allows simultaneous addressing of synapses in an array configuration, enabling real-time programming and on-chip learning, and can operate with identical pre- and post-neuron action signals, emulating spike-timing dependent plasticity effects.

Energy Efficiency in Neuromorphic Computing

Energy efficiency is a critical aspect of neuromorphic computing, particularly in the design of neuromorphic chips. As these chips aim to emulate the functionality of biological neural networks, they must also strive to match the brain's remarkable energy efficiency. The human brain, despite its complex cognitive capabilities, operates on approximately 20 watts of power. This level of efficiency is a benchmark that neuromorphic computing systems aspire to achieve.

In the context of synapse circuits, energy efficiency is primarily addressed through the design of low-power analog circuits. These circuits leverage the inherent physics of devices to perform computations, reducing the energy consumption associated with traditional digital logic. Techniques such as subthreshold operation and charge-based computing are employed to minimize power consumption while maintaining computational accuracy.

Plasticity models, which are crucial for learning and adaptation in neuromorphic systems, also play a significant role in energy efficiency. Implementing these models in hardware requires careful consideration of power consumption. Spike-timing-dependent plasticity (STDP) and other biologically-inspired learning rules are often implemented using low-power analog circuits or mixed-signal designs. These approaches allow for continuous, adaptive learning while minimizing energy expenditure.

Noise robustness in neuromorphic chip design is intrinsically linked to energy efficiency. As power consumption is reduced, the signal-to-noise ratio typically decreases, making the system more susceptible to errors. Designers must strike a balance between energy efficiency and noise tolerance. Techniques such as stochastic computing and probabilistic bit streams are being explored to maintain computational accuracy in low-power, noisy environments.

Recent advancements in materials science and device physics have opened new avenues for energy-efficient neuromorphic computing. Emerging non-volatile memory technologies, such as memristors and phase-change memory, offer the potential for ultra-low-power synaptic operations. These devices can maintain their state without continuous power consumption, significantly reducing the overall energy footprint of neuromorphic systems.

The integration of energy harvesting techniques is another promising direction for improving energy efficiency in neuromorphic chips. By scavenging energy from the environment, such as through thermal gradients or mechanical vibrations, these systems could potentially operate autonomously with minimal external power input. This approach aligns closely with the self-sustaining nature of biological neural networks.

As neuromorphic chip designs continue to evolve, the focus on energy efficiency remains paramount. Researchers are exploring novel architectures that optimize data movement and minimize redundant computations. Event-driven processing, inspired by the brain's sparse and asynchronous operation, is being implemented to reduce power consumption during periods of low activity. Additionally, 3D integration techniques are being investigated to shorten interconnect lengths and reduce the energy cost of data transfer between neural elements.

In the context of synapse circuits, energy efficiency is primarily addressed through the design of low-power analog circuits. These circuits leverage the inherent physics of devices to perform computations, reducing the energy consumption associated with traditional digital logic. Techniques such as subthreshold operation and charge-based computing are employed to minimize power consumption while maintaining computational accuracy.

Plasticity models, which are crucial for learning and adaptation in neuromorphic systems, also play a significant role in energy efficiency. Implementing these models in hardware requires careful consideration of power consumption. Spike-timing-dependent plasticity (STDP) and other biologically-inspired learning rules are often implemented using low-power analog circuits or mixed-signal designs. These approaches allow for continuous, adaptive learning while minimizing energy expenditure.

Noise robustness in neuromorphic chip design is intrinsically linked to energy efficiency. As power consumption is reduced, the signal-to-noise ratio typically decreases, making the system more susceptible to errors. Designers must strike a balance between energy efficiency and noise tolerance. Techniques such as stochastic computing and probabilistic bit streams are being explored to maintain computational accuracy in low-power, noisy environments.

Recent advancements in materials science and device physics have opened new avenues for energy-efficient neuromorphic computing. Emerging non-volatile memory technologies, such as memristors and phase-change memory, offer the potential for ultra-low-power synaptic operations. These devices can maintain their state without continuous power consumption, significantly reducing the overall energy footprint of neuromorphic systems.

The integration of energy harvesting techniques is another promising direction for improving energy efficiency in neuromorphic chips. By scavenging energy from the environment, such as through thermal gradients or mechanical vibrations, these systems could potentially operate autonomously with minimal external power input. This approach aligns closely with the self-sustaining nature of biological neural networks.

As neuromorphic chip designs continue to evolve, the focus on energy efficiency remains paramount. Researchers are exploring novel architectures that optimize data movement and minimize redundant computations. Event-driven processing, inspired by the brain's sparse and asynchronous operation, is being implemented to reduce power consumption during periods of low activity. Additionally, 3D integration techniques are being investigated to shorten interconnect lengths and reduce the energy cost of data transfer between neural elements.

Neuromorphic Chip Fabrication Techniques

Neuromorphic chip fabrication techniques have evolved significantly in recent years, driven by the need to create more efficient and brain-like computing systems. These techniques aim to produce chips that mimic the structure and function of biological neural networks, incorporating synapse circuits, plasticity models, and noise robustness features.

One of the primary fabrication methods for neuromorphic chips is the use of complementary metal-oxide-semiconductor (CMOS) technology. This well-established process allows for the integration of large numbers of artificial neurons and synapses on a single chip. Advanced CMOS techniques, such as 3D stacking and through-silicon vias (TSVs), enable the creation of high-density neuromorphic architectures with improved connectivity and reduced power consumption.

Another promising approach is the utilization of emerging non-volatile memory technologies, such as resistive random-access memory (RRAM) and phase-change memory (PCM). These materials can be integrated into CMOS processes to create synaptic elements with analog-like behavior, closely mimicking biological synapses. The ability to precisely control the resistance states of these devices allows for the implementation of synaptic plasticity and learning algorithms directly in hardware.

Photonic neuromorphic chips represent a cutting-edge fabrication technique that leverages optical components to process information. These chips use silicon photonics technology to create optical neurons and synapses, offering potential advantages in terms of speed and energy efficiency. Fabrication processes for photonic neuromorphic chips often involve the integration of lasers, waveguides, and photodetectors on a single substrate.

To address the challenges of noise robustness in neuromorphic systems, specialized fabrication techniques have been developed. These include the implementation of noise-resistant circuit designs and the incorporation of redundancy and error-correction mechanisms. Advanced packaging techniques, such as flip-chip bonding and wafer-level packaging, are employed to minimize external noise sources and improve overall system performance.

The fabrication of neuromorphic chips also involves the integration of specialized analog and mixed-signal circuits to implement plasticity models and learning algorithms. This requires precise control of device characteristics and careful consideration of process variations. Techniques such as mismatch compensation and adaptive biasing are often employed to ensure consistent performance across the chip.

As neuromorphic chip designs become more complex, advanced lithography and etching techniques are crucial for achieving the required feature sizes and densities. Extreme ultraviolet (EUV) lithography and multi-patterning techniques are being explored to push the boundaries of neuromorphic chip fabrication, enabling the creation of more sophisticated and powerful brain-inspired computing systems.

One of the primary fabrication methods for neuromorphic chips is the use of complementary metal-oxide-semiconductor (CMOS) technology. This well-established process allows for the integration of large numbers of artificial neurons and synapses on a single chip. Advanced CMOS techniques, such as 3D stacking and through-silicon vias (TSVs), enable the creation of high-density neuromorphic architectures with improved connectivity and reduced power consumption.

Another promising approach is the utilization of emerging non-volatile memory technologies, such as resistive random-access memory (RRAM) and phase-change memory (PCM). These materials can be integrated into CMOS processes to create synaptic elements with analog-like behavior, closely mimicking biological synapses. The ability to precisely control the resistance states of these devices allows for the implementation of synaptic plasticity and learning algorithms directly in hardware.

Photonic neuromorphic chips represent a cutting-edge fabrication technique that leverages optical components to process information. These chips use silicon photonics technology to create optical neurons and synapses, offering potential advantages in terms of speed and energy efficiency. Fabrication processes for photonic neuromorphic chips often involve the integration of lasers, waveguides, and photodetectors on a single substrate.

To address the challenges of noise robustness in neuromorphic systems, specialized fabrication techniques have been developed. These include the implementation of noise-resistant circuit designs and the incorporation of redundancy and error-correction mechanisms. Advanced packaging techniques, such as flip-chip bonding and wafer-level packaging, are employed to minimize external noise sources and improve overall system performance.

The fabrication of neuromorphic chips also involves the integration of specialized analog and mixed-signal circuits to implement plasticity models and learning algorithms. This requires precise control of device characteristics and careful consideration of process variations. Techniques such as mismatch compensation and adaptive biasing are often employed to ensure consistent performance across the chip.

As neuromorphic chip designs become more complex, advanced lithography and etching techniques are crucial for achieving the required feature sizes and densities. Extreme ultraviolet (EUV) lithography and multi-patterning techniques are being explored to push the boundaries of neuromorphic chip fabrication, enabling the creation of more sophisticated and powerful brain-inspired computing systems.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!