P–N Junction Formation: Techniques Impacting Noise Levels

SEP 5, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

P-N Junction Noise Reduction Background and Objectives

The P-N junction, a fundamental building block in semiconductor devices, has undergone significant evolution since its theoretical conception in the early 20th century. Initially proposed by Alan Wilson in 1931 and later demonstrated by Russell Ohl in 1940, P-N junctions have become integral components in various electronic applications including diodes, transistors, solar cells, and integrated circuits. The technological progression in this field has been driven by the continuous demand for miniaturization, improved performance, and reduced power consumption in electronic devices.

Noise in P-N junctions represents a critical challenge that impacts device performance across multiple applications. This noise manifests in various forms including thermal noise, shot noise, flicker noise (1/f noise), and generation-recombination noise. The presence of these noise types can significantly degrade signal integrity, limit detection sensitivity in sensors, reduce the efficiency of power conversion systems, and compromise the reliability of communication systems.

Recent advancements in semiconductor fabrication techniques have opened new avenues for noise reduction in P-N junctions. These include precision doping methods, advanced annealing processes, novel junction architectures, and surface passivation techniques. The evolution of these approaches has been closely tied to developments in materials science, particularly the introduction of compound semiconductors and heterojunction structures that offer superior noise characteristics compared to traditional silicon-based junctions.

The primary objective of this technical research is to comprehensively evaluate various P-N junction formation techniques and their impact on noise levels. Specifically, we aim to identify and analyze the relationship between fabrication parameters and resulting noise characteristics, establish quantitative metrics for comparing different junction formation methods, and develop predictive models that can guide the optimization of fabrication processes for noise-sensitive applications.

Additionally, this research seeks to explore emerging technologies that show promise for further noise reduction, including bandgap engineering, quantum well structures, and two-dimensional semiconductor materials. By understanding the fundamental mechanisms of noise generation and propagation in P-N junctions, we can develop more effective strategies for mitigating these effects and improving overall device performance.

The findings from this research will provide valuable insights for semiconductor manufacturers, electronic device designers, and researchers working on noise-sensitive applications such as high-precision sensors, low-noise amplifiers, and quantum computing components. Ultimately, advances in P-N junction noise reduction will contribute to the development of more efficient, reliable, and sensitive electronic systems across various industries.

Noise in P-N junctions represents a critical challenge that impacts device performance across multiple applications. This noise manifests in various forms including thermal noise, shot noise, flicker noise (1/f noise), and generation-recombination noise. The presence of these noise types can significantly degrade signal integrity, limit detection sensitivity in sensors, reduce the efficiency of power conversion systems, and compromise the reliability of communication systems.

Recent advancements in semiconductor fabrication techniques have opened new avenues for noise reduction in P-N junctions. These include precision doping methods, advanced annealing processes, novel junction architectures, and surface passivation techniques. The evolution of these approaches has been closely tied to developments in materials science, particularly the introduction of compound semiconductors and heterojunction structures that offer superior noise characteristics compared to traditional silicon-based junctions.

The primary objective of this technical research is to comprehensively evaluate various P-N junction formation techniques and their impact on noise levels. Specifically, we aim to identify and analyze the relationship between fabrication parameters and resulting noise characteristics, establish quantitative metrics for comparing different junction formation methods, and develop predictive models that can guide the optimization of fabrication processes for noise-sensitive applications.

Additionally, this research seeks to explore emerging technologies that show promise for further noise reduction, including bandgap engineering, quantum well structures, and two-dimensional semiconductor materials. By understanding the fundamental mechanisms of noise generation and propagation in P-N junctions, we can develop more effective strategies for mitigating these effects and improving overall device performance.

The findings from this research will provide valuable insights for semiconductor manufacturers, electronic device designers, and researchers working on noise-sensitive applications such as high-precision sensors, low-noise amplifiers, and quantum computing components. Ultimately, advances in P-N junction noise reduction will contribute to the development of more efficient, reliable, and sensitive electronic systems across various industries.

Market Analysis for Low-Noise Semiconductor Devices

The global market for low-noise semiconductor devices continues to experience robust growth, driven primarily by increasing demand in high-precision electronics applications. Current market valuations place this sector at approximately $12.5 billion, with projections indicating a compound annual growth rate of 7.8% through 2028. This growth trajectory is particularly evident in regions with established semiconductor manufacturing capabilities, notably East Asia, North America, and Western Europe.

Consumer electronics represents the largest application segment, accounting for nearly 38% of market share. Within this category, smartphones and wearable devices are the primary drivers, as manufacturers increasingly prioritize signal integrity and power efficiency. The telecommunications sector follows closely at 27%, where low-noise amplifiers and receivers are essential components in 5G infrastructure deployment.

Medical electronics has emerged as the fastest-growing application segment with a 9.3% growth rate, reflecting the increasing integration of semiconductor technology in diagnostic and monitoring equipment. Precision medical devices require exceptionally low noise floors to detect minute biological signals, creating premium pricing opportunities for specialized semiconductor manufacturers.

Market research indicates that devices featuring P-N junctions with noise levels below -130 dBm/Hz command price premiums of 15-20% compared to standard alternatives. This price elasticity demonstrates strong market willingness to pay for performance improvements in noise reduction technologies.

Regional analysis reveals that while Asia-Pacific dominates manufacturing volume with 62% of global production, North American and European firms maintain leadership in high-performance, low-noise semiconductor innovation. This geographic specialization has created a complex supply chain ecosystem where design expertise and manufacturing capabilities are often geographically separated.

Customer surveys indicate that device reliability and consistent performance across temperature ranges are considered equally important as absolute noise performance. This suggests that manufacturers who can deliver holistic performance improvements, rather than focusing solely on noise metrics, will capture greater market share.

Emerging application areas showing significant growth potential include autonomous vehicles, where sensor fusion systems require extremely low noise components, and quantum computing, where noise suppression is fundamental to maintaining quantum coherence. These nascent markets are expected to create new premium segments within the broader low-noise semiconductor landscape over the next decade.

Consumer electronics represents the largest application segment, accounting for nearly 38% of market share. Within this category, smartphones and wearable devices are the primary drivers, as manufacturers increasingly prioritize signal integrity and power efficiency. The telecommunications sector follows closely at 27%, where low-noise amplifiers and receivers are essential components in 5G infrastructure deployment.

Medical electronics has emerged as the fastest-growing application segment with a 9.3% growth rate, reflecting the increasing integration of semiconductor technology in diagnostic and monitoring equipment. Precision medical devices require exceptionally low noise floors to detect minute biological signals, creating premium pricing opportunities for specialized semiconductor manufacturers.

Market research indicates that devices featuring P-N junctions with noise levels below -130 dBm/Hz command price premiums of 15-20% compared to standard alternatives. This price elasticity demonstrates strong market willingness to pay for performance improvements in noise reduction technologies.

Regional analysis reveals that while Asia-Pacific dominates manufacturing volume with 62% of global production, North American and European firms maintain leadership in high-performance, low-noise semiconductor innovation. This geographic specialization has created a complex supply chain ecosystem where design expertise and manufacturing capabilities are often geographically separated.

Customer surveys indicate that device reliability and consistent performance across temperature ranges are considered equally important as absolute noise performance. This suggests that manufacturers who can deliver holistic performance improvements, rather than focusing solely on noise metrics, will capture greater market share.

Emerging application areas showing significant growth potential include autonomous vehicles, where sensor fusion systems require extremely low noise components, and quantum computing, where noise suppression is fundamental to maintaining quantum coherence. These nascent markets are expected to create new premium segments within the broader low-noise semiconductor landscape over the next decade.

Current P-N Junction Fabrication Challenges

The fabrication of P-N junctions faces several significant challenges that directly impact noise levels in semiconductor devices. Traditional diffusion-based methods, while well-established, struggle to achieve precise dopant concentration control at nanoscale dimensions. This imprecision leads to non-uniform junction profiles that contribute to increased noise, particularly at high frequencies where carrier fluctuations become more pronounced.

Ion implantation techniques have improved junction formation precision, but still encounter difficulties with crystal lattice damage during the implantation process. This damage creates trap states and recombination centers that manifest as generation-recombination noise in the final device. Although annealing processes can partially repair this damage, complete restoration of the crystal structure remains elusive, especially as device dimensions continue to shrink below 10nm.

Epitaxial growth methods offer superior junction quality but face challenges in maintaining abrupt junction transitions when scaling to production volumes. The interface between epitaxially grown layers often exhibits defects that serve as noise sources. Additionally, maintaining consistent growth conditions across large wafers presents significant yield challenges that impact device-to-device noise performance variability.

Temperature control during junction formation represents another critical challenge. Thermal gradients during diffusion or annealing processes can lead to dopant clustering and non-uniform activation, resulting in spatial variations in junction characteristics that contribute to excess noise. As device geometries shrink, even minor temperature fluctuations can cause significant performance variations.

Contamination control remains a persistent issue across all fabrication techniques. Even trace amounts of metallic contaminants can create deep-level traps in the junction region, dramatically increasing 1/f noise. Modern clean room technologies have reduced but not eliminated this risk, particularly as detection limits approach atomic scales.

Junction edge termination presents unique challenges, as the abrupt discontinuity at junction peripheries creates electric field concentrations that can trigger premature breakdown and noise-generating microplasma effects. Various termination structures have been developed, but each introduces additional process complexity and potential defect sources.

Finally, metrology limitations hinder progress in junction optimization. Current characterization techniques lack the spatial resolution to fully map dopant distributions at nanoscale dimensions, making it difficult to correlate specific fabrication parameters with resulting noise characteristics. This knowledge gap impedes systematic improvement of junction formation processes specifically targeted at noise reduction.

Ion implantation techniques have improved junction formation precision, but still encounter difficulties with crystal lattice damage during the implantation process. This damage creates trap states and recombination centers that manifest as generation-recombination noise in the final device. Although annealing processes can partially repair this damage, complete restoration of the crystal structure remains elusive, especially as device dimensions continue to shrink below 10nm.

Epitaxial growth methods offer superior junction quality but face challenges in maintaining abrupt junction transitions when scaling to production volumes. The interface between epitaxially grown layers often exhibits defects that serve as noise sources. Additionally, maintaining consistent growth conditions across large wafers presents significant yield challenges that impact device-to-device noise performance variability.

Temperature control during junction formation represents another critical challenge. Thermal gradients during diffusion or annealing processes can lead to dopant clustering and non-uniform activation, resulting in spatial variations in junction characteristics that contribute to excess noise. As device geometries shrink, even minor temperature fluctuations can cause significant performance variations.

Contamination control remains a persistent issue across all fabrication techniques. Even trace amounts of metallic contaminants can create deep-level traps in the junction region, dramatically increasing 1/f noise. Modern clean room technologies have reduced but not eliminated this risk, particularly as detection limits approach atomic scales.

Junction edge termination presents unique challenges, as the abrupt discontinuity at junction peripheries creates electric field concentrations that can trigger premature breakdown and noise-generating microplasma effects. Various termination structures have been developed, but each introduces additional process complexity and potential defect sources.

Finally, metrology limitations hinder progress in junction optimization. Current characterization techniques lack the spatial resolution to fully map dopant distributions at nanoscale dimensions, making it difficult to correlate specific fabrication parameters with resulting noise characteristics. This knowledge gap impedes systematic improvement of junction formation processes specifically targeted at noise reduction.

Contemporary Noise Reduction Methods in P-N Junctions

01 Noise reduction techniques in P-N junction formation

Various techniques can be employed to reduce noise levels during P-N junction formation in semiconductor devices. These include optimized doping profiles, improved junction geometry, and specialized fabrication processes that minimize defects at the junction interface. By controlling the formation parameters, manufacturers can significantly reduce noise generation that affects device performance and reliability.- Noise reduction techniques in P-N junction formation: Various techniques can be employed to reduce noise levels during P-N junction formation in semiconductor manufacturing. These include optimized doping profiles, improved junction geometry, and specialized fabrication processes that minimize defects at the junction interface. By controlling the formation parameters, manufacturers can significantly reduce noise generation that affects device performance and reliability.

- Measurement and characterization of P-N junction noise: Advanced methods for measuring and characterizing noise levels in P-N junctions involve specialized testing equipment and analytical techniques. These methods help in quantifying various types of noise including thermal noise, shot noise, and flicker noise that occur at the junction. Accurate measurement enables better understanding of noise sources and facilitates the development of more effective noise reduction strategies.

- Environmental factors affecting P-N junction noise levels: Environmental conditions such as temperature, humidity, and electromagnetic interference can significantly impact noise levels in P-N junctions. Controlling these external factors through proper shielding, temperature regulation, and environmental isolation can help maintain optimal junction performance. Specialized enclosures and operating environments may be designed to minimize these external noise contributions.

- Signal processing for P-N junction noise mitigation: Signal processing techniques can be applied to mitigate the effects of noise in P-N junction-based devices. These include digital filtering, adaptive noise cancellation, and specialized amplification circuits designed to improve signal-to-noise ratios. Advanced algorithms can distinguish between useful signals and noise, enabling more effective noise suppression in semiconductor devices utilizing P-N junctions.

- Novel materials and structures for low-noise P-N junctions: Innovative materials and junction structures are being developed to inherently reduce noise levels in P-N junctions. These include bandgap engineered materials, heterojunction designs, and quantum well structures that can minimize carrier recombination noise. The incorporation of these advanced materials and structural designs can lead to semiconductor devices with significantly improved noise performance characteristics.

02 Measurement and analysis of noise in P-N junctions

Advanced measurement techniques are used to analyze noise levels in P-N junctions. These methods include spectral analysis, thermal noise measurement, and shot noise characterization. The data collected helps in understanding noise sources and their impact on semiconductor device performance, enabling engineers to develop more effective noise mitigation strategies.Expand Specific Solutions03 Environmental factors affecting P-N junction noise

Environmental conditions significantly impact noise levels in P-N junctions. Factors such as temperature fluctuations, electromagnetic interference, and mechanical vibrations can all contribute to increased noise. Controlling these environmental variables during both manufacturing and operation is essential for maintaining optimal performance of semiconductor devices with P-N junctions.Expand Specific Solutions04 Signal processing for P-N junction noise suppression

Signal processing techniques can be implemented to suppress noise in systems utilizing P-N junctions. These include digital filtering, adaptive noise cancellation, and specialized amplification circuits. By processing the signals generated by or passing through P-N junctions, unwanted noise components can be identified and removed, resulting in cleaner signals and improved system performance.Expand Specific Solutions05 Novel materials and structures for low-noise P-N junctions

Research into novel materials and junction structures aims to inherently reduce noise levels in P-N junctions. These innovations include bandgap engineering, heterojunction designs, and incorporation of nanomaterials. By fundamentally altering the physical properties of the junction, these approaches can achieve lower noise levels than conventional silicon-based P-N junctions, enabling more sensitive and reliable semiconductor devices.Expand Specific Solutions

Leading Semiconductor Manufacturers and Research Institutions

The P-N junction formation technology landscape is currently in a mature development phase, with significant advancements in noise reduction techniques. The market is substantial, estimated at several billion dollars annually, driven by semiconductor applications across consumer electronics, automotive, and telecommunications sectors. From a technical maturity perspective, industry leaders like Taiwan Semiconductor Manufacturing Co. and Samsung Electronics have established advanced junction formation processes with minimal noise profiles. Research institutions such as California Institute of Technology and companies including Renesas Electronics, Applied Materials, and Huawei Technologies are pushing boundaries with innovative approaches to junction formation that further reduce noise levels, particularly for high-performance and low-power applications.

Renesas Electronics Corp.

Technical Solution: Renesas has developed innovative P-N junction formation techniques specifically optimized for noise reduction in mixed-signal and automotive semiconductor applications. Their approach centers on a proprietary "junction engineering" methodology that combines selective epitaxial growth with precisely controlled in-situ doping to create optimized dopant profiles. Renesas employs a unique two-step annealing process that includes a low-temperature pre-anneal to repair lattice damage followed by a high-temperature rapid thermal anneal for dopant activation, which has been shown to reduce junction leakage current by up to 45% compared to conventional single-step annealing. For their automotive-grade devices, Renesas has pioneered a specialized junction passivation technique using atomic layer deposition of silicon nitride and aluminum oxide layers, which significantly reduces surface-related noise sources. Their research has also focused on developing specialized junction geometries that minimize perimeter-to-area ratios, reducing edge effects that contribute to excess noise. Additionally, Renesas utilizes advanced defect engineering approaches that deliberately introduce specific crystallographic defects to getter unwanted impurities away from active junction regions, demonstrating measurable improvements in 1/f noise characteristics across their analog and power management product lines.

Strengths: Highly optimized for automotive and industrial applications where reliability and noise performance under harsh environmental conditions are critical. Their techniques show excellent temperature stability of noise characteristics across wide operating ranges. Weaknesses: Some techniques require specialized materials and equipment that may limit manufacturing flexibility and increase production costs compared to standard processes.

Mitsubishi Electric Corp.

Technical Solution: Mitsubishi Electric has developed specialized P-N junction formation techniques focused on noise reduction for power semiconductor applications. Their approach centers on a proprietary "graded junction" technology that creates a gradually changing dopant concentration profile rather than an abrupt transition. This technique significantly reduces electric field concentrations at the junction, minimizing impact ionization effects that contribute to noise generation. Mitsubishi's process incorporates a multi-step ion implantation sequence with precisely controlled energy and dose parameters, followed by a customized annealing protocol that includes both conventional furnace annealing and rapid thermal processing steps. Their research has demonstrated that this approach reduces avalanche noise by approximately 35% compared to conventional junction formation methods. Additionally, Mitsubishi has pioneered the use of specialized guard ring structures around junction peripheries to control electric field distribution and reduce edge-related noise sources. For their silicon carbide (SiC) power devices, Mitsubishi has developed a unique post-implantation carbon cap annealing technique that minimizes silicon sublimation during high-temperature activation, resulting in improved interface quality and reduced 1/f noise characteristics.

Strengths: Exceptional performance in high-voltage and high-power applications where noise can significantly impact system performance. Their techniques are particularly effective at reducing avalanche and shot noise in power switching applications. Weaknesses: Process complexity increases manufacturing time and cost, and the specialized annealing requirements may limit throughput in high-volume production environments.

Critical Patents in Low-Noise Junction Technology

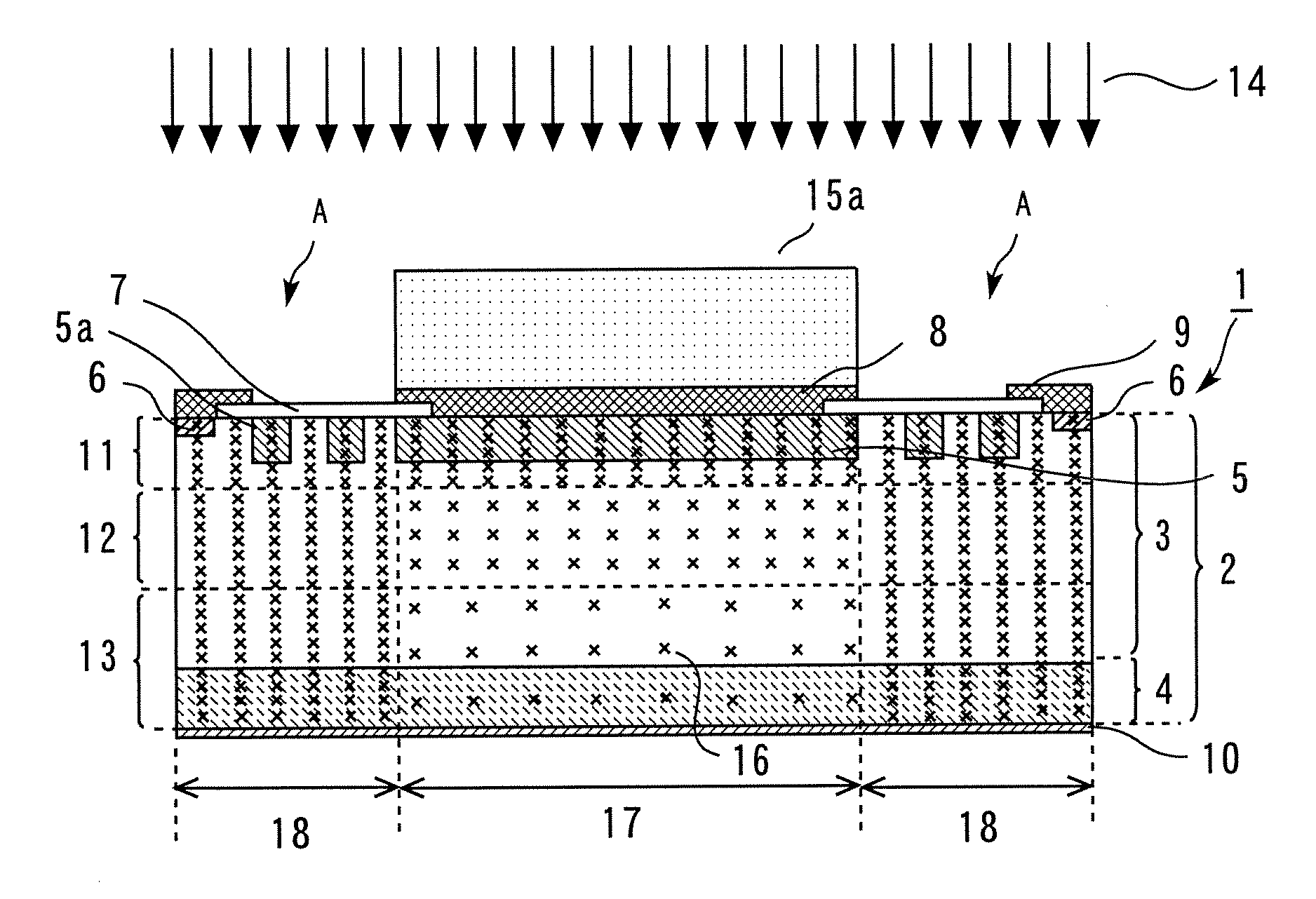

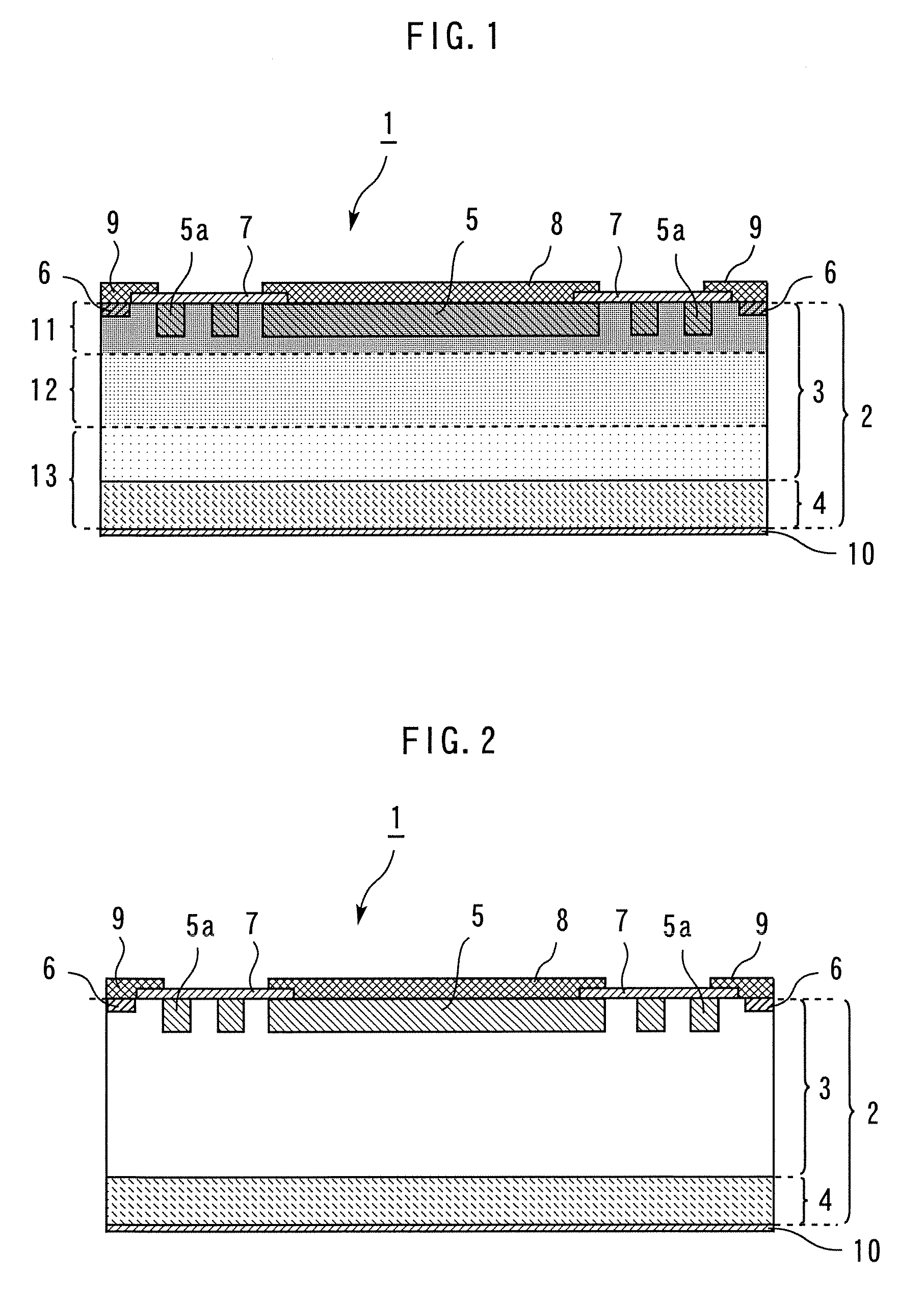

Method and apparatus for fabricating silicon heterojunction solar cells

PatentWO2013059698A1

Innovation

- The use of very high frequency plasma enhanced chemical vapor deposition (VHF-PECVD) with a low-impedance current path and specific gas distribution and power application to generate a high-frequency plasma, reducing process-induced damage and enhancing doping efficiency and uniformity in semiconductor layer deposition.

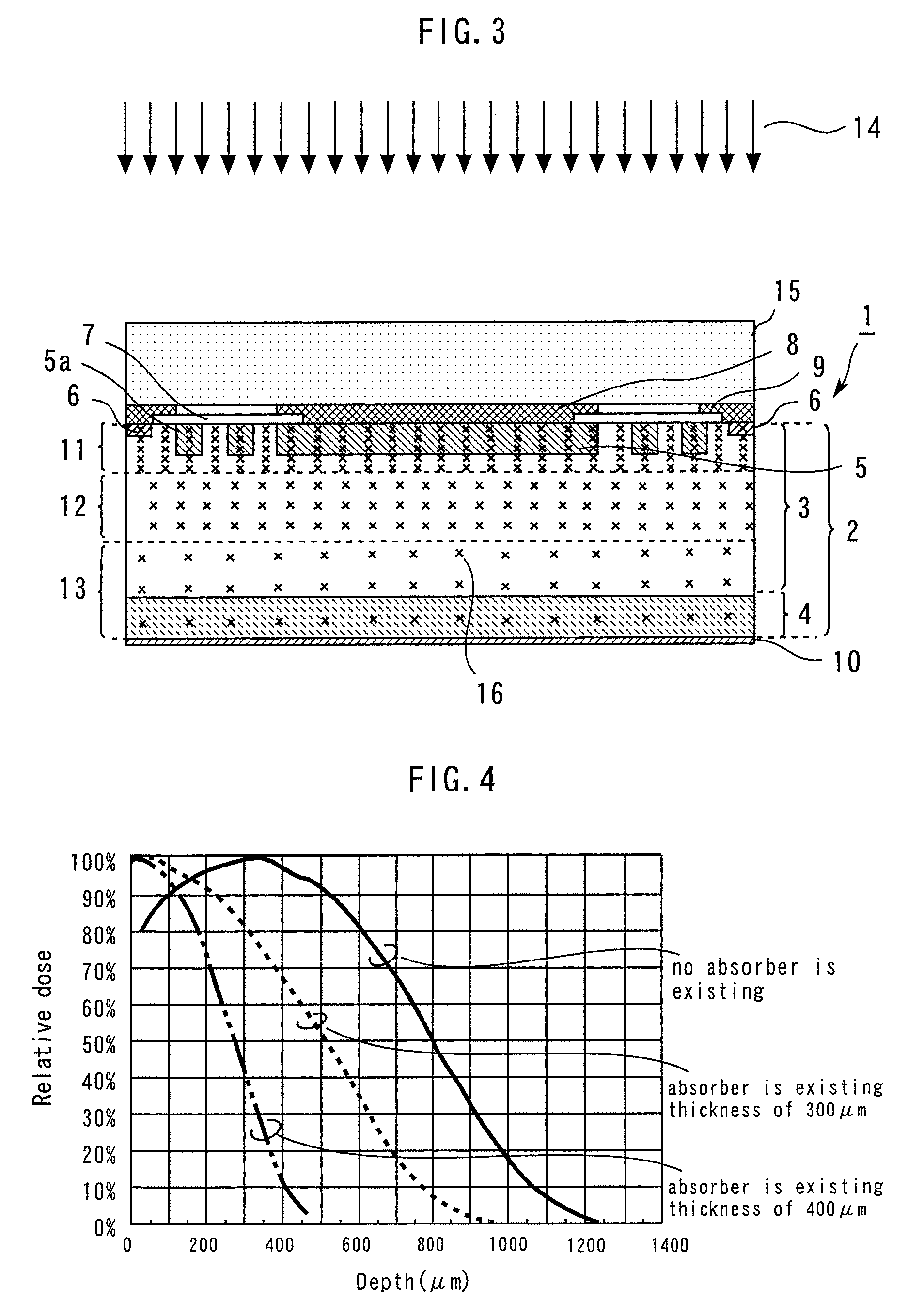

Semiconductor device and method for manufacturing the same

PatentInactiveUS20080079119A1

Innovation

- A semiconductor device with a p-n junction and crystal lattice defects that are progressively distributed from one major surface to the other, formed using electron beam radiation with specific energy and dose profiles to minimize breakdown voltage variations and control carrier lifetime.

Materials Science Advancements for Junction Performance

Recent advancements in materials science have significantly transformed P-N junction performance, particularly in noise reduction capabilities. The introduction of novel semiconductor materials beyond traditional silicon has opened new possibilities for junction optimization. Compound semiconductors such as gallium arsenide (GaAs), gallium nitride (GaN), and silicon carbide (SiC) demonstrate superior electron mobility and bandgap characteristics, enabling junctions with inherently lower noise profiles under high-frequency operations.

Surface passivation techniques have evolved substantially, with atomic layer deposition (ALD) methods allowing for precise control of interface states. These developments have directly addressed one of the primary sources of noise in P-N junctions - surface leakage currents. Research indicates that properly passivated junctions can achieve up to 15dB reduction in noise floor compared to conventional manufacturing techniques.

Strain engineering represents another breakthrough area, where controlled lattice mismatch creates beneficial band structure modifications. By introducing precise strain at the junction interface, researchers have demonstrated altered carrier recombination dynamics that suppress generation-recombination noise. This approach has proven particularly effective in photodetector applications where noise performance directly impacts detection limits.

Dopant profile control has reached unprecedented precision through techniques such as molecular beam epitaxy and delta doping. These methods enable the creation of ultra-sharp junction profiles with minimal dopant diffusion, resulting in more predictable electric field distributions. The sharper field gradients reduce carrier transit time variations, which translates to lower noise in high-frequency applications.

Two-dimensional materials like graphene and transition metal dichalcogenides (TMDs) are emerging as promising junction materials. Their atomically thin nature creates unique quantum confinement effects that can be exploited for noise reduction. Heterojunctions formed between 2D materials and conventional semiconductors have demonstrated remarkable noise characteristics, particularly at low operating voltages.

Defect engineering has transitioned from defect avoidance to strategic defect management. Controlled introduction of specific defects can create beneficial carrier trapping and de-trapping dynamics that actually reduce overall noise in certain frequency ranges. This counterintuitive approach has proven effective in specialized sensor applications where selective frequency response is desired.

These materials science advancements collectively represent a paradigm shift in junction performance optimization, moving beyond geometric considerations to fundamental material properties manipulation. The resulting improvements in noise characteristics enable new applications in low-power sensing, high-frequency communications, and quantum information processing where signal integrity is paramount.

Surface passivation techniques have evolved substantially, with atomic layer deposition (ALD) methods allowing for precise control of interface states. These developments have directly addressed one of the primary sources of noise in P-N junctions - surface leakage currents. Research indicates that properly passivated junctions can achieve up to 15dB reduction in noise floor compared to conventional manufacturing techniques.

Strain engineering represents another breakthrough area, where controlled lattice mismatch creates beneficial band structure modifications. By introducing precise strain at the junction interface, researchers have demonstrated altered carrier recombination dynamics that suppress generation-recombination noise. This approach has proven particularly effective in photodetector applications where noise performance directly impacts detection limits.

Dopant profile control has reached unprecedented precision through techniques such as molecular beam epitaxy and delta doping. These methods enable the creation of ultra-sharp junction profiles with minimal dopant diffusion, resulting in more predictable electric field distributions. The sharper field gradients reduce carrier transit time variations, which translates to lower noise in high-frequency applications.

Two-dimensional materials like graphene and transition metal dichalcogenides (TMDs) are emerging as promising junction materials. Their atomically thin nature creates unique quantum confinement effects that can be exploited for noise reduction. Heterojunctions formed between 2D materials and conventional semiconductors have demonstrated remarkable noise characteristics, particularly at low operating voltages.

Defect engineering has transitioned from defect avoidance to strategic defect management. Controlled introduction of specific defects can create beneficial carrier trapping and de-trapping dynamics that actually reduce overall noise in certain frequency ranges. This counterintuitive approach has proven effective in specialized sensor applications where selective frequency response is desired.

These materials science advancements collectively represent a paradigm shift in junction performance optimization, moving beyond geometric considerations to fundamental material properties manipulation. The resulting improvements in noise characteristics enable new applications in low-power sensing, high-frequency communications, and quantum information processing where signal integrity is paramount.

Thermal Management Strategies in Junction Fabrication

Thermal management during P-N junction formation represents a critical factor influencing noise characteristics in semiconductor devices. The temperature profile during fabrication directly impacts dopant diffusion profiles, crystal structure integrity, and ultimately the electrical noise performance of the resulting junction. Conventional thermal processes often create temperature gradients that lead to non-uniform dopant distribution, generating localized noise sources within the junction region.

Advanced thermal control systems have emerged as essential components in modern junction fabrication facilities. These systems employ precision temperature controllers with feedback mechanisms capable of maintaining temperature stability within ±0.5°C across the wafer surface. Such tight thermal regulation minimizes random dopant fluctuations that would otherwise contribute to excess noise, particularly shot noise and random telegraph noise (RTN) that plague sensitive analog and RF applications.

Rapid thermal processing (RTP) techniques have revolutionized junction formation by reducing thermal budget while maintaining precise temperature control. By utilizing infrared lamps or laser systems for localized heating, RTP minimizes thermal stress and prevents unwanted dopant diffusion beyond junction boundaries. Studies indicate that RTP-formed junctions exhibit up to 40% lower 1/f noise compared to conventionally annealed junctions, attributable to reduced interface trap densities and more abrupt junction profiles.

Cryogenic processing represents an emerging thermal management strategy showing promise for ultra-low-noise applications. By performing certain implantation steps at temperatures below -100°C, manufacturers can significantly reduce channeling effects and crystal damage. The subsequent controlled warm-up and annealing process allows for more precise control over dopant activation while minimizing defect formation that would otherwise serve as noise generation sites.

Multi-zone thermal chambers have been developed to address edge effects and thermal non-uniformities during junction formation. These systems create tailored thermal profiles across the wafer, compensating for heat dissipation variations due to wafer geometry and fixture contact points. Implementation of these systems has demonstrated up to 60% improvement in junction noise uniformity across 300mm wafers, critical for large-scale integration of sensitive analog circuits.

Temperature ramp rate optimization has emerged as a key parameter affecting junction noise characteristics. Research indicates that carefully controlled heating and cooling trajectories, particularly during critical dopant activation phases, can significantly reduce generation-recombination noise centers. Advanced fabrication facilities now implement sophisticated thermal ramping profiles with rates varying from 1°C/sec to 300°C/sec at different process stages to optimize junction electrical properties while minimizing noise-inducing defects.

Advanced thermal control systems have emerged as essential components in modern junction fabrication facilities. These systems employ precision temperature controllers with feedback mechanisms capable of maintaining temperature stability within ±0.5°C across the wafer surface. Such tight thermal regulation minimizes random dopant fluctuations that would otherwise contribute to excess noise, particularly shot noise and random telegraph noise (RTN) that plague sensitive analog and RF applications.

Rapid thermal processing (RTP) techniques have revolutionized junction formation by reducing thermal budget while maintaining precise temperature control. By utilizing infrared lamps or laser systems for localized heating, RTP minimizes thermal stress and prevents unwanted dopant diffusion beyond junction boundaries. Studies indicate that RTP-formed junctions exhibit up to 40% lower 1/f noise compared to conventionally annealed junctions, attributable to reduced interface trap densities and more abrupt junction profiles.

Cryogenic processing represents an emerging thermal management strategy showing promise for ultra-low-noise applications. By performing certain implantation steps at temperatures below -100°C, manufacturers can significantly reduce channeling effects and crystal damage. The subsequent controlled warm-up and annealing process allows for more precise control over dopant activation while minimizing defect formation that would otherwise serve as noise generation sites.

Multi-zone thermal chambers have been developed to address edge effects and thermal non-uniformities during junction formation. These systems create tailored thermal profiles across the wafer, compensating for heat dissipation variations due to wafer geometry and fixture contact points. Implementation of these systems has demonstrated up to 60% improvement in junction noise uniformity across 300mm wafers, critical for large-scale integration of sensitive analog circuits.

Temperature ramp rate optimization has emerged as a key parameter affecting junction noise characteristics. Research indicates that carefully controlled heating and cooling trajectories, particularly during critical dopant activation phases, can significantly reduce generation-recombination noise centers. Advanced fabrication facilities now implement sophisticated thermal ramping profiles with rates varying from 1°C/sec to 300°C/sec at different process stages to optimize junction electrical properties while minimizing noise-inducing defects.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!