How to Measure Charge Carrier Density in P–N Junctions

SEP 4, 202510 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

P-N Junction Carrier Density Measurement Background and Objectives

P-N junctions represent one of the most fundamental structures in semiconductor physics and electronic devices, serving as the building blocks for numerous applications including diodes, transistors, solar cells, and integrated circuits. The measurement of charge carrier density within these junctions has evolved significantly since the discovery of semiconductor properties in the early 20th century, with major advancements occurring during the development of solid-state electronics in the 1940s and 1950s.

The accurate determination of carrier density distributions across P-N junctions is crucial for understanding device performance, reliability, and efficiency. Historically, this field has progressed from basic theoretical models to sophisticated measurement techniques that can provide spatial resolution at the nanometer scale. The evolution of measurement methodologies has closely followed technological advancements in instrumentation, computational capabilities, and fabrication processes.

Current technological trends point toward increasingly miniaturized semiconductor devices with complex three-dimensional architectures, placing greater demands on measurement precision and spatial resolution. The industry's push toward more efficient power electronics, higher-density memory, and quantum computing applications further emphasizes the need for advanced carrier density measurement techniques that can operate under various conditions and at different scales.

The primary technical objectives in this domain include developing non-destructive measurement methods that can provide real-time, in-situ characterization of carrier densities with high spatial resolution. Additionally, there is a growing need for techniques that can function across a wide range of temperatures, under various bias conditions, and in different material systems beyond traditional silicon, such as wide-bandgap semiconductors and emerging 2D materials.

Another critical goal is to bridge the gap between theoretical models and experimental measurements, enabling more accurate device simulation and design optimization. This includes accounting for quantum effects, surface states, and interface phenomena that become increasingly dominant as device dimensions shrink to the nanoscale.

The integration of multiple measurement techniques to provide complementary information represents another important objective, as no single method can capture all aspects of carrier behavior in complex semiconductor structures. This multi-modal approach aims to create a more comprehensive understanding of carrier dynamics, including concentration, mobility, lifetime, and recombination mechanisms.

Ultimately, advances in carrier density measurement techniques are expected to enable the next generation of semiconductor devices with improved performance, reduced power consumption, and enhanced reliability, supporting continued innovation across the electronics industry and emerging technologies such as quantum computing, neuromorphic systems, and flexible electronics.

The accurate determination of carrier density distributions across P-N junctions is crucial for understanding device performance, reliability, and efficiency. Historically, this field has progressed from basic theoretical models to sophisticated measurement techniques that can provide spatial resolution at the nanometer scale. The evolution of measurement methodologies has closely followed technological advancements in instrumentation, computational capabilities, and fabrication processes.

Current technological trends point toward increasingly miniaturized semiconductor devices with complex three-dimensional architectures, placing greater demands on measurement precision and spatial resolution. The industry's push toward more efficient power electronics, higher-density memory, and quantum computing applications further emphasizes the need for advanced carrier density measurement techniques that can operate under various conditions and at different scales.

The primary technical objectives in this domain include developing non-destructive measurement methods that can provide real-time, in-situ characterization of carrier densities with high spatial resolution. Additionally, there is a growing need for techniques that can function across a wide range of temperatures, under various bias conditions, and in different material systems beyond traditional silicon, such as wide-bandgap semiconductors and emerging 2D materials.

Another critical goal is to bridge the gap between theoretical models and experimental measurements, enabling more accurate device simulation and design optimization. This includes accounting for quantum effects, surface states, and interface phenomena that become increasingly dominant as device dimensions shrink to the nanoscale.

The integration of multiple measurement techniques to provide complementary information represents another important objective, as no single method can capture all aspects of carrier behavior in complex semiconductor structures. This multi-modal approach aims to create a more comprehensive understanding of carrier dynamics, including concentration, mobility, lifetime, and recombination mechanisms.

Ultimately, advances in carrier density measurement techniques are expected to enable the next generation of semiconductor devices with improved performance, reduced power consumption, and enhanced reliability, supporting continued innovation across the electronics industry and emerging technologies such as quantum computing, neuromorphic systems, and flexible electronics.

Market Applications and Demand for Carrier Density Characterization

The precise measurement of charge carrier density in p-n junctions has become increasingly critical across multiple industries, driving significant market demand for advanced characterization techniques. The semiconductor industry represents the largest market segment, with an estimated global value exceeding $550 billion in 2023. Within this sector, accurate carrier density measurements directly impact device performance optimization, yield improvement, and quality control processes for integrated circuits, power electronics, and optoelectronic components.

The photovoltaic industry demonstrates particularly strong demand for carrier density characterization, as solar cell efficiency is fundamentally linked to carrier concentration and distribution across junction interfaces. With the global solar market growing at approximately 25% annually, manufacturers require increasingly sophisticated measurement techniques to develop high-efficiency cells that can achieve conversion efficiencies beyond 26% for single-junction designs.

Telecommunications and data infrastructure sectors represent another substantial market, where carrier density measurements enable the development of high-speed transistors, photodetectors, and laser diodes. The rollout of 5G networks and beyond has intensified demand for semiconductor devices operating at higher frequencies with precise carrier control, creating a specialized market for advanced junction characterization tools estimated at $3.2 billion.

The automotive industry's transition toward electric vehicles has dramatically expanded the need for power semiconductor devices with optimized p-n junctions. This sector requires carrier density measurement solutions that can evaluate wide-bandgap materials like silicon carbide and gallium nitride, which are increasingly replacing traditional silicon in high-power applications. Market analysts project this segment to grow at 30% annually through 2028.

Research institutions and semiconductor foundries represent a stable market base, consistently investing in advanced metrology equipment. The academic research market alone accounts for approximately $1.8 billion in annual spending on semiconductor characterization tools, with carrier density measurement systems comprising a significant portion.

Emerging applications in quantum computing, neuromorphic computing, and flexible electronics are creating new market opportunities for specialized carrier density measurement techniques. These nascent fields require unprecedented precision in junction characterization, often at cryogenic temperatures or under unique operating conditions that conventional tools cannot adequately address.

The geographical distribution of market demand shows concentration in East Asia (particularly Taiwan, South Korea, and Japan), North America, and Europe, aligning with major semiconductor manufacturing hubs. However, growing investments in semiconductor fabrication capabilities in India, Southeast Asia, and the Middle East are expanding the global market footprint for carrier density measurement technologies.

The photovoltaic industry demonstrates particularly strong demand for carrier density characterization, as solar cell efficiency is fundamentally linked to carrier concentration and distribution across junction interfaces. With the global solar market growing at approximately 25% annually, manufacturers require increasingly sophisticated measurement techniques to develop high-efficiency cells that can achieve conversion efficiencies beyond 26% for single-junction designs.

Telecommunications and data infrastructure sectors represent another substantial market, where carrier density measurements enable the development of high-speed transistors, photodetectors, and laser diodes. The rollout of 5G networks and beyond has intensified demand for semiconductor devices operating at higher frequencies with precise carrier control, creating a specialized market for advanced junction characterization tools estimated at $3.2 billion.

The automotive industry's transition toward electric vehicles has dramatically expanded the need for power semiconductor devices with optimized p-n junctions. This sector requires carrier density measurement solutions that can evaluate wide-bandgap materials like silicon carbide and gallium nitride, which are increasingly replacing traditional silicon in high-power applications. Market analysts project this segment to grow at 30% annually through 2028.

Research institutions and semiconductor foundries represent a stable market base, consistently investing in advanced metrology equipment. The academic research market alone accounts for approximately $1.8 billion in annual spending on semiconductor characterization tools, with carrier density measurement systems comprising a significant portion.

Emerging applications in quantum computing, neuromorphic computing, and flexible electronics are creating new market opportunities for specialized carrier density measurement techniques. These nascent fields require unprecedented precision in junction characterization, often at cryogenic temperatures or under unique operating conditions that conventional tools cannot adequately address.

The geographical distribution of market demand shows concentration in East Asia (particularly Taiwan, South Korea, and Japan), North America, and Europe, aligning with major semiconductor manufacturing hubs. However, growing investments in semiconductor fabrication capabilities in India, Southeast Asia, and the Middle East are expanding the global market footprint for carrier density measurement technologies.

Current Techniques and Challenges in Carrier Density Measurement

The measurement of charge carrier density in p-n junctions represents a critical aspect of semiconductor device characterization. Currently, several established techniques exist for this purpose, each with specific advantages and limitations. Hall effect measurements remain one of the most traditional approaches, providing valuable information about carrier concentration and mobility. However, this method faces significant challenges when applied to p-n junctions due to the presence of both carrier types and the depletion region, which complicates data interpretation.

Capacitance-voltage (C-V) profiling has emerged as a widely adopted technique that allows for spatial resolution of carrier density across the junction. By measuring the capacitance response to varying bias voltages, researchers can extract carrier concentration profiles. While powerful, this method suffers from resolution limitations at nanoscale dimensions and struggles with accuracy in high-frequency applications or when dealing with deep-level traps.

Scanning probe microscopy techniques, including Kelvin probe force microscopy (KPFM) and scanning capacitance microscopy (SCM), offer nanoscale spatial resolution for carrier density measurements. These approaches enable direct visualization of carrier distributions across junction interfaces but are primarily surface-sensitive and may not accurately represent bulk properties. Additionally, they require sophisticated equipment and careful sample preparation.

Optical methods such as photoluminescence spectroscopy and Raman spectroscopy provide non-destructive alternatives for carrier density assessment. These techniques analyze the spectral characteristics of light emitted or scattered from the semiconductor material to infer carrier concentrations. However, they often lack the spatial resolution required for detailed junction analysis and may be influenced by surface states and defects.

Secondary ion mass spectrometry (SIMS) offers excellent depth profiling capabilities but measures dopant concentration rather than actual carrier density, which may differ significantly due to incomplete ionization or compensation effects. Electron holography in transmission electron microscopy provides direct visualization of electric potential across junctions but requires complex sample preparation and specialized equipment.

The primary challenges in carrier density measurement include achieving sufficient spatial resolution to characterize modern nanoscale devices, distinguishing between different carrier types in the same region, and developing non-destructive methods suitable for in-line manufacturing processes. Additionally, measurements at extreme conditions (high temperatures or under illumination) remain difficult but are increasingly important for understanding device performance in real-world applications.

Recent developments in scanning microwave impedance microscopy and terahertz spectroscopy show promise for overcoming some of these limitations, but significant technical hurdles remain before these techniques can be widely adopted in industrial settings.

Capacitance-voltage (C-V) profiling has emerged as a widely adopted technique that allows for spatial resolution of carrier density across the junction. By measuring the capacitance response to varying bias voltages, researchers can extract carrier concentration profiles. While powerful, this method suffers from resolution limitations at nanoscale dimensions and struggles with accuracy in high-frequency applications or when dealing with deep-level traps.

Scanning probe microscopy techniques, including Kelvin probe force microscopy (KPFM) and scanning capacitance microscopy (SCM), offer nanoscale spatial resolution for carrier density measurements. These approaches enable direct visualization of carrier distributions across junction interfaces but are primarily surface-sensitive and may not accurately represent bulk properties. Additionally, they require sophisticated equipment and careful sample preparation.

Optical methods such as photoluminescence spectroscopy and Raman spectroscopy provide non-destructive alternatives for carrier density assessment. These techniques analyze the spectral characteristics of light emitted or scattered from the semiconductor material to infer carrier concentrations. However, they often lack the spatial resolution required for detailed junction analysis and may be influenced by surface states and defects.

Secondary ion mass spectrometry (SIMS) offers excellent depth profiling capabilities but measures dopant concentration rather than actual carrier density, which may differ significantly due to incomplete ionization or compensation effects. Electron holography in transmission electron microscopy provides direct visualization of electric potential across junctions but requires complex sample preparation and specialized equipment.

The primary challenges in carrier density measurement include achieving sufficient spatial resolution to characterize modern nanoscale devices, distinguishing between different carrier types in the same region, and developing non-destructive methods suitable for in-line manufacturing processes. Additionally, measurements at extreme conditions (high temperatures or under illumination) remain difficult but are increasingly important for understanding device performance in real-world applications.

Recent developments in scanning microwave impedance microscopy and terahertz spectroscopy show promise for overcoming some of these limitations, but significant technical hurdles remain before these techniques can be widely adopted in industrial settings.

Established Carrier Density Measurement Methodologies

01 Fundamentals of P-N Junction Charge Carrier Behavior

P-N junctions exhibit specific charge carrier density distributions that are fundamental to semiconductor device operation. The junction forms a depletion region where mobile carriers are depleted, creating an electric field. The carrier concentration varies exponentially with distance from the junction, following diffusion equations. Understanding these carrier density profiles is essential for designing and optimizing semiconductor devices including diodes and transistors.- Fundamentals of P-N Junction Charge Carrier Behavior: P-N junctions exhibit specific charge carrier density distributions due to the diffusion and drift of electrons and holes across the junction. The depletion region forms as mobile carriers recombine, leaving behind fixed charges that create an electric field. This fundamental behavior governs the electrical characteristics of semiconductor devices, including the relationship between carrier concentration gradients and junction potential.

- Measurement and Analysis Techniques for Carrier Density: Various methods have been developed to measure and analyze charge carrier density in P-N junctions. These include optical techniques, electrical characterization methods, and computational modeling approaches. Advanced imaging and spectroscopy allow for spatial mapping of carrier distributions, while electrical measurements provide quantitative data on carrier concentrations under different operating conditions.

- Temperature and Environmental Effects on Carrier Density: Temperature significantly impacts charge carrier density in P-N junctions through thermal generation and recombination processes. Environmental factors such as radiation exposure, humidity, and pressure can also alter carrier concentrations. Understanding these effects is crucial for designing semiconductor devices that maintain stable performance across varying operating conditions.

- Novel Materials and Structures for Carrier Density Control: Advanced semiconductor materials and novel junction structures have been developed to precisely control charge carrier density. These include heterojunctions, quantum wells, and nanostructured materials that enable tailored carrier profiles. Such innovations allow for enhanced device performance through optimized carrier transport properties and reduced recombination losses.

- Modeling and Simulation of P-N Junction Carrier Dynamics: Computational models and simulation techniques have been developed to predict and analyze charge carrier dynamics in P-N junctions. These approaches incorporate quantum mechanical effects, carrier generation-recombination mechanisms, and transport phenomena to provide insights into device behavior. Simulation tools enable optimization of junction designs before physical fabrication, accelerating the development of advanced semiconductor devices.

02 Measurement and Analysis Techniques for Charge Carrier Density

Various techniques have been developed to measure and analyze charge carrier density in P-N junctions. These include optical methods, electrical characterization, and advanced imaging techniques that can map carrier distributions with high spatial resolution. These measurement approaches help in understanding device performance, validating theoretical models, and identifying defects or irregularities in semiconductor structures.Expand Specific Solutions03 Modulation and Control of Carrier Density

Methods for modulating and controlling charge carrier density in P-N junctions involve techniques such as doping profile engineering, application of external electric fields, temperature control, and illumination. These approaches allow for dynamic adjustment of carrier concentrations, enabling the development of devices with specific electrical characteristics and improved performance in various applications.Expand Specific Solutions04 Advanced P-N Junction Structures and Materials

Novel materials and junction structures have been developed to enhance control over charge carrier density. These include heterojunctions, quantum wells, and nanostructured semiconductors that offer unique carrier confinement properties. Advanced material systems allow for precise engineering of band structures and carrier distributions, leading to improved efficiency in optoelectronic devices, solar cells, and high-frequency applications.Expand Specific Solutions05 Simulation and Modeling of Carrier Density Distributions

Computational methods for simulating and modeling charge carrier density in P-N junctions enable prediction of device behavior under various conditions. These include finite element analysis, Monte Carlo simulations, and quantum mechanical models that account for carrier generation, recombination, and transport phenomena. Simulation tools help optimize device designs before fabrication, reducing development cycles and improving performance outcomes.Expand Specific Solutions

Leading Research Institutions and Semiconductor Industry Players

The charge carrier density measurement in P-N junctions market is currently in a growth phase, with increasing demand driven by semiconductor manufacturing advancements. The global market size is expanding due to rising applications in electronics, photovoltaics, and power devices. Technologically, the field shows varying maturity levels across different measurement approaches. Leading players like KLA Corp. and Infineon Technologies AG offer advanced commercial solutions, while research institutions such as Shanghai Institute of Technical Physics, Interuniversitair Micro-Electronica Centrum, and Institute of Semiconductors CAS drive innovation through fundamental research. Semiconductor manufacturers including United Microelectronics, Texas Instruments, and Shin-Etsu Handotai represent key stakeholders requiring precise measurement capabilities for product development and quality control.

Interuniversitair Micro-Electronica Centrum VZW

Technical Solution: IMEC has developed a multi-modal approach to charge carrier density measurement in p-n junctions that combines electrical, optical, and physical characterization techniques. Their primary innovation is a scanning capacitance microscopy (SCM) system with advanced signal processing algorithms that can achieve sub-10nm resolution in carrier profiling. IMEC's methodology integrates conventional capacitance-voltage measurements with Kelvin probe force microscopy (KPFM) to simultaneously map both carrier concentration and built-in potential across junction interfaces[1]. The center has pioneered the use of photoluminescence spectroscopy combined with electrochemical capacitance-voltage profiling to distinguish between different types of dopants and identify compensation effects. IMEC's carrier measurement platform incorporates machine learning algorithms that can extract carrier density profiles from complex measurement data, accounting for measurement artifacts and junction geometry effects[3]. Their system also includes temperature-dependent Hall effect measurements (80K-400K) that enable the separation of carrier mobility and concentration effects, particularly valuable for wide-bandgap semiconductor materials.

Strengths: Exceptional spatial resolution (sub-10nm) for advanced node semiconductor devices; comprehensive characterization of both majority and minority carriers; ability to measure carrier densities in three dimensions. Weaknesses: Complex measurement setup requiring specialized expertise; longer measurement times compared to standard industrial techniques; challenges in absolute calibration for novel semiconductor materials.

Institute of Semiconductors of Chinese Academy of Sciences

Technical Solution: The Institute of Semiconductors of Chinese Academy of Sciences has developed a comprehensive suite of techniques for measuring charge carrier density in p-n junctions, particularly focused on wide-bandgap semiconductors and novel material systems. Their approach combines conventional capacitance-voltage profiling with advanced scanning probe microscopy techniques, including Scanning Spreading Resistance Microscopy (SSRM) and Scanning Capacitance Microscopy (SCM) with nanometer-scale resolution. The Institute has pioneered the use of temperature-dependent Hall effect measurements (10K-800K) coupled with deep-level transient spectroscopy (DLTS) to provide detailed information about carrier activation energies and trap states that influence effective carrier concentrations[1]. Their methodology incorporates specialized sample preparation techniques, including focused ion beam (FIB) cross-sectioning and low-damage polishing procedures, to minimize measurement artifacts. The Institute has also developed novel optical techniques based on Raman spectroscopy and photoluminescence that can provide non-contact carrier density measurements, particularly valuable for sensitive materials where conventional probing might introduce defects[4]. Their measurement systems include sophisticated modeling software that can account for quantum confinement effects in nanoscale junctions and heterojunctions.

Strengths: Exceptional expertise in characterizing novel semiconductor materials including SiC, GaN, and 2D materials; comprehensive approach combining electrical, optical, and physical characterization; advanced modeling capabilities for complex junction structures. Weaknesses: Some techniques require specialized equipment not widely available in industrial settings; longer measurement times for comprehensive characterization; challenges in standardization across different material systems.

Critical Patents and Research in Carrier Density Metrology

Process and device for the optical determination of charge carrier density variations in semiconductor components

PatentWO1993011440A1

Innovation

- The method employs an acousto-optical Bragg cell to split a laser beam into probe and reference beams, allowing for rapid adjustment of their distance and alignment using an acoustic frequency control signal, eliminating the need for laser beam polarization and enabling quick adaptation to varying channel widths by changing the splitting angle, which is converted into a change in beam distance using a lens device.

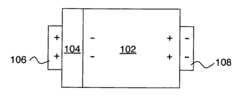

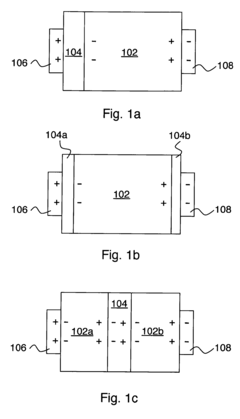

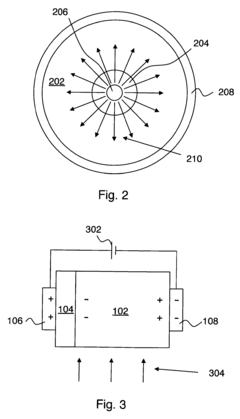

Energy storage device with large charge separation

PatentActiveUS20120313589A1

Innovation

- The development of semiconductor-based energy storage devices that utilize plasma formation and p-n junctions to achieve high energy density through charge separation and increased permittivity, allowing for higher charge densities and efficient energy storage.

Semiconductor Device Performance Correlation with Carrier Density

The correlation between semiconductor device performance and carrier density represents a fundamental relationship in semiconductor physics and engineering. Device characteristics such as switching speed, power consumption, and overall efficiency are directly influenced by the concentration and distribution of charge carriers within the semiconductor material, particularly at p-n junctions.

Carrier density measurements provide critical insights into how devices will perform under various operating conditions. Higher carrier densities typically enable faster switching speeds in transistors due to increased current flow capabilities, but may simultaneously lead to higher power consumption and heat generation. This trade-off becomes particularly important in modern semiconductor applications where energy efficiency is paramount.

For power electronics applications, understanding the relationship between carrier density and breakdown voltage is essential. Devices with optimized carrier density profiles can achieve higher blocking voltages while maintaining low on-state resistance, significantly improving energy conversion efficiency in power systems.

In optoelectronic devices such as LEDs and solar cells, carrier density directly impacts quantum efficiency. The recombination rate of electrons and holes, which determines light emission in LEDs or charge collection in solar cells, is proportional to the product of electron and hole densities. Precise carrier density engineering enables manufacturers to maximize device efficiency and performance.

Temperature sensitivity of semiconductor devices can also be traced to carrier density variations. As temperature increases, intrinsic carrier concentration rises exponentially, potentially altering device characteristics. Devices designed with appropriate carrier density profiles demonstrate improved thermal stability and reliability across wider operating temperature ranges.

Modern integrated circuit performance metrics such as clock speed and power density correlate strongly with carrier density management. The continuous miniaturization of semiconductor devices has made carrier density engineering increasingly critical, as quantum effects become more pronounced at nanoscale dimensions.

Statistical analysis of manufacturing data consistently shows that variations in carrier density account for significant portions of device-to-device performance variations. This understanding has led to more sophisticated process control techniques focused on achieving precise and uniform carrier density distributions across wafers.

Carrier density measurements provide critical insights into how devices will perform under various operating conditions. Higher carrier densities typically enable faster switching speeds in transistors due to increased current flow capabilities, but may simultaneously lead to higher power consumption and heat generation. This trade-off becomes particularly important in modern semiconductor applications where energy efficiency is paramount.

For power electronics applications, understanding the relationship between carrier density and breakdown voltage is essential. Devices with optimized carrier density profiles can achieve higher blocking voltages while maintaining low on-state resistance, significantly improving energy conversion efficiency in power systems.

In optoelectronic devices such as LEDs and solar cells, carrier density directly impacts quantum efficiency. The recombination rate of electrons and holes, which determines light emission in LEDs or charge collection in solar cells, is proportional to the product of electron and hole densities. Precise carrier density engineering enables manufacturers to maximize device efficiency and performance.

Temperature sensitivity of semiconductor devices can also be traced to carrier density variations. As temperature increases, intrinsic carrier concentration rises exponentially, potentially altering device characteristics. Devices designed with appropriate carrier density profiles demonstrate improved thermal stability and reliability across wider operating temperature ranges.

Modern integrated circuit performance metrics such as clock speed and power density correlate strongly with carrier density management. The continuous miniaturization of semiconductor devices has made carrier density engineering increasingly critical, as quantum effects become more pronounced at nanoscale dimensions.

Statistical analysis of manufacturing data consistently shows that variations in carrier density account for significant portions of device-to-device performance variations. This understanding has led to more sophisticated process control techniques focused on achieving precise and uniform carrier density distributions across wafers.

Standardization and Calibration Protocols for Measurement Accuracy

Accurate measurement of charge carrier density in p-n junctions requires robust standardization and calibration protocols to ensure reliability and reproducibility. These protocols serve as the foundation for consistent measurements across different laboratories and research institutions, enabling meaningful comparison of results and advancement of semiconductor technology.

The development of standardized measurement procedures begins with the establishment of reference materials with well-characterized carrier densities. Silicon and germanium reference samples with precisely controlled doping profiles are widely used as calibration standards. These reference materials undergo rigorous certification processes by national metrology institutes such as NIST (USA), PTB (Germany), and AIST (Japan) to ensure traceability to fundamental physical constants.

Calibration of measurement equipment represents a critical aspect of accurate carrier density determination. Hall effect measurement systems require regular calibration using reference samples to account for magnetic field non-uniformities and contact resistance effects. For capacitance-voltage profiling techniques, calibration involves verification of voltage source accuracy and capacitance meter linearity across the measurement range. Temperature control during calibration is particularly important, as carrier mobility and density exhibit strong temperature dependence.

Measurement uncertainty analysis constitutes an essential component of standardization protocols. This includes quantification of systematic errors from equipment limitations, random errors from environmental fluctuations, and sample-specific uncertainties. The Joint Committee for Guides in Metrology (JCGM) provides guidelines for uncertainty calculation that have been adapted specifically for semiconductor measurements by industry consortia like SEMI and IEEE.

Inter-laboratory comparison studies play a vital role in validating measurement protocols. These round-robin tests involve multiple facilities measuring identical samples and comparing results to identify systematic biases and establish measurement reproducibility limits. The International Technology Roadmap for Semiconductors (ITRS) has coordinated several such studies, establishing benchmark data for various measurement techniques.

Automation of calibration procedures has significantly improved measurement accuracy in recent years. Software-controlled calibration routines can compensate for drift in measurement parameters and apply correction factors in real-time. Machine learning algorithms are increasingly being deployed to recognize measurement artifacts and optimize calibration intervals based on equipment performance history.

Documentation and training standards ensure proper implementation of measurement protocols across the semiconductor industry. Detailed procedural documents with step-by-step instructions, acceptance criteria, and troubleshooting guides help maintain measurement consistency. Certification programs for measurement technicians further reinforce adherence to standardized practices and proper interpretation of results.

The development of standardized measurement procedures begins with the establishment of reference materials with well-characterized carrier densities. Silicon and germanium reference samples with precisely controlled doping profiles are widely used as calibration standards. These reference materials undergo rigorous certification processes by national metrology institutes such as NIST (USA), PTB (Germany), and AIST (Japan) to ensure traceability to fundamental physical constants.

Calibration of measurement equipment represents a critical aspect of accurate carrier density determination. Hall effect measurement systems require regular calibration using reference samples to account for magnetic field non-uniformities and contact resistance effects. For capacitance-voltage profiling techniques, calibration involves verification of voltage source accuracy and capacitance meter linearity across the measurement range. Temperature control during calibration is particularly important, as carrier mobility and density exhibit strong temperature dependence.

Measurement uncertainty analysis constitutes an essential component of standardization protocols. This includes quantification of systematic errors from equipment limitations, random errors from environmental fluctuations, and sample-specific uncertainties. The Joint Committee for Guides in Metrology (JCGM) provides guidelines for uncertainty calculation that have been adapted specifically for semiconductor measurements by industry consortia like SEMI and IEEE.

Inter-laboratory comparison studies play a vital role in validating measurement protocols. These round-robin tests involve multiple facilities measuring identical samples and comparing results to identify systematic biases and establish measurement reproducibility limits. The International Technology Roadmap for Semiconductors (ITRS) has coordinated several such studies, establishing benchmark data for various measurement techniques.

Automation of calibration procedures has significantly improved measurement accuracy in recent years. Software-controlled calibration routines can compensate for drift in measurement parameters and apply correction factors in real-time. Machine learning algorithms are increasingly being deployed to recognize measurement artifacts and optimize calibration intervals based on equipment performance history.

Documentation and training standards ensure proper implementation of measurement protocols across the semiconductor industry. Detailed procedural documents with step-by-step instructions, acceptance criteria, and troubleshooting guides help maintain measurement consistency. Certification programs for measurement technicians further reinforce adherence to standardized practices and proper interpretation of results.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!