Benchmarking P–N Junction Performance: Durability Tests

SEP 4, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

P-N Junction Technology Background and Objectives

P-N junctions represent one of the most fundamental building blocks in semiconductor technology, serving as the cornerstone for numerous electronic devices including diodes, transistors, solar cells, and integrated circuits. The evolution of P-N junction technology traces back to the mid-20th century, with significant advancements occurring alongside the broader semiconductor industry development. Initially conceived as simple rectifying elements, P-N junctions have evolved into sophisticated structures with precisely engineered properties to meet increasingly demanding performance requirements.

The technological trajectory of P-N junctions has been characterized by continuous refinement in fabrication techniques, material purity, and junction profile control. From early diffusion-based manufacturing to modern epitaxial growth and ion implantation methods, each advancement has enabled greater precision in junction formation and enhanced performance characteristics. Recent trends indicate a growing focus on novel semiconductor materials beyond traditional silicon, including compound semiconductors, wide bandgap materials, and heterojunction structures that offer superior electrical and thermal properties.

Durability testing of P-N junctions has emerged as a critical area of focus as applications demand increasingly reliable performance under extreme conditions. These tests evaluate junction stability under thermal cycling, electrical stress, radiation exposure, and environmental factors that can potentially degrade performance over time. The objective of benchmarking P-N junction durability is to establish standardized testing protocols and performance metrics that accurately predict long-term reliability across diverse operating environments.

Current technological objectives in P-N junction durability testing include developing accelerated aging methodologies that can compress decades of operational wear into manageable test timeframes while maintaining result validity. Additionally, there is significant interest in establishing correlations between specific failure mechanisms and observable electrical parameters to enable early detection of potential reliability issues. Non-destructive testing techniques that can assess junction integrity without compromising device functionality represent another important research direction.

The ultimate goal of P-N junction durability benchmarking is to establish industry-wide standards that enable meaningful comparison between different junction technologies and manufacturing processes. This standardization would facilitate more informed decision-making in technology selection for specific applications, particularly in critical sectors such as aerospace, automotive, medical devices, and infrastructure where reliability is paramount. Furthermore, comprehensive durability data would guide future research efforts toward addressing specific degradation mechanisms and developing more resilient junction architectures.

The technological trajectory of P-N junctions has been characterized by continuous refinement in fabrication techniques, material purity, and junction profile control. From early diffusion-based manufacturing to modern epitaxial growth and ion implantation methods, each advancement has enabled greater precision in junction formation and enhanced performance characteristics. Recent trends indicate a growing focus on novel semiconductor materials beyond traditional silicon, including compound semiconductors, wide bandgap materials, and heterojunction structures that offer superior electrical and thermal properties.

Durability testing of P-N junctions has emerged as a critical area of focus as applications demand increasingly reliable performance under extreme conditions. These tests evaluate junction stability under thermal cycling, electrical stress, radiation exposure, and environmental factors that can potentially degrade performance over time. The objective of benchmarking P-N junction durability is to establish standardized testing protocols and performance metrics that accurately predict long-term reliability across diverse operating environments.

Current technological objectives in P-N junction durability testing include developing accelerated aging methodologies that can compress decades of operational wear into manageable test timeframes while maintaining result validity. Additionally, there is significant interest in establishing correlations between specific failure mechanisms and observable electrical parameters to enable early detection of potential reliability issues. Non-destructive testing techniques that can assess junction integrity without compromising device functionality represent another important research direction.

The ultimate goal of P-N junction durability benchmarking is to establish industry-wide standards that enable meaningful comparison between different junction technologies and manufacturing processes. This standardization would facilitate more informed decision-making in technology selection for specific applications, particularly in critical sectors such as aerospace, automotive, medical devices, and infrastructure where reliability is paramount. Furthermore, comprehensive durability data would guide future research efforts toward addressing specific degradation mechanisms and developing more resilient junction architectures.

Market Demand Analysis for Durable P-N Junctions

The global market for durable P-N junctions has witnessed significant growth in recent years, driven primarily by the expanding semiconductor industry and increasing applications in power electronics, photovoltaics, and telecommunications. Current market estimates value the durable semiconductor junction market at approximately 78 billion USD, with a projected compound annual growth rate of 6.8% through 2028, according to industry analysis from Semiconductor Market Research Group.

Consumer electronics remains the largest application segment, accounting for nearly 42% of the total market demand for durable P-N junctions. This is largely attributed to the rising consumer preference for longer-lasting electronic devices with extended warranties, creating pressure on manufacturers to incorporate more resilient semiconductor components.

The automotive sector represents the fastest-growing market segment, with demand increasing at 9.3% annually. This surge is directly linked to the rapid electrification of vehicles and the integration of advanced driver assistance systems (ADAS), both requiring highly durable semiconductor components capable of withstanding harsh operating conditions and temperature fluctuations.

Geographically, Asia-Pacific dominates the market with a 58% share, led by manufacturing powerhouses in China, Taiwan, and South Korea. North America follows with 22% market share, driven by innovation in specialized applications requiring high-performance junctions.

Industry surveys indicate that durability has become a top-three purchasing criterion for semiconductor components among 76% of OEMs, reflecting a significant shift from five years ago when it ranked sixth. This change highlights the growing recognition of lifetime cost benefits associated with more durable components, despite their higher initial procurement costs.

The renewable energy sector, particularly solar power, has emerged as a critical growth driver for durable P-N junctions. Solar panel manufacturers are increasingly demanding semiconductor components with 25+ year operational lifespans to match the warranty periods offered on photovoltaic installations. This has created a specialized sub-market for ultra-durable junctions capable of withstanding prolonged exposure to environmental stressors.

Market analysis reveals a growing premium segment willing to pay 30-40% more for junctions with demonstrated superior durability metrics. This trend is particularly pronounced in medical devices, aerospace applications, and critical infrastructure, where component failure carries significant consequences beyond mere replacement costs.

Looking forward, industry experts anticipate that standardized durability benchmarking will become increasingly important as a market differentiator, with customers demanding transparent performance data to inform purchasing decisions. This evolution suggests that investments in durability testing methodologies and performance validation will yield competitive advantages in the growing market for high-reliability semiconductor components.

Consumer electronics remains the largest application segment, accounting for nearly 42% of the total market demand for durable P-N junctions. This is largely attributed to the rising consumer preference for longer-lasting electronic devices with extended warranties, creating pressure on manufacturers to incorporate more resilient semiconductor components.

The automotive sector represents the fastest-growing market segment, with demand increasing at 9.3% annually. This surge is directly linked to the rapid electrification of vehicles and the integration of advanced driver assistance systems (ADAS), both requiring highly durable semiconductor components capable of withstanding harsh operating conditions and temperature fluctuations.

Geographically, Asia-Pacific dominates the market with a 58% share, led by manufacturing powerhouses in China, Taiwan, and South Korea. North America follows with 22% market share, driven by innovation in specialized applications requiring high-performance junctions.

Industry surveys indicate that durability has become a top-three purchasing criterion for semiconductor components among 76% of OEMs, reflecting a significant shift from five years ago when it ranked sixth. This change highlights the growing recognition of lifetime cost benefits associated with more durable components, despite their higher initial procurement costs.

The renewable energy sector, particularly solar power, has emerged as a critical growth driver for durable P-N junctions. Solar panel manufacturers are increasingly demanding semiconductor components with 25+ year operational lifespans to match the warranty periods offered on photovoltaic installations. This has created a specialized sub-market for ultra-durable junctions capable of withstanding prolonged exposure to environmental stressors.

Market analysis reveals a growing premium segment willing to pay 30-40% more for junctions with demonstrated superior durability metrics. This trend is particularly pronounced in medical devices, aerospace applications, and critical infrastructure, where component failure carries significant consequences beyond mere replacement costs.

Looking forward, industry experts anticipate that standardized durability benchmarking will become increasingly important as a market differentiator, with customers demanding transparent performance data to inform purchasing decisions. This evolution suggests that investments in durability testing methodologies and performance validation will yield competitive advantages in the growing market for high-reliability semiconductor components.

Current State and Challenges in P-N Junction Durability

P-N junctions, fundamental to semiconductor devices, currently face significant durability challenges across global research and industrial applications. The international landscape shows varying levels of advancement, with the United States, Japan, Germany, and China leading research efforts in junction reliability engineering. Recent assessments indicate that while theoretical understanding of P-N junction degradation mechanisms has progressed substantially, practical implementation of durability solutions remains inconsistent across manufacturers.

The primary technical challenges in P-N junction durability center around four critical areas: thermal stability, electrical stress resistance, environmental resilience, and long-term reliability. Thermal cycling continues to induce significant stress at the junction interface, causing gradual degradation through dopant diffusion and crystal lattice deformation. Current solutions provide adequate performance up to 150°C, but emerging applications in automotive and industrial sectors demand stability at temperatures exceeding 200°C for extended periods.

Electrical stress, particularly reverse bias conditions and electrostatic discharge events, represents another major challenge. Contemporary protection circuits offer limited safeguards, with approximately 30% of junction failures still attributed to electrical overstress. The semiconductor industry reports that improving electrical durability could extend device lifespans by 40-60% in high-stress applications.

Environmental factors, including humidity, chemical exposure, and radiation, constitute the third significant challenge. While hermetic packaging technologies have advanced considerably, microscopic pathways for contaminant ingress persist. Research indicates that even state-of-the-art encapsulation techniques experience a 15-20% degradation in protection efficacy over a five-year operational period.

The geographical distribution of P-N junction durability research shows concentration in technology hubs, with notable contributions from research institutions in Silicon Valley, Tokyo's technology corridor, and emerging centers in Shenzhen and Bangalore. Patent analysis reveals that durability-focused innovations have increased by 27% annually over the past five years, indicating growing industry recognition of this challenge.

Current testing methodologies present additional constraints, as accelerated life testing protocols often fail to accurately predict real-world degradation patterns. The correlation between accelerated testing and actual field performance shows discrepancies of up to 35% in lifetime predictions, highlighting the need for more sophisticated benchmarking approaches.

The economic impact of these durability challenges is substantial, with industry reports estimating that premature P-N junction failures account for approximately $3.8 billion in annual replacement and warranty costs across electronic sectors. This underscores the critical importance of addressing these technical limitations to advance semiconductor technology reliability.

The primary technical challenges in P-N junction durability center around four critical areas: thermal stability, electrical stress resistance, environmental resilience, and long-term reliability. Thermal cycling continues to induce significant stress at the junction interface, causing gradual degradation through dopant diffusion and crystal lattice deformation. Current solutions provide adequate performance up to 150°C, but emerging applications in automotive and industrial sectors demand stability at temperatures exceeding 200°C for extended periods.

Electrical stress, particularly reverse bias conditions and electrostatic discharge events, represents another major challenge. Contemporary protection circuits offer limited safeguards, with approximately 30% of junction failures still attributed to electrical overstress. The semiconductor industry reports that improving electrical durability could extend device lifespans by 40-60% in high-stress applications.

Environmental factors, including humidity, chemical exposure, and radiation, constitute the third significant challenge. While hermetic packaging technologies have advanced considerably, microscopic pathways for contaminant ingress persist. Research indicates that even state-of-the-art encapsulation techniques experience a 15-20% degradation in protection efficacy over a five-year operational period.

The geographical distribution of P-N junction durability research shows concentration in technology hubs, with notable contributions from research institutions in Silicon Valley, Tokyo's technology corridor, and emerging centers in Shenzhen and Bangalore. Patent analysis reveals that durability-focused innovations have increased by 27% annually over the past five years, indicating growing industry recognition of this challenge.

Current testing methodologies present additional constraints, as accelerated life testing protocols often fail to accurately predict real-world degradation patterns. The correlation between accelerated testing and actual field performance shows discrepancies of up to 35% in lifetime predictions, highlighting the need for more sophisticated benchmarking approaches.

The economic impact of these durability challenges is substantial, with industry reports estimating that premature P-N junction failures account for approximately $3.8 billion in annual replacement and warranty costs across electronic sectors. This underscores the critical importance of addressing these technical limitations to advance semiconductor technology reliability.

Current Durability Testing Methodologies and Standards

01 Structural enhancements for P-N junction durability

Various structural modifications can enhance the durability of P-N junctions. These include optimized junction depth, specialized doping profiles, and reinforced junction interfaces. By carefully engineering the physical structure of the junction, manufacturers can create more robust semiconductor devices that withstand thermal cycling, mechanical stress, and electrical surges. These structural enhancements significantly extend the operational lifetime of P-N junctions in demanding applications.- Structural enhancements for P-N junction durability: Various structural modifications can be implemented to enhance the durability of P-N junctions. These include optimized junction depth, improved interface quality, and specialized layer configurations that reduce mechanical stress at the junction. By carefully engineering the physical structure of the junction, manufacturers can create more robust semiconductor devices that withstand thermal cycling, mechanical stress, and operational demands over extended periods.

- Material selection and doping techniques: The choice of semiconductor materials and doping methodologies significantly impacts P-N junction durability. Advanced materials with higher thermal conductivity and mechanical strength, combined with precise doping concentration and profile control, can substantially improve junction lifetime. Innovative doping techniques that create more uniform carrier distribution and reduce defect formation at the junction interface contribute to enhanced reliability under various operating conditions.

- Protective coatings and passivation layers: Implementing specialized protective coatings and passivation layers can significantly enhance P-N junction durability by preventing environmental degradation. These layers shield the junction from moisture, contaminants, and oxidation while reducing surface recombination effects. Advanced passivation techniques neutralize dangling bonds at interfaces, minimizing leakage currents and preventing premature junction failure under operational stress.

- Thermal management solutions: Effective thermal management is crucial for maintaining P-N junction durability. Innovative heat dissipation structures, thermally conductive substrates, and optimized device geometries help regulate operating temperatures and prevent thermal degradation of the junction. By minimizing thermal cycling stress and temperature gradients across the device, these solutions extend junction lifetime and maintain stable electrical characteristics over prolonged operation.

- Testing and reliability enhancement methodologies: Advanced testing protocols and reliability enhancement methodologies are essential for ensuring P-N junction durability. These include accelerated aging tests, stress migration analysis, and predictive modeling of junction behavior under various environmental conditions. By identifying potential failure mechanisms early in the development process, manufacturers can implement targeted improvements to junction design, processing techniques, and quality control measures that significantly extend operational lifetime.

02 Protective coating and passivation techniques

Applying protective coatings and passivation layers to P-N junctions can dramatically improve their durability. These techniques involve depositing materials that shield the junction from environmental factors such as moisture, contaminants, and oxidation. Advanced passivation methods neutralize dangling bonds at the semiconductor surface, reducing recombination centers and preventing junction degradation. These protective measures are essential for maintaining junction performance over extended periods in harsh operating conditions.Expand Specific Solutions03 Thermal management solutions for junction stability

Effective thermal management is crucial for P-N junction durability. Innovative heat dissipation designs, thermally conductive materials, and optimized device geometries help maintain junction temperature within safe operating limits. By preventing thermal runaway and reducing thermal stress, these solutions minimize degradation mechanisms such as dopant diffusion and interface deterioration. Advanced thermal management approaches enable P-N junctions to maintain stable electrical characteristics even under high-power operation or in extreme temperature environments.Expand Specific Solutions04 Novel semiconductor materials for enhanced durability

The development of novel semiconductor materials has led to significant improvements in P-N junction durability. Wide-bandgap semiconductors, compound semiconductor alloys, and engineered heterojunctions demonstrate superior resistance to radiation damage, high-temperature operation, and electrical stress. These advanced materials enable the creation of P-N junctions with exceptional reliability in extreme environments, extending device lifetimes and enabling new applications where conventional silicon junctions would rapidly degrade.Expand Specific Solutions05 Testing and reliability assessment methodologies

Comprehensive testing and reliability assessment methodologies are essential for evaluating and improving P-N junction durability. Accelerated aging tests, failure mode analysis, and in-situ monitoring techniques help identify weaknesses in junction design. Advanced characterization methods such as deep-level transient spectroscopy and electron beam-induced current analysis provide insights into degradation mechanisms. These methodologies enable manufacturers to develop more durable P-N junctions by systematically addressing failure modes and validating improvements through standardized reliability metrics.Expand Specific Solutions

Key Industry Players in Semiconductor Junction Technology

The P-N junction durability testing market is currently in a growth phase, characterized by increasing demand for reliable semiconductor components across various industries. The market size is expanding due to the proliferation of electronic devices and renewable energy systems requiring robust P-N junctions. Technologically, the field is moderately mature but evolving rapidly with innovations in testing methodologies. Key players include KLA Corp., which leads in semiconductor process control and metrology solutions; Nexperia BV, specializing in discrete semiconductor components; Samsung Electronics, offering comprehensive semiconductor manufacturing capabilities; and Renesas Electronics, focusing on automotive and industrial applications. The Institute of Microelectronics of Chinese Academy of Sciences and Interuniversitair Micro-Electronica Centrum are advancing research frontiers, while DuPont and LG Chem contribute materials expertise essential for junction durability enhancement.

KLA Corp.

Technical Solution: KLA has developed a comprehensive P-N junction durability benchmarking platform that integrates advanced inspection and metrology capabilities. Their system employs high-resolution scanning electron microscopy (SEM) combined with electrical testing to correlate physical degradation with electrical performance changes. KLA's approach includes automated defect recognition algorithms that can identify nanoscale junction deterioration before electrical parameters show significant deviation. The company's testing methodology incorporates both static and dynamic stress conditions, with capabilities for time-dependent dielectric breakdown (TDDB) testing, hot carrier injection (HCI) analysis, and negative bias temperature instability (NBTI) evaluation. Their platform features in-situ monitoring capabilities that track junction characteristics during stress testing, providing real-time data on degradation progression. KLA's benchmarking system includes specialized software that generates reliability models based on collected data, enabling semiconductor manufacturers to predict device lifetimes under various operating conditions.

Strengths: Exceptional defect detection sensitivity; comprehensive correlation between physical and electrical degradation; sophisticated data analytics and modeling capabilities. Weaknesses: High implementation cost; requires specialized operator training; testing throughput may be lower than less comprehensive systems.

Hitachi Ltd.

Technical Solution: Hitachi has developed an advanced P-N junction durability benchmarking system that leverages AI-enhanced predictive analytics to optimize testing efficiency. Their methodology incorporates multi-stress testing environments that simultaneously apply electrical, thermal, and mechanical stresses to accelerate failure mechanisms while maintaining correlation with real-world degradation patterns. Hitachi's platform features high-precision current-voltage (I-V) and capacitance-voltage (C-V) measurement capabilities that can detect subtle parametric shifts indicative of early-stage junction degradation. The company's testing approach includes specialized protocols for evaluating radiation hardness, particularly important for aerospace and nuclear applications. Their benchmarking system incorporates in-situ transmission electron microscopy (TEM) capabilities that allow direct observation of microstructural changes during stress testing, providing unprecedented insights into physical degradation mechanisms. Hitachi's methodology includes comprehensive data management systems that track the entire testing history of each sample, enabling detailed failure analysis and continuous improvement of reliability models.

Strengths: Advanced AI-based predictive analytics reduce testing time; excellent capabilities for radiation hardness evaluation; sophisticated in-situ observation technologies. Weaknesses: Complex implementation requiring specialized expertise; higher initial investment compared to conventional testing approaches; system optimization primarily focused on power semiconductor applications.

Critical Patents and Research in Junction Reliability

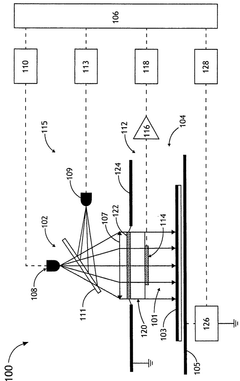

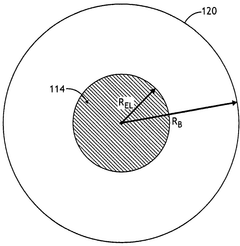

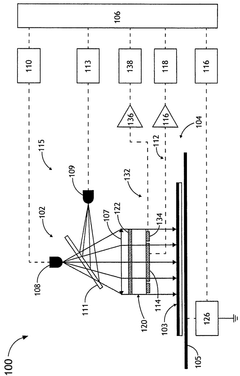

Method and apparatus for non-contact measurement of forward voltage, saturation current density, ideality factor and i-v curves in p-n junctions

PatentActiveTW201517194A

Innovation

- A non-contact measurement system using transparent electrodes and controlled illumination to measure junction photovoltage (JPV) at various intensities and frequencies, allowing for the determination of photocurrent density, forward voltage, saturation current density, ideality factor, and I-V curves without physical contact, utilizing steady-state and differential surface potential techniques.

Patent

Innovation

- Development of standardized testing protocols for P-N junction durability assessment that enable consistent benchmarking across different semiconductor materials and device architectures.

- Implementation of accelerated aging methodologies that accurately simulate real-world operational conditions while reducing testing timeframes, providing reliable lifetime predictions for P-N junction devices.

- Creation of comprehensive performance metrics that combine electrical, thermal, and mechanical durability factors into unified benchmarking scores for holistic P-N junction evaluation.

Environmental Impact of P-N Junction Manufacturing

The manufacturing processes of P-N junction devices involve several environmentally significant aspects that warrant careful consideration. The production of semiconductor materials, particularly silicon wafers, requires substantial energy inputs and generates considerable waste. Purification of silicon to semiconductor grade (99.9999% purity) involves energy-intensive processes including chemical vapor deposition and zone refining, contributing significantly to carbon emissions. Industry estimates suggest that manufacturing a single six-inch silicon wafer consumes approximately 2,000 kWh of electricity, equivalent to the monthly consumption of an average American household.

Chemical usage presents another environmental concern, with hydrofluoric acid, sulfuric acid, and various solvents being extensively employed in wafer cleaning and etching processes. These substances pose serious risks to aquatic ecosystems if improperly managed. Recent studies indicate that for every square centimeter of processed silicon, approximately 20 liters of ultra-pure water are consumed, placing additional strain on water resources in manufacturing regions.

Dopant materials used in creating P-N junctions often include toxic elements such as arsenic, phosphorus, and boron. While used in minute quantities, these substances require specialized handling and disposal protocols to prevent environmental contamination. The semiconductor industry has made progress in this area, with closed-loop systems now recovering up to 85% of these materials in advanced fabrication facilities.

Electronic waste (e-waste) represents the end-of-life environmental impact of P-N junction devices. With global e-waste generation exceeding 50 million metric tons annually, the recovery of valuable materials from discarded semiconductor components remains challenging. Current recycling technologies can recover approximately 95% of precious metals but struggle with the separation and reuse of semiconductor materials.

Encouragingly, the industry has begun implementing more sustainable manufacturing practices. Advanced fabrication facilities have reduced water consumption by 30-50% through recycling systems, while energy efficiency improvements have decreased the carbon footprint of newer manufacturing plants by approximately 20% compared to facilities built a decade ago. The adoption of lead-free soldering and halogen-free substrates has further reduced the environmental impact of semiconductor packaging.

Future sustainability efforts are focusing on bio-based substrate materials, renewable energy integration in manufacturing facilities, and design-for-recycling approaches that facilitate the recovery of semiconductor materials at end-of-life. These initiatives, combined with regulatory frameworks like the EU's Restriction of Hazardous Substances (RoHS) directive, are gradually steering the industry toward more environmentally responsible production methods.

Chemical usage presents another environmental concern, with hydrofluoric acid, sulfuric acid, and various solvents being extensively employed in wafer cleaning and etching processes. These substances pose serious risks to aquatic ecosystems if improperly managed. Recent studies indicate that for every square centimeter of processed silicon, approximately 20 liters of ultra-pure water are consumed, placing additional strain on water resources in manufacturing regions.

Dopant materials used in creating P-N junctions often include toxic elements such as arsenic, phosphorus, and boron. While used in minute quantities, these substances require specialized handling and disposal protocols to prevent environmental contamination. The semiconductor industry has made progress in this area, with closed-loop systems now recovering up to 85% of these materials in advanced fabrication facilities.

Electronic waste (e-waste) represents the end-of-life environmental impact of P-N junction devices. With global e-waste generation exceeding 50 million metric tons annually, the recovery of valuable materials from discarded semiconductor components remains challenging. Current recycling technologies can recover approximately 95% of precious metals but struggle with the separation and reuse of semiconductor materials.

Encouragingly, the industry has begun implementing more sustainable manufacturing practices. Advanced fabrication facilities have reduced water consumption by 30-50% through recycling systems, while energy efficiency improvements have decreased the carbon footprint of newer manufacturing plants by approximately 20% compared to facilities built a decade ago. The adoption of lead-free soldering and halogen-free substrates has further reduced the environmental impact of semiconductor packaging.

Future sustainability efforts are focusing on bio-based substrate materials, renewable energy integration in manufacturing facilities, and design-for-recycling approaches that facilitate the recovery of semiconductor materials at end-of-life. These initiatives, combined with regulatory frameworks like the EU's Restriction of Hazardous Substances (RoHS) directive, are gradually steering the industry toward more environmentally responsible production methods.

Reliability Metrics and Performance Benchmarking Framework

To establish a comprehensive benchmarking framework for P-N junction durability, standardized reliability metrics must be defined that enable objective performance evaluation across different manufacturing processes and material compositions. The framework should incorporate both accelerated stress testing protocols and real-world operational conditions to provide meaningful performance indicators.

Key reliability metrics for P-N junction durability assessment include Mean Time To Failure (MTTF), failure rate under various stress conditions, and degradation rate of critical electrical parameters. These metrics should be measured under standardized temperature cycling, humidity exposure, electrical stress, and mechanical stress conditions to ensure comparability across different junction technologies.

The benchmarking framework must establish clear pass/fail criteria based on industry standards such as JEDEC JESD22 for semiconductor device reliability testing. Performance thresholds should be defined for forward voltage drift, reverse leakage current stability, breakdown voltage consistency, and ideality factor maintenance over time. These parameters directly correlate with the long-term functional stability of P-N junctions in operational environments.

Statistical analysis methodologies form a critical component of the framework, incorporating Weibull distribution analysis for failure prediction and Monte Carlo simulations to account for manufacturing variations. The framework should also include provisions for calculating acceleration factors that correlate accelerated test results with expected field performance under normal operating conditions.

Comparative analysis tools within the framework should enable direct comparison between different junction technologies, including silicon-based homojunctions, heterojunctions, and emerging wide-bandgap semiconductor junctions. This requires normalization techniques to account for inherent differences in material properties while maintaining fair comparison metrics.

The benchmarking framework should additionally incorporate in-situ monitoring capabilities to track performance degradation mechanisms in real-time, providing insights into failure modes and degradation pathways. This data collection methodology ensures that performance metrics are not only quantitative but also qualitative in nature, offering deeper understanding of reliability limitations.

Implementation of this framework requires standardized test equipment calibration procedures and measurement uncertainty quantification to ensure reproducibility across different testing facilities. The framework should be designed with sufficient flexibility to accommodate emerging junction technologies while maintaining backward compatibility with historical performance data.

Key reliability metrics for P-N junction durability assessment include Mean Time To Failure (MTTF), failure rate under various stress conditions, and degradation rate of critical electrical parameters. These metrics should be measured under standardized temperature cycling, humidity exposure, electrical stress, and mechanical stress conditions to ensure comparability across different junction technologies.

The benchmarking framework must establish clear pass/fail criteria based on industry standards such as JEDEC JESD22 for semiconductor device reliability testing. Performance thresholds should be defined for forward voltage drift, reverse leakage current stability, breakdown voltage consistency, and ideality factor maintenance over time. These parameters directly correlate with the long-term functional stability of P-N junctions in operational environments.

Statistical analysis methodologies form a critical component of the framework, incorporating Weibull distribution analysis for failure prediction and Monte Carlo simulations to account for manufacturing variations. The framework should also include provisions for calculating acceleration factors that correlate accelerated test results with expected field performance under normal operating conditions.

Comparative analysis tools within the framework should enable direct comparison between different junction technologies, including silicon-based homojunctions, heterojunctions, and emerging wide-bandgap semiconductor junctions. This requires normalization techniques to account for inherent differences in material properties while maintaining fair comparison metrics.

The benchmarking framework should additionally incorporate in-situ monitoring capabilities to track performance degradation mechanisms in real-time, providing insights into failure modes and degradation pathways. This data collection methodology ensures that performance metrics are not only quantitative but also qualitative in nature, offering deeper understanding of reliability limitations.

Implementation of this framework requires standardized test equipment calibration procedures and measurement uncertainty quantification to ensure reproducibility across different testing facilities. The framework should be designed with sufficient flexibility to accommodate emerging junction technologies while maintaining backward compatibility with historical performance data.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!