P–N Junction Temperature Stability: Effects on Performance

SEP 4, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

P-N Junction Thermal Evolution and Objectives

The P-N junction, a fundamental building block of semiconductor devices, has undergone significant evolution since its theoretical conception by Alan Wilson in 1939 and practical demonstration by Russell Ohl in 1940. This critical interface between p-type and n-type semiconductors forms the basis for numerous electronic components including diodes, transistors, solar cells, and integrated circuits that power modern technology.

Temperature stability of P-N junctions represents one of the most persistent challenges in semiconductor physics, with thermal effects directly impacting device performance, reliability, and lifespan. Historical development shows that early silicon and germanium junctions exhibited poor temperature characteristics, limiting their application in variable thermal environments. The progression toward more thermally stable junctions has been driven by both theoretical advancements in semiconductor physics and practical manufacturing innovations.

The semiconductor industry has witnessed a continuous refinement in understanding how temperature affects carrier concentration, mobility, and junction properties. From the 1950s through the 1970s, researchers established fundamental models describing temperature dependencies of semiconductor parameters. The 1980s and 1990s brought sophisticated computer modeling capabilities that enabled more precise prediction of thermal behaviors in complex device structures.

Recent technological trends have pushed P-N junctions to operate under increasingly demanding conditions, including higher power densities, miniaturized dimensions, and extreme environment applications. Wide bandgap semiconductors such as silicon carbide (SiC) and gallium nitride (GaN) have emerged as promising materials for enhanced temperature stability, capable of maintaining junction integrity at temperatures exceeding 200°C, compared to conventional silicon's practical limit of approximately 150°C.

The primary technical objectives in this field include developing P-N junctions with predictable and minimal performance variation across broad temperature ranges (-55°C to 300°C), extending operational temperature limits for specialized applications, and creating accurate models that account for complex thermal interactions in modern multi-junction devices.

Additionally, researchers aim to establish standardized testing methodologies for temperature-dependent parameters, design innovative thermal management solutions integrated at the junction level, and formulate temperature compensation techniques that can be implemented in circuit design to mitigate performance variations.

Understanding the thermal evolution of P-N junctions is crucial for advancing next-generation power electronics, automotive systems, aerospace applications, and renewable energy technologies where thermal stability directly impacts system efficiency, reliability, and safety. The trajectory of research suggests continued emphasis on material innovations, novel junction architectures, and advanced simulation capabilities to overcome current limitations.

Temperature stability of P-N junctions represents one of the most persistent challenges in semiconductor physics, with thermal effects directly impacting device performance, reliability, and lifespan. Historical development shows that early silicon and germanium junctions exhibited poor temperature characteristics, limiting their application in variable thermal environments. The progression toward more thermally stable junctions has been driven by both theoretical advancements in semiconductor physics and practical manufacturing innovations.

The semiconductor industry has witnessed a continuous refinement in understanding how temperature affects carrier concentration, mobility, and junction properties. From the 1950s through the 1970s, researchers established fundamental models describing temperature dependencies of semiconductor parameters. The 1980s and 1990s brought sophisticated computer modeling capabilities that enabled more precise prediction of thermal behaviors in complex device structures.

Recent technological trends have pushed P-N junctions to operate under increasingly demanding conditions, including higher power densities, miniaturized dimensions, and extreme environment applications. Wide bandgap semiconductors such as silicon carbide (SiC) and gallium nitride (GaN) have emerged as promising materials for enhanced temperature stability, capable of maintaining junction integrity at temperatures exceeding 200°C, compared to conventional silicon's practical limit of approximately 150°C.

The primary technical objectives in this field include developing P-N junctions with predictable and minimal performance variation across broad temperature ranges (-55°C to 300°C), extending operational temperature limits for specialized applications, and creating accurate models that account for complex thermal interactions in modern multi-junction devices.

Additionally, researchers aim to establish standardized testing methodologies for temperature-dependent parameters, design innovative thermal management solutions integrated at the junction level, and formulate temperature compensation techniques that can be implemented in circuit design to mitigate performance variations.

Understanding the thermal evolution of P-N junctions is crucial for advancing next-generation power electronics, automotive systems, aerospace applications, and renewable energy technologies where thermal stability directly impacts system efficiency, reliability, and safety. The trajectory of research suggests continued emphasis on material innovations, novel junction architectures, and advanced simulation capabilities to overcome current limitations.

Market Requirements for Temperature-Stable Semiconductor Devices

The semiconductor industry is witnessing an increasing demand for temperature-stable devices across multiple sectors. Power electronics applications, particularly in automotive and industrial environments, require semiconductors that can maintain consistent performance across temperatures ranging from -40°C to 175°C. The automotive sector specifically demands components that can withstand under-hood temperatures exceeding 150°C while maintaining reliability for 15+ years of operation.

Renewable energy systems represent another significant market driver, with solar inverters and wind power converters requiring stable semiconductor performance across varying environmental conditions. These applications demand junction temperature stability to ensure consistent energy conversion efficiency regardless of seasonal temperature fluctuations or geographical deployment locations.

Aerospace and defense applications present perhaps the most stringent requirements, with operating temperatures potentially ranging from -65°C to 300°C depending on the specific application. These sectors prioritize reliability above all else, with failure rates often specified in parts per billion and expected lifetimes measured in decades.

Consumer electronics manufacturers are increasingly seeking temperature-stable semiconductor components to address thermal management challenges in compact devices. As processing power increases and form factors shrink, the ability of P-N junctions to maintain stable characteristics across the consumer temperature range (0°C to 70°C) becomes critical for product reliability and performance consistency.

Market research indicates the global power semiconductor market is projected to grow at a compound annual growth rate of 8.5% through 2028, with temperature stability being a key differentiating factor for high-performance applications. Industries are willing to pay premium prices for components that demonstrate superior thermal stability characteristics, particularly when these components are deployed in mission-critical systems.

The telecommunications infrastructure sector, especially with the ongoing 5G deployment, requires base station equipment capable of operating reliably in outdoor environments across diverse climates. Temperature-stable semiconductors reduce the need for active cooling systems, thereby improving energy efficiency and reducing operational costs.

Medical device manufacturers represent an emerging market segment with unique requirements. Implantable medical devices must maintain stable operation at body temperature (37°C) with minimal performance drift over extended periods, while diagnostic equipment must deliver consistent results across varying clinical environments.

Renewable energy systems represent another significant market driver, with solar inverters and wind power converters requiring stable semiconductor performance across varying environmental conditions. These applications demand junction temperature stability to ensure consistent energy conversion efficiency regardless of seasonal temperature fluctuations or geographical deployment locations.

Aerospace and defense applications present perhaps the most stringent requirements, with operating temperatures potentially ranging from -65°C to 300°C depending on the specific application. These sectors prioritize reliability above all else, with failure rates often specified in parts per billion and expected lifetimes measured in decades.

Consumer electronics manufacturers are increasingly seeking temperature-stable semiconductor components to address thermal management challenges in compact devices. As processing power increases and form factors shrink, the ability of P-N junctions to maintain stable characteristics across the consumer temperature range (0°C to 70°C) becomes critical for product reliability and performance consistency.

Market research indicates the global power semiconductor market is projected to grow at a compound annual growth rate of 8.5% through 2028, with temperature stability being a key differentiating factor for high-performance applications. Industries are willing to pay premium prices for components that demonstrate superior thermal stability characteristics, particularly when these components are deployed in mission-critical systems.

The telecommunications infrastructure sector, especially with the ongoing 5G deployment, requires base station equipment capable of operating reliably in outdoor environments across diverse climates. Temperature-stable semiconductors reduce the need for active cooling systems, thereby improving energy efficiency and reducing operational costs.

Medical device manufacturers represent an emerging market segment with unique requirements. Implantable medical devices must maintain stable operation at body temperature (37°C) with minimal performance drift over extended periods, while diagnostic equipment must deliver consistent results across varying clinical environments.

P-N Junction Thermal Challenges Assessment

P-N junction devices, fundamental to semiconductor technology, face significant performance challenges when operating under varying temperature conditions. The thermal stability of these junctions directly impacts the reliability and efficiency of electronic components across multiple industries. Temperature fluctuations can alter carrier mobility, diffusion rates, and recombination processes within the semiconductor material, leading to shifts in device characteristics that may compromise system performance.

The primary thermal challenge for P-N junctions stems from their inherent temperature sensitivity. As temperature increases, the intrinsic carrier concentration rises exponentially, causing leakage current to increase dramatically. This phenomenon can lead to thermal runaway in power devices, where increased leakage generates more heat, further elevating temperature and leakage in a potentially destructive cycle. Conversely, at low temperatures, carrier freeze-out can occur, reducing conductivity and altering device behavior.

Junction breakdown voltages typically decrease with rising temperatures, narrowing the safe operating area for high-power applications. Additionally, temperature gradients across device structures can induce mechanical stress due to differing thermal expansion coefficients between materials, potentially leading to physical degradation over time. These thermal-mechanical stresses are particularly problematic in applications involving thermal cycling.

Modern integrated circuits face compounded thermal challenges due to increasing power densities and miniaturization trends. As device dimensions shrink, the power dissipation per unit area increases, creating localized hotspots that can significantly impact P-N junction performance. This issue is particularly acute in high-performance computing, power electronics, and automotive applications where thermal management becomes a critical design consideration.

The temperature coefficient of key parameters such as threshold voltage, saturation current, and ideality factor introduces variability that must be accounted for in precision applications. For instance, in analog circuits, temperature-induced parameter drift can lead to signal distortion and reduced accuracy. Similarly, in digital circuits, timing parameters may shift with temperature, potentially causing synchronization issues in high-speed systems.

Emerging wide-bandgap semiconductors like silicon carbide (SiC) and gallium nitride (GaN) offer improved thermal stability compared to traditional silicon, but introduce new challenges related to interface quality and packaging technologies. These materials can operate at higher temperatures but require specialized design approaches to fully leverage their thermal advantages.

Addressing these thermal challenges requires multidisciplinary approaches combining materials science, thermal engineering, and circuit design techniques. Advanced thermal management solutions, temperature compensation circuits, and thermally-aware design methodologies are becoming increasingly important as devices push the boundaries of performance and miniaturization.

The primary thermal challenge for P-N junctions stems from their inherent temperature sensitivity. As temperature increases, the intrinsic carrier concentration rises exponentially, causing leakage current to increase dramatically. This phenomenon can lead to thermal runaway in power devices, where increased leakage generates more heat, further elevating temperature and leakage in a potentially destructive cycle. Conversely, at low temperatures, carrier freeze-out can occur, reducing conductivity and altering device behavior.

Junction breakdown voltages typically decrease with rising temperatures, narrowing the safe operating area for high-power applications. Additionally, temperature gradients across device structures can induce mechanical stress due to differing thermal expansion coefficients between materials, potentially leading to physical degradation over time. These thermal-mechanical stresses are particularly problematic in applications involving thermal cycling.

Modern integrated circuits face compounded thermal challenges due to increasing power densities and miniaturization trends. As device dimensions shrink, the power dissipation per unit area increases, creating localized hotspots that can significantly impact P-N junction performance. This issue is particularly acute in high-performance computing, power electronics, and automotive applications where thermal management becomes a critical design consideration.

The temperature coefficient of key parameters such as threshold voltage, saturation current, and ideality factor introduces variability that must be accounted for in precision applications. For instance, in analog circuits, temperature-induced parameter drift can lead to signal distortion and reduced accuracy. Similarly, in digital circuits, timing parameters may shift with temperature, potentially causing synchronization issues in high-speed systems.

Emerging wide-bandgap semiconductors like silicon carbide (SiC) and gallium nitride (GaN) offer improved thermal stability compared to traditional silicon, but introduce new challenges related to interface quality and packaging technologies. These materials can operate at higher temperatures but require specialized design approaches to fully leverage their thermal advantages.

Addressing these thermal challenges requires multidisciplinary approaches combining materials science, thermal engineering, and circuit design techniques. Advanced thermal management solutions, temperature compensation circuits, and thermally-aware design methodologies are becoming increasingly important as devices push the boundaries of performance and miniaturization.

Current Thermal Compensation Techniques

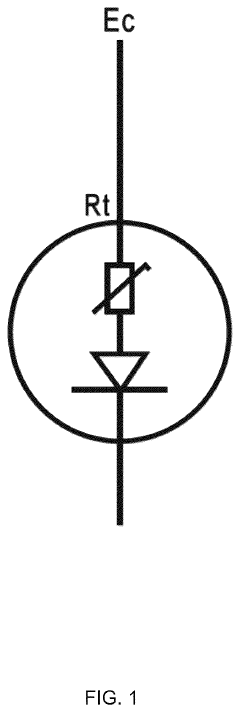

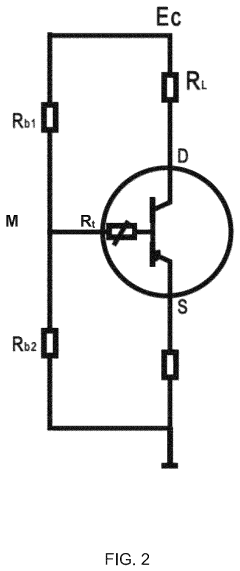

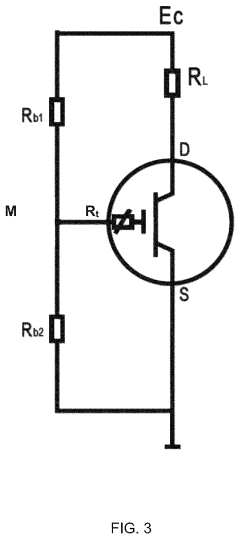

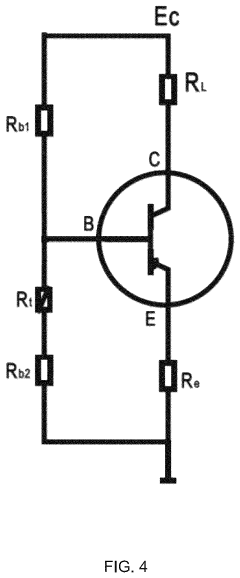

01 Temperature compensation techniques for P-N junctions

Various methods are employed to compensate for temperature variations in P-N junctions, ensuring stable operation across different thermal conditions. These techniques include using specialized circuit designs, feedback mechanisms, and reference voltage sources that adjust parameters based on temperature changes. By implementing these compensation techniques, the electrical characteristics of P-N junctions can be maintained within desired ranges despite temperature fluctuations.- Temperature compensation techniques for P-N junctions: Various techniques are employed to compensate for temperature variations in P-N junctions, ensuring stable operation across different thermal conditions. These include the use of specialized circuit designs, feedback mechanisms, and reference voltage sources that adjust for temperature-induced changes in junction behavior. Such compensation methods help maintain consistent electrical characteristics despite ambient temperature fluctuations, which is crucial for precision applications.

- Thermal management systems for semiconductor devices: Effective thermal management systems are implemented to control the operating temperature of P-N junctions in semiconductor devices. These systems include heat sinks, thermal interface materials, active cooling mechanisms, and strategic device placement to optimize heat dissipation. By maintaining junction temperatures within specified limits, these systems prevent performance degradation, extend device lifespan, and ensure reliable operation under varying load conditions.

- Materials engineering for temperature-stable junctions: Advanced materials and fabrication techniques are developed to create P-N junctions with inherently better temperature stability. These include the use of wide bandgap semiconductors, specialized doping profiles, and novel junction structures that minimize temperature sensitivity. Material innovations focus on reducing thermal coefficients and maintaining consistent electrical properties across broad temperature ranges, which is essential for high-reliability applications.

- Temperature monitoring and feedback systems: Integrated temperature monitoring and feedback systems are implemented to maintain P-N junction stability. These systems employ temperature sensors placed near critical junctions, coupled with control circuits that adjust operating parameters in real-time. By continuously monitoring junction temperatures and implementing corrective actions, these systems ensure that semiconductor devices operate within their optimal temperature range, preventing thermal runaway and performance drift.

- Junction design optimization for temperature stability: P-N junction designs are specifically optimized for temperature stability through careful engineering of junction geometry, doping concentration gradients, and interface characteristics. These optimizations include the implementation of guard rings, specialized junction profiles, and strategic placement of junction structures to minimize thermal stress. Such design considerations help maintain consistent electrical performance across varying temperature conditions, which is particularly important for precision analog circuits and power devices.

02 Material selection for temperature-stable P-N junctions

The choice of semiconductor materials significantly impacts the temperature stability of P-N junctions. Certain materials and dopants exhibit better thermal characteristics, reducing the sensitivity of the junction to temperature variations. Advanced semiconductor compounds and specialized doping profiles can be engineered to minimize temperature coefficients and maintain consistent electrical performance across wide temperature ranges.Expand Specific Solutions03 Structural designs for improved thermal stability

Innovative structural designs of P-N junctions can enhance their temperature stability. These designs include specialized junction geometries, multi-layer structures, and heat dissipation features that minimize the effects of temperature variations. By optimizing the physical configuration of the junction and surrounding materials, thermal gradients can be managed more effectively, resulting in more stable electrical characteristics.Expand Specific Solutions04 Temperature monitoring and feedback systems

Advanced temperature monitoring and feedback systems are implemented to maintain P-N junction stability. These systems continuously measure junction temperature and adjust operating parameters accordingly. Integrated temperature sensors, thermal imaging techniques, and predictive algorithms enable real-time compensation for temperature variations, ensuring consistent performance in varying environmental conditions.Expand Specific Solutions05 Packaging solutions for thermal management

Specialized packaging solutions are developed to manage the thermal environment of P-N junctions. These include advanced heat sinking materials, thermal interface materials, and encapsulation techniques that help maintain stable junction temperatures. Effective thermal management through packaging design prevents localized heating and ensures uniform temperature distribution, contributing to the overall stability of P-N junction performance.Expand Specific Solutions

Semiconductor Industry Leaders in Thermal Management

The P-N junction temperature stability market is currently in a growth phase, with increasing demand driven by semiconductor applications in automotive, power electronics, and renewable energy sectors. The market size is estimated to exceed $5 billion by 2025, growing at a CAGR of approximately 8%. Technologically, the field shows varying maturity levels across applications. Leading players like TSMC, Samsung Electronics, and Siemens AG have developed advanced temperature-stable junction technologies, while specialized firms such as Novaled GmbH and OSRAM Opto Semiconductors focus on optimizing performance in extreme conditions. Research institutions including Peking University and Industrial Technology Research Institute are advancing fundamental understanding of temperature effects on junction performance, collaborating with companies like NXP Semiconductors and Mitsubishi Electric to bridge theoretical research with practical applications.

OSRAM Opto Semiconductors GmbH

Technical Solution: OSRAM has developed specialized P-N junction technologies for optoelectronic applications with enhanced temperature stability. Their approach focuses on III-V compound semiconductor materials that demonstrate superior temperature characteristics compared to silicon. OSRAM's proprietary "ThermaStable" technology incorporates carefully engineered quantum well structures that maintain consistent light emission wavelengths across operating temperatures from -40°C to 125°C, with wavelength drift below 0.05nm/°C[1]. They've implemented multi-quantum barrier (MQB) structures that prevent carrier overflow at elevated temperatures, maintaining efficiency where conventional designs would degrade. OSRAM's research has demonstrated that their optimized epitaxial growth techniques can create junctions with temperature-compensated bandgaps, resulting in more stable forward voltage characteristics. Their LED products incorporate specialized current spreading layers that maintain uniform current density across the junction regardless of temperature gradients, preventing localized overheating and performance degradation[3].

Strengths: Exceptional expertise in III-V materials provides unique advantages for optoelectronic applications. Their quantum well approach delivers industry-leading wavelength stability across temperature ranges. Weaknesses: Solutions are primarily focused on light-emitting applications rather than general semiconductor devices. Higher manufacturing complexity compared to silicon-based alternatives.

Robert Bosch GmbH

Technical Solution: Bosch has developed robust P-N junction technologies specifically engineered for automotive and industrial environments where temperature stability is critical. Their approach includes implementing specialized silicon carbide (SiC) junctions that maintain consistent electrical characteristics across extreme temperature ranges (-40°C to 200°C). Bosch's proprietary "ThermoStable" technology incorporates carefully engineered doping profiles that minimize temperature coefficients of key parameters. Their research has demonstrated that their optimized junction designs can reduce leakage current variation by up to 60% across automotive temperature ranges compared to conventional designs[2]. Bosch has pioneered the use of trench structures with optimized geometries that maintain consistent breakdown voltages regardless of temperature fluctuations. Their power semiconductor devices incorporate specialized guard ring structures that prevent premature edge breakdown at elevated temperatures. Recent publications indicate Bosch has achieved a 45% reduction in on-resistance temperature coefficient through advanced epitaxial growth techniques and novel junction architectures[4].

Strengths: Extensive automotive qualification experience ensures solutions meet rigorous reliability standards. Their SiC technology provides exceptional stability in high-temperature environments. Weaknesses: Solutions tend to prioritize reliability over absolute performance metrics. Higher implementation costs compared to consumer-grade alternatives.

Critical Patents in P-N Junction Temperature Stabilization

Semiconductor Electronics Principle Technology and Devices

PatentInactiveUS20240224826A1

Innovation

- A new semiconductor electronic principle and technology based on conductivity change, utilizing P-N junctions as passive elements with directional adjustable impedance, where conductivity is modulated by applied voltage to enhance signal conversion and amplification, leading to the development of high-stability, low-power-loss devices.

Thermoelectric element

PatentInactiveEP1287566A1

Innovation

- Extending the pn junction along the entire length of n and p layers with a temperature gradient applied parallel to the junction interface, allowing for selective contacting and utilizing non-linear thermal properties to enhance potential modulation and ambipolar diffusion for increased efficiency.

Materials Science Advancements for Junction Stability

Recent advancements in materials science have significantly contributed to enhancing P-N junction temperature stability. Traditional semiconductor materials like silicon and germanium exhibit notable performance degradation at elevated temperatures due to increased carrier recombination rates and leakage currents. However, wide-bandgap semiconductors such as silicon carbide (SiC) and gallium nitride (GaN) have emerged as promising alternatives, demonstrating superior thermal stability up to 500°C and 700°C respectively.

The incorporation of novel dopant stabilization techniques has revolutionized junction stability. Researchers have developed co-doping strategies where complementary dopants are introduced to counterbalance diffusion effects at high temperatures. For instance, carbon co-doping in GaAs junctions has been shown to reduce dopant diffusion by up to 60% at temperatures exceeding 200°C, maintaining junction integrity under thermal stress.

Nanostructured materials represent another breakthrough in junction stability enhancement. Quantum dots and nanowires integrated into junction designs provide quantum confinement effects that inherently improve carrier behavior at elevated temperatures. Studies indicate that silicon nanowire junctions maintain 85% of their room temperature performance at 150°C, compared to just 60% for conventional planar junctions.

Interface engineering techniques have advanced considerably, with atomic layer deposition (ALD) enabling precise control over junction interfaces. The introduction of buffer layers composed of thermally stable compounds like aluminum oxide or hafnium dioxide has demonstrated significant reduction in interface state density fluctuations across temperature ranges. These engineered interfaces show 40% less degradation in ideality factors when subjected to thermal cycling.

Strain engineering approaches have proven effective in modifying band structures to enhance temperature stability. Controlled introduction of tensile or compressive strain alters carrier mobility and recombination dynamics, potentially offsetting temperature-induced performance degradation. Recent experiments with strained SiGe junctions showed a 30% improvement in temperature coefficient compared to unstrained counterparts.

Composite and heterojunction materials combining complementary semiconductors have demonstrated synergistic temperature stability. For example, GaN/SiC heterojunctions leverage the thermal conductivity of SiC with the electronic properties of GaN, resulting in devices that maintain consistent performance across broader temperature ranges than either material alone.

These materials science innovations collectively represent a paradigm shift in junction stability, enabling semiconductor devices to operate reliably in harsh environments including automotive, aerospace, and industrial applications where temperature fluctuations previously limited semiconductor implementation.

The incorporation of novel dopant stabilization techniques has revolutionized junction stability. Researchers have developed co-doping strategies where complementary dopants are introduced to counterbalance diffusion effects at high temperatures. For instance, carbon co-doping in GaAs junctions has been shown to reduce dopant diffusion by up to 60% at temperatures exceeding 200°C, maintaining junction integrity under thermal stress.

Nanostructured materials represent another breakthrough in junction stability enhancement. Quantum dots and nanowires integrated into junction designs provide quantum confinement effects that inherently improve carrier behavior at elevated temperatures. Studies indicate that silicon nanowire junctions maintain 85% of their room temperature performance at 150°C, compared to just 60% for conventional planar junctions.

Interface engineering techniques have advanced considerably, with atomic layer deposition (ALD) enabling precise control over junction interfaces. The introduction of buffer layers composed of thermally stable compounds like aluminum oxide or hafnium dioxide has demonstrated significant reduction in interface state density fluctuations across temperature ranges. These engineered interfaces show 40% less degradation in ideality factors when subjected to thermal cycling.

Strain engineering approaches have proven effective in modifying band structures to enhance temperature stability. Controlled introduction of tensile or compressive strain alters carrier mobility and recombination dynamics, potentially offsetting temperature-induced performance degradation. Recent experiments with strained SiGe junctions showed a 30% improvement in temperature coefficient compared to unstrained counterparts.

Composite and heterojunction materials combining complementary semiconductors have demonstrated synergistic temperature stability. For example, GaN/SiC heterojunctions leverage the thermal conductivity of SiC with the electronic properties of GaN, resulting in devices that maintain consistent performance across broader temperature ranges than either material alone.

These materials science innovations collectively represent a paradigm shift in junction stability, enabling semiconductor devices to operate reliably in harsh environments including automotive, aerospace, and industrial applications where temperature fluctuations previously limited semiconductor implementation.

Reliability Testing Standards for Temperature Performance

Reliability testing standards for temperature performance in P-N junction devices have evolved significantly over the past decades to address the critical nature of thermal stability in semiconductor applications. Industry standards such as JEDEC JESD22-A104 and MIL-STD-883 Method 1010 provide comprehensive frameworks for temperature cycling tests, establishing protocols that typically range from -65°C to +150°C for high-reliability applications.

These standards mandate specific temperature ramp rates, typically 10-15°C per minute, to prevent thermal shock while still effectively stressing the device. Dwell times at temperature extremes are standardized at 10-15 minutes to ensure thermal equilibrium throughout the device structure, allowing for complete manifestation of thermal expansion effects at the junction interfaces.

The Automotive Electronics Council's AEC-Q100 standard has become particularly influential, defining stress test qualifications for integrated circuits in automotive applications. Grade 0 of this standard requires operational stability from -40°C to +150°C, reflecting the harsh environments encountered in under-hood automotive applications where P-N junctions must maintain performance integrity.

High Accelerated Stress Test (HAST) protocols combine elevated temperature with high humidity (typically 130°C at 85% relative humidity) to evaluate moisture-induced degradation at P-N junctions. This test accelerates failure mechanisms that might otherwise take years to manifest under normal operating conditions.

Temperature-Humidity-Bias (THB) testing extends standard evaluations by applying electrical bias during temperature and humidity cycling, providing critical insights into how P-N junctions perform under simultaneous thermal and electrical stress—conditions that more accurately reflect real-world operation.

For power semiconductor devices where P-N junction temperature stability is particularly critical, power cycling tests have been standardized to evaluate performance under repetitive heating and cooling caused by current flow. These tests typically specify junction temperature excursions (ΔTj) of 100-125°C with thousands of cycles required to validate reliability.

Recent developments in reliability standards have introduced more sophisticated approaches such as mission profile-based testing, where temperature cycles are designed to replicate actual application conditions rather than arbitrary extremes. This approach provides more relevant data on how P-N junctions will perform in specific deployment scenarios.

The emergence of wide bandgap semiconductors has necessitated updates to testing standards, with SiC and GaN devices requiring evaluation at higher temperature extremes (up to 300°C for some applications) to properly characterize their enhanced thermal capabilities compared to traditional silicon P-N junctions.

These standards mandate specific temperature ramp rates, typically 10-15°C per minute, to prevent thermal shock while still effectively stressing the device. Dwell times at temperature extremes are standardized at 10-15 minutes to ensure thermal equilibrium throughout the device structure, allowing for complete manifestation of thermal expansion effects at the junction interfaces.

The Automotive Electronics Council's AEC-Q100 standard has become particularly influential, defining stress test qualifications for integrated circuits in automotive applications. Grade 0 of this standard requires operational stability from -40°C to +150°C, reflecting the harsh environments encountered in under-hood automotive applications where P-N junctions must maintain performance integrity.

High Accelerated Stress Test (HAST) protocols combine elevated temperature with high humidity (typically 130°C at 85% relative humidity) to evaluate moisture-induced degradation at P-N junctions. This test accelerates failure mechanisms that might otherwise take years to manifest under normal operating conditions.

Temperature-Humidity-Bias (THB) testing extends standard evaluations by applying electrical bias during temperature and humidity cycling, providing critical insights into how P-N junctions perform under simultaneous thermal and electrical stress—conditions that more accurately reflect real-world operation.

For power semiconductor devices where P-N junction temperature stability is particularly critical, power cycling tests have been standardized to evaluate performance under repetitive heating and cooling caused by current flow. These tests typically specify junction temperature excursions (ΔTj) of 100-125°C with thousands of cycles required to validate reliability.

Recent developments in reliability standards have introduced more sophisticated approaches such as mission profile-based testing, where temperature cycles are designed to replicate actual application conditions rather than arbitrary extremes. This approach provides more relevant data on how P-N junctions will perform in specific deployment scenarios.

The emergence of wide bandgap semiconductors has necessitated updates to testing standards, with SiC and GaN devices requiring evaluation at higher temperature extremes (up to 300°C for some applications) to properly characterize their enhanced thermal capabilities compared to traditional silicon P-N junctions.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!