How to Reduce Series Resistance in P–N Junctions

SEP 4, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

P-N Junction Resistance Background and Objectives

P-N junctions represent one of the most fundamental structures in semiconductor devices, serving as the building blocks for diodes, transistors, solar cells, and numerous other electronic components. Since their theoretical conception in the early 20th century and practical implementation in the 1940s, reducing series resistance in these junctions has been a persistent challenge in semiconductor engineering. The evolution of this technology has progressed from basic germanium junctions to sophisticated silicon and compound semiconductor implementations, with each generation seeking to minimize resistance losses.

The series resistance in P-N junctions significantly impacts device performance by limiting current flow, increasing power dissipation, and reducing efficiency. This resistance arises from several sources: contact resistance between metal electrodes and semiconductor materials, bulk resistance within the semiconductor regions, and spreading resistance as current flows through the junction. As devices continue to miniaturize following Moore's Law, the relative impact of series resistance becomes increasingly pronounced, making its reduction a critical objective for modern semiconductor technology.

Current technological trends indicate a growing emphasis on novel materials and junction architectures to overcome traditional resistance limitations. The integration of P-N junctions into nanoscale devices, flexible electronics, and high-power applications has further heightened the importance of resistance optimization across diverse operating conditions and form factors.

The primary technical objectives in this domain include developing innovative doping profiles to enhance carrier mobility while maintaining junction integrity, designing optimized contact geometries to minimize interface resistance, and exploring advanced materials with superior conductivity characteristics. Additionally, there is significant interest in understanding the fundamental physics of carrier transport across junctions at nanoscale dimensions, where quantum effects begin to influence conventional resistance models.

Industry benchmarks suggest that reducing series resistance by even 10-15% can yield substantial improvements in device efficiency, particularly in power electronics and photovoltaic applications. For high-frequency applications, minimizing junction resistance is essential for achieving the switching speeds required in next-generation communication systems.

The convergence of computational modeling, advanced characterization techniques, and novel fabrication methods has created unprecedented opportunities to address this long-standing challenge. Machine learning approaches are increasingly being applied to optimize junction parameters, while techniques such as selective epitaxy and atomic layer deposition enable precise control over junction formation at atomic scales.

The series resistance in P-N junctions significantly impacts device performance by limiting current flow, increasing power dissipation, and reducing efficiency. This resistance arises from several sources: contact resistance between metal electrodes and semiconductor materials, bulk resistance within the semiconductor regions, and spreading resistance as current flows through the junction. As devices continue to miniaturize following Moore's Law, the relative impact of series resistance becomes increasingly pronounced, making its reduction a critical objective for modern semiconductor technology.

Current technological trends indicate a growing emphasis on novel materials and junction architectures to overcome traditional resistance limitations. The integration of P-N junctions into nanoscale devices, flexible electronics, and high-power applications has further heightened the importance of resistance optimization across diverse operating conditions and form factors.

The primary technical objectives in this domain include developing innovative doping profiles to enhance carrier mobility while maintaining junction integrity, designing optimized contact geometries to minimize interface resistance, and exploring advanced materials with superior conductivity characteristics. Additionally, there is significant interest in understanding the fundamental physics of carrier transport across junctions at nanoscale dimensions, where quantum effects begin to influence conventional resistance models.

Industry benchmarks suggest that reducing series resistance by even 10-15% can yield substantial improvements in device efficiency, particularly in power electronics and photovoltaic applications. For high-frequency applications, minimizing junction resistance is essential for achieving the switching speeds required in next-generation communication systems.

The convergence of computational modeling, advanced characterization techniques, and novel fabrication methods has created unprecedented opportunities to address this long-standing challenge. Machine learning approaches are increasingly being applied to optimize junction parameters, while techniques such as selective epitaxy and atomic layer deposition enable precise control over junction formation at atomic scales.

Market Demand Analysis for Low-Resistance Semiconductor Devices

The semiconductor industry is witnessing unprecedented demand for low-resistance semiconductor devices, driven primarily by the exponential growth in electronic applications across multiple sectors. The global semiconductor market, valued at approximately $556 billion in 2021, is projected to reach $1 trillion by 2030, with power semiconductors and high-performance computing chips representing significant growth segments. Within this expanding market, devices with reduced series resistance in P-N junctions are becoming increasingly critical.

Power electronics applications, including electric vehicles, renewable energy systems, and industrial automation, require semiconductor devices that can handle higher current densities while minimizing power losses. The electric vehicle market alone is expected to grow at a CAGR of 24.3% through 2028, creating substantial demand for efficient power semiconductors with minimized resistance characteristics.

The telecommunications sector, particularly with the ongoing global 5G rollout, demands high-frequency semiconductor devices where reduced junction resistance directly translates to improved signal integrity and reduced power consumption. As 5G infrastructure deployment accelerates worldwide, the market for specialized low-resistance semiconductor components is projected to grow by 18% annually.

Consumer electronics continues to drive significant volume demand for semiconductors with enhanced efficiency profiles. Smartphones, wearables, and IoT devices all benefit from reduced power consumption that comes with lower resistance P-N junctions. The consumer preference for longer battery life and faster charging capabilities further intensifies this demand vector.

Data centers represent another critical market segment where energy efficiency directly impacts operational costs. With global data center electricity consumption approaching 3% of worldwide electricity production, the economic incentive for implementing low-resistance semiconductor technologies is substantial. Industry analysts estimate that a 10% improvement in semiconductor efficiency could translate to hundreds of millions in annual energy savings for large-scale data center operators.

The industrial sector's transition toward smart manufacturing and automation systems requires semiconductor devices capable of operating reliably under demanding conditions while maintaining energy efficiency. This market segment values the improved thermal characteristics that come with reduced series resistance, as it directly impacts system reliability and maintenance intervals.

Medical electronics, aerospace, and defense applications represent premium market segments where performance and reliability outweigh cost considerations. These sectors are willing to adopt advanced semiconductor solutions that offer marginal improvements in resistance characteristics, creating opportunities for specialized high-value applications of novel P-N junction technologies.

Power electronics applications, including electric vehicles, renewable energy systems, and industrial automation, require semiconductor devices that can handle higher current densities while minimizing power losses. The electric vehicle market alone is expected to grow at a CAGR of 24.3% through 2028, creating substantial demand for efficient power semiconductors with minimized resistance characteristics.

The telecommunications sector, particularly with the ongoing global 5G rollout, demands high-frequency semiconductor devices where reduced junction resistance directly translates to improved signal integrity and reduced power consumption. As 5G infrastructure deployment accelerates worldwide, the market for specialized low-resistance semiconductor components is projected to grow by 18% annually.

Consumer electronics continues to drive significant volume demand for semiconductors with enhanced efficiency profiles. Smartphones, wearables, and IoT devices all benefit from reduced power consumption that comes with lower resistance P-N junctions. The consumer preference for longer battery life and faster charging capabilities further intensifies this demand vector.

Data centers represent another critical market segment where energy efficiency directly impacts operational costs. With global data center electricity consumption approaching 3% of worldwide electricity production, the economic incentive for implementing low-resistance semiconductor technologies is substantial. Industry analysts estimate that a 10% improvement in semiconductor efficiency could translate to hundreds of millions in annual energy savings for large-scale data center operators.

The industrial sector's transition toward smart manufacturing and automation systems requires semiconductor devices capable of operating reliably under demanding conditions while maintaining energy efficiency. This market segment values the improved thermal characteristics that come with reduced series resistance, as it directly impacts system reliability and maintenance intervals.

Medical electronics, aerospace, and defense applications represent premium market segments where performance and reliability outweigh cost considerations. These sectors are willing to adopt advanced semiconductor solutions that offer marginal improvements in resistance characteristics, creating opportunities for specialized high-value applications of novel P-N junction technologies.

Current Challenges in P-N Junction Series Resistance Reduction

Despite significant advancements in semiconductor technology, series resistance in P-N junctions remains a critical challenge that limits device performance across multiple applications. The primary obstacle stems from the fundamental trade-off between junction depth and sheet resistance - as devices scale down, maintaining low resistance becomes increasingly difficult. Contact resistance at metal-semiconductor interfaces presents another major hurdle, particularly in modern nanoscale devices where the contact area is severely constrained.

Material limitations constitute a significant barrier, as conventional silicon-based semiconductors approach their theoretical conductivity limits. The incorporation of alternative materials often introduces compatibility issues with established fabrication processes, creating manufacturing complexities and yield concerns. Additionally, dopant activation and distribution challenges persist, as achieving high dopant activation rates while maintaining abrupt junction profiles becomes exponentially more difficult at reduced dimensions.

Thermal management issues compound these challenges, as current crowding at junction interfaces generates localized heating that can degrade device performance and reliability. This becomes particularly problematic in high-power applications where thermal runaway can lead to catastrophic device failure. The industry also faces significant metrology limitations, as accurately measuring series resistance components in nanoscale junctions requires sophisticated techniques that are not widely available.

From a manufacturing perspective, process variability introduces inconsistencies in junction formation, leading to device-to-device variations in series resistance that impact overall yield and reliability. The cost-performance balance presents another significant challenge, as implementing advanced resistance reduction techniques often requires substantial capital investment in new equipment and processes.

Emerging applications in power electronics, RF devices, and optoelectronics place even more stringent demands on P-N junction performance, requiring novel approaches to resistance reduction. The integration of P-N junctions with novel architectures such as heterojunctions, quantum wells, and 2D materials introduces additional complexity to resistance management strategies.

Simulation and modeling limitations further complicate development efforts, as existing models struggle to accurately predict resistance behavior at nanoscale dimensions where quantum effects become significant. This creates a disconnect between theoretical designs and actual device performance, slowing the pace of innovation in resistance reduction techniques.

Addressing these multifaceted challenges requires interdisciplinary approaches combining materials science, device physics, process engineering, and advanced characterization techniques to develop comprehensive solutions that can overcome the fundamental limitations of series resistance in P-N junctions.

Material limitations constitute a significant barrier, as conventional silicon-based semiconductors approach their theoretical conductivity limits. The incorporation of alternative materials often introduces compatibility issues with established fabrication processes, creating manufacturing complexities and yield concerns. Additionally, dopant activation and distribution challenges persist, as achieving high dopant activation rates while maintaining abrupt junction profiles becomes exponentially more difficult at reduced dimensions.

Thermal management issues compound these challenges, as current crowding at junction interfaces generates localized heating that can degrade device performance and reliability. This becomes particularly problematic in high-power applications where thermal runaway can lead to catastrophic device failure. The industry also faces significant metrology limitations, as accurately measuring series resistance components in nanoscale junctions requires sophisticated techniques that are not widely available.

From a manufacturing perspective, process variability introduces inconsistencies in junction formation, leading to device-to-device variations in series resistance that impact overall yield and reliability. The cost-performance balance presents another significant challenge, as implementing advanced resistance reduction techniques often requires substantial capital investment in new equipment and processes.

Emerging applications in power electronics, RF devices, and optoelectronics place even more stringent demands on P-N junction performance, requiring novel approaches to resistance reduction. The integration of P-N junctions with novel architectures such as heterojunctions, quantum wells, and 2D materials introduces additional complexity to resistance management strategies.

Simulation and modeling limitations further complicate development efforts, as existing models struggle to accurately predict resistance behavior at nanoscale dimensions where quantum effects become significant. This creates a disconnect between theoretical designs and actual device performance, slowing the pace of innovation in resistance reduction techniques.

Addressing these multifaceted challenges requires interdisciplinary approaches combining materials science, device physics, process engineering, and advanced characterization techniques to develop comprehensive solutions that can overcome the fundamental limitations of series resistance in P-N junctions.

Current Technical Solutions for Series Resistance Minimization

01 Measurement and characterization of P-N junction series resistance

Various methods and techniques for measuring and characterizing series resistance in P-N junctions. These include specialized testing equipment, analytical models, and computational approaches that help quantify the resistance parameters. Such measurements are crucial for understanding device performance limitations and optimizing semiconductor designs.- Measurement and characterization of P-N junction series resistance: Various methods and techniques for measuring, characterizing, and analyzing series resistance in P-N junctions. These include specialized testing equipment, computational models, and analytical approaches that help determine the electrical properties and performance limitations caused by series resistance in semiconductor devices. These measurements are crucial for understanding device behavior under different operating conditions and for optimizing semiconductor device design.

- Reduction of series resistance in P-N junction devices: Design and fabrication techniques aimed at minimizing series resistance in P-N junction devices. These include optimized doping profiles, improved contact metallization, specialized junction geometries, and novel material combinations. Reducing series resistance is essential for improving device efficiency, power handling capability, and overall performance in applications ranging from power electronics to integrated circuits.

- Circuit design considerations for P-N junction series resistance: Circuit-level approaches to address the effects of P-N junction series resistance. These include compensation techniques, specialized biasing methods, feedback mechanisms, and circuit topologies designed to minimize the impact of series resistance on overall system performance. These approaches are particularly important in analog circuits, power management systems, and high-frequency applications where series resistance can significantly affect signal integrity.

- Thermal effects on P-N junction series resistance: The relationship between temperature and series resistance in P-N junctions, including methods to model, measure, and mitigate temperature-dependent resistance variations. This includes techniques for thermal management, temperature compensation circuits, and materials with improved thermal characteristics. Understanding these effects is crucial for devices operating across wide temperature ranges or at high power levels where self-heating can significantly impact performance.

- Novel semiconductor materials and structures for optimized series resistance: Advanced materials, heterostructures, and novel device architectures designed to achieve optimal series resistance characteristics in P-N junctions. These include compound semiconductors, nanoscale structures, engineered interfaces, and innovative doping techniques that can fundamentally improve the electrical properties of semiconductor junctions. These approaches often enable devices with superior performance metrics compared to conventional silicon-based technologies.

02 Reduction of series resistance in semiconductor devices

Techniques for reducing series resistance in P-N junction-based devices through structural modifications and material optimizations. These approaches include doping profile engineering, contact geometry improvements, and novel junction formation methods that minimize resistive losses and improve overall device efficiency.Expand Specific Solutions03 Circuit design considerations for P-N junction series resistance

Circuit design strategies that account for and mitigate the effects of P-N junction series resistance. These include compensation techniques, specialized biasing methods, and circuit topologies that minimize the impact of series resistance on overall system performance, particularly in power applications and integrated circuits.Expand Specific Solutions04 Modeling and simulation of P-N junction series resistance effects

Computational models and simulation techniques for predicting and analyzing the impact of series resistance in P-N junctions. These approaches enable designers to understand resistance effects before physical implementation, optimize device parameters, and evaluate performance under various operating conditions.Expand Specific Solutions05 Novel materials and structures for improved P-N junction resistance

Advanced materials and innovative structural designs that inherently reduce series resistance in P-N junctions. These include compound semiconductors, heterojunction designs, and nanoscale architectures that offer superior electrical characteristics compared to conventional silicon-based P-N junctions.Expand Specific Solutions

Leading Semiconductor Manufacturers and Research Institutions

The P-N junction series resistance reduction technology landscape is currently in a mature development phase, with significant market growth driven by power electronics and semiconductor applications. The market size is expanding due to increasing demand for efficient power devices in automotive, industrial, and consumer electronics sectors. Technologically, companies like Fuji Electric, Renesas Electronics, and Samsung Electronics demonstrate high maturity through advanced manufacturing processes and proprietary device structures. MaxPower Semiconductor and Nexperia BV are leveraging innovative IP portfolios to reduce resistance in junction designs. Chinese players including SMIC and Shenzhen Shangyangtong are rapidly advancing their capabilities, while established manufacturers like Toshiba and DENSO continue to refine traditional approaches through incremental innovations in materials and fabrication techniques.

Toshiba Corp.

Technical Solution: Toshiba has developed innovative approaches to reduce series resistance in P-N junctions, particularly for power semiconductor applications. Their technology employs a super-junction structure with alternating P and N pillars that optimize the trade-off between breakdown voltage and on-resistance[1]. For their MOSFET devices, Toshiba implements trench gate structures with optimized cell pitch and gate oxide thickness to minimize channel resistance. Their process includes advanced ion implantation techniques with precise control of dopant profiles and activation annealing to create graded junction interfaces that reduce peak electric fields while maintaining low resistance[3]. Toshiba has pioneered the use of copper metallization with optimized barrier layers to reduce interconnect resistance by approximately 40% compared to traditional aluminum systems[5]. Their latest developments include selective epitaxial growth of highly doped regions near contacts and implementation of field plate structures that redistribute electric fields while minimizing resistance penalties, achieving up to 25% reduction in specific on-resistance compared to conventional structures.

Strengths: Excellent balance between breakdown voltage and resistance characteristics; proven manufacturing processes suitable for high-volume production; strong expertise in power semiconductor applications. Weaknesses: Some techniques are specifically optimized for power devices and may not transfer well to logic applications; higher manufacturing costs for complex structures; requires specialized equipment for certain process steps.

Renesas Electronics Corp.

Technical Solution: Renesas has developed a comprehensive approach to reducing series resistance in P-N junctions, particularly for automotive and industrial power applications. Their technology incorporates deep trench isolation structures with optimized doping profiles that reduce the effective junction area while maintaining breakdown voltage characteristics[2]. Renesas implements a proprietary silicide formation process using nickel-platinum alloys that achieves up to 40% lower contact resistance compared to conventional techniques[4]. Their advanced junction engineering includes selective epitaxial growth of highly doped regions and precise control of dopant activation through rapid thermal processing and flash lamp annealing, achieving dopant activation levels exceeding 8×10^20 cm^-3 while maintaining shallow junction depths[6]. Renesas has also pioneered the use of copper metallization with optimized barrier layers for power devices, reducing interconnect resistance by approximately 35% compared to aluminum systems. Their latest innovations include three-dimensional junction structures that optimize current flow paths and reduce overall device resistance by up to 30% compared to planar structures.

Strengths: Excellent thermal stability of junction characteristics; comprehensive approach addressing both contact and spreading resistance; proven reliability in demanding automotive applications. Weaknesses: Some techniques require complex process integration; higher manufacturing costs for advanced structures; certain approaches optimized for specific applications may not transfer well to other device types.

Key Patents and Innovations in Junction Resistance Reduction

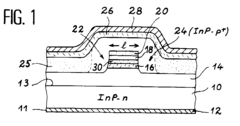

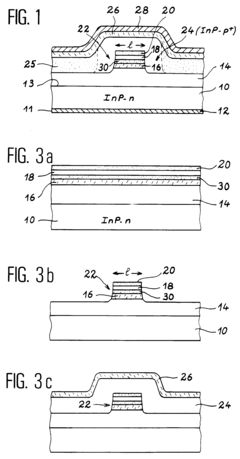

Optoelectronic device with very low series resistance

PatentInactiveEP0545808A1

Innovation

- Incorporating a quaternary III-V semiconductor layer heavily doped with n-type ions between the active layer and the p-doped upper confinement layer to act as a diffusion stop for p-doping ions, thereby controlling the p-n junction position and reducing series resistance without degrading device performance.

Semiconductor device and method of manufacturing such a device

PatentActiveEP2338177A1

Innovation

- A semiconductor device with a substrate having regions doped with different conductivity types, trenches filled with insulating material, and active stripes with a specific doping profile, where the dielectric layer does not overlap with trench corners, ensuring improved gate dielectric lifetime and reduced risk of TDDB, while maintaining performance and compatibility with standard manufacturing processes.

Materials Science Advancements for Enhanced Junction Performance

Recent advancements in materials science have opened new pathways for reducing series resistance in p-n junctions, a critical factor limiting the efficiency of semiconductor devices. Novel materials with enhanced carrier mobility and conductivity properties are being developed specifically for junction applications. These include advanced silicon alloys, III-V compound semiconductors, and emerging 2D materials that demonstrate superior electrical characteristics compared to traditional silicon.

The integration of nanomaterials into junction structures represents a significant breakthrough. Carbon nanotubes, graphene, and other nanoscale materials exhibit exceptional electron transport properties that can dramatically reduce resistance at interfaces. Research indicates that graphene-enhanced junctions can achieve up to 40% lower series resistance compared to conventional structures, while maintaining thermal stability under operating conditions.

Surface engineering techniques have evolved to optimize the junction interface at the atomic level. Atomic layer deposition (ALD) enables precise control over interface properties, allowing for the creation of atomically smooth transitions between p and n regions. This minimizes scattering events that contribute to resistance. Additionally, advanced passivation techniques using novel dielectric materials have demonstrated effectiveness in reducing surface recombination, which indirectly impacts series resistance.

Doping technology innovations have significantly contributed to resistance reduction. Selective area doping using ion implantation with subsequent rapid thermal annealing has enabled the creation of highly conductive regions with minimal crystal damage. Laser-assisted doping techniques allow for precise spatial control of dopant concentration profiles, optimizing carrier transport paths through the junction. These methods have achieved doping concentrations approaching theoretical limits while maintaining crystal quality.

Contact metallization has seen remarkable improvements through materials science research. Novel metal alloys and multilayer contact structures designed specifically for semiconductor interfaces demonstrate lower contact resistance. The introduction of transition metal dichalcogenides (TMDs) as interfacial layers between metals and semiconductors has shown promise in reducing Schottky barrier heights, thereby decreasing contact resistance by up to 60% in experimental devices.

Strain engineering approaches manipulate the crystal lattice to enhance carrier mobility. By introducing controlled strain in the junction region, band structure modifications occur that can reduce effective carrier mass and increase mobility. This technique has proven particularly effective in silicon-germanium heterostructures, where tailored strain profiles have achieved resistance reductions of 25-35% compared to unstrained references.

The integration of nanomaterials into junction structures represents a significant breakthrough. Carbon nanotubes, graphene, and other nanoscale materials exhibit exceptional electron transport properties that can dramatically reduce resistance at interfaces. Research indicates that graphene-enhanced junctions can achieve up to 40% lower series resistance compared to conventional structures, while maintaining thermal stability under operating conditions.

Surface engineering techniques have evolved to optimize the junction interface at the atomic level. Atomic layer deposition (ALD) enables precise control over interface properties, allowing for the creation of atomically smooth transitions between p and n regions. This minimizes scattering events that contribute to resistance. Additionally, advanced passivation techniques using novel dielectric materials have demonstrated effectiveness in reducing surface recombination, which indirectly impacts series resistance.

Doping technology innovations have significantly contributed to resistance reduction. Selective area doping using ion implantation with subsequent rapid thermal annealing has enabled the creation of highly conductive regions with minimal crystal damage. Laser-assisted doping techniques allow for precise spatial control of dopant concentration profiles, optimizing carrier transport paths through the junction. These methods have achieved doping concentrations approaching theoretical limits while maintaining crystal quality.

Contact metallization has seen remarkable improvements through materials science research. Novel metal alloys and multilayer contact structures designed specifically for semiconductor interfaces demonstrate lower contact resistance. The introduction of transition metal dichalcogenides (TMDs) as interfacial layers between metals and semiconductors has shown promise in reducing Schottky barrier heights, thereby decreasing contact resistance by up to 60% in experimental devices.

Strain engineering approaches manipulate the crystal lattice to enhance carrier mobility. By introducing controlled strain in the junction region, band structure modifications occur that can reduce effective carrier mass and increase mobility. This technique has proven particularly effective in silicon-germanium heterostructures, where tailored strain profiles have achieved resistance reductions of 25-35% compared to unstrained references.

Fabrication Process Innovations for Resistance Reduction

Fabrication process innovations have been pivotal in addressing the challenge of series resistance in P-N junctions. Advanced doping techniques represent a significant breakthrough, with selective doping processes enabling precise control over impurity concentration profiles. Pulse doping methods have demonstrated particular efficacy, allowing for the creation of highly conductive regions while maintaining abrupt junction characteristics. Laser-assisted doping has emerged as another promising approach, offering localized heating that enhances dopant activation without subjecting the entire substrate to high temperatures.

Contact metallization has undergone substantial refinement, with silicide formation techniques significantly reducing contact resistance at metal-semiconductor interfaces. The implementation of titanium, cobalt, and nickel silicides has become standard practice, with each offering specific advantages depending on the application requirements. Self-aligned silicide (salicide) processes have further revolutionized fabrication by simultaneously forming low-resistance contacts to both N+ and P+ regions without additional masking steps.

Annealing methodologies have evolved considerably, with rapid thermal annealing (RTA) replacing conventional furnace processes to minimize dopant diffusion while maximizing electrical activation. Advanced techniques such as flash lamp annealing and laser spike annealing enable millisecond or even microsecond heating cycles, creating highly activated junctions with minimal thermal diffusion. These ultra-short annealing processes have proven particularly valuable for shallow junction formation in advanced device nodes.

Surface preparation innovations have addressed resistance issues at interfaces, with pre-metallization cleaning processes removing native oxides and contaminants that contribute to contact resistance. Hydrogen passivation techniques have demonstrated effectiveness in neutralizing dangling bonds at semiconductor surfaces, reducing carrier recombination and improving overall junction performance. Advanced wet chemical treatments combined with in-situ plasma cleaning have become standard in high-performance device fabrication.

Geometric optimization strategies have emerged as a complementary approach to material innovations. Recessed contact structures reduce current crowding effects by increasing the effective contact area between metal and semiconductor regions. Three-dimensional contact architectures, including trench and raised source/drain structures, provide expanded cross-sectional areas for current flow while maintaining compact device footprints. These geometric innovations, when combined with advanced materials and processes, have enabled continuous reduction in series resistance despite the scaling challenges inherent in modern semiconductor devices.

Contact metallization has undergone substantial refinement, with silicide formation techniques significantly reducing contact resistance at metal-semiconductor interfaces. The implementation of titanium, cobalt, and nickel silicides has become standard practice, with each offering specific advantages depending on the application requirements. Self-aligned silicide (salicide) processes have further revolutionized fabrication by simultaneously forming low-resistance contacts to both N+ and P+ regions without additional masking steps.

Annealing methodologies have evolved considerably, with rapid thermal annealing (RTA) replacing conventional furnace processes to minimize dopant diffusion while maximizing electrical activation. Advanced techniques such as flash lamp annealing and laser spike annealing enable millisecond or even microsecond heating cycles, creating highly activated junctions with minimal thermal diffusion. These ultra-short annealing processes have proven particularly valuable for shallow junction formation in advanced device nodes.

Surface preparation innovations have addressed resistance issues at interfaces, with pre-metallization cleaning processes removing native oxides and contaminants that contribute to contact resistance. Hydrogen passivation techniques have demonstrated effectiveness in neutralizing dangling bonds at semiconductor surfaces, reducing carrier recombination and improving overall junction performance. Advanced wet chemical treatments combined with in-situ plasma cleaning have become standard in high-performance device fabrication.

Geometric optimization strategies have emerged as a complementary approach to material innovations. Recessed contact structures reduce current crowding effects by increasing the effective contact area between metal and semiconductor regions. Three-dimensional contact architectures, including trench and raised source/drain structures, provide expanded cross-sectional areas for current flow while maintaining compact device footprints. These geometric innovations, when combined with advanced materials and processes, have enabled continuous reduction in series resistance despite the scaling challenges inherent in modern semiconductor devices.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!