How to Test RRAM Efficiency in High-Temperature Systems

SEP 10, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

RRAM Technology Background and Testing Objectives

Resistive Random Access Memory (RRAM) has emerged as a promising non-volatile memory technology over the past two decades, offering advantages such as high density, low power consumption, and compatibility with CMOS processes. The evolution of RRAM technology can be traced back to the early 2000s when researchers first demonstrated reliable resistive switching phenomena in metal-oxide materials. Since then, significant advancements have been made in understanding the underlying mechanisms and improving device performance.

RRAM operates based on the principle of resistive switching, where the resistance of a dielectric material can be altered between high and low resistance states by applying appropriate electrical stimuli. This mechanism relies on the formation and rupture of conductive filaments within the dielectric layer, typically composed of metal oxides such as HfO2, TiO2, or Ta2O5. The technological trajectory has been focused on enhancing switching speed, endurance, retention time, and reducing power consumption.

High-temperature environments present unique challenges for RRAM operation and testing. As electronic systems in automotive, aerospace, industrial, and oil and gas exploration applications increasingly require components that can function reliably at elevated temperatures (typically ranging from 85°C to 200°C or higher), understanding RRAM behavior under these conditions becomes critical. Temperature affects various aspects of RRAM performance, including switching dynamics, retention characteristics, and overall reliability.

The primary objectives of testing RRAM efficiency in high-temperature systems are multifaceted. First, it aims to characterize the fundamental electrical parameters such as SET/RESET voltages, ON/OFF resistance ratios, and switching speeds as functions of temperature. This provides insights into how the core functionality of RRAM devices evolves under thermal stress.

Second, testing seeks to evaluate long-term reliability metrics including data retention, endurance cycles, and failure mechanisms at elevated temperatures. These parameters are crucial for determining the viability of RRAM in mission-critical applications where component failure could have severe consequences.

Third, the testing objectives include understanding the physical and chemical changes occurring within RRAM devices at high temperatures, such as ion migration dynamics, oxide layer stability, and electrode interface reactions. This fundamental knowledge is essential for developing more robust device architectures and materials.

Finally, testing aims to establish standardized methodologies and benchmarks for high-temperature RRAM evaluation, enabling fair comparisons between different device technologies and facilitating industry adoption. The ultimate goal is to develop RRAM solutions that maintain consistent performance across a wide temperature range, thereby expanding their applicability in extreme environment electronics.

RRAM operates based on the principle of resistive switching, where the resistance of a dielectric material can be altered between high and low resistance states by applying appropriate electrical stimuli. This mechanism relies on the formation and rupture of conductive filaments within the dielectric layer, typically composed of metal oxides such as HfO2, TiO2, or Ta2O5. The technological trajectory has been focused on enhancing switching speed, endurance, retention time, and reducing power consumption.

High-temperature environments present unique challenges for RRAM operation and testing. As electronic systems in automotive, aerospace, industrial, and oil and gas exploration applications increasingly require components that can function reliably at elevated temperatures (typically ranging from 85°C to 200°C or higher), understanding RRAM behavior under these conditions becomes critical. Temperature affects various aspects of RRAM performance, including switching dynamics, retention characteristics, and overall reliability.

The primary objectives of testing RRAM efficiency in high-temperature systems are multifaceted. First, it aims to characterize the fundamental electrical parameters such as SET/RESET voltages, ON/OFF resistance ratios, and switching speeds as functions of temperature. This provides insights into how the core functionality of RRAM devices evolves under thermal stress.

Second, testing seeks to evaluate long-term reliability metrics including data retention, endurance cycles, and failure mechanisms at elevated temperatures. These parameters are crucial for determining the viability of RRAM in mission-critical applications where component failure could have severe consequences.

Third, the testing objectives include understanding the physical and chemical changes occurring within RRAM devices at high temperatures, such as ion migration dynamics, oxide layer stability, and electrode interface reactions. This fundamental knowledge is essential for developing more robust device architectures and materials.

Finally, testing aims to establish standardized methodologies and benchmarks for high-temperature RRAM evaluation, enabling fair comparisons between different device technologies and facilitating industry adoption. The ultimate goal is to develop RRAM solutions that maintain consistent performance across a wide temperature range, thereby expanding their applicability in extreme environment electronics.

Market Demand for High-Temperature Memory Solutions

The high-temperature memory solutions market is experiencing significant growth driven by expanding applications in automotive, aerospace, industrial automation, and oil and gas exploration sectors. As operating environments become increasingly harsh, traditional memory technologies face substantial performance and reliability challenges, creating a robust demand for alternatives like RRAM that can withstand elevated temperatures.

The automotive industry represents one of the largest market segments, with under-hood electronics regularly exposed to temperatures exceeding 125°C. Market research indicates the automotive memory market is projected to grow at a CAGR of 18.5% through 2028, with high-temperature applications accounting for approximately one-third of this growth. Vehicle electrification trends are further accelerating this demand as power electronics require memory solutions capable of operating reliably at junction temperatures up to 175°C.

Aerospace and defense applications constitute another critical market segment. Avionics systems must maintain data integrity in extreme temperature conditions ranging from -55°C to +125°C. The need for radiation-hardened, high-temperature memory solutions in this sector is driving premium pricing and specialized development efforts, with the aerospace memory market expected to reach $3.2 billion by 2026.

Industrial automation represents a rapidly expanding application area where high-temperature memory is essential for factory floor equipment, robotics, and process control systems. These environments frequently expose electronics to temperatures between 85°C and 150°C while requiring uninterrupted operation for extended periods. The industrial IoT revolution is amplifying this demand as more sensors and edge computing devices are deployed in harsh industrial settings.

Deep drilling operations in the oil and gas industry create perhaps the most extreme temperature requirements, with downhole tools operating at temperatures exceeding 200°C. This niche but lucrative market segment commands premium pricing for qualified memory solutions, with companies willing to pay substantial premiums for proven reliability.

The overall high-temperature memory market is currently dominated by specialized DRAM and flash solutions, but these technologies face fundamental physical limitations at extreme temperatures. This creates a significant opportunity for emerging technologies like RRAM, which demonstrates inherent advantages in high-temperature environments. Market analysis suggests that RRAM could capture up to 15% of the high-temperature memory market within five years if manufacturers can demonstrate reliable performance and establish standardized testing protocols.

The automotive industry represents one of the largest market segments, with under-hood electronics regularly exposed to temperatures exceeding 125°C. Market research indicates the automotive memory market is projected to grow at a CAGR of 18.5% through 2028, with high-temperature applications accounting for approximately one-third of this growth. Vehicle electrification trends are further accelerating this demand as power electronics require memory solutions capable of operating reliably at junction temperatures up to 175°C.

Aerospace and defense applications constitute another critical market segment. Avionics systems must maintain data integrity in extreme temperature conditions ranging from -55°C to +125°C. The need for radiation-hardened, high-temperature memory solutions in this sector is driving premium pricing and specialized development efforts, with the aerospace memory market expected to reach $3.2 billion by 2026.

Industrial automation represents a rapidly expanding application area where high-temperature memory is essential for factory floor equipment, robotics, and process control systems. These environments frequently expose electronics to temperatures between 85°C and 150°C while requiring uninterrupted operation for extended periods. The industrial IoT revolution is amplifying this demand as more sensors and edge computing devices are deployed in harsh industrial settings.

Deep drilling operations in the oil and gas industry create perhaps the most extreme temperature requirements, with downhole tools operating at temperatures exceeding 200°C. This niche but lucrative market segment commands premium pricing for qualified memory solutions, with companies willing to pay substantial premiums for proven reliability.

The overall high-temperature memory market is currently dominated by specialized DRAM and flash solutions, but these technologies face fundamental physical limitations at extreme temperatures. This creates a significant opportunity for emerging technologies like RRAM, which demonstrates inherent advantages in high-temperature environments. Market analysis suggests that RRAM could capture up to 15% of the high-temperature memory market within five years if manufacturers can demonstrate reliable performance and establish standardized testing protocols.

Current Challenges in High-Temperature RRAM Testing

Testing RRAM (Resistive Random-Access Memory) devices in high-temperature environments presents significant technical challenges that impede accurate performance evaluation and reliability assessment. Current testing methodologies struggle to maintain precision when operating temperatures exceed 85°C, with particularly severe limitations above 125°C, which is often required for automotive, aerospace, and industrial applications.

The primary challenge lies in isolating RRAM-specific performance metrics from temperature-induced effects on the surrounding circuitry. As temperatures rise, peripheral components such as sense amplifiers, multiplexers, and control logic experience increased leakage currents and threshold voltage shifts, which can mask or distort the actual RRAM cell behavior being measured. This creates ambiguity in determining whether observed performance degradation stems from the RRAM cells themselves or from the testing infrastructure.

Measurement accuracy is further compromised by thermal noise, which increases proportionally with temperature according to Johnson-Nyquist noise principles. This is especially problematic when measuring the subtle resistance changes that characterize multi-level cell RRAM operations, where the signal-to-noise ratio deteriorates significantly at elevated temperatures, making state discrimination increasingly difficult.

Current test equipment faces substantial calibration challenges in high-temperature environments. Most commercial semiconductor parameter analyzers and memory testers are optimized for room-temperature operation, with compensation mechanisms that become increasingly inadequate above 100°C. This leads to systematic measurement errors that compound with rising temperatures, particularly affecting switching speed and endurance measurements.

The accelerated degradation mechanisms activated at high temperatures create another testing hurdle. Phenomena such as oxygen vacancy migration, electrode material diffusion, and interfacial layer breakdown occur at rates exponentially dependent on temperature. This makes it difficult to design test protocols that can accurately capture these effects without introducing artifacts from the measurement process itself.

Time-dependent variability presents yet another challenge. RRAM devices exhibit different temperature-dependent drift behaviors based on their material composition and fabrication process. Current testing methodologies struggle to distinguish between normal device-to-device variation and temperature-induced performance shifts, especially during extended high-temperature operation.

Finally, there is a significant gap in standardized testing protocols specifically designed for high-temperature RRAM evaluation. While standards exist for conventional memory technologies, the unique switching mechanisms and failure modes of RRAM require specialized approaches that account for the complex interplay between temperature, voltage stress, and cycling effects. This lack of standardization hampers cross-platform comparison and technology benchmarking efforts in the emerging non-volatile memory landscape.

The primary challenge lies in isolating RRAM-specific performance metrics from temperature-induced effects on the surrounding circuitry. As temperatures rise, peripheral components such as sense amplifiers, multiplexers, and control logic experience increased leakage currents and threshold voltage shifts, which can mask or distort the actual RRAM cell behavior being measured. This creates ambiguity in determining whether observed performance degradation stems from the RRAM cells themselves or from the testing infrastructure.

Measurement accuracy is further compromised by thermal noise, which increases proportionally with temperature according to Johnson-Nyquist noise principles. This is especially problematic when measuring the subtle resistance changes that characterize multi-level cell RRAM operations, where the signal-to-noise ratio deteriorates significantly at elevated temperatures, making state discrimination increasingly difficult.

Current test equipment faces substantial calibration challenges in high-temperature environments. Most commercial semiconductor parameter analyzers and memory testers are optimized for room-temperature operation, with compensation mechanisms that become increasingly inadequate above 100°C. This leads to systematic measurement errors that compound with rising temperatures, particularly affecting switching speed and endurance measurements.

The accelerated degradation mechanisms activated at high temperatures create another testing hurdle. Phenomena such as oxygen vacancy migration, electrode material diffusion, and interfacial layer breakdown occur at rates exponentially dependent on temperature. This makes it difficult to design test protocols that can accurately capture these effects without introducing artifacts from the measurement process itself.

Time-dependent variability presents yet another challenge. RRAM devices exhibit different temperature-dependent drift behaviors based on their material composition and fabrication process. Current testing methodologies struggle to distinguish between normal device-to-device variation and temperature-induced performance shifts, especially during extended high-temperature operation.

Finally, there is a significant gap in standardized testing protocols specifically designed for high-temperature RRAM evaluation. While standards exist for conventional memory technologies, the unique switching mechanisms and failure modes of RRAM require specialized approaches that account for the complex interplay between temperature, voltage stress, and cycling effects. This lack of standardization hampers cross-platform comparison and technology benchmarking efforts in the emerging non-volatile memory landscape.

Existing High-Temperature RRAM Testing Approaches

01 Material optimization for RRAM efficiency

Various materials can be optimized in RRAM devices to improve efficiency. This includes using specific metal oxides, doped materials, and novel composite structures as the resistive switching layer. The selection and engineering of these materials can significantly impact the switching speed, power consumption, and overall performance of RRAM devices. Optimized material interfaces and controlled defect engineering contribute to more reliable and energy-efficient memory operations.- Material optimization for RRAM efficiency: Various materials can be optimized to enhance RRAM efficiency. This includes using specific metal oxides, doped materials, and novel composite structures that improve switching characteristics. These optimized materials can reduce operating voltages, increase endurance, and improve retention time, all of which contribute to higher energy efficiency and better performance in resistive memory devices.

- Architectural improvements in RRAM design: Novel architectural designs can significantly improve RRAM efficiency. These include crossbar arrays, 3D stacking configurations, and innovative cell structures that optimize current flow and reduce parasitic effects. Such architectural improvements allow for higher density memory arrays while maintaining or improving power efficiency, leading to better overall system performance.

- Switching mechanism optimization: Optimizing the switching mechanisms in RRAM devices is crucial for efficiency. This involves controlling filament formation and rupture processes, managing oxygen vacancy migration, and implementing precise voltage control schemes. By fine-tuning these switching mechanisms, RRAM devices can achieve faster switching speeds, lower power consumption, and more reliable operation across multiple cycles.

- Integration with CMOS technology: Efficient integration of RRAM with conventional CMOS technology enhances overall system efficiency. This includes developing compatible fabrication processes, designing appropriate peripheral circuits, and implementing efficient sensing schemes. Such integration allows RRAM to leverage existing semiconductor infrastructure while providing benefits like non-volatility, reduced standby power, and improved system-level energy efficiency.

- Advanced programming and read schemes: Implementing advanced programming and read schemes can significantly improve RRAM efficiency. These include multi-level cell programming, adaptive pulse schemes, and error correction techniques that optimize the trade-off between speed, power, and reliability. Such advanced operational schemes enable higher data density, reduced energy per bit, and improved overall memory system efficiency.

02 Novel RRAM cell architectures

Innovative RRAM cell designs and architectures can enhance memory efficiency. These include 3D stacking configurations, crossbar arrays, and multi-level cell structures that increase storage density while maintaining or improving performance. Advanced cell architectures can reduce the footprint of memory arrays while enabling faster access times and lower power operation. Some designs incorporate selector devices to minimize sneak path currents in high-density arrays, further improving energy efficiency.Expand Specific Solutions03 Programming and operation methods for improved efficiency

Specialized programming algorithms and operation methods can significantly improve RRAM efficiency. These include pulse-width modulation techniques, adaptive programming schemes, and optimized read/write protocols that reduce energy consumption during memory operations. Advanced sensing circuits and reference schemes enable more reliable data reading at lower power levels. Some methods incorporate feedback mechanisms that adjust programming parameters in real-time based on device characteristics, leading to more consistent performance and extended device lifetime.Expand Specific Solutions04 Integration with CMOS and system-level optimization

Efficient integration of RRAM with CMOS technology and system-level optimization techniques can enhance overall memory system efficiency. This includes specialized peripheral circuits, optimized memory controllers, and hybrid memory architectures that leverage the strengths of RRAM technology. Advanced fabrication processes enable seamless integration with existing semiconductor manufacturing flows. System-level approaches consider the entire memory hierarchy, optimizing for specific application requirements such as neuromorphic computing or IoT devices where energy efficiency is paramount.Expand Specific Solutions05 Reliability and endurance enhancement techniques

Various techniques can be employed to enhance the reliability and endurance of RRAM devices, which directly impacts their operational efficiency. These include specialized forming processes, wear-leveling algorithms, and error correction methods that extend device lifetime while maintaining low power operation. Some approaches incorporate self-healing mechanisms or adaptive refresh schemes that compensate for device degradation over time. Improved reliability translates to more efficient operation by reducing the need for error correction overhead and minimizing performance degradation throughout the device lifetime.Expand Specific Solutions

Leading Companies in RRAM Testing Equipment

The RRAM efficiency testing in high-temperature systems market is currently in its growth phase, with an estimated global market size of $300-500 million and projected annual growth of 15-20%. The competitive landscape features established semiconductor giants like Samsung Electronics, Intel, and TSMC alongside specialized players such as CrossBar and TetraMem. Technical maturity varies significantly, with companies like Hitachi and Texas Instruments demonstrating advanced high-temperature testing capabilities, while academic institutions including Peking University and Institute of Microelectronics of Chinese Academy of Sciences are driving fundamental research innovations. Chinese manufacturers like SMIC and Huawei are rapidly advancing their capabilities, challenging traditional market leaders from South Korea, Japan, and the United States in this strategically important memory technology segment.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has pioneered comprehensive high-temperature testing methodologies for their RRAM technology, focusing on both device-level and system-level reliability. Their approach includes accelerated lifetime testing at temperatures ranging from 85°C to 150°C to evaluate data retention and endurance characteristics. Samsung employs specialized high-temperature probe stations with integrated thermal control systems that maintain temperature stability within ±0.1°C during electrical characterization. Their testing protocol incorporates multiple temperature set points with extended dwell times to identify temperature-dependent failure mechanisms. For system-level validation, Samsung utilizes environmental chambers that simulate real-world operating conditions while monitoring performance metrics including read/write latency, power consumption, and bit error rates. The company has developed temperature-aware ECC (Error Correction Code) algorithms that dynamically adjust correction capabilities based on operating temperature to maintain system reliability.

Strengths: Comprehensive testing infrastructure that enables both device and system-level validation; advanced temperature-aware error correction techniques that enhance reliability in fluctuating thermal environments. Weaknesses: Testing methodology requires significant time investment for statistical validation; temperature compensation circuits increase overall chip area and power consumption.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC has developed an integrated high-temperature testing platform for RRAM technologies that spans from wafer-level characterization to system-level validation. Their approach includes specialized high-temperature probe stations capable of precise temperature control (±0.5°C) from room temperature to 200°C during electrical characterization. TSMC employs a comprehensive reliability testing protocol that includes high-temperature data retention testing (up to 150°C), temperature-accelerated endurance testing, and temperature cycling between extreme conditions. Their methodology incorporates statistical analysis of large sample sizes (>1000 devices per condition) to establish reliable failure rate models and acceleration factors. TSMC has pioneered the development of specialized test structures that enable isolation and characterization of specific temperature-dependent failure mechanisms including oxygen vacancy migration, electrode material diffusion, and interfacial degradation. Their testing infrastructure includes automated systems that can simultaneously characterize multiple wafers under controlled temperature conditions, enabling efficient process optimization and qualification.

Strengths: Industry-leading wafer-level testing capabilities that enable rapid process optimization; comprehensive statistical approach that provides high-confidence reliability projections. Weaknesses: Focus primarily on manufacturing process validation rather than system-level optimization; testing methodology optimized for standard qualification rather than application-specific requirements.

Key Innovations in RRAM Thermal Characterization

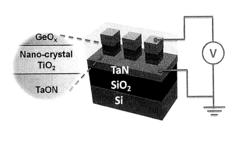

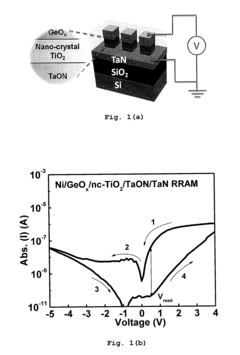

Resistive random access memory (RRAM) using stacked dielectrics and method for manufacturing the same

PatentInactiveUS8791444B2

Innovation

- A RRAM device with a metal-insulator-metal (MIM) structure using stacked dielectrics of GeOx/nc-TiO2/TaON and different work-function top and bottom electrodes, achieving ultra-low switching energy and extremely long endurance through the use of nano-crystal TiO2 and low-cost electrodes like Ni and TaN.

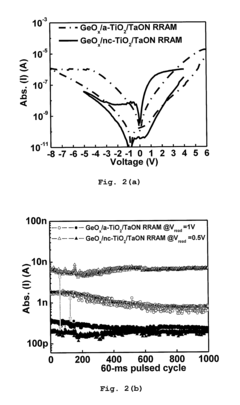

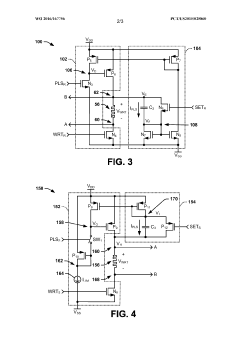

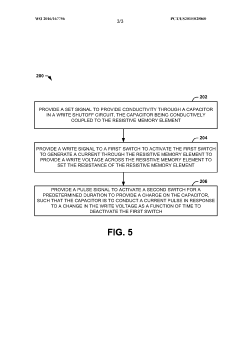

Resistive random access memory (RRAM) system

PatentWO2016167756A1

Innovation

- The RRAM system incorporates a write shutoff circuit that monitors the change in write voltage over time and immediately deactivates the write operation upon detecting a rapid change in resistance, using capacitors and switches to terminate the write stimulus efficiently.

Thermal Management Strategies for RRAM Testing

Effective thermal management is critical for reliable RRAM testing in high-temperature environments, as temperature fluctuations can significantly impact device performance and measurement accuracy. A comprehensive thermal management strategy must address both the macro-level testing environment and the micro-level heat dissipation at the device interface.

Active cooling systems represent the primary approach for maintaining stable testing conditions. Liquid cooling solutions offer superior thermal conductivity compared to air-based systems, with specialized coolants capable of maintaining temperature stability within ±0.5°C even when ambient conditions reach 150°C. Advanced implementations incorporate microfluidic channels directly into test fixtures, allowing precise temperature control at the chip level.

Thermal isolation techniques complement active cooling by preventing heat transfer between system components. Strategic placement of thermal barriers using materials with low thermal conductivity, such as ceramic composites or aerogels, can effectively compartmentalize the testing environment. This isolation is particularly important for protecting sensitive measurement equipment from heat-induced drift.

Real-time temperature monitoring forms the backbone of adaptive thermal management systems. Distributed temperature sensors with sub-millisecond response times enable dynamic adjustments to cooling parameters. Integration of infrared thermography provides non-contact temperature mapping across the device under test, revealing potential hotspots that might compromise measurement integrity.

Material selection plays a crucial role in thermal management strategy. Thermally conductive interface materials with stability at high temperatures ensure efficient heat transfer between the RRAM device and cooling systems. Recent developments in diamond-based thermal interface materials demonstrate thermal conductivity exceeding 2000 W/m·K while maintaining electrical isolation properties.

Test sequence optimization represents a software-based approach to thermal management. Intelligent scheduling algorithms can minimize thermal cycling by grouping similar temperature tests, reducing thermal stabilization time between measurements. Predictive thermal modeling enables preemptive cooling adjustments based on anticipated heat generation during specific test operations.

For extreme temperature testing scenarios, specialized environmental chambers incorporating vacuum or inert gas environments prevent oxidation and other temperature-accelerated degradation mechanisms. These chambers can maintain precise temperature control while eliminating convective heat transfer variables that might introduce measurement inconsistencies.

Active cooling systems represent the primary approach for maintaining stable testing conditions. Liquid cooling solutions offer superior thermal conductivity compared to air-based systems, with specialized coolants capable of maintaining temperature stability within ±0.5°C even when ambient conditions reach 150°C. Advanced implementations incorporate microfluidic channels directly into test fixtures, allowing precise temperature control at the chip level.

Thermal isolation techniques complement active cooling by preventing heat transfer between system components. Strategic placement of thermal barriers using materials with low thermal conductivity, such as ceramic composites or aerogels, can effectively compartmentalize the testing environment. This isolation is particularly important for protecting sensitive measurement equipment from heat-induced drift.

Real-time temperature monitoring forms the backbone of adaptive thermal management systems. Distributed temperature sensors with sub-millisecond response times enable dynamic adjustments to cooling parameters. Integration of infrared thermography provides non-contact temperature mapping across the device under test, revealing potential hotspots that might compromise measurement integrity.

Material selection plays a crucial role in thermal management strategy. Thermally conductive interface materials with stability at high temperatures ensure efficient heat transfer between the RRAM device and cooling systems. Recent developments in diamond-based thermal interface materials demonstrate thermal conductivity exceeding 2000 W/m·K while maintaining electrical isolation properties.

Test sequence optimization represents a software-based approach to thermal management. Intelligent scheduling algorithms can minimize thermal cycling by grouping similar temperature tests, reducing thermal stabilization time between measurements. Predictive thermal modeling enables preemptive cooling adjustments based on anticipated heat generation during specific test operations.

For extreme temperature testing scenarios, specialized environmental chambers incorporating vacuum or inert gas environments prevent oxidation and other temperature-accelerated degradation mechanisms. These chambers can maintain precise temperature control while eliminating convective heat transfer variables that might introduce measurement inconsistencies.

Reliability Standards for High-Temperature Memory Applications

Reliability standards for high-temperature memory applications represent a critical framework for evaluating RRAM performance in extreme thermal environments. These standards typically encompass temperature ranges from 85°C to 150°C for automotive applications, and up to 200°C for industrial, aerospace, and downhole drilling applications. The Joint Electron Device Engineering Council (JEDEC) has established JESD47 and JESD22-A108 standards specifically addressing high-temperature operational life testing and storage requirements.

For RRAM testing in high-temperature environments, reliability standards mandate specific endurance metrics, including a minimum of 10^5 write cycles at maximum operating temperature with less than 10% resistance state deviation. Data retention requirements typically specify maintaining distinguishable resistance states for at least 10 years at the maximum rated temperature, with accelerated testing methodologies employed to verify this performance within practical timeframes.

Temperature coefficient of resistance (TCR) characterization is another essential standard parameter, requiring RRAM cells to maintain distinct high and low resistance states across the entire operational temperature range. The standards typically specify maximum acceptable drift rates for resistance values, usually below 5% per 10°C temperature change to ensure reliable operation.

Signal-to-noise ratio (SNR) requirements become increasingly stringent at elevated temperatures, with standards typically mandating minimum 10dB separation between resistance states at maximum operating temperature. This ensures reliable data reading despite increased thermal noise. Additionally, standards address read disturb immunity, requiring that repeated read operations (typically >10^6) should not cause state changes at elevated temperatures.

Power consumption standards for high-temperature RRAM operation typically specify maximum current draw during read/write operations, with particular attention to leakage current which tends to increase exponentially with temperature. Maximum acceptable leakage is often defined as <100nA per cell at maximum operating temperature.

Thermal cycling reliability represents another critical standard, requiring RRAM to withstand a minimum of 1,000 cycles between temperature extremes (typically -40°C to maximum operating temperature) without significant performance degradation. Failure rate metrics are also standardized, with high-temperature applications typically requiring <100 FIT (failures in 10^9 device-hours) at maximum operating temperature.

These reliability standards are continuously evolving as RRAM technology advances and applications in extreme environments expand. Compliance with these standards is verified through rigorous testing protocols including high-temperature operating life tests, data retention bake tests, and temperature cycling stress tests.

For RRAM testing in high-temperature environments, reliability standards mandate specific endurance metrics, including a minimum of 10^5 write cycles at maximum operating temperature with less than 10% resistance state deviation. Data retention requirements typically specify maintaining distinguishable resistance states for at least 10 years at the maximum rated temperature, with accelerated testing methodologies employed to verify this performance within practical timeframes.

Temperature coefficient of resistance (TCR) characterization is another essential standard parameter, requiring RRAM cells to maintain distinct high and low resistance states across the entire operational temperature range. The standards typically specify maximum acceptable drift rates for resistance values, usually below 5% per 10°C temperature change to ensure reliable operation.

Signal-to-noise ratio (SNR) requirements become increasingly stringent at elevated temperatures, with standards typically mandating minimum 10dB separation between resistance states at maximum operating temperature. This ensures reliable data reading despite increased thermal noise. Additionally, standards address read disturb immunity, requiring that repeated read operations (typically >10^6) should not cause state changes at elevated temperatures.

Power consumption standards for high-temperature RRAM operation typically specify maximum current draw during read/write operations, with particular attention to leakage current which tends to increase exponentially with temperature. Maximum acceptable leakage is often defined as <100nA per cell at maximum operating temperature.

Thermal cycling reliability represents another critical standard, requiring RRAM to withstand a minimum of 1,000 cycles between temperature extremes (typically -40°C to maximum operating temperature) without significant performance degradation. Failure rate metrics are also standardized, with high-temperature applications typically requiring <100 FIT (failures in 10^9 device-hours) at maximum operating temperature.

These reliability standards are continuously evolving as RRAM technology advances and applications in extreme environments expand. Compliance with these standards is verified through rigorous testing protocols including high-temperature operating life tests, data retention bake tests, and temperature cycling stress tests.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!