Neuromorphic Chips in Real-time Data Processing Applications

OCT 9, 202510 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Neuromorphic Computing Evolution and Objectives

Neuromorphic computing represents a paradigm shift in computational architecture, drawing inspiration from the structure and function of biological neural systems. Since the introduction of the first neuromorphic chip by Carver Mead in the late 1980s, this field has evolved from theoretical concepts to practical implementations capable of addressing complex real-time data processing challenges. The evolution trajectory has been marked by significant milestones, including the development of silicon neurons, spike-based communication protocols, and adaptive learning mechanisms that mimic biological neural plasticity.

The fundamental objective of neuromorphic computing in real-time data processing applications is to overcome the limitations of traditional von Neumann architectures, particularly the bottleneck between memory and processing units. By integrating memory and computation within the same physical structure, neuromorphic chips aim to achieve unprecedented energy efficiency while maintaining high computational throughput for time-sensitive applications.

Recent technological advancements have accelerated the development of neuromorphic systems, with notable projects including IBM's TrueNorth, Intel's Loihi, and BrainChip's Akida. These platforms demonstrate the growing maturity of neuromorphic technology, transitioning from research curiosities to commercially viable solutions for edge computing, sensor fusion, and autonomous systems where real-time processing is critical.

The current technological trajectory suggests a convergence toward hybrid systems that combine traditional digital processing with neuromorphic elements, leveraging the strengths of each approach. This hybrid model aims to address the immediate needs of real-time applications while the pure neuromorphic paradigm continues to mature.

From a theoretical perspective, neuromorphic computing represents a fundamental rethinking of information processing, moving away from deterministic, clock-driven computation toward event-driven, probabilistic models that better reflect the uncertainty inherent in real-world data streams. This shift aligns with the growing recognition that biological systems offer valuable design principles for handling complex, unstructured data in dynamic environments.

The ultimate objective of neuromorphic chips in real-time processing applications extends beyond performance metrics to include adaptability, robustness, and contextual understanding. These systems aim to process sensory data streams with biological-like efficiency, enabling applications from advanced robotics to intelligent infrastructure that can respond to environmental changes with minimal latency and energy consumption.

As the field progresses, research objectives are increasingly focused on scaling neuromorphic architectures while maintaining their inherent advantages, developing programming paradigms suited to their unique operational characteristics, and establishing benchmarks that accurately reflect their performance in real-world applications rather than traditional computing metrics.

The fundamental objective of neuromorphic computing in real-time data processing applications is to overcome the limitations of traditional von Neumann architectures, particularly the bottleneck between memory and processing units. By integrating memory and computation within the same physical structure, neuromorphic chips aim to achieve unprecedented energy efficiency while maintaining high computational throughput for time-sensitive applications.

Recent technological advancements have accelerated the development of neuromorphic systems, with notable projects including IBM's TrueNorth, Intel's Loihi, and BrainChip's Akida. These platforms demonstrate the growing maturity of neuromorphic technology, transitioning from research curiosities to commercially viable solutions for edge computing, sensor fusion, and autonomous systems where real-time processing is critical.

The current technological trajectory suggests a convergence toward hybrid systems that combine traditional digital processing with neuromorphic elements, leveraging the strengths of each approach. This hybrid model aims to address the immediate needs of real-time applications while the pure neuromorphic paradigm continues to mature.

From a theoretical perspective, neuromorphic computing represents a fundamental rethinking of information processing, moving away from deterministic, clock-driven computation toward event-driven, probabilistic models that better reflect the uncertainty inherent in real-world data streams. This shift aligns with the growing recognition that biological systems offer valuable design principles for handling complex, unstructured data in dynamic environments.

The ultimate objective of neuromorphic chips in real-time processing applications extends beyond performance metrics to include adaptability, robustness, and contextual understanding. These systems aim to process sensory data streams with biological-like efficiency, enabling applications from advanced robotics to intelligent infrastructure that can respond to environmental changes with minimal latency and energy consumption.

As the field progresses, research objectives are increasingly focused on scaling neuromorphic architectures while maintaining their inherent advantages, developing programming paradigms suited to their unique operational characteristics, and establishing benchmarks that accurately reflect their performance in real-world applications rather than traditional computing metrics.

Real-time Data Processing Market Demands

The real-time data processing market is experiencing unprecedented growth driven by the proliferation of IoT devices, smart infrastructure, and autonomous systems. Current market analyses indicate that industries including automotive, healthcare, telecommunications, and industrial automation are increasingly demanding solutions capable of processing massive data streams with minimal latency. This shift is particularly evident in applications requiring instantaneous decision-making such as autonomous vehicles, where millisecond delays can have critical safety implications.

Neuromorphic chips are emerging as a compelling solution to these market demands due to their architecture that mimics neural networks in the human brain. Traditional computing architectures face significant bottlenecks when processing real-time data streams, particularly in power consumption and processing speed. Market research shows that organizations are seeking solutions that can reduce energy consumption by at least 70% while maintaining or improving processing capabilities.

The financial services sector represents another significant market driver, with high-frequency trading systems requiring ultra-low latency processing to maintain competitive advantage. Similarly, smart cities initiatives worldwide are creating demand for edge computing solutions that can process sensor data locally without constant cloud connectivity, reducing bandwidth requirements and improving response times.

Healthcare applications present a rapidly expanding market segment, with neuromorphic solutions enabling real-time patient monitoring systems that can detect anomalies and predict adverse events before they occur. The market for such predictive healthcare systems is projected to grow substantially as aging populations increase pressure on healthcare resources globally.

Security and surveillance systems constitute another major market segment, with advanced video analytics requiring real-time processing of multiple video streams to identify potential threats. Current solutions often struggle with the computational demands of simultaneous multi-stream processing, creating opportunities for neuromorphic technologies.

Telecommunications providers are actively seeking solutions for 5G and future network technologies that can handle the exponential increase in data traffic while minimizing latency. The ability of neuromorphic chips to process data in parallel makes them particularly suitable for network optimization and traffic management applications.

Consumer electronics manufacturers are also exploring neuromorphic solutions for next-generation devices that can offer enhanced AI capabilities while maintaining battery life, responding to consumer demand for smarter, more responsive personal devices with improved privacy through on-device processing rather than cloud-dependent solutions.

Neuromorphic chips are emerging as a compelling solution to these market demands due to their architecture that mimics neural networks in the human brain. Traditional computing architectures face significant bottlenecks when processing real-time data streams, particularly in power consumption and processing speed. Market research shows that organizations are seeking solutions that can reduce energy consumption by at least 70% while maintaining or improving processing capabilities.

The financial services sector represents another significant market driver, with high-frequency trading systems requiring ultra-low latency processing to maintain competitive advantage. Similarly, smart cities initiatives worldwide are creating demand for edge computing solutions that can process sensor data locally without constant cloud connectivity, reducing bandwidth requirements and improving response times.

Healthcare applications present a rapidly expanding market segment, with neuromorphic solutions enabling real-time patient monitoring systems that can detect anomalies and predict adverse events before they occur. The market for such predictive healthcare systems is projected to grow substantially as aging populations increase pressure on healthcare resources globally.

Security and surveillance systems constitute another major market segment, with advanced video analytics requiring real-time processing of multiple video streams to identify potential threats. Current solutions often struggle with the computational demands of simultaneous multi-stream processing, creating opportunities for neuromorphic technologies.

Telecommunications providers are actively seeking solutions for 5G and future network technologies that can handle the exponential increase in data traffic while minimizing latency. The ability of neuromorphic chips to process data in parallel makes them particularly suitable for network optimization and traffic management applications.

Consumer electronics manufacturers are also exploring neuromorphic solutions for next-generation devices that can offer enhanced AI capabilities while maintaining battery life, responding to consumer demand for smarter, more responsive personal devices with improved privacy through on-device processing rather than cloud-dependent solutions.

Neuromorphic Chip Technology Status and Barriers

Neuromorphic computing technology has witnessed significant advancements globally, yet several technical barriers continue to impede its widespread adoption in real-time data processing applications. Current neuromorphic chips demonstrate impressive capabilities in specific neural network implementations, with leading designs from IBM's TrueNorth, Intel's Loihi, and BrainChip's Akida showing promising energy efficiency metrics—often 50-100 times more efficient than traditional GPU implementations for certain workloads.

The fundamental architecture of these chips mimics biological neural systems through spiking neural networks (SNNs), enabling event-driven processing that theoretically offers substantial advantages for real-time applications. However, the practical implementation faces several critical challenges that limit commercial viability and performance optimization.

Scaling remains a primary barrier, with current neuromorphic designs struggling to maintain efficiency when scaled to handle complex, real-world data processing tasks. Most existing chips contain between 1-16 million neurons, whereas human-level cognitive tasks may require billions of interconnected neurons. The manufacturing processes for these specialized architectures also present yield challenges at larger scales.

Power consumption, while improved compared to traditional computing architectures, still presents limitations for edge deployment scenarios. Current-generation neuromorphic chips typically operate in the 50-300mW range for basic processing tasks, but power requirements increase non-linearly with network complexity, creating thermal management challenges in compact form factors.

Programming models and development tools represent another significant barrier. Unlike conventional computing platforms with mature software ecosystems, neuromorphic computing lacks standardized programming interfaces and high-level abstractions. Engineers must often work with proprietary toolchains and low-level programming constructs, increasing development complexity and limiting algorithm portability across different neuromorphic platforms.

Hardware-software co-design challenges are particularly acute, as existing machine learning frameworks and algorithms require substantial modification to leverage the unique characteristics of neuromorphic hardware. The translation of conventional deep learning models to spiking neural network implementations introduces accuracy losses and training inefficiencies that have not been fully resolved.

Reliability and fault tolerance mechanisms remain underdeveloped compared to traditional computing architectures. The inherent variability in neuromorphic circuits, while potentially beneficial for certain applications, creates challenges for applications requiring deterministic behavior and predictable performance characteristics.

Geographically, neuromorphic research and development shows concentration in North America, Europe, and increasingly in China and Japan. The United States leads in commercial development through companies like Intel and IBM, while the European Union has established significant research initiatives through the Human Brain Project. China has recently accelerated investments in neuromorphic computing through its Brain Science Project and related initiatives.

The fundamental architecture of these chips mimics biological neural systems through spiking neural networks (SNNs), enabling event-driven processing that theoretically offers substantial advantages for real-time applications. However, the practical implementation faces several critical challenges that limit commercial viability and performance optimization.

Scaling remains a primary barrier, with current neuromorphic designs struggling to maintain efficiency when scaled to handle complex, real-world data processing tasks. Most existing chips contain between 1-16 million neurons, whereas human-level cognitive tasks may require billions of interconnected neurons. The manufacturing processes for these specialized architectures also present yield challenges at larger scales.

Power consumption, while improved compared to traditional computing architectures, still presents limitations for edge deployment scenarios. Current-generation neuromorphic chips typically operate in the 50-300mW range for basic processing tasks, but power requirements increase non-linearly with network complexity, creating thermal management challenges in compact form factors.

Programming models and development tools represent another significant barrier. Unlike conventional computing platforms with mature software ecosystems, neuromorphic computing lacks standardized programming interfaces and high-level abstractions. Engineers must often work with proprietary toolchains and low-level programming constructs, increasing development complexity and limiting algorithm portability across different neuromorphic platforms.

Hardware-software co-design challenges are particularly acute, as existing machine learning frameworks and algorithms require substantial modification to leverage the unique characteristics of neuromorphic hardware. The translation of conventional deep learning models to spiking neural network implementations introduces accuracy losses and training inefficiencies that have not been fully resolved.

Reliability and fault tolerance mechanisms remain underdeveloped compared to traditional computing architectures. The inherent variability in neuromorphic circuits, while potentially beneficial for certain applications, creates challenges for applications requiring deterministic behavior and predictable performance characteristics.

Geographically, neuromorphic research and development shows concentration in North America, Europe, and increasingly in China and Japan. The United States leads in commercial development through companies like Intel and IBM, while the European Union has established significant research initiatives through the Human Brain Project. China has recently accelerated investments in neuromorphic computing through its Brain Science Project and related initiatives.

Current Neuromorphic Solutions for Real-time Processing

01 Neuromorphic Architecture and Design Principles

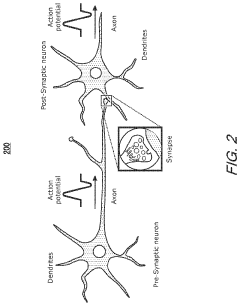

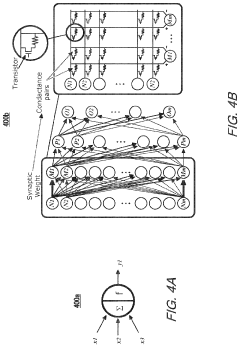

Neuromorphic chips are designed to mimic the structure and functionality of the human brain, using artificial neural networks implemented in hardware. These chips feature parallel processing capabilities, low power consumption, and the ability to learn and adapt. The architecture typically includes interconnected neurons and synapses that process information in a distributed manner, enabling efficient pattern recognition and cognitive tasks while consuming significantly less power than traditional computing architectures.- Neuromorphic architecture design and implementation: Neuromorphic chips are designed to mimic the structure and function of the human brain, using specialized architectures that integrate memory and processing. These designs typically incorporate neural networks, synaptic connections, and spike-based processing to achieve brain-like computation. The architecture often includes parallel processing elements that can perform computations simultaneously, similar to how neurons in the brain operate concurrently, enabling efficient processing of complex patterns and data.

- Materials and fabrication techniques for neuromorphic devices: Advanced materials and fabrication techniques are essential for creating efficient neuromorphic chips. These include the use of novel semiconductor materials, memristive devices, and phase-change materials that can mimic synaptic behavior. Fabrication techniques often involve integrating these materials with conventional CMOS technology to create hybrid systems that combine the benefits of traditional computing with neuromorphic capabilities. These approaches enable the creation of devices with low power consumption and high computational density.

- Energy efficiency and power optimization in neuromorphic computing: Neuromorphic chips are designed to be highly energy-efficient, consuming significantly less power than conventional computing systems while performing complex cognitive tasks. This efficiency is achieved through event-driven processing, where computations occur only when needed, similar to the brain's operation. Various techniques are employed to optimize power consumption, including low-voltage operation, sparse activation patterns, and specialized circuit designs that minimize energy use during both computation and data transfer.

- Learning algorithms and training methods for neuromorphic systems: Specialized learning algorithms and training methods are developed for neuromorphic chips to enable them to adapt and learn from data. These include spike-timing-dependent plasticity (STDP), reinforcement learning, and supervised learning approaches adapted for spiking neural networks. The algorithms are designed to work with the unique characteristics of neuromorphic hardware, such as discrete spiking events and local learning rules. These methods allow neuromorphic systems to continuously improve their performance and adapt to new tasks without extensive retraining.

- Applications and integration of neuromorphic chips in various systems: Neuromorphic chips are being integrated into various systems and applications, including computer vision, speech recognition, autonomous vehicles, robotics, and edge computing devices. These chips excel at pattern recognition, sensory processing, and decision-making tasks in real-time environments. The integration often involves interfacing neuromorphic hardware with conventional computing systems, sensors, and actuators to create complete solutions that can perceive, learn from, and interact with the physical world efficiently.

02 Memristor-Based Neuromorphic Computing

Memristors serve as key components in neuromorphic chips by emulating synaptic functions. These non-volatile memory devices can store and process information simultaneously, making them ideal for implementing neural networks in hardware. Memristor-based neuromorphic systems offer advantages in terms of energy efficiency, density, and the ability to perform in-memory computing. The variable resistance states of memristors allow them to model synaptic plasticity, enabling learning capabilities in neuromorphic hardware.Expand Specific Solutions03 Spiking Neural Networks Implementation

Spiking Neural Networks (SNNs) represent a biologically plausible approach to neuromorphic computing where information is processed using discrete spikes rather than continuous values. These networks communicate through temporal events, similar to biological neurons, allowing for efficient event-driven computation. SNN implementations in neuromorphic chips offer advantages in terms of power efficiency and temporal information processing, making them suitable for real-time applications such as computer vision, speech recognition, and autonomous systems.Expand Specific Solutions04 Neuromorphic Sensing and Vision Systems

Neuromorphic vision systems integrate sensors with neural processing to mimic the human visual system. These systems use event-based sensors that respond to changes in the visual field rather than capturing complete frames at fixed intervals. This approach significantly reduces power consumption and data processing requirements while enabling high-speed vision capabilities. Neuromorphic vision chips can perform tasks such as object recognition, motion detection, and depth perception with greater efficiency than conventional computer vision systems.Expand Specific Solutions05 Learning and Adaptation in Neuromorphic Hardware

Neuromorphic chips incorporate on-chip learning capabilities that allow them to adapt to new data and environments without requiring reprogramming. These systems implement various learning algorithms such as spike-timing-dependent plasticity (STDP), reinforcement learning, and unsupervised learning directly in hardware. The ability to learn and adapt in real-time makes neuromorphic chips particularly suitable for edge computing applications where systems must operate autonomously and adapt to changing conditions with minimal power consumption.Expand Specific Solutions

Leading Neuromorphic Chip Manufacturers and Competitors

Neuromorphic chip technology for real-time data processing is currently in an early growth phase, with the market expected to expand significantly as applications in edge computing, IoT, and AI accelerate. The global market size is projected to reach several billion dollars by 2030, driven by increasing demand for energy-efficient AI processing at the edge. Technologically, the field shows varying maturity levels across players: established semiconductor giants like Intel, IBM, and Samsung are advancing commercial neuromorphic architectures, while specialized innovators such as Syntiant, Polyn Technology, and Grai Matter Labs are developing application-specific solutions with ultra-low power consumption. Academic institutions including Tsinghua University and Chongqing University are contributing fundamental research. The competitive landscape is characterized by a balance between large corporations leveraging their manufacturing capabilities and agile startups focusing on novel architectures optimized for specific use cases.

International Business Machines Corp.

Technical Solution: IBM's TrueNorth neuromorphic architecture represents one of the most mature neuromorphic computing platforms for real-time data processing. The chip contains 1 million digital neurons and 256 million synapses organized into 4,096 neurosynaptic cores[3]. TrueNorth operates on an event-driven, parallel, and fault-tolerant paradigm that consumes merely 70mW during real-time operation. IBM has demonstrated TrueNorth's capabilities in real-time applications including multi-object detection and classification, achieving 1,200-2,600 frames per second while consuming only 25-275mW[4]. The architecture's non-von Neumann design enables simultaneous computation and memory access, eliminating the bottleneck found in traditional computing systems. IBM has further enhanced TrueNorth with programming tools like Corelet Programming Language and a simulator ecosystem that allows developers to design, test, and deploy neuromorphic applications. The company has also explored hybrid systems combining TrueNorth with traditional computing architectures to leverage the strengths of both paradigms for complex real-time data processing tasks.

Strengths: Extremely low power consumption (20mW/cm²) making it suitable for edge computing; highly scalable architecture; mature development ecosystem compared to other neuromorphic platforms; proven performance in real-world applications. Weaknesses: Limited precision for certain types of calculations; requires specialized programming approaches; higher initial implementation complexity compared to conventional computing solutions; primarily focused on inference rather than training.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has developed neuromorphic processing technology that integrates memory and processing in a single architecture, specifically designed for real-time data processing applications. Their approach utilizes resistive random-access memory (RRAM) and magnetoresistive random-access memory (MRAM) technologies to create artificial synapses and neurons[5]. Samsung's neuromorphic chips employ a unique architecture that enables in-memory computing, allowing data to be processed where it is stored rather than shuttling between separate memory and processing units. This significantly reduces energy consumption and latency, critical factors for real-time applications. The company has demonstrated their technology in applications such as real-time pattern recognition, sensor data processing, and edge AI implementations. Samsung's neuromorphic research also focuses on implementing spike-timing-dependent plasticity (STDP) learning rules directly in hardware, enabling on-chip learning capabilities[6]. Their neuromorphic vision sensors can process visual information with microsecond latency, making them suitable for applications requiring immediate response such as autonomous vehicles and industrial automation.

Strengths: Integration with Samsung's extensive semiconductor manufacturing capabilities ensures scalability; in-memory computing architecture significantly reduces power consumption; microsecond response times ideal for time-critical applications; compatibility with existing semiconductor fabrication processes. Weaknesses: Less mature ecosystem compared to some competitors; limited public information about specific performance benchmarks; still primarily in research and development phase for many applications; requires specialized expertise to fully leverage the architecture's capabilities.

Key Patents in Brain-inspired Computing Architectures

Neuromorphic chip for updating precise synaptic weight values

PatentPendingUS20230385619A1

Innovation

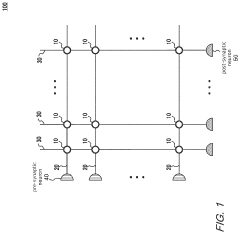

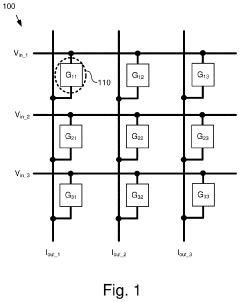

- The neuromorphic chip employs a crossbar array structure with resistive devices and switches that allow for the expression of a single synaptic weight using a variable number of resistive elements, enabling precise synaptic weight updates by dynamically connecting axon lines and aggregating resistive cells to compensate for device variability.

Hardware Accelerated Discretized Neural Network

PatentActiveUS20210334338A1

Innovation

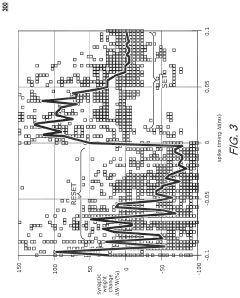

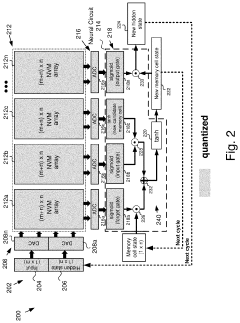

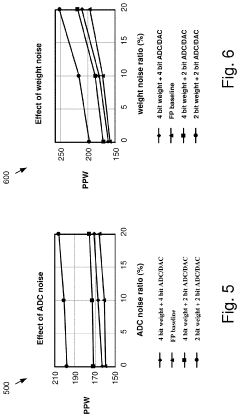

- A quantized neural network architecture that converts digital input and hidden state signals into analog form, processes them using non-volatile memory weight arrays for vector matrix multiplication, and then converts back to digital, with bit-widths reduced to 4 bits or less, utilizing DACs and ADCs to maintain performance comparable to 32-bit implementations.

Energy Efficiency Benchmarks and Optimization

Energy efficiency represents a critical benchmark for evaluating neuromorphic chips in real-time data processing applications. Current neuromorphic architectures demonstrate significant advantages over traditional von Neumann computing systems, with leading implementations achieving power efficiency improvements of 100-1000x for specific neural network workloads. Intel's Loihi 2 chip, for instance, operates at approximately 2.3 pJ per synaptic operation, while IBM's TrueNorth achieves around 26 pJ per synaptic event—orders of magnitude better than GPU implementations for similar tasks.

Standardized benchmarking methodologies have emerged to facilitate meaningful comparisons across different neuromorphic platforms. These include the Spiking Neural Network Architecture (SNNA) benchmark suite and the Neuro-Vector-Matrix (NVM) tests, which evaluate performance across various real-time processing scenarios including object detection, speech recognition, and anomaly detection in sensor data streams.

Energy optimization techniques for neuromorphic systems operate at multiple levels of abstraction. At the hardware level, innovations in memristive materials and 3D integration technologies have reduced static power consumption by up to 40% compared to earlier generations. Dynamic voltage and frequency scaling (DVFS) techniques, when applied to neuromorphic architectures, provide additional 15-30% energy savings during periods of varying computational load.

Algorithm-level optimizations focus on spike encoding schemes and network sparsity. Temporal coding approaches that leverage precise spike timing rather than rate coding have demonstrated energy reductions of 35-60% in pattern recognition tasks. Sparse connectivity implementations further reduce energy consumption by eliminating unnecessary synaptic operations, with recent implementations achieving 70-85% energy savings through pruning techniques while maintaining accuracy within 2-3% of dense networks.

System-level energy management strategies include workload-aware power gating and intelligent task scheduling. Hybrid approaches that combine neuromorphic accelerators with traditional computing elements show particular promise, with heterogeneous systems demonstrating 40-65% overall energy savings for complex real-time applications like autonomous navigation and multi-sensor fusion.

The energy efficiency frontier continues to advance through emerging technologies such as photonic neuromorphic computing, which promises theoretical energy efficiencies below 1 femtojoule per operation. Superconducting neuromorphic circuits represent another promising direction, potentially offering energy efficiencies approaching the thermodynamic limits of computation, albeit with significant practical implementation challenges related to cryogenic cooling requirements.

Standardized benchmarking methodologies have emerged to facilitate meaningful comparisons across different neuromorphic platforms. These include the Spiking Neural Network Architecture (SNNA) benchmark suite and the Neuro-Vector-Matrix (NVM) tests, which evaluate performance across various real-time processing scenarios including object detection, speech recognition, and anomaly detection in sensor data streams.

Energy optimization techniques for neuromorphic systems operate at multiple levels of abstraction. At the hardware level, innovations in memristive materials and 3D integration technologies have reduced static power consumption by up to 40% compared to earlier generations. Dynamic voltage and frequency scaling (DVFS) techniques, when applied to neuromorphic architectures, provide additional 15-30% energy savings during periods of varying computational load.

Algorithm-level optimizations focus on spike encoding schemes and network sparsity. Temporal coding approaches that leverage precise spike timing rather than rate coding have demonstrated energy reductions of 35-60% in pattern recognition tasks. Sparse connectivity implementations further reduce energy consumption by eliminating unnecessary synaptic operations, with recent implementations achieving 70-85% energy savings through pruning techniques while maintaining accuracy within 2-3% of dense networks.

System-level energy management strategies include workload-aware power gating and intelligent task scheduling. Hybrid approaches that combine neuromorphic accelerators with traditional computing elements show particular promise, with heterogeneous systems demonstrating 40-65% overall energy savings for complex real-time applications like autonomous navigation and multi-sensor fusion.

The energy efficiency frontier continues to advance through emerging technologies such as photonic neuromorphic computing, which promises theoretical energy efficiencies below 1 femtojoule per operation. Superconducting neuromorphic circuits represent another promising direction, potentially offering energy efficiencies approaching the thermodynamic limits of computation, albeit with significant practical implementation challenges related to cryogenic cooling requirements.

Integration Challenges with Conventional Computing Systems

The integration of neuromorphic chips with conventional computing systems presents significant challenges that must be addressed for successful deployment in real-time data processing applications. Traditional computing architectures based on the von Neumann model operate fundamentally differently from neuromorphic systems, creating a technological disconnect at the hardware interface level. This incompatibility manifests in differing data formats, processing paradigms, and communication protocols that complicate seamless interaction between these disparate systems.

Signal conversion between neuromorphic and conventional systems represents a primary challenge. Neuromorphic chips typically process spike-based information, while conventional systems utilize binary or floating-point representations. This necessitates specialized interface circuits that can efficiently translate between these different signal domains without introducing excessive latency or information loss, which is particularly critical for real-time applications.

Power management presents another significant hurdle. While neuromorphic chips offer energy efficiency advantages for specific workloads, hybrid systems must carefully orchestrate power distribution and management across both computing paradigms. The dynamic power requirements of neuromorphic components can create instabilities in conventional power delivery systems not designed for such fluctuating demands.

Software frameworks and programming models for hybrid neuromorphic-conventional systems remain underdeveloped. Current development environments typically cater to either neuromorphic or conventional computing paradigms separately, lacking unified abstractions that would allow developers to seamlessly leverage both architectures within a single application. This fragmentation increases development complexity and limits adoption.

Data synchronization between the asynchronous event-driven processing of neuromorphic chips and the clock-driven execution of conventional systems creates timing challenges. Real-time applications require precise coordination between these disparate processing models to maintain data coherence and temporal accuracy, often necessitating complex buffering mechanisms and timing control systems.

System-level performance optimization across hybrid architectures requires sophisticated workload partitioning strategies. Determining which computational tasks should be allocated to neuromorphic versus conventional components remains largely heuristic rather than systematic. The lack of standardized benchmarking methodologies for hybrid systems further complicates comparative performance evaluation and optimization efforts.

Standardization efforts remain in nascent stages, with few established protocols for neuromorphic-conventional system integration. This absence of standards impedes interoperability and increases integration costs, as custom solutions must be developed for each implementation scenario rather than leveraging common interfaces and methodologies.

Signal conversion between neuromorphic and conventional systems represents a primary challenge. Neuromorphic chips typically process spike-based information, while conventional systems utilize binary or floating-point representations. This necessitates specialized interface circuits that can efficiently translate between these different signal domains without introducing excessive latency or information loss, which is particularly critical for real-time applications.

Power management presents another significant hurdle. While neuromorphic chips offer energy efficiency advantages for specific workloads, hybrid systems must carefully orchestrate power distribution and management across both computing paradigms. The dynamic power requirements of neuromorphic components can create instabilities in conventional power delivery systems not designed for such fluctuating demands.

Software frameworks and programming models for hybrid neuromorphic-conventional systems remain underdeveloped. Current development environments typically cater to either neuromorphic or conventional computing paradigms separately, lacking unified abstractions that would allow developers to seamlessly leverage both architectures within a single application. This fragmentation increases development complexity and limits adoption.

Data synchronization between the asynchronous event-driven processing of neuromorphic chips and the clock-driven execution of conventional systems creates timing challenges. Real-time applications require precise coordination between these disparate processing models to maintain data coherence and temporal accuracy, often necessitating complex buffering mechanisms and timing control systems.

System-level performance optimization across hybrid architectures requires sophisticated workload partitioning strategies. Determining which computational tasks should be allocated to neuromorphic versus conventional components remains largely heuristic rather than systematic. The lack of standardized benchmarking methodologies for hybrid systems further complicates comparative performance evaluation and optimization efforts.

Standardization efforts remain in nascent stages, with few established protocols for neuromorphic-conventional system integration. This absence of standards impedes interoperability and increases integration costs, as custom solutions must be developed for each implementation scenario rather than leveraging common interfaces and methodologies.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!