Compiler And Scheduling Optimization For QEC Cycle Efficiency

SEP 2, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

QEC Compiler Evolution and Objectives

Quantum Error Correction (QEC) compilers have evolved significantly over the past decade, transitioning from theoretical constructs to practical tools essential for fault-tolerant quantum computing. The initial QEC compilers emerged around 2015, focusing primarily on implementing basic error correction codes like the Surface Code with minimal optimization. These early compilers operated under idealized assumptions about quantum hardware and lacked sophisticated scheduling capabilities.

By 2018, second-generation QEC compilers began incorporating hardware-specific constraints and introduced preliminary scheduling algorithms to manage the complex sequence of operations required for error syndrome extraction and correction. This marked a crucial shift from purely theoretical approaches to more practical implementations that acknowledged the limitations of real quantum devices.

The current generation of QEC compilers, developed since 2020, represents a significant advancement with comprehensive optimization frameworks that address the entire QEC cycle. These compilers feature multi-objective optimization capabilities, balancing error suppression effectiveness against resource utilization and time efficiency. They incorporate machine learning techniques to predict error patterns and adaptively adjust correction strategies based on hardware performance characteristics.

Looking forward, the primary objective of QEC compiler development is to achieve substantial improvements in cycle efficiency, which directly impacts the logical error rate and resource overhead of fault-tolerant quantum computers. Specific goals include reducing the latency between error detection and correction to minimize error propagation, optimizing the parallelization of syndrome extraction operations across large qubit arrays, and developing hardware-adaptive compilation strategies that can dynamically reconfigure based on observed error rates and patterns.

Another critical objective is the development of compiler techniques that can efficiently handle heterogeneous quantum architectures, where different physical qubit technologies or hybrid systems may be employed within the same quantum computer. This requires sophisticated scheduling algorithms that can account for varying gate fidelities, coherence times, and connectivity constraints across the system.

The ultimate aim of QEC compiler optimization is to reach the threshold where logical error rates decrease exponentially with modest increases in physical resources, making large-scale fault-tolerant quantum computation practically feasible. This necessitates not only algorithmic innovations but also tight integration with hardware control systems to minimize the overhead associated with classical processing during the QEC cycle.

By 2018, second-generation QEC compilers began incorporating hardware-specific constraints and introduced preliminary scheduling algorithms to manage the complex sequence of operations required for error syndrome extraction and correction. This marked a crucial shift from purely theoretical approaches to more practical implementations that acknowledged the limitations of real quantum devices.

The current generation of QEC compilers, developed since 2020, represents a significant advancement with comprehensive optimization frameworks that address the entire QEC cycle. These compilers feature multi-objective optimization capabilities, balancing error suppression effectiveness against resource utilization and time efficiency. They incorporate machine learning techniques to predict error patterns and adaptively adjust correction strategies based on hardware performance characteristics.

Looking forward, the primary objective of QEC compiler development is to achieve substantial improvements in cycle efficiency, which directly impacts the logical error rate and resource overhead of fault-tolerant quantum computers. Specific goals include reducing the latency between error detection and correction to minimize error propagation, optimizing the parallelization of syndrome extraction operations across large qubit arrays, and developing hardware-adaptive compilation strategies that can dynamically reconfigure based on observed error rates and patterns.

Another critical objective is the development of compiler techniques that can efficiently handle heterogeneous quantum architectures, where different physical qubit technologies or hybrid systems may be employed within the same quantum computer. This requires sophisticated scheduling algorithms that can account for varying gate fidelities, coherence times, and connectivity constraints across the system.

The ultimate aim of QEC compiler optimization is to reach the threshold where logical error rates decrease exponentially with modest increases in physical resources, making large-scale fault-tolerant quantum computation practically feasible. This necessitates not only algorithmic innovations but also tight integration with hardware control systems to minimize the overhead associated with classical processing during the QEC cycle.

Market Analysis for Quantum Error Correction Solutions

The quantum error correction (QEC) solutions market is experiencing significant growth as quantum computing transitions from research laboratories to practical applications. Current market estimates value the global quantum computing market at approximately $866 million in 2023, with QEC technologies representing a critical enabling segment expected to grow at a CAGR of 25-30% through 2030.

The demand for efficient QEC solutions is primarily driven by major quantum hardware developers and research institutions seeking to achieve fault-tolerant quantum computing. Organizations including IBM, Google, IonQ, and Rigetti are investing heavily in QEC technologies, with particular emphasis on compiler and scheduling optimization to improve QEC cycle efficiency.

Market segmentation reveals three primary customer categories: quantum hardware manufacturers requiring integrated QEC solutions, quantum software companies developing error mitigation platforms, and research institutions advancing theoretical frameworks. The hardware segment currently dominates market share at roughly 45%, followed by software solutions at 32% and research services at 23%.

Regional analysis shows North America leading with approximately 42% market share, followed by Europe (28%), Asia-Pacific (24%), and rest of world (6%). The United States and China are engaged in particularly aggressive investment patterns, with government funding initiatives exceeding $1.2 billion and $10 billion respectively over the next five years.

Venture capital investment in QEC-focused startups has shown remarkable growth, with funding increasing from $105 million in 2018 to over $650 million in 2023. Companies specializing in compiler optimization and scheduling algorithms for QEC have attracted particular interest, with average Series A valuations increasing by 85% since 2020.

Market forecasts suggest the QEC compiler and scheduling optimization segment will reach $1.2 billion by 2028, representing a specialized but rapidly growing niche within the broader quantum computing ecosystem. This growth is contingent upon demonstrable improvements in logical qubit stability and error threshold reductions.

Customer pain points center around the computational overhead of implementing QEC protocols, with end-users reporting that current solutions consume 70-90% of quantum processing resources. This creates substantial market opportunity for optimization technologies that can reduce this overhead while maintaining or improving error suppression capabilities.

The demand for efficient QEC solutions is primarily driven by major quantum hardware developers and research institutions seeking to achieve fault-tolerant quantum computing. Organizations including IBM, Google, IonQ, and Rigetti are investing heavily in QEC technologies, with particular emphasis on compiler and scheduling optimization to improve QEC cycle efficiency.

Market segmentation reveals three primary customer categories: quantum hardware manufacturers requiring integrated QEC solutions, quantum software companies developing error mitigation platforms, and research institutions advancing theoretical frameworks. The hardware segment currently dominates market share at roughly 45%, followed by software solutions at 32% and research services at 23%.

Regional analysis shows North America leading with approximately 42% market share, followed by Europe (28%), Asia-Pacific (24%), and rest of world (6%). The United States and China are engaged in particularly aggressive investment patterns, with government funding initiatives exceeding $1.2 billion and $10 billion respectively over the next five years.

Venture capital investment in QEC-focused startups has shown remarkable growth, with funding increasing from $105 million in 2018 to over $650 million in 2023. Companies specializing in compiler optimization and scheduling algorithms for QEC have attracted particular interest, with average Series A valuations increasing by 85% since 2020.

Market forecasts suggest the QEC compiler and scheduling optimization segment will reach $1.2 billion by 2028, representing a specialized but rapidly growing niche within the broader quantum computing ecosystem. This growth is contingent upon demonstrable improvements in logical qubit stability and error threshold reductions.

Customer pain points center around the computational overhead of implementing QEC protocols, with end-users reporting that current solutions consume 70-90% of quantum processing resources. This creates substantial market opportunity for optimization technologies that can reduce this overhead while maintaining or improving error suppression capabilities.

Current QEC Compiler Challenges and Limitations

Quantum Error Correction (QEC) compilers currently face significant challenges that limit their effectiveness in achieving optimal cycle efficiency. The primary limitation stems from the complexity of mapping abstract quantum error correction codes to physical hardware implementations. Current compilers struggle with the exponential growth in state space as qubit counts increase, making it difficult to efficiently schedule operations across large quantum systems.

Traditional compiler optimization techniques from classical computing often fail to translate effectively to the quantum domain. QEC compilers must simultaneously consider unique quantum constraints such as limited qubit connectivity, gate fidelity variations, and coherence time limitations. The scheduling algorithms in existing compilers typically employ heuristic approaches that produce sub-optimal solutions, particularly when dealing with complex error correction codes like surface codes or color codes.

Another critical limitation is the lack of standardized intermediate representations (IRs) specifically designed for QEC operations. While quantum computing has seen the development of various IRs like OpenQASM and Quil, these are not optimized for the specific patterns and requirements of error correction cycles. This forces compiler developers to create custom solutions that lack interoperability and reusability across different quantum computing platforms.

The dynamic nature of quantum errors presents another significant challenge. Current compilers typically use static scheduling approaches that cannot adapt to real-time error rates and patterns. This inflexibility results in either overly conservative error correction strategies that waste quantum resources or insufficient error mitigation that compromises computation integrity.

Hardware-software co-design remains underdeveloped in the QEC compiler space. Most compilers operate with limited knowledge of the underlying hardware characteristics, resulting in schedules that fail to leverage hardware-specific optimizations. The absence of feedback loops between hardware performance metrics and compiler decisions prevents adaptive optimization strategies.

Parallelization of QEC operations presents another substantial challenge. Current compilers struggle to effectively schedule concurrent error detection and correction operations while maintaining the logical state integrity. This limitation becomes particularly pronounced in distributed quantum computing architectures where communication latency between physical qubits adds another layer of complexity.

Finally, there is a significant gap in compiler support for fault-tolerant logical operations within QEC cycles. While physical-level operations are reasonably well-supported, compilers lack sophisticated mechanisms to optimize the implementation of logical gates that must be executed within the error correction framework, resulting in excessive overhead and reduced computational throughput.

Traditional compiler optimization techniques from classical computing often fail to translate effectively to the quantum domain. QEC compilers must simultaneously consider unique quantum constraints such as limited qubit connectivity, gate fidelity variations, and coherence time limitations. The scheduling algorithms in existing compilers typically employ heuristic approaches that produce sub-optimal solutions, particularly when dealing with complex error correction codes like surface codes or color codes.

Another critical limitation is the lack of standardized intermediate representations (IRs) specifically designed for QEC operations. While quantum computing has seen the development of various IRs like OpenQASM and Quil, these are not optimized for the specific patterns and requirements of error correction cycles. This forces compiler developers to create custom solutions that lack interoperability and reusability across different quantum computing platforms.

The dynamic nature of quantum errors presents another significant challenge. Current compilers typically use static scheduling approaches that cannot adapt to real-time error rates and patterns. This inflexibility results in either overly conservative error correction strategies that waste quantum resources or insufficient error mitigation that compromises computation integrity.

Hardware-software co-design remains underdeveloped in the QEC compiler space. Most compilers operate with limited knowledge of the underlying hardware characteristics, resulting in schedules that fail to leverage hardware-specific optimizations. The absence of feedback loops between hardware performance metrics and compiler decisions prevents adaptive optimization strategies.

Parallelization of QEC operations presents another substantial challenge. Current compilers struggle to effectively schedule concurrent error detection and correction operations while maintaining the logical state integrity. This limitation becomes particularly pronounced in distributed quantum computing architectures where communication latency between physical qubits adds another layer of complexity.

Finally, there is a significant gap in compiler support for fault-tolerant logical operations within QEC cycles. While physical-level operations are reasonably well-supported, compilers lack sophisticated mechanisms to optimize the implementation of logical gates that must be executed within the error correction framework, resulting in excessive overhead and reduced computational throughput.

State-of-the-Art QEC Cycle Optimization Approaches

01 Compiler optimization techniques for quantum error correction

Compiler optimization techniques specifically designed for quantum error correction (QEC) cycles can significantly improve the efficiency of quantum computations. These techniques include specialized instruction scheduling, code transformation, and optimization passes that understand the unique requirements of QEC operations. By optimizing the compilation process for QEC cycles, the overall execution time can be reduced while maintaining error correction capabilities.- Compiler optimization techniques for quantum error correction: Specialized compiler techniques can optimize quantum error correction (QEC) cycles by reducing the computational overhead and improving execution efficiency. These techniques include code transformation, instruction scheduling, and resource allocation specifically designed for quantum computing environments. By optimizing the compilation process, the execution time of QEC cycles can be significantly reduced while maintaining error correction capabilities.

- Scheduling algorithms for parallel QEC operations: Advanced scheduling algorithms can improve the efficiency of quantum error correction cycles by optimizing the execution order of operations and maximizing parallelism. These algorithms analyze dependencies between quantum operations and schedule them to minimize idle time and resource contention. By efficiently scheduling QEC operations across available quantum resources, the overall cycle time can be reduced and throughput increased.

- Hardware-software co-design for QEC optimization: Hardware-software co-design approaches can enhance QEC cycle efficiency by creating optimized implementations that consider both the physical constraints of quantum hardware and the logical requirements of error correction algorithms. This includes specialized instruction sets, custom hardware accelerators, and adaptive compilation techniques that adjust to specific quantum architectures. The co-design methodology enables more efficient execution of error correction protocols by matching software implementations to hardware capabilities.

- Runtime optimization and dynamic scheduling for QEC: Runtime optimization systems can dynamically adjust QEC operations based on real-time feedback from quantum systems. These approaches include adaptive scheduling, just-in-time compilation, and dynamic resource allocation that respond to changing error rates and system conditions. By continuously optimizing execution during runtime, these techniques can improve the efficiency of error correction cycles and adapt to variations in quantum hardware performance.

- Performance analysis and modeling for QEC optimization: Performance analysis frameworks and modeling techniques can identify bottlenecks and optimization opportunities in quantum error correction cycles. These approaches include simulation-based analysis, performance prediction models, and profiling tools specifically designed for quantum computing workloads. By accurately modeling the behavior of QEC operations, developers can make informed decisions about optimization strategies and evaluate their impact on overall system efficiency.

02 Scheduling algorithms for parallel execution of QEC operations

Advanced scheduling algorithms can optimize the parallel execution of quantum error correction operations across available quantum resources. These algorithms analyze dependencies between QEC operations and schedule them to maximize resource utilization while minimizing cycle time. By efficiently allocating quantum gates and operations across available qubits and quantum circuits, these scheduling techniques can significantly improve the throughput and efficiency of QEC cycles.Expand Specific Solutions03 Hardware-software co-design for QEC optimization

Hardware-software co-design approaches optimize QEC cycle efficiency by considering both the physical constraints of quantum hardware and the logical requirements of error correction codes. These techniques involve designing compiler optimizations that are aware of the underlying quantum hardware architecture, allowing for more efficient mapping of QEC operations to physical qubits. This integrated approach enables better utilization of quantum resources and reduces the overhead associated with error correction.Expand Specific Solutions04 Dynamic optimization and adaptive compilation for QEC

Dynamic optimization techniques adapt the compilation and scheduling of QEC cycles based on runtime conditions and error rates. These approaches use feedback from quantum hardware to adjust compilation strategies, allowing for real-time optimization of error correction procedures. Adaptive compilation can respond to changing noise patterns and hardware characteristics, ensuring optimal QEC performance even in variable quantum computing environments.Expand Specific Solutions05 Resource-aware compilation for efficient QEC implementation

Resource-aware compilation strategies focus on optimizing the use of limited quantum resources during QEC cycles. These techniques analyze the resource requirements of error correction codes and develop compilation strategies that minimize qubit usage, gate count, and circuit depth. By carefully managing quantum resources, these approaches can reduce the overhead of error correction while maintaining fault tolerance, leading to more efficient QEC implementations.Expand Specific Solutions

Leading Companies in Quantum Compiler Technology

Quantum Error Correction (QEC) cycle efficiency optimization is currently in an early development stage, with the market showing rapid growth potential as quantum computing advances. The global market size for QEC technologies is expanding, driven by increasing investments in quantum computing infrastructure. Technologically, companies like IBM, Google, Intel, and IonQ are leading hardware development, while Microsoft and Quantinuum focus on software-based compiler optimizations. Academic institutions including Tsinghua University and National Taiwan University contribute significant research. The field shows varying maturity levels: hardware-focused QEC remains experimental, while compiler optimization approaches are reaching practical implementation stages. The competitive landscape features collaboration between hardware manufacturers and software developers to create integrated solutions that maximize error correction efficiency while minimizing resource overhead.

International Business Machines Corp.

Technical Solution: IBM's approach to QEC cycle efficiency focuses on their comprehensive Qiskit compiler framework that optimizes quantum error correction cycles. Their solution implements a multi-level optimization strategy that includes circuit-level optimizations, pulse-level scheduling, and hardware-aware compilation techniques. IBM has developed specialized middleware that dynamically adjusts QEC protocols based on real-time error rates and qubit connectivity graphs. Their compiler performs automatic decomposition of complex QEC operations into primitive gates optimized for their quantum hardware architecture. IBM's Qiskit Runtime service incorporates just-in-time compilation techniques that reduce latency between classical and quantum processing units, critical for efficient QEC feedback loops[1]. Additionally, IBM has implemented parallel syndrome extraction techniques that minimize the overall QEC cycle time while maintaining high fidelity error detection capabilities[3].

Strengths: IBM's solution benefits from tight integration with their quantum hardware, allowing for highly optimized, hardware-specific QEC implementations. Their extensive experience with superconducting qubit systems enables precise calibration and error mitigation techniques. Weaknesses: The optimization techniques are somewhat specialized for IBM's own quantum architecture, potentially limiting portability to other quantum computing platforms. The system requires significant classical computing resources for real-time feedback and optimization.

Microsoft Technology Licensing LLC

Technical Solution: Microsoft's approach to QEC cycle efficiency centers around their Q# quantum programming language and the Quantum Development Kit (QDK), which includes specialized compiler optimizations for error correction protocols. Their solution implements a resource estimation framework that analyzes quantum circuits to determine the physical resources needed for fault-tolerant operation. Microsoft has developed a unique topological quantum error correction compiler that optimizes for surface code implementations, with particular focus on logical qubit encoding and decoding operations. Their system performs automatic scheduling of QEC operations to minimize the critical path length while respecting hardware constraints. Microsoft's compiler implements specialized optimizations for syndrome extraction circuits, reducing both the number of physical operations and the time required for error detection[2]. Additionally, they've developed techniques for dynamic circuit rewriting based on real-time error information, allowing for adaptive QEC protocols that respond to changing noise environments[4]. Their LIQUi|> simulation platform enables testing and validation of these optimizations before deployment on actual quantum hardware.

Strengths: Microsoft's solution offers excellent integration with classical computing resources through Azure Quantum, enabling powerful hybrid classical-quantum optimization approaches. Their topological QEC approach potentially offers higher error thresholds than other methods. Weaknesses: Some optimizations are theoretical and await full hardware implementation. The system has higher classical computing overhead for certain optimization techniques compared to more streamlined approaches.

Key Patents in Quantum Compiler Scheduling

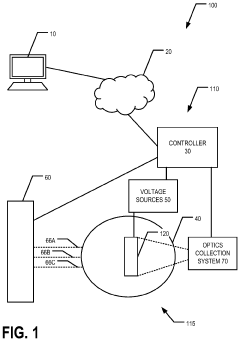

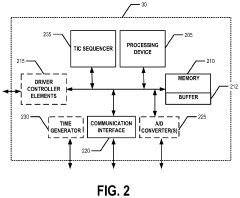

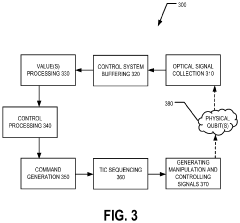

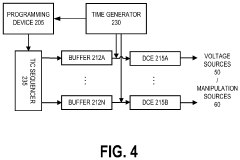

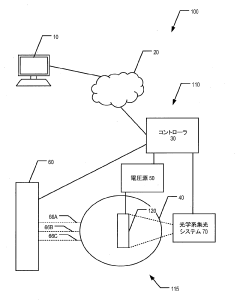

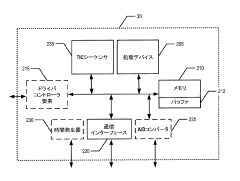

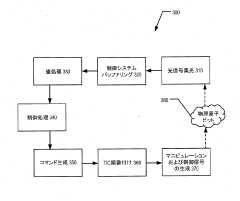

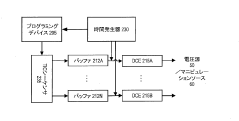

Quantum system controller configured for quantum error correction

PatentActiveUS11934920B2

Innovation

- A quantum system controller configured with a classical or semiconductor-based processing device generates commands to execute quantum error corrections in real-time or near real-time, using time-indexed execution and software-based corrections to modify quantum gates and qubits, ensuring accurate quantum error correction within the coherence time.

Quantum system controller configured to provide quantum error correction

PatentActiveJP2023029309A

Innovation

- A quantum system controller is employed to detect and correct quantum errors in real-time or near-real-time by generating time-indexed commands that execute quantum circuits, applying software-based and physical corrections to qubits within the coherence time of the qubits, using a classical and semiconductor-based processing device to manage quantum error correction.

Quantum Hardware-Software Co-design Strategies

Quantum Hardware-Software Co-design Strategies represent a critical approach to addressing the challenges in Quantum Error Correction (QEC) cycle efficiency. The integration of hardware capabilities with software optimization techniques creates synergistic solutions that neither domain could achieve independently. Current quantum computing systems face significant limitations in error correction cycle times, with hardware constraints and software inefficiencies creating bottlenecks that impede quantum advantage.

Effective co-design strategies begin with comprehensive hardware characterization, mapping the specific capabilities, constraints, and error profiles of the quantum processing units. This characterization data then informs compiler design decisions, allowing for optimization techniques tailored to the specific quantum hardware architecture. The feedback loop between hardware engineers and software developers enables continuous refinement of both components.

Compiler-aware hardware design represents one promising direction, where quantum processors are developed with features specifically intended to facilitate efficient compilation and scheduling of QEC operations. These features may include specialized instruction sets for common error correction routines, dedicated classical processing units for real-time decoding, and optimized qubit connectivity patterns that align with typical QEC code structures.

Conversely, hardware-aware compilation techniques adapt software strategies to the realities of current quantum hardware limitations. This includes techniques such as noise-adaptive compilation, where QEC operations are scheduled to minimize exposure to the most error-prone components of the system. Temporal optimization strategies leverage knowledge of coherence time variations across the quantum processor to prioritize critical operations on the most stable qubits.

Dynamic resource allocation represents another key co-design strategy, where the compiler makes real-time decisions about qubit assignment and operation scheduling based on continuously updated hardware performance metrics. This approach requires sophisticated classical control systems capable of rapid feedback and reconfiguration of quantum operations.

The development of specialized intermediate representations (IRs) that capture both hardware constraints and QEC requirements facilitates more effective optimization across the hardware-software boundary. These IRs serve as a common language between hardware and software teams, enabling coordinated development efforts and more efficient translation of high-level QEC algorithms into optimized physical operations.

Ultimately, successful hardware-software co-design requires cross-disciplinary collaboration between quantum hardware engineers, compiler developers, and QEC theorists. Organizations that establish effective communication channels and integrated development processes between these traditionally separate domains will likely achieve superior QEC cycle efficiency and accelerate progress toward fault-tolerant quantum computing.

Effective co-design strategies begin with comprehensive hardware characterization, mapping the specific capabilities, constraints, and error profiles of the quantum processing units. This characterization data then informs compiler design decisions, allowing for optimization techniques tailored to the specific quantum hardware architecture. The feedback loop between hardware engineers and software developers enables continuous refinement of both components.

Compiler-aware hardware design represents one promising direction, where quantum processors are developed with features specifically intended to facilitate efficient compilation and scheduling of QEC operations. These features may include specialized instruction sets for common error correction routines, dedicated classical processing units for real-time decoding, and optimized qubit connectivity patterns that align with typical QEC code structures.

Conversely, hardware-aware compilation techniques adapt software strategies to the realities of current quantum hardware limitations. This includes techniques such as noise-adaptive compilation, where QEC operations are scheduled to minimize exposure to the most error-prone components of the system. Temporal optimization strategies leverage knowledge of coherence time variations across the quantum processor to prioritize critical operations on the most stable qubits.

Dynamic resource allocation represents another key co-design strategy, where the compiler makes real-time decisions about qubit assignment and operation scheduling based on continuously updated hardware performance metrics. This approach requires sophisticated classical control systems capable of rapid feedback and reconfiguration of quantum operations.

The development of specialized intermediate representations (IRs) that capture both hardware constraints and QEC requirements facilitates more effective optimization across the hardware-software boundary. These IRs serve as a common language between hardware and software teams, enabling coordinated development efforts and more efficient translation of high-level QEC algorithms into optimized physical operations.

Ultimately, successful hardware-software co-design requires cross-disciplinary collaboration between quantum hardware engineers, compiler developers, and QEC theorists. Organizations that establish effective communication channels and integrated development processes between these traditionally separate domains will likely achieve superior QEC cycle efficiency and accelerate progress toward fault-tolerant quantum computing.

Benchmarking Frameworks for QEC Performance

To effectively evaluate and compare quantum error correction (QEC) implementations, robust benchmarking frameworks are essential. Current QEC benchmarking approaches can be categorized into three primary methodologies: simulation-based frameworks, hardware-specific benchmarks, and standardized metrics collections.

Simulation-based frameworks such as Stim, PyMatching, and QuaC provide controlled environments for testing QEC protocols before hardware implementation. These tools enable researchers to model noise characteristics, simulate error propagation, and evaluate the performance of different QEC codes under various conditions. The advantage of simulation lies in the ability to isolate specific variables and perform controlled experiments that would be challenging in physical quantum systems.

Hardware-specific benchmarks focus on evaluating QEC performance on actual quantum processors. Companies like IBM, Google, and Rigetti have developed custom benchmarking suites tailored to their respective quantum architectures. These benchmarks typically measure key performance indicators such as logical error rates, code distance scalability, and syndrome extraction fidelity. The IBM Quantum team, for instance, has established protocols for measuring the performance of surface codes on their superconducting qubit platforms.

Standardized metrics collections have emerged as a critical component for comparing QEC implementations across different platforms. These include logical error rate per QEC cycle, resource overhead (physical qubits required per logical qubit), cycle time efficiency, and energy consumption. The Quantum Economic Development Consortium (QED-C) has been working toward establishing industry-standard benchmarks for quantum error correction that can be universally applied.

Cross-platform benchmarking initiatives are gaining momentum, with projects like QED-C's Technical Advisory Committee developing hardware-agnostic metrics for QEC performance. These efforts aim to create fair comparison methodologies that account for the fundamental differences between quantum computing architectures while providing meaningful performance indicators.

Recent advancements include the development of application-specific benchmarks that evaluate QEC performance in the context of particular quantum algorithms. This approach recognizes that the requirements for error correction may vary significantly depending on the computational task, leading to more nuanced performance evaluations that consider both the theoretical error suppression capabilities and the practical impact on algorithm execution.

Simulation-based frameworks such as Stim, PyMatching, and QuaC provide controlled environments for testing QEC protocols before hardware implementation. These tools enable researchers to model noise characteristics, simulate error propagation, and evaluate the performance of different QEC codes under various conditions. The advantage of simulation lies in the ability to isolate specific variables and perform controlled experiments that would be challenging in physical quantum systems.

Hardware-specific benchmarks focus on evaluating QEC performance on actual quantum processors. Companies like IBM, Google, and Rigetti have developed custom benchmarking suites tailored to their respective quantum architectures. These benchmarks typically measure key performance indicators such as logical error rates, code distance scalability, and syndrome extraction fidelity. The IBM Quantum team, for instance, has established protocols for measuring the performance of surface codes on their superconducting qubit platforms.

Standardized metrics collections have emerged as a critical component for comparing QEC implementations across different platforms. These include logical error rate per QEC cycle, resource overhead (physical qubits required per logical qubit), cycle time efficiency, and energy consumption. The Quantum Economic Development Consortium (QED-C) has been working toward establishing industry-standard benchmarks for quantum error correction that can be universally applied.

Cross-platform benchmarking initiatives are gaining momentum, with projects like QED-C's Technical Advisory Committee developing hardware-agnostic metrics for QEC performance. These efforts aim to create fair comparison methodologies that account for the fundamental differences between quantum computing architectures while providing meaningful performance indicators.

Recent advancements include the development of application-specific benchmarks that evaluate QEC performance in the context of particular quantum algorithms. This approach recognizes that the requirements for error correction may vary significantly depending on the computational task, leading to more nuanced performance evaluations that consider both the theoretical error suppression capabilities and the practical impact on algorithm execution.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!