Fault-Tolerant Gate Sets For Surface Code Implementations

SEP 2, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Surface Code Fault-Tolerance Background and Objectives

Surface code quantum error correction has emerged as one of the most promising approaches for achieving fault-tolerant quantum computation. The development of surface codes traces back to Kitaev's toric code in the late 1990s, which demonstrated how topological properties could be leveraged for quantum error correction. Since then, the field has evolved significantly, with surface codes becoming the leading quantum error correction paradigm due to their high threshold and relatively simple implementation requirements.

The evolution of surface code technology has been marked by several key milestones. Initially, theoretical work established the fundamental principles and error thresholds. This was followed by experimental demonstrations of small-scale surface code implementations in various quantum computing platforms, including superconducting qubits, trapped ions, and photonic systems. Recent advancements have focused on optimizing the code structure and developing more efficient decoding algorithms.

The primary objective in surface code fault-tolerance research is to develop gate sets that maintain error protection while enabling universal quantum computation. This presents a significant challenge as the native operations of surface codes typically include only a limited set of gates, necessitating the development of techniques for implementing a universal gate set without compromising fault-tolerance properties.

Current research aims to achieve several critical technical goals. First, increasing the error threshold of surface codes to make them more resilient against physical noise. Second, reducing the resource overhead required for implementation, as current designs demand substantial qubit numbers. Third, developing efficient methods for implementing non-Clifford gates, particularly the T gate, which is essential for universal quantum computation but challenging to implement fault-tolerantly.

The field is also exploring the integration of surface codes with other quantum technologies, such as quantum communication protocols and distributed quantum computing architectures. This integration is crucial for scaling quantum computers beyond the limitations of single quantum processors.

Looking forward, the trajectory of surface code development points toward more hardware-efficient implementations, improved decoding algorithms leveraging machine learning techniques, and novel approaches to magic state distillation for implementing non-Clifford operations. The ultimate goal remains achieving practical, large-scale fault-tolerant quantum computation capable of solving problems beyond the reach of classical computers.

The evolution of surface code technology has been marked by several key milestones. Initially, theoretical work established the fundamental principles and error thresholds. This was followed by experimental demonstrations of small-scale surface code implementations in various quantum computing platforms, including superconducting qubits, trapped ions, and photonic systems. Recent advancements have focused on optimizing the code structure and developing more efficient decoding algorithms.

The primary objective in surface code fault-tolerance research is to develop gate sets that maintain error protection while enabling universal quantum computation. This presents a significant challenge as the native operations of surface codes typically include only a limited set of gates, necessitating the development of techniques for implementing a universal gate set without compromising fault-tolerance properties.

Current research aims to achieve several critical technical goals. First, increasing the error threshold of surface codes to make them more resilient against physical noise. Second, reducing the resource overhead required for implementation, as current designs demand substantial qubit numbers. Third, developing efficient methods for implementing non-Clifford gates, particularly the T gate, which is essential for universal quantum computation but challenging to implement fault-tolerantly.

The field is also exploring the integration of surface codes with other quantum technologies, such as quantum communication protocols and distributed quantum computing architectures. This integration is crucial for scaling quantum computers beyond the limitations of single quantum processors.

Looking forward, the trajectory of surface code development points toward more hardware-efficient implementations, improved decoding algorithms leveraging machine learning techniques, and novel approaches to magic state distillation for implementing non-Clifford operations. The ultimate goal remains achieving practical, large-scale fault-tolerant quantum computation capable of solving problems beyond the reach of classical computers.

Quantum Computing Market Demand Analysis

The quantum computing market is experiencing unprecedented growth, driven by significant advancements in quantum technologies and increasing recognition of their transformative potential across industries. Current market projections indicate the global quantum computing market is valued at approximately $866 million in 2023, with forecasts suggesting expansion to reach $4.6 billion by 2028, representing a compound annual growth rate (CAGR) of 39.8%.

The demand for fault-tolerant gate sets for surface code implementations specifically stems from the critical need to overcome quantum decoherence and error rates that currently limit practical quantum computing applications. Organizations across financial services, pharmaceuticals, materials science, and cybersecurity sectors are particularly invested in quantum error correction advancements, as they represent the bridge between current noisy intermediate-scale quantum (NISQ) devices and fully fault-tolerant quantum computers.

Financial institutions have emerged as early adopters, allocating substantial R&D budgets toward quantum technologies. Major banks and investment firms are exploring quantum algorithms for portfolio optimization, risk assessment, and fraud detection, with JPMorgan Chase, Goldman Sachs, and BBVA leading significant research initiatives in quantum finance applications.

The pharmaceutical and healthcare sectors demonstrate growing demand for quantum computing solutions, particularly for drug discovery and protein folding simulations. Companies like Roche, Biogen, and Pfizer have established quantum computing partnerships, recognizing that fault-tolerant quantum systems could potentially reduce drug development timelines from years to months, representing billions in potential cost savings.

Government and defense sectors globally have increased quantum computing investments substantially, with the US, China, EU, and Japan committing multi-billion dollar funding packages. The US National Quantum Initiative alone has allocated $1.2 billion over five years, while China's quantum investments reportedly exceed $10 billion.

Market analysis reveals a significant shift in enterprise attitudes toward quantum computing, with 76% of Fortune 500 companies now having dedicated quantum computing exploration teams, compared to just 35% in 2019. Furthermore, 89% of these organizations identify quantum error correction and fault tolerance as the primary technical barrier to practical implementation.

Venture capital funding in quantum computing startups focusing on error correction and fault tolerance has seen remarkable growth, with investments reaching $1.7 billion in 2022, more than double the amount from 2020. This underscores the market's recognition that fault-tolerant gate sets for surface codes represent a critical enabling technology for the quantum computing ecosystem's commercial viability.

The demand for fault-tolerant gate sets for surface code implementations specifically stems from the critical need to overcome quantum decoherence and error rates that currently limit practical quantum computing applications. Organizations across financial services, pharmaceuticals, materials science, and cybersecurity sectors are particularly invested in quantum error correction advancements, as they represent the bridge between current noisy intermediate-scale quantum (NISQ) devices and fully fault-tolerant quantum computers.

Financial institutions have emerged as early adopters, allocating substantial R&D budgets toward quantum technologies. Major banks and investment firms are exploring quantum algorithms for portfolio optimization, risk assessment, and fraud detection, with JPMorgan Chase, Goldman Sachs, and BBVA leading significant research initiatives in quantum finance applications.

The pharmaceutical and healthcare sectors demonstrate growing demand for quantum computing solutions, particularly for drug discovery and protein folding simulations. Companies like Roche, Biogen, and Pfizer have established quantum computing partnerships, recognizing that fault-tolerant quantum systems could potentially reduce drug development timelines from years to months, representing billions in potential cost savings.

Government and defense sectors globally have increased quantum computing investments substantially, with the US, China, EU, and Japan committing multi-billion dollar funding packages. The US National Quantum Initiative alone has allocated $1.2 billion over five years, while China's quantum investments reportedly exceed $10 billion.

Market analysis reveals a significant shift in enterprise attitudes toward quantum computing, with 76% of Fortune 500 companies now having dedicated quantum computing exploration teams, compared to just 35% in 2019. Furthermore, 89% of these organizations identify quantum error correction and fault tolerance as the primary technical barrier to practical implementation.

Venture capital funding in quantum computing startups focusing on error correction and fault tolerance has seen remarkable growth, with investments reaching $1.7 billion in 2022, more than double the amount from 2020. This underscores the market's recognition that fault-tolerant gate sets for surface codes represent a critical enabling technology for the quantum computing ecosystem's commercial viability.

Current State and Challenges in Fault-Tolerant Gate Sets

The current landscape of fault-tolerant gate sets for surface code implementations reveals significant progress alongside persistent challenges. Surface codes have emerged as leading candidates for quantum error correction due to their high threshold and relatively simple implementation requirements. However, the development of complete, efficient fault-tolerant gate sets remains a critical bottleneck in practical quantum computing systems.

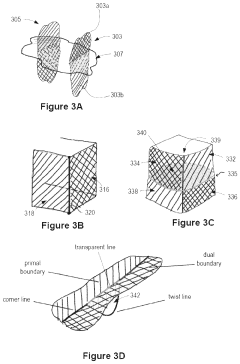

Recent advancements have established several approaches to implementing fault-tolerant gates on surface codes. The transversal implementation of certain gates (particularly the CNOT gate) has been well-established, while non-transversal gates like the T gate typically require more complex protocols such as magic state distillation. This dichotomy creates a fundamental challenge: the most straightforward implementations are limited to Clifford gates, which are insufficient for universal quantum computation.

State-of-the-art implementations now incorporate code deformation techniques, lattice surgery, and braiding of defects to expand the repertoire of fault-tolerant operations. These methods have demonstrated theoretical feasibility but face significant overhead costs in terms of physical qubits and operation time. Current estimates suggest that implementing a single non-Clifford gate may require resources equivalent to hundreds or thousands of physical qubits.

A major technical hurdle involves the trade-off between code distance and gate fidelity. As the code distance increases to protect against errors, the complexity of implementing certain gates grows substantially. This scaling challenge is particularly pronounced for non-Clifford gates, which are essential for computational universality but notoriously difficult to implement fault-tolerantly.

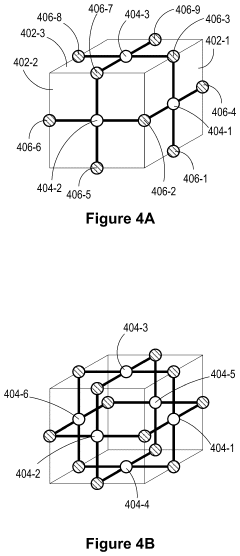

Hardware constraints further complicate implementation efforts. Surface codes typically require nearest-neighbor interactions on a 2D lattice, but many existing quantum computing platforms struggle to maintain the required connectivity and gate fidelities. The threshold for fault-tolerance in surface codes (approximately 1% error rate) remains challenging for many current hardware implementations, particularly when considering the full gate set required for universal computation.

Recent experimental demonstrations have shown promising results for small-scale surface code implementations, but scaling to the sizes needed for practical quantum advantage remains elusive. The gap between theoretical proposals and experimental capabilities continues to narrow, yet significant engineering challenges persist in realizing fully fault-tolerant gate sets.

The standardization of fault-tolerant gate sets also presents challenges for the quantum computing ecosystem. Different hardware platforms may favor different implementations, potentially leading to fragmentation in approaches and hindering the development of portable quantum software. This underscores the need for continued research into platform-agnostic methods for implementing fault-tolerant gate sets on surface codes.

Recent advancements have established several approaches to implementing fault-tolerant gates on surface codes. The transversal implementation of certain gates (particularly the CNOT gate) has been well-established, while non-transversal gates like the T gate typically require more complex protocols such as magic state distillation. This dichotomy creates a fundamental challenge: the most straightforward implementations are limited to Clifford gates, which are insufficient for universal quantum computation.

State-of-the-art implementations now incorporate code deformation techniques, lattice surgery, and braiding of defects to expand the repertoire of fault-tolerant operations. These methods have demonstrated theoretical feasibility but face significant overhead costs in terms of physical qubits and operation time. Current estimates suggest that implementing a single non-Clifford gate may require resources equivalent to hundreds or thousands of physical qubits.

A major technical hurdle involves the trade-off between code distance and gate fidelity. As the code distance increases to protect against errors, the complexity of implementing certain gates grows substantially. This scaling challenge is particularly pronounced for non-Clifford gates, which are essential for computational universality but notoriously difficult to implement fault-tolerantly.

Hardware constraints further complicate implementation efforts. Surface codes typically require nearest-neighbor interactions on a 2D lattice, but many existing quantum computing platforms struggle to maintain the required connectivity and gate fidelities. The threshold for fault-tolerance in surface codes (approximately 1% error rate) remains challenging for many current hardware implementations, particularly when considering the full gate set required for universal computation.

Recent experimental demonstrations have shown promising results for small-scale surface code implementations, but scaling to the sizes needed for practical quantum advantage remains elusive. The gap between theoretical proposals and experimental capabilities continues to narrow, yet significant engineering challenges persist in realizing fully fault-tolerant gate sets.

The standardization of fault-tolerant gate sets also presents challenges for the quantum computing ecosystem. Different hardware platforms may favor different implementations, potentially leading to fragmentation in approaches and hindering the development of portable quantum software. This underscores the need for continued research into platform-agnostic methods for implementing fault-tolerant gate sets on surface codes.

Current Fault-Tolerant Gate Set Solutions

01 Quantum Computing Fault-Tolerant Gate Sets

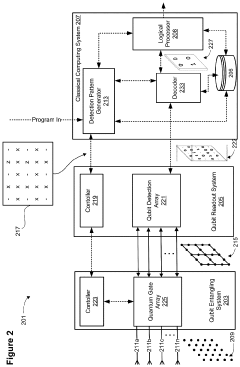

Fault-tolerant gate sets in quantum computing systems provide error correction capabilities that maintain computational integrity despite physical qubit errors. These specialized gate sets implement logical operations on encoded quantum information while preventing error propagation. The approach includes techniques for implementing universal quantum computation with topological codes and methods for constructing fault-tolerant logical gates that operate directly on encoded quantum states.- Quantum Computing Fault-Tolerant Gate Sets: Quantum computing systems implement fault-tolerant gate sets to protect quantum information from errors and decoherence. These specialized gate sets allow for error correction while maintaining computational integrity. The approach involves encoding logical qubits across multiple physical qubits and implementing operations that can detect and correct errors without corrupting the quantum information being processed. These techniques are essential for building reliable quantum computers that can perform complex calculations despite the inherent fragility of quantum states.

- Error Detection and Correction in Digital Circuits: Fault-tolerant gate sets in digital circuits employ error detection and correction mechanisms to maintain system reliability. These systems use redundant logic, parity checking, and specialized encoding schemes to identify when errors occur and apply corrective measures. By implementing these techniques at the gate level, systems can continue to function correctly even when individual components fail. This approach is particularly important in mission-critical applications where system failures could have severe consequences.

- Redundancy-Based Fault Tolerance: Redundancy-based approaches to fault tolerance involve duplicating critical components or functions to ensure system reliability. These methods include triple modular redundancy (TMR), N-modular redundancy, and standby sparing techniques. By implementing multiple identical circuits and using voting mechanisms to determine the correct output, systems can tolerate failures in individual components. This approach is widely used in safety-critical applications where continuous operation must be maintained despite potential hardware failures.

- Reconfigurable Fault-Tolerant Architectures: Reconfigurable architectures provide fault tolerance by dynamically adapting to failures. These systems can detect faulty components and reconfigure their operation to bypass damaged elements. Field-programmable gate arrays (FPGAs) and other programmable logic devices are commonly used to implement such systems, allowing for runtime adaptation to faults. This approach combines hardware redundancy with software-based fault management to create resilient systems that can maintain functionality even as components degrade over time.

- Network and Communication System Fault Tolerance: Fault-tolerant gate sets in network and communication systems ensure reliable data transmission despite hardware or connection failures. These implementations use specialized protocols, routing algorithms, and error-handling mechanisms to maintain connectivity and data integrity. By implementing redundant communication paths and intelligent error recovery mechanisms, these systems can continue to function even when individual nodes or connections fail. This approach is critical for telecommunications infrastructure, data centers, and distributed computing environments.

02 Error Detection and Correction in Digital Circuits

Fault-tolerant gate sets incorporate error detection and correction mechanisms in digital circuits to identify and mitigate faults during operation. These systems employ redundancy techniques, parity checking, and specialized logic structures to ensure reliable operation even when individual components fail. The approach includes methods for detecting transient errors, permanent faults, and implementing recovery mechanisms that maintain system functionality without interruption.Expand Specific Solutions03 Redundancy-Based Fault Tolerance Architectures

Redundancy-based fault tolerance architectures implement multiple identical processing paths with voting mechanisms to mask failures. These systems use triple modular redundancy (TMR), N-modular redundancy, or selective redundancy to ensure correct operation despite component failures. The architectures include specialized voter circuits, fault isolation mechanisms, and techniques for dynamically reconfiguring systems to bypass faulty components while maintaining operational continuity.Expand Specific Solutions04 Network and Communication System Fault Tolerance

Fault-tolerant gate sets for network and communication systems ensure continuous operation despite hardware or software failures. These systems implement redundant communication paths, automatic failover mechanisms, and error-resilient protocols. The technologies include methods for maintaining data integrity during transmission, detecting communication failures, and implementing recovery procedures that minimize service disruption in critical infrastructure applications.Expand Specific Solutions05 Reconfigurable Hardware Fault Tolerance

Reconfigurable hardware systems implement fault tolerance through dynamic circuit adaptation and self-healing capabilities. These systems can detect faults in programmable logic devices and reconfigure around damaged components. The approach includes built-in self-test mechanisms, partial reconfiguration techniques, and methods for isolating faulty regions while maintaining overall system functionality through alternative routing and resource allocation strategies.Expand Specific Solutions

Leading Quantum Computing Players and Ecosystem

The fault-tolerant gate sets for surface code implementations landscape is currently in an early growth phase, with a rapidly expanding market driven by quantum computing advancements. The technology remains in development stages, with varying maturity levels across key players. Google, IBM, and Microsoft lead research efforts, leveraging their quantum computing infrastructure and extensive patent portfolios. Specialized quantum companies like IonQ and Rigetti are making significant contributions through focused innovation. Academic institutions including Xidian University and Beihang University collaborate with industry leaders to advance theoretical frameworks. Hardware manufacturers such as Micron Technology and GLOBALFOUNDRIES provide essential components for physical implementations, creating a diverse ecosystem where cross-sector partnerships are increasingly critical for overcoming technical challenges in error correction and gate fidelity.

Google LLC

Technical Solution: Google has pioneered significant advancements in fault-tolerant gate sets for surface code implementations through their Quantum AI division. Their approach focuses on developing logical qubits using the surface code architecture with custom gate sets that minimize error propagation. Google's Sycamore processor demonstrated quantum supremacy using surface codes with specialized fault-tolerant gates that can detect and correct errors during computation. Their implementation includes a combination of transversal gates and code deformation techniques to achieve universal quantum computation. Google researchers have developed protocols for magic state distillation that work efficiently with their surface code architecture, enabling T gates and other non-Clifford operations necessary for universal quantum computing. Their recent work has focused on reducing the overhead of fault-tolerant protocols by optimizing the physical-to-logical qubit ratio and developing more efficient error correction circuits.

Strengths: Industry-leading experimental quantum hardware to test theoretical protocols; extensive research team with deep expertise in error correction; demonstrated practical implementations of surface codes. Weaknesses: Their approach requires significant physical qubit overhead; still facing challenges in scaling logical qubit operations to practical problem sizes.

Microsoft Technology Licensing LLC

Technical Solution: Microsoft has developed a comprehensive approach to fault-tolerant gate sets through their topological quantum computing research program. Their primary focus has been on developing surface code implementations that support Majorana-based qubits, which inherently provide some protection against local errors. Microsoft's fault-tolerant gate set design incorporates lattice surgery techniques for logical operations between surface code patches. Their research has produced novel protocols for implementing non-Clifford gates with reduced overhead compared to traditional approaches. Microsoft has pioneered the concept of "floquet codes" that dynamically evolve the surface code structure to implement certain logical operations with higher fidelity. Their quantum development kit includes simulation tools specifically designed to model and optimize fault-tolerant gate operations on surface codes, allowing researchers to test error correction protocols before hardware implementation.

Strengths: Strong theoretical foundation in topological quantum computing; innovative approach to fault-tolerance through topological protection; extensive software tools for simulation and optimization. Weaknesses: Their hardware implementation has progressed more slowly than competitors; heavy reliance on theoretical advances that await full experimental validation.

Key Innovations in Surface Code Error Correction

Methods and devices for fault tolerant quantum gates

PatentActiveUS11940834B1

Innovation

- A method involving a lattice structure of entangled qubits with a defect qubit entangled with both edge and face qubits, allowing for the implementation of Hadamard and phase gates through quantum measurements, eliminating the need for state injection and reducing resource requirements.

Quantum error-correction in microwave integrated quantum circuits

PatentActiveUS11977113B1

Innovation

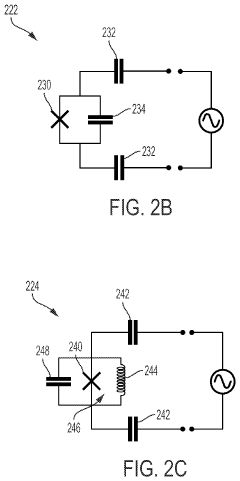

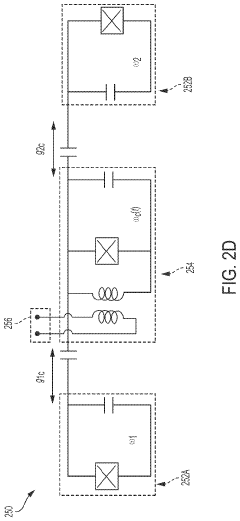

- Implementing topological quantum error-correcting codes using parity measurements between qubits arranged in lattices, such as surface codes and color codes, where ancilla qubits are used to detect errors with low overhead by applying two-qubit gates in superconducting devices like transmon and fluxonium devices, which are already present in the architecture.

Quantum Error Correction Benchmarking Methods

Quantum Error Correction Benchmarking Methods have become essential tools for evaluating the performance of fault-tolerant gate sets in surface code implementations. These methods provide standardized frameworks to assess how effectively quantum error correction protocols mitigate errors and maintain quantum information integrity.

The most widely adopted benchmarking approach is Randomized Benchmarking (RB), which measures the average error rate of quantum gates by applying random sequences of increasing length. For surface codes specifically, this technique has been adapted to evaluate logical operations on encoded qubits. Recent advancements include Interleaved Randomized Benchmarking, which isolates the performance of individual fault-tolerant gates within the surface code architecture.

Quantum Process Tomography represents another critical benchmarking method, providing complete characterization of quantum operations. However, its application to surface codes presents significant challenges due to the exponential scaling with system size. Researchers have developed compressed sensing techniques to make this approach more tractable for larger surface code implementations.

Error threshold estimation serves as a fundamental benchmark for surface code implementations. By systematically increasing noise levels and observing when logical error rates exceed physical error rates, researchers can determine the critical threshold below which quantum error correction provides an advantage. For fault-tolerant gate sets, these thresholds typically range between 0.5% and 1% depending on the specific implementation.

Logical error rate scaling provides insights into how error correction performance improves with increasing code distance. Benchmark results consistently demonstrate that surface codes with well-designed fault-tolerant gate sets achieve the theoretical exponential suppression of errors with linear increases in qubit overhead.

Cycle benchmarking has emerged as a specialized technique for surface codes, measuring error rates per complete error correction cycle. This approach is particularly valuable for evaluating the performance of fault-tolerant gate sets under realistic operating conditions, including measurement and feedback operations.

Diamond distance and fidelity metrics offer quantitative measures of how closely implemented operations match their ideal counterparts. These metrics have been standardized across the quantum computing industry to enable meaningful comparisons between different fault-tolerant gate implementations on surface codes.

The most widely adopted benchmarking approach is Randomized Benchmarking (RB), which measures the average error rate of quantum gates by applying random sequences of increasing length. For surface codes specifically, this technique has been adapted to evaluate logical operations on encoded qubits. Recent advancements include Interleaved Randomized Benchmarking, which isolates the performance of individual fault-tolerant gates within the surface code architecture.

Quantum Process Tomography represents another critical benchmarking method, providing complete characterization of quantum operations. However, its application to surface codes presents significant challenges due to the exponential scaling with system size. Researchers have developed compressed sensing techniques to make this approach more tractable for larger surface code implementations.

Error threshold estimation serves as a fundamental benchmark for surface code implementations. By systematically increasing noise levels and observing when logical error rates exceed physical error rates, researchers can determine the critical threshold below which quantum error correction provides an advantage. For fault-tolerant gate sets, these thresholds typically range between 0.5% and 1% depending on the specific implementation.

Logical error rate scaling provides insights into how error correction performance improves with increasing code distance. Benchmark results consistently demonstrate that surface codes with well-designed fault-tolerant gate sets achieve the theoretical exponential suppression of errors with linear increases in qubit overhead.

Cycle benchmarking has emerged as a specialized technique for surface codes, measuring error rates per complete error correction cycle. This approach is particularly valuable for evaluating the performance of fault-tolerant gate sets under realistic operating conditions, including measurement and feedback operations.

Diamond distance and fidelity metrics offer quantitative measures of how closely implemented operations match their ideal counterparts. These metrics have been standardized across the quantum computing industry to enable meaningful comparisons between different fault-tolerant gate implementations on surface codes.

Scalability Considerations for Surface Code Architectures

Surface code architectures face significant scalability challenges that must be addressed for practical quantum computing implementations. The physical qubit overhead required for surface codes increases quadratically with the desired logical error rate reduction, necessitating careful resource optimization. For large-scale quantum algorithms, millions of physical qubits may be needed to implement just hundreds of logical qubits with sufficient error protection.

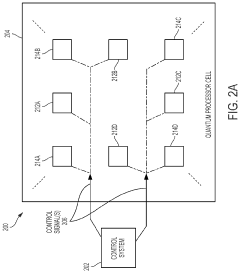

Connectivity requirements present another major scalability concern. Surface codes demand nearest-neighbor interactions between physical qubits, which constrains physical implementation options. As systems scale up, maintaining this connectivity across larger qubit arrays becomes increasingly difficult, particularly for modular quantum computing approaches where inter-module communication creates potential bottlenecks.

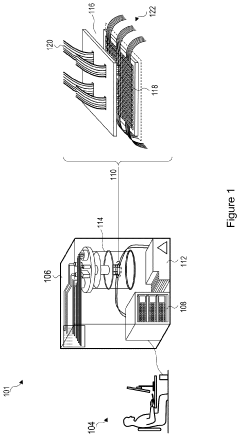

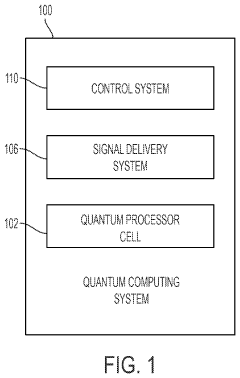

The classical control electronics required for surface code operation also pose scalability limitations. Each physical qubit requires dedicated control and measurement channels, leading to wiring complexity that grows linearly with qubit count. For large-scale implementations, this necessitates advanced multiplexing techniques and cryogenic electronics to manage the increasing number of control lines without overwhelming thermal budgets.

Fault-tolerant gate sets must be optimized for scalability by minimizing the resources required per logical operation. Transversal gates, which naturally preserve the code structure, offer the most efficient implementation path. However, no quantum error correction code permits a universal transversal gate set, requiring more resource-intensive techniques like magic state distillation for universal computation.

Time complexity represents another critical dimension of scalability. The surface code's cycle time for error syndrome extraction directly impacts computational throughput. As systems scale, maintaining synchronized operation across larger qubit arrays becomes challenging, potentially leading to increased cycle times that could offset the advantages of having more qubits.

Decoding complexity grows with code distance, requiring more sophisticated classical processing to handle error correction in real-time. Parallel decoding algorithms and specialized hardware accelerators will be essential for maintaining acceptable latency as surface codes scale to practical sizes for fault-tolerant quantum computing applications.

Connectivity requirements present another major scalability concern. Surface codes demand nearest-neighbor interactions between physical qubits, which constrains physical implementation options. As systems scale up, maintaining this connectivity across larger qubit arrays becomes increasingly difficult, particularly for modular quantum computing approaches where inter-module communication creates potential bottlenecks.

The classical control electronics required for surface code operation also pose scalability limitations. Each physical qubit requires dedicated control and measurement channels, leading to wiring complexity that grows linearly with qubit count. For large-scale implementations, this necessitates advanced multiplexing techniques and cryogenic electronics to manage the increasing number of control lines without overwhelming thermal budgets.

Fault-tolerant gate sets must be optimized for scalability by minimizing the resources required per logical operation. Transversal gates, which naturally preserve the code structure, offer the most efficient implementation path. However, no quantum error correction code permits a universal transversal gate set, requiring more resource-intensive techniques like magic state distillation for universal computation.

Time complexity represents another critical dimension of scalability. The surface code's cycle time for error syndrome extraction directly impacts computational throughput. As systems scale, maintaining synchronized operation across larger qubit arrays becomes challenging, potentially leading to increased cycle times that could offset the advantages of having more qubits.

Decoding complexity grows with code distance, requiring more sophisticated classical processing to handle error correction in real-time. Parallel decoding algorithms and specialized hardware accelerators will be essential for maintaining acceptable latency as surface codes scale to practical sizes for fault-tolerant quantum computing applications.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!