Evaluating RRAM Memory Density for Smart City Solutions

SEP 10, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

RRAM Technology Evolution and Objectives

Resistive Random Access Memory (RRAM) has emerged as a promising non-volatile memory technology over the past two decades, evolving from theoretical concepts to practical implementations. The technology leverages the resistance switching phenomenon in certain metal oxides and has progressed through several generations of material science and fabrication techniques. Initially developed as a potential replacement for flash memory, RRAM has expanded its application scope to include neuromorphic computing, edge AI, and increasingly, smart city infrastructure.

The evolution of RRAM began with simple metal-insulator-metal structures in the early 2000s, progressing to more sophisticated multi-layer designs that enhanced reliability and endurance. A significant milestone occurred around 2010 when researchers demonstrated practical devices with acceptable switching characteristics and retention times. By 2015, the technology had advanced to include various material compositions, including hafnium oxide, tantalum oxide, and titanium oxide-based structures, each offering specific advantages in terms of switching speed, power consumption, or retention.

Recent developments have focused on scaling RRAM to higher densities while maintaining performance parameters. The transition from planar to 3D architectures represents a critical evolutionary step, enabling dramatic increases in memory density without proportional increases in chip area. Cross-point arrays and selector device integration have further enhanced the commercial viability of high-density RRAM solutions.

For smart city applications, the primary objective of RRAM development is achieving unprecedented memory density while maintaining low power consumption and high reliability under variable environmental conditions. Smart cities generate massive amounts of data from numerous sensors, requiring storage solutions that can handle high-volume, high-velocity data streams at the edge. RRAM aims to provide memory densities exceeding 10 Tb/in² while consuming less than 10 pJ per bit operation.

Another critical objective is enhancing RRAM's radiation hardness and temperature stability, as smart city infrastructure must operate reliably in diverse and often harsh environments. Current research targets RRAM configurations that maintain data integrity across temperature ranges from -40°C to +85°C and withstand radiation levels typical in urban environments.

The technology roadmap also prioritizes integration capabilities with existing CMOS processes to facilitate cost-effective manufacturing and deployment. As smart cities evolve toward more distributed intelligence architectures, RRAM must support in-memory computing paradigms that reduce data movement and enable real-time analytics at the edge, with latency targets below 100 nanoseconds for read operations.

The evolution of RRAM began with simple metal-insulator-metal structures in the early 2000s, progressing to more sophisticated multi-layer designs that enhanced reliability and endurance. A significant milestone occurred around 2010 when researchers demonstrated practical devices with acceptable switching characteristics and retention times. By 2015, the technology had advanced to include various material compositions, including hafnium oxide, tantalum oxide, and titanium oxide-based structures, each offering specific advantages in terms of switching speed, power consumption, or retention.

Recent developments have focused on scaling RRAM to higher densities while maintaining performance parameters. The transition from planar to 3D architectures represents a critical evolutionary step, enabling dramatic increases in memory density without proportional increases in chip area. Cross-point arrays and selector device integration have further enhanced the commercial viability of high-density RRAM solutions.

For smart city applications, the primary objective of RRAM development is achieving unprecedented memory density while maintaining low power consumption and high reliability under variable environmental conditions. Smart cities generate massive amounts of data from numerous sensors, requiring storage solutions that can handle high-volume, high-velocity data streams at the edge. RRAM aims to provide memory densities exceeding 10 Tb/in² while consuming less than 10 pJ per bit operation.

Another critical objective is enhancing RRAM's radiation hardness and temperature stability, as smart city infrastructure must operate reliably in diverse and often harsh environments. Current research targets RRAM configurations that maintain data integrity across temperature ranges from -40°C to +85°C and withstand radiation levels typical in urban environments.

The technology roadmap also prioritizes integration capabilities with existing CMOS processes to facilitate cost-effective manufacturing and deployment. As smart cities evolve toward more distributed intelligence architectures, RRAM must support in-memory computing paradigms that reduce data movement and enable real-time analytics at the edge, with latency targets below 100 nanoseconds for read operations.

Smart City Applications Market Analysis

The smart city applications market is experiencing unprecedented growth, driven by increasing urbanization and the need for more efficient city management systems. Current market valuations place the global smart city technology sector at approximately $648 billion in 2023, with projections indicating growth to reach $1.2 trillion by 2030, representing a compound annual growth rate (CAGR) of 10.6%. This expansion is particularly significant in regions with rapid urban development, including East Asia, North America, and Western Europe.

Memory solutions, especially high-density storage technologies like RRAM, are becoming critical components in this ecosystem. The market segment specifically for memory solutions in smart city applications was valued at $42 billion in 2022 and is expected to grow at a CAGR of 14.3% through 2028, outpacing the overall smart city market growth.

Key demand drivers for RRAM in smart city applications include the exponential increase in data generation from IoT sensors, which is estimated to reach 79.4 zettabytes by 2025. Smart city initiatives typically deploy between 10,000 to 40,000 sensors per square kilometer in dense urban environments, creating substantial requirements for efficient data storage and processing capabilities.

Market segmentation reveals that transportation and mobility applications currently represent the largest share (28%) of memory solution deployments in smart cities, followed by energy management (22%), public safety (18%), and infrastructure monitoring (15%). These applications require memory solutions that can operate reliably in diverse environmental conditions while maintaining high data integrity.

Regional analysis shows that Asia-Pacific dominates the market with 42% share, followed by North America (27%) and Europe (21%). China alone accounts for 24% of global smart city memory solution deployments, with significant investments in over 500 smart city initiatives nationwide.

Consumer adoption patterns indicate increasing acceptance of smart city technologies, with 67% of urban residents expressing willingness to share data for improved city services. This trend is particularly strong among younger demographics, with 78% of residents under 35 showing positive attitudes toward smart city technologies.

Market challenges include concerns about data privacy (cited by 72% of potential users), system interoperability issues, and the high initial implementation costs. Despite these challenges, the market demonstrates strong growth potential, particularly for memory solutions that can address the specific requirements of edge computing applications in urban environments, where RRAM's characteristics offer significant advantages over conventional memory technologies.

Memory solutions, especially high-density storage technologies like RRAM, are becoming critical components in this ecosystem. The market segment specifically for memory solutions in smart city applications was valued at $42 billion in 2022 and is expected to grow at a CAGR of 14.3% through 2028, outpacing the overall smart city market growth.

Key demand drivers for RRAM in smart city applications include the exponential increase in data generation from IoT sensors, which is estimated to reach 79.4 zettabytes by 2025. Smart city initiatives typically deploy between 10,000 to 40,000 sensors per square kilometer in dense urban environments, creating substantial requirements for efficient data storage and processing capabilities.

Market segmentation reveals that transportation and mobility applications currently represent the largest share (28%) of memory solution deployments in smart cities, followed by energy management (22%), public safety (18%), and infrastructure monitoring (15%). These applications require memory solutions that can operate reliably in diverse environmental conditions while maintaining high data integrity.

Regional analysis shows that Asia-Pacific dominates the market with 42% share, followed by North America (27%) and Europe (21%). China alone accounts for 24% of global smart city memory solution deployments, with significant investments in over 500 smart city initiatives nationwide.

Consumer adoption patterns indicate increasing acceptance of smart city technologies, with 67% of urban residents expressing willingness to share data for improved city services. This trend is particularly strong among younger demographics, with 78% of residents under 35 showing positive attitudes toward smart city technologies.

Market challenges include concerns about data privacy (cited by 72% of potential users), system interoperability issues, and the high initial implementation costs. Despite these challenges, the market demonstrates strong growth potential, particularly for memory solutions that can address the specific requirements of edge computing applications in urban environments, where RRAM's characteristics offer significant advantages over conventional memory technologies.

RRAM Density Status and Technical Barriers

RRAM technology has demonstrated significant advancements in memory density over the past decade, yet still faces substantial technical barriers that limit its widespread adoption in smart city applications. Current commercial RRAM solutions offer densities ranging from 1-8 Gb per die, which falls short compared to NAND flash memory that has reached terabit-level densities. This density gap represents one of the primary technical challenges for RRAM implementation in data-intensive smart city environments.

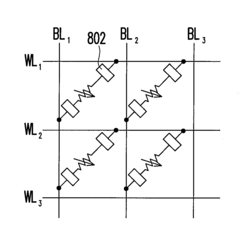

The fundamental physical limitations affecting RRAM density include sneak path currents in crossbar arrays, which necessitate selector devices that consume additional chip area. While one-selector-one-resistor (1S1R) and one-transistor-one-resistor (1T1R) architectures have been developed to address this issue, they introduce complexity and reduce effective density. The selector devices often require more space than the memory element itself, creating a significant barrier to ultra-high density integration.

Material uniformity presents another critical challenge, as variations in switching layer composition lead to inconsistent resistance states across large arrays. This variability increases with scaling, resulting in higher bit error rates that necessitate more sophisticated error correction codes, further reducing effective storage capacity. Research indicates that cell-to-cell variability increases exponentially below the 20nm node, creating a practical scaling limit with current materials.

3D integration approaches, while promising for density improvement, introduce additional fabrication challenges. Current 3D RRAM structures typically achieve only 4-8 layers compared to 3D NAND's 128+ layers, due to thermal budget constraints during fabrication and increased complexity in addressing schemes. The vertical integration process often degrades material interfaces, leading to reliability concerns in multi-layer structures.

Power consumption during write operations represents another significant barrier, particularly for edge computing applications in smart city infrastructure where energy efficiency is paramount. High current densities required for reliable switching operations limit the minimum cell size, as smaller cells cannot sustain the necessary current without structural damage.

Endurance limitations also impact effective density, as wear-leveling algorithms must be implemented to distribute write operations, requiring additional overhead memory. Current RRAM technologies typically demonstrate 10^6-10^9 write cycles, which is insufficient for write-intensive smart city applications like real-time sensor data processing without sophisticated management techniques.

Addressing these technical barriers requires interdisciplinary approaches combining materials science, device physics, and circuit design innovations. Recent research directions include exploration of novel switching materials with improved uniformity, selector-less architectures, and advanced 3D integration techniques specifically optimized for RRAM characteristics.

The fundamental physical limitations affecting RRAM density include sneak path currents in crossbar arrays, which necessitate selector devices that consume additional chip area. While one-selector-one-resistor (1S1R) and one-transistor-one-resistor (1T1R) architectures have been developed to address this issue, they introduce complexity and reduce effective density. The selector devices often require more space than the memory element itself, creating a significant barrier to ultra-high density integration.

Material uniformity presents another critical challenge, as variations in switching layer composition lead to inconsistent resistance states across large arrays. This variability increases with scaling, resulting in higher bit error rates that necessitate more sophisticated error correction codes, further reducing effective storage capacity. Research indicates that cell-to-cell variability increases exponentially below the 20nm node, creating a practical scaling limit with current materials.

3D integration approaches, while promising for density improvement, introduce additional fabrication challenges. Current 3D RRAM structures typically achieve only 4-8 layers compared to 3D NAND's 128+ layers, due to thermal budget constraints during fabrication and increased complexity in addressing schemes. The vertical integration process often degrades material interfaces, leading to reliability concerns in multi-layer structures.

Power consumption during write operations represents another significant barrier, particularly for edge computing applications in smart city infrastructure where energy efficiency is paramount. High current densities required for reliable switching operations limit the minimum cell size, as smaller cells cannot sustain the necessary current without structural damage.

Endurance limitations also impact effective density, as wear-leveling algorithms must be implemented to distribute write operations, requiring additional overhead memory. Current RRAM technologies typically demonstrate 10^6-10^9 write cycles, which is insufficient for write-intensive smart city applications like real-time sensor data processing without sophisticated management techniques.

Addressing these technical barriers requires interdisciplinary approaches combining materials science, device physics, and circuit design innovations. Recent research directions include exploration of novel switching materials with improved uniformity, selector-less architectures, and advanced 3D integration techniques specifically optimized for RRAM characteristics.

Current RRAM Density Enhancement Approaches

01 3D RRAM architecture for high density memory

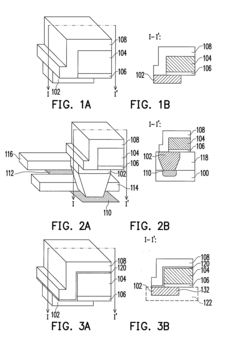

Three-dimensional (3D) architectures are employed in RRAM designs to significantly increase memory density. These structures include vertical stacking of memory cells, cross-point arrays, and multi-layer configurations that maximize the number of memory cells per unit area. 3D RRAM architectures enable higher storage capacity while maintaining a small footprint, making them suitable for applications requiring high-density non-volatile memory solutions.- 3D RRAM architecture for increased memory density: Three-dimensional RRAM architectures enable significant increases in memory density by stacking memory cells vertically. This approach allows for more memory cells to be integrated within the same footprint compared to traditional 2D structures. Various 3D integration techniques include vertical RRAM arrays, cross-point structures, and multi-layer stacking, which can achieve higher bit densities while maintaining or improving performance characteristics.

- Novel materials and interfaces for enhanced RRAM density: Advanced materials and engineered interfaces are critical for improving RRAM memory density. Utilizing specialized resistive switching materials such as metal oxides, chalcogenides, and two-dimensional materials enables smaller cell sizes and more reliable switching behavior. Engineered interfaces between the switching layer and electrodes can reduce variability and improve retention characteristics, allowing for more compact memory cells that maintain performance at smaller dimensions.

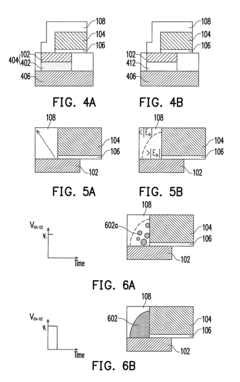

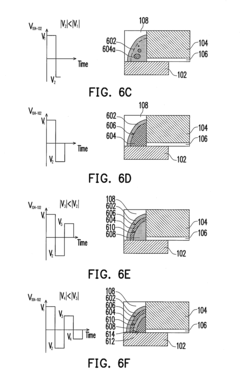

- Multi-level cell technology for RRAM density improvement: Multi-level cell (MLC) technology significantly increases RRAM memory density by storing multiple bits of information in a single memory cell. By precisely controlling the resistance states of RRAM cells, multiple distinct resistance levels can be achieved, effectively multiplying the storage capacity without increasing the physical cell count. This approach requires sophisticated programming algorithms and sensing circuits to reliably distinguish between the different resistance states.

- Selector devices and crossbar arrays for high-density RRAM: Selector devices integrated with RRAM cells enable high-density crossbar array architectures by mitigating sneak path currents. These selector components, such as diodes, transistors, or threshold switching materials, allow for densely packed memory arrays without interference between adjacent cells. Crossbar architectures maximize memory density by placing memory elements at each intersection of perpendicular conductive lines, achieving the theoretical minimum cell area of 4F² (where F is the minimum feature size).

- Scaling and fabrication techniques for ultra-high density RRAM: Advanced scaling and fabrication techniques enable ultra-high density RRAM implementations. These include sub-lithographic patterning methods, atomic layer deposition, self-aligned processes, and innovative cell structures that minimize feature sizes beyond conventional lithography limits. Complementary techniques such as edge-defined fabrication and sidewall spacer approaches allow for nanoscale memory elements that maximize density while maintaining manufacturability and yield at scale.

02 Novel materials and structures for enhanced RRAM density

Advanced materials and innovative structural designs are utilized to improve RRAM memory density. These include specialized resistive switching materials, oxide-based memristors, and nanoscale filament structures that enable smaller cell sizes. By incorporating materials with superior switching characteristics and designing optimized cell structures, RRAM devices can achieve higher density while maintaining reliable operation and performance.Expand Specific Solutions03 Multi-level cell technology for RRAM density improvement

Multi-level cell (MLC) technology allows RRAM devices to store multiple bits of information in a single memory cell by utilizing different resistance states. This approach significantly increases memory density without expanding the physical footprint of the device. MLC RRAM implementations require precise control of resistance levels and sophisticated sensing circuits to reliably distinguish between multiple states, but offer substantial density advantages over conventional binary storage approaches.Expand Specific Solutions04 Integration and fabrication techniques for high-density RRAM

Advanced integration and fabrication techniques are crucial for achieving high-density RRAM. These include back-end-of-line (BEOL) integration, CMOS-compatible processes, and innovative patterning methods that enable smaller feature sizes. Techniques such as atomic layer deposition, self-aligned fabrication, and advanced lithography allow for the creation of densely packed RRAM arrays with minimal cell-to-cell variation, maximizing memory density while ensuring manufacturability.Expand Specific Solutions05 Selector devices and array architectures for high-density RRAM

Selector devices and optimized array architectures are implemented to address sneak path issues in high-density RRAM arrays. These include transistors, diodes, and threshold switching selectors that enable reliable cell selection in dense crossbar arrays. Advanced array architectures with optimized wordline/bitline configurations and hierarchical addressing schemes further enhance memory density while maintaining access speed and reducing power consumption in large RRAM arrays.Expand Specific Solutions

Leading RRAM Manufacturers and Competitors

The RRAM memory density market for smart city solutions is in its growth phase, with increasing adoption driven by IoT applications requiring high-density, low-power memory solutions. Major semiconductor players like Micron Technology, Samsung Electronics, and TSMC are advancing RRAM technology commercialization, while research institutions such as IMEC-CAS and Zhejiang University contribute significant innovations. The market is characterized by a competitive landscape where established memory manufacturers (Intel, Qualcomm) compete with specialized RRAM developers like Hefei Reliance Memory. Technical challenges in scaling, endurance, and integration are being addressed through collaborative efforts between industry and academia, with companies like Huawei and IBM focusing on system-level integration for smart city applications.

Micron Technology, Inc.

Technical Solution: Micron has developed advanced RRAM (Resistive Random Access Memory) technology specifically optimized for smart city applications. Their 3D crossbar architecture achieves memory densities exceeding 10 Gb/cm², significantly higher than conventional memory solutions. Micron's RRAM implementation features multi-level cell capabilities (storing multiple bits per cell) that further increases effective density while maintaining reliability. Their smart city solution incorporates specialized memory controllers that optimize power consumption during idle states, critical for IoT sensors and edge computing devices deployed throughout urban environments. Micron has also implemented adaptive refresh algorithms that extend data retention periods based on environmental conditions, reducing power requirements for long-term data storage in distributed smart city infrastructure.

Strengths: Superior density-to-power ratio optimized for battery-powered smart city devices; excellent data retention characteristics in variable urban environmental conditions. Weaknesses: Higher initial production costs compared to traditional memory technologies; requires specialized interface protocols that may limit compatibility with some existing systems.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC has developed advanced RRAM manufacturing processes specifically optimized for smart city applications, achieving memory densities exceeding 15 Gb/cm² through their innovative 7nm process technology. Their approach incorporates hafnium oxide-based resistive switching materials that provide excellent retention characteristics while maintaining low switching voltages, critical for energy-constrained smart city deployments. TSMC's RRAM technology features a unique selector device architecture that minimizes sneak path currents, allowing for higher array densities without performance degradation. For smart city applications, they've implemented specialized peripheral circuitry that enables ultra-low standby power modes, extending battery life in distributed sensors. TSMC has also developed advanced multi-level cell programming techniques that effectively double memory density while maintaining reliability standards required for critical urban infrastructure applications.

Strengths: Industry-leading manufacturing process technology enables superior density scaling; excellent compatibility with standard CMOS processes facilitates integration with sensor and processing elements. Weaknesses: Requires specialized programming algorithms that increase controller complexity; exhibits variability in switching characteristics that necessitates more complex error correction.

Key Patents and Research in RRAM Scaling

Resistive memory cell and operation thereof, and resistive memory and operation and fabrication thereof

PatentInactiveUS20120020140A1

Innovation

- The use of conductive domain walls in high-resistance ferroelectric materials, such as BiFeO3, to store data by applying voltage pulses and forming domains with varying polarities, allowing for efficient data storage with reduced power consumption.

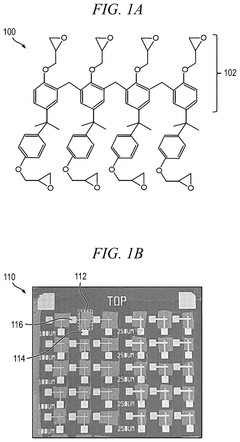

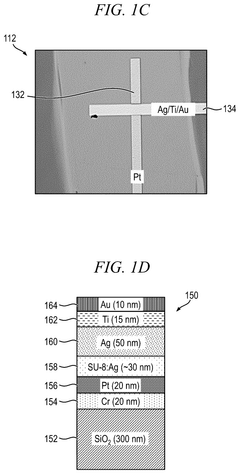

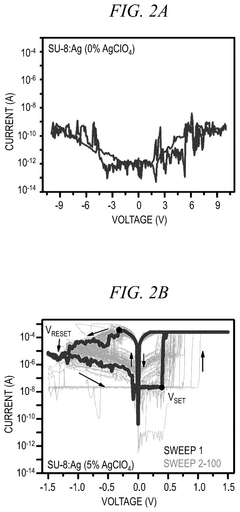

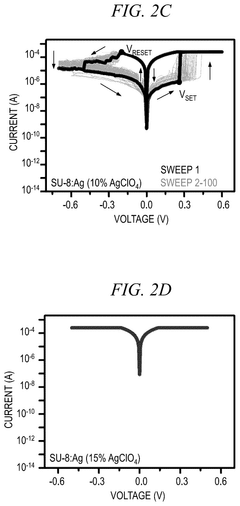

Metal-oxide infiltrated organic-inorganic hybrid resistive random-access memory device

PatentActiveUS12356877B2

Innovation

- A novel organic-inorganic hybrid RRAM device is developed using a SU-8:AgClO4 matrix infiltrated with AlOx through vapor-phase infiltration (VPI), allowing control of resistive switching characteristics by adjusting AgClO4 concentration and AlOx amount, reducing stochasticity and enhancing reproducibility.

Energy Efficiency Considerations for Smart City Implementation

Energy efficiency stands as a critical factor in the implementation of RRAM-based memory solutions for smart city infrastructure. The power consumption profile of RRAM technology offers significant advantages over conventional memory technologies, with standby power requirements typically 10-100 times lower than DRAM and operational energy consumption reduced by 30-60% compared to flash memory. This energy efficiency translates directly into extended battery life for distributed IoT sensors and reduced cooling requirements for edge computing nodes throughout smart city deployments.

When implementing RRAM in smart city solutions, several energy optimization strategies must be considered. Adaptive power management techniques can dynamically adjust voltage levels based on workload demands, potentially reducing energy consumption by up to 40% during low-activity periods. Multi-level cell configurations, while offering higher density, present an energy trade-off that requires careful evaluation based on specific application requirements. Research indicates that 2-bit MLC RRAM configurations strike an optimal balance between density and energy efficiency for most smart city applications.

The thermal characteristics of RRAM also contribute significantly to overall system efficiency. Unlike DRAM, which requires periodic refresh operations consuming substantial power, RRAM's non-volatile nature eliminates refresh power requirements entirely. This characteristic is particularly valuable in outdoor smart city installations where ambient temperatures can fluctuate widely, reducing cooling infrastructure needs by approximately 25-35% compared to traditional memory solutions.

From a system architecture perspective, RRAM enables more efficient data processing paradigms. By supporting in-memory computing capabilities, RRAM reduces energy-intensive data movement between storage and processing units. Early implementations demonstrate energy savings of 60-80% for specific pattern recognition and data filtering operations common in smart city applications such as traffic monitoring and environmental sensing.

The integration of RRAM with energy harvesting technologies presents another promising direction for smart city implementations. The low write energy requirements of RRAM (typically 0.1-1 pJ/bit) make it compatible with energy harvesting sources such as solar, vibration, or RF energy capture. This synergy enables the development of self-powered sensor nodes that can operate indefinitely without battery replacement, dramatically reducing maintenance costs and environmental impact across large-scale smart city deployments.

When evaluating total energy impact, lifecycle considerations reveal that RRAM-based solutions can reduce overall energy consumption by 40-60% compared to conventional memory technologies when accounting for manufacturing, operation, and end-of-life phases. This comprehensive energy efficiency makes RRAM particularly attractive for sustainable smart city initiatives aiming to minimize carbon footprint while maximizing computational capabilities at the edge.

When implementing RRAM in smart city solutions, several energy optimization strategies must be considered. Adaptive power management techniques can dynamically adjust voltage levels based on workload demands, potentially reducing energy consumption by up to 40% during low-activity periods. Multi-level cell configurations, while offering higher density, present an energy trade-off that requires careful evaluation based on specific application requirements. Research indicates that 2-bit MLC RRAM configurations strike an optimal balance between density and energy efficiency for most smart city applications.

The thermal characteristics of RRAM also contribute significantly to overall system efficiency. Unlike DRAM, which requires periodic refresh operations consuming substantial power, RRAM's non-volatile nature eliminates refresh power requirements entirely. This characteristic is particularly valuable in outdoor smart city installations where ambient temperatures can fluctuate widely, reducing cooling infrastructure needs by approximately 25-35% compared to traditional memory solutions.

From a system architecture perspective, RRAM enables more efficient data processing paradigms. By supporting in-memory computing capabilities, RRAM reduces energy-intensive data movement between storage and processing units. Early implementations demonstrate energy savings of 60-80% for specific pattern recognition and data filtering operations common in smart city applications such as traffic monitoring and environmental sensing.

The integration of RRAM with energy harvesting technologies presents another promising direction for smart city implementations. The low write energy requirements of RRAM (typically 0.1-1 pJ/bit) make it compatible with energy harvesting sources such as solar, vibration, or RF energy capture. This synergy enables the development of self-powered sensor nodes that can operate indefinitely without battery replacement, dramatically reducing maintenance costs and environmental impact across large-scale smart city deployments.

When evaluating total energy impact, lifecycle considerations reveal that RRAM-based solutions can reduce overall energy consumption by 40-60% compared to conventional memory technologies when accounting for manufacturing, operation, and end-of-life phases. This comprehensive energy efficiency makes RRAM particularly attractive for sustainable smart city initiatives aiming to minimize carbon footprint while maximizing computational capabilities at the edge.

Data Security Implications of High-Density RRAM

The increasing deployment of high-density RRAM in smart city infrastructure introduces significant data security considerations that must be addressed comprehensively. As RRAM technology enables massive data storage capabilities at the edge of smart city networks, it simultaneously creates new attack surfaces and security vulnerabilities that traditional memory technologies did not present.

RRAM's non-volatile nature means that sensitive data persists even when power is removed, creating potential data exposure risks if physical access to devices is compromised. This characteristic is particularly concerning in distributed smart city environments where edge devices may be deployed in publicly accessible or minimally secured locations. The persistence of data requires implementation of robust encryption schemes specifically optimized for RRAM's unique architecture.

The high density of RRAM introduces additional security challenges related to side-channel attacks. Research has demonstrated that the electrical characteristics of RRAM cells can potentially leak information about stored data through power analysis, electromagnetic emissions, or timing attacks. These vulnerabilities become more pronounced as memory density increases, creating more complex attack vectors that traditional security measures may not adequately address.

Cross-cell interference in high-density RRAM arrays presents another security concern. As cells are packed more tightly together, the potential for data corruption or unauthorized access through manipulating adjacent cells increases. This phenomenon, sometimes called "read disturb" or "program disturb," can be exploited by sophisticated attackers to extract sensitive information without direct access to the target memory cells.

From a data governance perspective, high-density RRAM enables storage of substantially more personally identifiable information (PII) and sensitive data at the edge, raising compliance concerns with regulations such as GDPR, CCPA, and other data protection frameworks. The distributed nature of smart city deployments complicates the implementation of consistent security policies across all storage nodes.

Emerging research indicates that specialized security architectures for RRAM are necessary, including hardware-level encryption engines, secure boot processes, and physical unclonable functions (PUFs) that leverage the inherent variability of RRAM cells to create device-specific security keys. These approaches must balance security requirements with the performance and power constraints that make RRAM attractive for smart city applications.

The integration of high-density RRAM with other emerging technologies like AI accelerators in edge devices creates compound security challenges that require holistic security approaches spanning hardware design, firmware implementation, and system architecture. As smart cities increasingly rely on these integrated systems for critical infrastructure management, the security implications of RRAM deployment will become increasingly significant to overall urban resilience and citizen privacy protection.

RRAM's non-volatile nature means that sensitive data persists even when power is removed, creating potential data exposure risks if physical access to devices is compromised. This characteristic is particularly concerning in distributed smart city environments where edge devices may be deployed in publicly accessible or minimally secured locations. The persistence of data requires implementation of robust encryption schemes specifically optimized for RRAM's unique architecture.

The high density of RRAM introduces additional security challenges related to side-channel attacks. Research has demonstrated that the electrical characteristics of RRAM cells can potentially leak information about stored data through power analysis, electromagnetic emissions, or timing attacks. These vulnerabilities become more pronounced as memory density increases, creating more complex attack vectors that traditional security measures may not adequately address.

Cross-cell interference in high-density RRAM arrays presents another security concern. As cells are packed more tightly together, the potential for data corruption or unauthorized access through manipulating adjacent cells increases. This phenomenon, sometimes called "read disturb" or "program disturb," can be exploited by sophisticated attackers to extract sensitive information without direct access to the target memory cells.

From a data governance perspective, high-density RRAM enables storage of substantially more personally identifiable information (PII) and sensitive data at the edge, raising compliance concerns with regulations such as GDPR, CCPA, and other data protection frameworks. The distributed nature of smart city deployments complicates the implementation of consistent security policies across all storage nodes.

Emerging research indicates that specialized security architectures for RRAM are necessary, including hardware-level encryption engines, secure boot processes, and physical unclonable functions (PUFs) that leverage the inherent variability of RRAM cells to create device-specific security keys. These approaches must balance security requirements with the performance and power constraints that make RRAM attractive for smart city applications.

The integration of high-density RRAM with other emerging technologies like AI accelerators in edge devices creates compound security challenges that require holistic security approaches spanning hardware design, firmware implementation, and system architecture. As smart cities increasingly rely on these integrated systems for critical infrastructure management, the security implications of RRAM deployment will become increasingly significant to overall urban resilience and citizen privacy protection.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!