How EUV Lithography Changes the Paradigm for Circuit Design

OCT 14, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

EUV Lithography Evolution and Design Objectives

Extreme Ultraviolet (EUV) lithography represents a revolutionary advancement in semiconductor manufacturing technology, marking a significant departure from traditional Deep Ultraviolet (DUV) lithography methods. The evolution of EUV technology spans over three decades, beginning in the 1980s with initial research into short-wavelength lithography solutions. By utilizing 13.5nm wavelength light, compared to 193nm in DUV systems, EUV enables the production of significantly smaller circuit features, supporting the continued advancement of Moore's Law.

The primary objective of EUV lithography development has been to overcome the physical limitations of traditional optical lithography techniques. As semiconductor manufacturers pushed toward sub-10nm process nodes, conventional DUV lithography required increasingly complex multi-patterning techniques, which introduced additional manufacturing steps, increased costs, and reduced yield. EUV technology aims to simplify this process while enabling further miniaturization of integrated circuits.

Technical evolution of EUV systems has progressed through several critical phases. Early development focused on fundamental light source challenges, as generating sufficient power at 13.5nm wavelength proved exceptionally difficult. The breakthrough came with the development of laser-produced plasma sources using tin droplets, which provided the necessary photon flux for industrial applications. Parallel advancements in reflective optics, mask technology, and resist chemistry were equally crucial to making EUV commercially viable.

The industry's EUV implementation roadmap has evolved from initial proof-of-concept demonstrations to today's high-volume manufacturing capabilities. Early EUV scanners delivered in the 2010s offered limited throughput and reliability, while current systems can process over 150 wafers per hour with significantly improved uptime. Future objectives include enhancing resolution through high-NA (numerical aperture) EUV systems, which promise to extend scaling capabilities to the 2nm node and beyond.

From a circuit design perspective, EUV technology establishes new objectives centered on exploiting the enhanced resolution capabilities. Design teams can now implement more complex architectures with higher transistor densities, enabling greater functionality within the same silicon area. Additionally, EUV's reduced need for multiple patterning steps allows for more regular design layouts and potentially simpler design rules, though with different constraints than traditional lithography systems.

The long-term technical trajectory for EUV lithography includes continued improvements in source power, system reliability, and resolution enhancement techniques. These advancements aim to support semiconductor scaling for at least another decade, with research already underway for potential successor technologies such as high-NA EUV and directed self-assembly approaches that could extend scaling even further.

The primary objective of EUV lithography development has been to overcome the physical limitations of traditional optical lithography techniques. As semiconductor manufacturers pushed toward sub-10nm process nodes, conventional DUV lithography required increasingly complex multi-patterning techniques, which introduced additional manufacturing steps, increased costs, and reduced yield. EUV technology aims to simplify this process while enabling further miniaturization of integrated circuits.

Technical evolution of EUV systems has progressed through several critical phases. Early development focused on fundamental light source challenges, as generating sufficient power at 13.5nm wavelength proved exceptionally difficult. The breakthrough came with the development of laser-produced plasma sources using tin droplets, which provided the necessary photon flux for industrial applications. Parallel advancements in reflective optics, mask technology, and resist chemistry were equally crucial to making EUV commercially viable.

The industry's EUV implementation roadmap has evolved from initial proof-of-concept demonstrations to today's high-volume manufacturing capabilities. Early EUV scanners delivered in the 2010s offered limited throughput and reliability, while current systems can process over 150 wafers per hour with significantly improved uptime. Future objectives include enhancing resolution through high-NA (numerical aperture) EUV systems, which promise to extend scaling capabilities to the 2nm node and beyond.

From a circuit design perspective, EUV technology establishes new objectives centered on exploiting the enhanced resolution capabilities. Design teams can now implement more complex architectures with higher transistor densities, enabling greater functionality within the same silicon area. Additionally, EUV's reduced need for multiple patterning steps allows for more regular design layouts and potentially simpler design rules, though with different constraints than traditional lithography systems.

The long-term technical trajectory for EUV lithography includes continued improvements in source power, system reliability, and resolution enhancement techniques. These advancements aim to support semiconductor scaling for at least another decade, with research already underway for potential successor technologies such as high-NA EUV and directed self-assembly approaches that could extend scaling even further.

Market Demand Analysis for Advanced Semiconductor Nodes

The semiconductor industry's demand for advanced nodes continues to accelerate, driven primarily by the computational requirements of artificial intelligence, high-performance computing, and next-generation mobile applications. Market analysis indicates that the transition to sub-7nm nodes represents a critical inflection point, with EUV lithography emerging as the enabling technology for these advanced manufacturing processes.

Current projections show the advanced semiconductor market growing at a compound annual growth rate of 19% through 2026, significantly outpacing the broader semiconductor industry's growth rate of 7%. This acceleration is particularly evident in the data center segment, where the demand for AI processors manufactured at 5nm and below is expected to triple by 2025.

The economic drivers behind this market expansion are compelling. While the cost per transistor had temporarily plateaued with traditional multi-patterning techniques, EUV lithography has revitalized Moore's Law economics. Despite the substantial capital investment required for EUV equipment, the technology enables a 20-30% reduction in overall manufacturing costs at advanced nodes when factoring in yield improvements and process simplification.

Regional analysis reveals an intensifying global competition for advanced semiconductor manufacturing capabilities. Asia-Pacific currently dominates with approximately 75% of advanced node capacity, though significant investments in the United States and Europe aim to rebalance this distribution. Government initiatives worldwide, including the CHIPS Act in the US and the European Chips Act, collectively represent over $100 billion in committed funding to develop domestic advanced semiconductor ecosystems.

Customer segmentation shows that mobile processors remain the largest market for advanced nodes, accounting for 42% of wafer starts. However, high-performance computing and AI accelerators represent the fastest-growing segments, with projected five-year growth rates exceeding 35%. Automotive applications are also emerging as a significant market, particularly for advanced driver assistance systems and autonomous driving capabilities.

The transition to EUV-enabled nodes has created new market dynamics among fabless semiconductor companies. Those with designs optimized for EUV manufacturing processes gain significant advantages in power efficiency and performance density, creating competitive differentiation. This has accelerated design migration to advanced nodes, with over 60% of new high-performance designs targeting 5nm or smaller process technologies.

Supply constraints remain a significant market factor, with lead times for EUV lithography equipment extending to 18-24 months. This equipment bottleneck has created a strategic advantage for foundries with secured EUV capacity, allowing them to command premium pricing for advanced node manufacturing services.

Current projections show the advanced semiconductor market growing at a compound annual growth rate of 19% through 2026, significantly outpacing the broader semiconductor industry's growth rate of 7%. This acceleration is particularly evident in the data center segment, where the demand for AI processors manufactured at 5nm and below is expected to triple by 2025.

The economic drivers behind this market expansion are compelling. While the cost per transistor had temporarily plateaued with traditional multi-patterning techniques, EUV lithography has revitalized Moore's Law economics. Despite the substantial capital investment required for EUV equipment, the technology enables a 20-30% reduction in overall manufacturing costs at advanced nodes when factoring in yield improvements and process simplification.

Regional analysis reveals an intensifying global competition for advanced semiconductor manufacturing capabilities. Asia-Pacific currently dominates with approximately 75% of advanced node capacity, though significant investments in the United States and Europe aim to rebalance this distribution. Government initiatives worldwide, including the CHIPS Act in the US and the European Chips Act, collectively represent over $100 billion in committed funding to develop domestic advanced semiconductor ecosystems.

Customer segmentation shows that mobile processors remain the largest market for advanced nodes, accounting for 42% of wafer starts. However, high-performance computing and AI accelerators represent the fastest-growing segments, with projected five-year growth rates exceeding 35%. Automotive applications are also emerging as a significant market, particularly for advanced driver assistance systems and autonomous driving capabilities.

The transition to EUV-enabled nodes has created new market dynamics among fabless semiconductor companies. Those with designs optimized for EUV manufacturing processes gain significant advantages in power efficiency and performance density, creating competitive differentiation. This has accelerated design migration to advanced nodes, with over 60% of new high-performance designs targeting 5nm or smaller process technologies.

Supply constraints remain a significant market factor, with lead times for EUV lithography equipment extending to 18-24 months. This equipment bottleneck has created a strategic advantage for foundries with secured EUV capacity, allowing them to command premium pricing for advanced node manufacturing services.

EUV Technology Status and Implementation Challenges

Extreme Ultraviolet (EUV) lithography represents a revolutionary advancement in semiconductor manufacturing, currently deployed in leading-edge production nodes at 7nm and below. The technology utilizes 13.5nm wavelength light to achieve unprecedented resolution capabilities, enabling the continuation of Moore's Law despite reaching the physical limitations of previous deep ultraviolet (DUV) lithography systems. Major semiconductor manufacturers including TSMC, Samsung, and Intel have implemented EUV in their most advanced fabrication facilities, though with varying degrees of integration and success.

Despite its transformative potential, EUV technology faces significant implementation challenges. The most pressing issue remains the power source efficiency, with current EUV light sources achieving only 250-300W of usable power, below the ideal 500W target for optimal throughput. This limitation directly impacts production economics, as lower power translates to slower wafer processing and higher per-chip costs. Additionally, the complex physics of EUV light generation—involving laser-pulsed tin droplets creating plasma—introduces reliability concerns that affect consistent manufacturing output.

Mask infrastructure presents another substantial challenge. EUV masks require fundamentally different manufacturing processes compared to traditional photomasks, including specialized multi-layer reflective coatings and defect mitigation strategies. The absence of pellicles (protective films) that can withstand EUV's intense energy further complicates mask protection and maintenance protocols. Current EUV pellicle solutions offer limited transmission efficiency and durability, creating a significant bottleneck in the manufacturing process.

Photoresist chemistry for EUV presents unique challenges due to the fundamentally different interaction mechanisms between EUV photons and resist materials. Unlike DUV lithography, EUV generates secondary electrons that affect pattern formation, requiring entirely new resist formulations. Current EUV resists struggle to simultaneously achieve the "triangle of death" requirements: resolution, sensitivity, and line edge roughness, forcing difficult engineering trade-offs.

From an infrastructure perspective, EUV systems demand extraordinary precision in their operating environment. The systems require specialized facilities with enhanced vibration control, temperature stability within millikelvin ranges, and vacuum systems capable of maintaining ultra-high vacuum conditions. These requirements substantially increase the capital expenditure for fabs implementing EUV technology, with each EUV scanner costing approximately $150-200 million compared to $40-60 million for DUV systems.

The global distribution of EUV expertise and equipment remains highly concentrated, with ASML maintaining a virtual monopoly on EUV scanner production. This concentration creates supply chain vulnerabilities and geopolitical considerations that impact technology adoption timelines. Despite these challenges, the semiconductor industry continues to invest heavily in overcoming EUV limitations, recognizing its critical importance to future circuit design paradigms and manufacturing capabilities.

Despite its transformative potential, EUV technology faces significant implementation challenges. The most pressing issue remains the power source efficiency, with current EUV light sources achieving only 250-300W of usable power, below the ideal 500W target for optimal throughput. This limitation directly impacts production economics, as lower power translates to slower wafer processing and higher per-chip costs. Additionally, the complex physics of EUV light generation—involving laser-pulsed tin droplets creating plasma—introduces reliability concerns that affect consistent manufacturing output.

Mask infrastructure presents another substantial challenge. EUV masks require fundamentally different manufacturing processes compared to traditional photomasks, including specialized multi-layer reflective coatings and defect mitigation strategies. The absence of pellicles (protective films) that can withstand EUV's intense energy further complicates mask protection and maintenance protocols. Current EUV pellicle solutions offer limited transmission efficiency and durability, creating a significant bottleneck in the manufacturing process.

Photoresist chemistry for EUV presents unique challenges due to the fundamentally different interaction mechanisms between EUV photons and resist materials. Unlike DUV lithography, EUV generates secondary electrons that affect pattern formation, requiring entirely new resist formulations. Current EUV resists struggle to simultaneously achieve the "triangle of death" requirements: resolution, sensitivity, and line edge roughness, forcing difficult engineering trade-offs.

From an infrastructure perspective, EUV systems demand extraordinary precision in their operating environment. The systems require specialized facilities with enhanced vibration control, temperature stability within millikelvin ranges, and vacuum systems capable of maintaining ultra-high vacuum conditions. These requirements substantially increase the capital expenditure for fabs implementing EUV technology, with each EUV scanner costing approximately $150-200 million compared to $40-60 million for DUV systems.

The global distribution of EUV expertise and equipment remains highly concentrated, with ASML maintaining a virtual monopoly on EUV scanner production. This concentration creates supply chain vulnerabilities and geopolitical considerations that impact technology adoption timelines. Despite these challenges, the semiconductor industry continues to invest heavily in overcoming EUV limitations, recognizing its critical importance to future circuit design paradigms and manufacturing capabilities.

Current EUV-Based Circuit Design Methodologies

01 EUV lithography system design and optimization

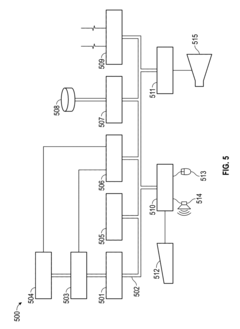

Extreme Ultraviolet (EUV) lithography systems require specialized design considerations to achieve optimal performance. These systems incorporate advanced optical components, illumination sources, and control mechanisms to handle the unique properties of EUV light. Design optimizations focus on improving resolution, reducing aberrations, and enhancing overall system stability to enable precise pattern transfer at extremely small feature sizes.- EUV lithography system design and optimization: Extreme Ultraviolet (EUV) lithography systems require specialized design considerations to achieve optimal performance. These systems incorporate advanced optical components, illumination sources, and control mechanisms to handle the unique challenges of EUV wavelengths. Innovations in system architecture focus on improving resolution, reducing aberrations, and enhancing overall system stability to enable precise circuit pattern transfer at increasingly smaller nodes.

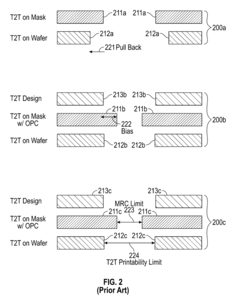

- Circuit design rules and pattern optimization for EUV: EUV lithography requires specialized circuit design rules to accommodate its unique characteristics. These include considerations for feature sizing, spacing, and orientation to minimize pattern distortion and maximize yield. Advanced computational techniques are employed to optimize circuit layouts specifically for EUV processes, including pattern decomposition strategies and design for manufacturability approaches that account for EUV-specific effects.

- Multi-patterning and resolution enhancement techniques: To overcome resolution limitations in EUV lithography, various multi-patterning and resolution enhancement techniques have been developed. These include computational lithography approaches, source mask optimization, and advanced patterning strategies that enable the fabrication of complex circuit features beyond the nominal resolution limits of EUV systems. These techniques are essential for extending EUV capabilities to more advanced technology nodes.

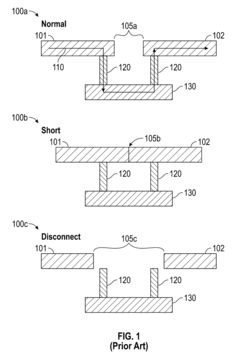

- EUV-specific defect detection and mitigation: EUV lithography introduces unique defect challenges that require specialized detection and mitigation strategies. Advanced inspection techniques have been developed to identify EUV-specific defects such as pattern bridging, line edge roughness, and stochastic effects. Circuit design paradigms incorporate defect-aware methodologies that enhance yield by accounting for the statistical nature of EUV-induced variations and implementing redundancy or repair mechanisms.

- Integration of EUV with advanced packaging technologies: EUV lithography is increasingly being integrated with advanced packaging technologies to enable next-generation semiconductor devices. This integration requires specialized circuit design approaches that consider both front-end EUV patterning and back-end packaging requirements. Design paradigms focus on optimizing system-level performance through co-design methodologies that leverage the high-resolution capabilities of EUV while addressing thermal, electrical, and mechanical constraints of advanced packaging.

02 Circuit design rules and pattern optimization for EUV

EUV lithography necessitates specialized circuit design rules to accommodate its unique characteristics. These rules address challenges such as stochastic effects, pattern fidelity, and resolution limitations. Design approaches include optimizing layout geometries, implementing assist features, and developing new computational methods to enhance pattern transfer accuracy while maintaining circuit functionality at advanced technology nodes.Expand Specific Solutions03 Multi-patterning techniques for EUV lithography

Multi-patterning techniques are employed in EUV lithography to overcome resolution limitations and improve pattern fidelity. These approaches involve decomposing complex patterns into multiple simpler exposures that can be more accurately reproduced. Advanced computational algorithms are used to optimize pattern decomposition while minimizing overlay errors and maximizing process windows, enabling the fabrication of increasingly complex circuit designs.Expand Specific Solutions04 EUV mask technology and defect mitigation

EUV mask technology presents unique challenges due to the reflective nature of EUV optics and the absence of pellicles in early implementations. Advanced mask designs incorporate features to mitigate defects, enhance contrast, and improve pattern fidelity. Computational approaches are used to predict and compensate for mask-induced imaging errors, while novel materials and structures are developed to enhance mask performance and durability in the EUV environment.Expand Specific Solutions05 Integration of EUV with complementary lithography techniques

EUV lithography is often integrated with complementary lithography techniques to optimize semiconductor manufacturing. This hybrid approach combines the high-resolution capabilities of EUV with the cost-effectiveness of other methods like immersion lithography or directed self-assembly. Integration strategies focus on determining which layers benefit most from EUV processing while developing seamless workflows that maintain alignment precision across different lithography platforms.Expand Specific Solutions

Key Semiconductor and Equipment Manufacturing Players

EUV lithography represents a transformative shift in semiconductor manufacturing, currently in its early adoption phase despite significant market growth projections. The technology is maturing rapidly but remains at different implementation stages across key players. ASML Netherlands BV dominates the EUV equipment market, while leading semiconductor manufacturers like Taiwan Semiconductor Manufacturing Co., Samsung Electronics, and Intel are investing heavily in EUV integration. GlobalFoundries, SMIC, and SK hynix are advancing their EUV capabilities, though at varying paces. The ecosystem includes materials suppliers (Shin-Etsu Chemical, AGC) and equipment manufacturers (Applied Materials, Tokyo Electron, Lam Research) working to overcome technical challenges in photoresist development, mask technology, and defect reduction to enable the next generation of circuit designs below 7nm.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC has pioneered the implementation of EUV lithography in high-volume manufacturing, fundamentally changing circuit design approaches. Their N7+ technology was the first to incorporate EUV, and their N5 process uses extensive EUV layers. TSMC's EUV implementation includes: (1) specialized design rule modifications that account for EUV-specific stochastic effects and pattern fidelity challenges; (2) advanced computational lithography techniques optimized for EUV's unique imaging characteristics; (3) innovative multi-patterning strategies that combine EUV with traditional lithography to optimize cost and performance; and (4) custom resist and materials processing tailored to EUV's high-energy photons. TSMC has demonstrated that EUV enables approximately 20% smaller die sizes and 10% power reduction compared to equivalent non-EUV nodes, while reducing mask complexity by eliminating multiple patterning steps.

Strengths: Industry-leading implementation expertise; comprehensive design ecosystem supporting EUV-specific requirements; proven high-volume manufacturing capability. Weaknesses: Extremely high capital expenditure requirements; geographic concentration risk; dependency on limited EUV equipment suppliers.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has developed a comprehensive EUV lithography implementation strategy for advanced semiconductor manufacturing. Their approach includes: (1) specialized circuit design methodologies that account for EUV's unique patterning characteristics, including stochastic edge effects and line-edge roughness considerations; (2) custom design rule modifications that optimize for EUV's capabilities while mitigating its limitations; (3) advanced computational lithography techniques specifically tailored to EUV's imaging properties; and (4) innovative materials engineering for EUV-specific photoresists and process integration. Samsung's 7nm LPP (Low Power Plus) process was their first to incorporate EUV, followed by 5nm and 3nm nodes with increasing EUV layer usage. Their implementation has demonstrated approximately 40% area reduction and 50% power savings compared to their 10nm process, while reducing mask complexity by eliminating multiple patterning steps for critical layers.

Strengths: Vertical integration from equipment research to chip design; significant financial resources for continued investment; ability to optimize designs specifically for their manufacturing processes. Weaknesses: Relatively less mature EUV implementation compared to TSMC; challenges in yield optimization; higher defect densities in early implementations.

Critical EUV Patents and Technical Innovations

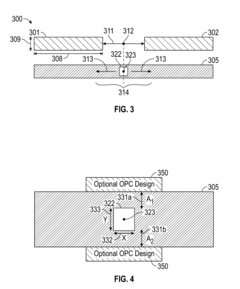

Methods for optical proximity correction in the design and fabrication of integrated circuits using extreme ultraviolet lithography

PatentActiveUS9651855B2

Innovation

- The implementation of novel optical proximity correction (OPC) techniques that generate a third polygon with dimensions corresponding to the combination of first and second design polygons and a filled polygon within it, allowing for closer tip proximity without the need for multiple masks.

Extreme ultraviolet lithography photomasks

PatentActiveUS20170315438A1

Innovation

- The introduction of a 'black border' region with a modified surface morphology on the photomask structure to scatter deep ultraviolet (DUV) light away from the next mirror, reducing EUV reflectivity and preventing radiation overlap, achieved through a combination of substrate modification, multilayer reflective coatings, and absorber layer patterning.

Supply Chain Implications for EUV Adoption

The adoption of Extreme Ultraviolet (EUV) lithography represents a significant shift in semiconductor manufacturing, creating profound implications for the global supply chain. The transition from traditional Deep Ultraviolet (DUV) to EUV technology has restructured supplier relationships and created new dependencies within the semiconductor ecosystem.

ASML's virtual monopoly on EUV lithography systems has established a critical bottleneck in the supply chain. With each EUV machine costing upwards of $150 million and requiring specialized expertise to operate, only the largest semiconductor manufacturers can afford this investment. This has accelerated industry consolidation, with smaller players increasingly unable to compete at advanced nodes.

The geographical concentration of EUV expertise presents significant geopolitical concerns. Key components for EUV systems come from a limited number of suppliers across Europe, Japan, and the United States, creating vulnerability to trade restrictions and national security considerations. The complex optics systems from Zeiss in Germany and specialized laser technology from Cymer in the US exemplify this concentrated supply network.

Raw material requirements for EUV implementation have shifted dramatically, particularly regarding ultra-pure materials needed for masks and photoresists. The demand for high-purity tin used in EUV light sources has created new supply pressures, while specialized materials for EUV masks have necessitated new purification technologies and supplier relationships.

Workforce implications are equally significant, as EUV adoption requires highly specialized engineering talent. Organizations must develop comprehensive training programs and knowledge transfer mechanisms to build expertise in EUV-specific design rules and manufacturing processes. This has triggered intense competition for talent with EUV experience.

The extended lead times for EUV equipment—often exceeding 18 months—have forced manufacturers to implement more sophisticated capacity planning. This has ripple effects throughout the supply chain, requiring coordinated investment decisions among chipmakers, equipment suppliers, and materials providers.

For circuit designers, these supply chain realities translate to longer development cycles and increased costs. The limited availability of EUV manufacturing capacity means design teams must secure production slots far in advance, affecting time-to-market strategies. Additionally, the concentration of EUV capability among fewer manufacturers has altered traditional customer-supplier dynamics, with implications for intellectual property protection and competitive positioning.

ASML's virtual monopoly on EUV lithography systems has established a critical bottleneck in the supply chain. With each EUV machine costing upwards of $150 million and requiring specialized expertise to operate, only the largest semiconductor manufacturers can afford this investment. This has accelerated industry consolidation, with smaller players increasingly unable to compete at advanced nodes.

The geographical concentration of EUV expertise presents significant geopolitical concerns. Key components for EUV systems come from a limited number of suppliers across Europe, Japan, and the United States, creating vulnerability to trade restrictions and national security considerations. The complex optics systems from Zeiss in Germany and specialized laser technology from Cymer in the US exemplify this concentrated supply network.

Raw material requirements for EUV implementation have shifted dramatically, particularly regarding ultra-pure materials needed for masks and photoresists. The demand for high-purity tin used in EUV light sources has created new supply pressures, while specialized materials for EUV masks have necessitated new purification technologies and supplier relationships.

Workforce implications are equally significant, as EUV adoption requires highly specialized engineering talent. Organizations must develop comprehensive training programs and knowledge transfer mechanisms to build expertise in EUV-specific design rules and manufacturing processes. This has triggered intense competition for talent with EUV experience.

The extended lead times for EUV equipment—often exceeding 18 months—have forced manufacturers to implement more sophisticated capacity planning. This has ripple effects throughout the supply chain, requiring coordinated investment decisions among chipmakers, equipment suppliers, and materials providers.

For circuit designers, these supply chain realities translate to longer development cycles and increased costs. The limited availability of EUV manufacturing capacity means design teams must secure production slots far in advance, affecting time-to-market strategies. Additionally, the concentration of EUV capability among fewer manufacturers has altered traditional customer-supplier dynamics, with implications for intellectual property protection and competitive positioning.

Energy Efficiency and Sustainability Considerations in EUV

Extreme Ultraviolet (EUV) lithography represents a significant advancement in semiconductor manufacturing, but its energy consumption profile poses substantial challenges for the industry's sustainability goals. EUV systems require approximately 10 times more power than previous Deep Ultraviolet (DUV) lithography tools, with a single EUV machine consuming up to 1 megawatt during operation. This increased energy demand stems primarily from the complex laser-produced plasma light source that generates the 13.5nm wavelength radiation necessary for EUV patterning.

The environmental impact of this energy consumption is considerable, particularly as semiconductor fabs transition to multiple EUV tools. A modern semiconductor fabrication facility utilizing EUV technology may require dedicated power substations, contributing significantly to the industry's carbon footprint. This reality has prompted leading semiconductor manufacturers to implement comprehensive sustainability initiatives, including investments in renewable energy sources and carbon offset programs.

Despite these high energy requirements, EUV lithography offers counterbalancing sustainability benefits through process simplification. Traditional multi-patterning approaches using DUV technology often require 2-4 times more process steps to achieve similar feature densities. EUV's ability to pattern critical layers in a single exposure reduces chemical usage, water consumption, and overall manufacturing time, potentially offsetting some of its energy disadvantages.

Circuit designers must now incorporate energy efficiency considerations directly into their design methodologies when targeting EUV-based processes. This includes optimizing layouts to maximize the value derived from each energy-intensive EUV exposure step. Design approaches that minimize the number of critical layers requiring EUV lithography can significantly reduce the overall energy footprint of chip production.

Material innovation represents another frontier in improving EUV sustainability. Research into more sensitive photoresists that require less exposure energy could substantially reduce power consumption. Similarly, advancements in EUV light source technology, particularly improvements in conversion efficiency from laser energy to usable EUV radiation, offer promising pathways to reduce the technology's energy intensity.

The semiconductor industry has begun establishing collaborative initiatives focused specifically on improving EUV energy efficiency. These consortia bring together equipment manufacturers, chip designers, and material scientists to develop holistic approaches to sustainability challenges. Their roadmaps typically target 30-50% improvements in EUV energy efficiency over the next five years through combined innovations in equipment design, materials, and process optimization.

The environmental impact of this energy consumption is considerable, particularly as semiconductor fabs transition to multiple EUV tools. A modern semiconductor fabrication facility utilizing EUV technology may require dedicated power substations, contributing significantly to the industry's carbon footprint. This reality has prompted leading semiconductor manufacturers to implement comprehensive sustainability initiatives, including investments in renewable energy sources and carbon offset programs.

Despite these high energy requirements, EUV lithography offers counterbalancing sustainability benefits through process simplification. Traditional multi-patterning approaches using DUV technology often require 2-4 times more process steps to achieve similar feature densities. EUV's ability to pattern critical layers in a single exposure reduces chemical usage, water consumption, and overall manufacturing time, potentially offsetting some of its energy disadvantages.

Circuit designers must now incorporate energy efficiency considerations directly into their design methodologies when targeting EUV-based processes. This includes optimizing layouts to maximize the value derived from each energy-intensive EUV exposure step. Design approaches that minimize the number of critical layers requiring EUV lithography can significantly reduce the overall energy footprint of chip production.

Material innovation represents another frontier in improving EUV sustainability. Research into more sensitive photoresists that require less exposure energy could substantially reduce power consumption. Similarly, advancements in EUV light source technology, particularly improvements in conversion efficiency from laser energy to usable EUV radiation, offer promising pathways to reduce the technology's energy intensity.

The semiconductor industry has begun establishing collaborative initiatives focused specifically on improving EUV energy efficiency. These consortia bring together equipment manufacturers, chip designers, and material scientists to develop holistic approaches to sustainability challenges. Their roadmaps typically target 30-50% improvements in EUV energy efficiency over the next five years through combined innovations in equipment design, materials, and process optimization.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!