Measure RRAM Retention Using Accelerated Aging Tests

SEP 10, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

RRAM Retention Technology Background and Objectives

Resistive Random Access Memory (RRAM) has emerged as a promising candidate for next-generation non-volatile memory technologies due to its simple structure, high density, low power consumption, and compatibility with CMOS processes. Since its conceptualization in the early 2000s, RRAM technology has evolved significantly, transitioning from laboratory experiments to commercial prototypes. The fundamental operating principle of RRAM relies on the reversible formation and rupture of conductive filaments within a dielectric layer, enabling the switching between high and low resistance states.

Data retention, the ability of a memory cell to maintain its programmed state over time, represents one of the critical reliability metrics for any non-volatile memory technology. For RRAM devices, retention performance directly impacts their viability in various applications ranging from consumer electronics to automotive and industrial systems where data integrity must be maintained for years or even decades under diverse environmental conditions.

The evolution of RRAM retention technology has been marked by continuous improvements in material engineering, device architecture, and programming schemes. Early RRAM devices suffered from significant retention issues due to unstable filament structures and material degradation. Recent advancements in oxide materials, interface engineering, and doping techniques have substantially enhanced retention capabilities, though challenges remain for widespread commercial adoption.

Accelerated aging tests have become the standard methodology for evaluating RRAM retention characteristics, as waiting for actual years of operation is impractical for research and development cycles. These tests involve subjecting devices to elevated temperatures to accelerate the degradation mechanisms that would naturally occur over extended periods at normal operating temperatures. The Arrhenius model typically serves as the theoretical foundation for extrapolating high-temperature test results to predict retention behavior at normal operating conditions.

The primary objective of RRAM retention measurement using accelerated aging tests is to develop reliable protocols that can accurately predict device performance over the required lifetime while minimizing test duration. This involves establishing standardized testing methodologies, identifying appropriate acceleration factors, and understanding the fundamental physical mechanisms governing retention failure modes.

Additional goals include correlating retention performance with specific material compositions and fabrication processes, developing predictive models that can estimate retention characteristics from short-term measurements, and establishing design guidelines for optimizing the retention-performance tradeoff. These efforts aim to address the growing demand for non-volatile memory solutions in emerging applications such as edge computing, Internet of Things (IoT) devices, and neuromorphic systems where reliability under various environmental conditions is paramount.

Data retention, the ability of a memory cell to maintain its programmed state over time, represents one of the critical reliability metrics for any non-volatile memory technology. For RRAM devices, retention performance directly impacts their viability in various applications ranging from consumer electronics to automotive and industrial systems where data integrity must be maintained for years or even decades under diverse environmental conditions.

The evolution of RRAM retention technology has been marked by continuous improvements in material engineering, device architecture, and programming schemes. Early RRAM devices suffered from significant retention issues due to unstable filament structures and material degradation. Recent advancements in oxide materials, interface engineering, and doping techniques have substantially enhanced retention capabilities, though challenges remain for widespread commercial adoption.

Accelerated aging tests have become the standard methodology for evaluating RRAM retention characteristics, as waiting for actual years of operation is impractical for research and development cycles. These tests involve subjecting devices to elevated temperatures to accelerate the degradation mechanisms that would naturally occur over extended periods at normal operating temperatures. The Arrhenius model typically serves as the theoretical foundation for extrapolating high-temperature test results to predict retention behavior at normal operating conditions.

The primary objective of RRAM retention measurement using accelerated aging tests is to develop reliable protocols that can accurately predict device performance over the required lifetime while minimizing test duration. This involves establishing standardized testing methodologies, identifying appropriate acceleration factors, and understanding the fundamental physical mechanisms governing retention failure modes.

Additional goals include correlating retention performance with specific material compositions and fabrication processes, developing predictive models that can estimate retention characteristics from short-term measurements, and establishing design guidelines for optimizing the retention-performance tradeoff. These efforts aim to address the growing demand for non-volatile memory solutions in emerging applications such as edge computing, Internet of Things (IoT) devices, and neuromorphic systems where reliability under various environmental conditions is paramount.

Market Demand Analysis for High-Retention RRAM

The global market for Resistive Random Access Memory (RRAM) with high retention capabilities is experiencing significant growth, driven by increasing demands for non-volatile memory solutions that can maintain data integrity over extended periods. Current market projections indicate that the RRAM segment is expected to grow at a compound annual growth rate of 16.2% from 2023 to 2030, with high-retention variants becoming increasingly important in this expansion.

The demand for high-retention RRAM is particularly strong in sectors requiring long-term data storage without power consumption. The automotive industry represents a major market driver, as vehicles increasingly incorporate advanced driver assistance systems and autonomous capabilities that require reliable, long-term data storage in harsh operating environments. Temperature variations from -40°C to 125°C in automotive applications make retention a critical parameter for memory components.

Industrial IoT applications constitute another significant market segment, with deployed sensors and edge computing devices often positioned in remote locations where maintenance access is limited. These applications require memory solutions that can retain data for 10+ years while operating in challenging environmental conditions. The ability of high-retention RRAM to maintain data integrity without refresh cycles provides substantial energy savings in these power-constrained scenarios.

Consumer electronics manufacturers are also showing increased interest in high-retention RRAM solutions. As devices become more sophisticated while simultaneously shrinking in size, the need for compact, energy-efficient memory with reliable long-term storage capabilities becomes paramount. Market research indicates that consumers increasingly value devices with longer lifespans and improved reliability, creating pull-through demand for components with superior retention characteristics.

The healthcare and medical device sector represents an emerging market opportunity for high-retention RRAM. Implantable medical devices and portable diagnostic equipment require memory solutions that can maintain critical patient data with absolute reliability over many years. The market potential in this segment is expected to grow substantially as regulatory frameworks evolve to accommodate new memory technologies in medical applications.

Enterprise storage systems are gradually incorporating RRAM technologies to address the growing need for persistent memory tiers that bridge the performance gap between DRAM and NAND flash. High-retention characteristics are essential in these applications to ensure data integrity during power loss events and system failures. Market analysis suggests that enterprise customers are willing to pay premium prices for memory solutions that offer enhanced reliability and data retention guarantees.

The demand for high-retention RRAM is particularly strong in sectors requiring long-term data storage without power consumption. The automotive industry represents a major market driver, as vehicles increasingly incorporate advanced driver assistance systems and autonomous capabilities that require reliable, long-term data storage in harsh operating environments. Temperature variations from -40°C to 125°C in automotive applications make retention a critical parameter for memory components.

Industrial IoT applications constitute another significant market segment, with deployed sensors and edge computing devices often positioned in remote locations where maintenance access is limited. These applications require memory solutions that can retain data for 10+ years while operating in challenging environmental conditions. The ability of high-retention RRAM to maintain data integrity without refresh cycles provides substantial energy savings in these power-constrained scenarios.

Consumer electronics manufacturers are also showing increased interest in high-retention RRAM solutions. As devices become more sophisticated while simultaneously shrinking in size, the need for compact, energy-efficient memory with reliable long-term storage capabilities becomes paramount. Market research indicates that consumers increasingly value devices with longer lifespans and improved reliability, creating pull-through demand for components with superior retention characteristics.

The healthcare and medical device sector represents an emerging market opportunity for high-retention RRAM. Implantable medical devices and portable diagnostic equipment require memory solutions that can maintain critical patient data with absolute reliability over many years. The market potential in this segment is expected to grow substantially as regulatory frameworks evolve to accommodate new memory technologies in medical applications.

Enterprise storage systems are gradually incorporating RRAM technologies to address the growing need for persistent memory tiers that bridge the performance gap between DRAM and NAND flash. High-retention characteristics are essential in these applications to ensure data integrity during power loss events and system failures. Market analysis suggests that enterprise customers are willing to pay premium prices for memory solutions that offer enhanced reliability and data retention guarantees.

Current Challenges in RRAM Retention Testing

Despite significant advancements in RRAM technology, retention testing remains one of the most challenging aspects of reliability assessment. The fundamental challenge lies in the inherent trade-off between test duration and accuracy of lifetime prediction. Conventional retention testing requires months or even years to obtain reliable data at operating temperatures, making it impractical for rapid technology development cycles and commercial qualification processes.

Accelerated aging tests attempt to address this issue by elevating temperatures to accelerate failure mechanisms, but this approach introduces several complications. The primary concern is whether the failure mechanisms at elevated temperatures accurately represent those at normal operating conditions. Evidence suggests that different degradation pathways may dominate at different temperature regimes, potentially leading to inaccurate lifetime projections when extrapolating from high-temperature data.

The Arrhenius model, commonly used for extrapolation in accelerated testing, assumes a constant activation energy across temperature ranges. However, RRAM devices often exhibit complex degradation behaviors with multiple competing mechanisms, each with different activation energies. This fundamental assumption mismatch can result in significant errors when projecting long-term retention characteristics from accelerated test data.

Statistical challenges further complicate retention testing. RRAM devices typically show wide device-to-device variability in retention characteristics, necessitating large sample sizes for meaningful statistical analysis. This variability stems from manufacturing process variations, random defect distributions, and intrinsic stochastic nature of filament formation and rupture processes.

Test equipment limitations present additional hurdles. Maintaining precise temperature control over extended periods, especially at elevated temperatures, requires sophisticated environmental chambers. Moreover, the measurement process itself can potentially disturb the device state, particularly for destructive read operations or when frequent measurements are required.

The definition of failure criteria remains inconsistent across the industry. Some researchers define retention failure as a specific resistance window closure percentage, while others use absolute resistance thresholds or bit error rates. This lack of standardization makes cross-comparison between different research results challenging and hampers industry-wide reliability assessment protocols.

Finally, accelerated testing methodologies struggle to account for cycling-dependent retention behavior. Evidence suggests that retention characteristics can evolve with program/erase cycling, but most accelerated tests focus on fresh devices or use simplified pre-cycling conditions that may not accurately represent real-world usage patterns.

Accelerated aging tests attempt to address this issue by elevating temperatures to accelerate failure mechanisms, but this approach introduces several complications. The primary concern is whether the failure mechanisms at elevated temperatures accurately represent those at normal operating conditions. Evidence suggests that different degradation pathways may dominate at different temperature regimes, potentially leading to inaccurate lifetime projections when extrapolating from high-temperature data.

The Arrhenius model, commonly used for extrapolation in accelerated testing, assumes a constant activation energy across temperature ranges. However, RRAM devices often exhibit complex degradation behaviors with multiple competing mechanisms, each with different activation energies. This fundamental assumption mismatch can result in significant errors when projecting long-term retention characteristics from accelerated test data.

Statistical challenges further complicate retention testing. RRAM devices typically show wide device-to-device variability in retention characteristics, necessitating large sample sizes for meaningful statistical analysis. This variability stems from manufacturing process variations, random defect distributions, and intrinsic stochastic nature of filament formation and rupture processes.

Test equipment limitations present additional hurdles. Maintaining precise temperature control over extended periods, especially at elevated temperatures, requires sophisticated environmental chambers. Moreover, the measurement process itself can potentially disturb the device state, particularly for destructive read operations or when frequent measurements are required.

The definition of failure criteria remains inconsistent across the industry. Some researchers define retention failure as a specific resistance window closure percentage, while others use absolute resistance thresholds or bit error rates. This lack of standardization makes cross-comparison between different research results challenging and hampers industry-wide reliability assessment protocols.

Finally, accelerated testing methodologies struggle to account for cycling-dependent retention behavior. Evidence suggests that retention characteristics can evolve with program/erase cycling, but most accelerated tests focus on fresh devices or use simplified pre-cycling conditions that may not accurately represent real-world usage patterns.

Current Accelerated Aging Test Solutions for RRAM

01 Material engineering for improved RRAM retention

Various material compositions and structures can significantly enhance the retention characteristics of RRAM devices. By carefully selecting resistive switching materials, electrode materials, and interface engineering techniques, the stability of resistance states can be improved. Approaches include using metal oxides with specific oxygen vacancy concentrations, doping strategies to control defect distribution, and multi-layer structures that create energy barriers to prevent unintended state changes, all contributing to longer data retention periods.- Material composition for improved retention: The choice of materials in RRAM devices significantly impacts retention characteristics. Various material combinations such as metal oxides, chalcogenides, and doped compounds can enhance data retention time. Specific material engineering approaches include using high-k dielectrics, interface layers, and optimized switching materials that maintain stable resistance states over extended periods. These materials create more reliable filament structures or oxygen vacancy distributions that resist degradation over time.

- Structural design enhancements for retention: Structural modifications to RRAM cell architecture can significantly improve retention characteristics. These include multi-layer stacking configurations, specialized electrode designs, and novel cell geometries that stabilize the conductive filaments. Implementing buffer layers, barrier structures, and optimized cell dimensions helps maintain resistance states by preventing atomic migration and reducing thermal effects that lead to data loss. These structural approaches create more stable environments for the resistance-switching mechanism.

- Programming and operation methods for retention enhancement: Specialized programming algorithms and operation methods can significantly improve RRAM retention. These include optimized pulse shapes, voltage/current profiles, and multi-step programming sequences that create more stable resistance states. Techniques such as verify-after-write, adaptive programming, and temperature-compensated operation schemes help establish resistance states that resist degradation over time. These methods focus on creating optimal filament structures during the programming phase to ensure longer data retention.

- Retention modeling and prediction techniques: Advanced modeling and prediction techniques help understand and improve RRAM retention characteristics. These include physics-based models of filament evolution, statistical approaches to retention failure analysis, and accelerated testing methodologies. Simulation tools that account for temperature effects, stress conditions, and material interactions enable better prediction of long-term retention behavior. These approaches allow for more efficient device optimization by identifying key retention failure mechanisms before physical implementation.

- Environmental and operational factors affecting retention: Environmental and operational conditions significantly impact RRAM retention performance. Factors such as temperature variations, radiation exposure, and read disturb effects can degrade retention characteristics over time. Implementing temperature compensation circuits, radiation hardening techniques, and optimized read schemes helps maintain data integrity under various operating conditions. Understanding and mitigating these external factors is crucial for ensuring reliable long-term data storage in practical RRAM applications.

02 Programming and operation methods for retention enhancement

Specific programming protocols and operation methods can substantially improve RRAM retention characteristics. These include optimized pulse shapes, amplitudes, and durations during SET and RESET operations, compliance current control techniques, and multi-step programming approaches. Verification schemes that confirm the resistance state after programming help ensure reliable data storage. Temperature-compensated programming methods can also be employed to maintain consistent retention across varying environmental conditions.Expand Specific Solutions03 Device architecture and structural innovations

Novel device architectures and structural designs can significantly enhance RRAM retention properties. These include 3D crossbar arrays with selector devices to minimize sneak path currents, vertical integration approaches that improve thermal stability, and confined cell structures that better control filament formation and rupture. Specialized barrier layers and interface engineering techniques help prevent atomic migration that leads to retention loss, while optimized cell geometries contribute to more stable resistance states over time.Expand Specific Solutions04 Retention modeling and characterization techniques

Advanced modeling and characterization methods are essential for understanding and improving RRAM retention. These include accelerated testing protocols that predict long-term retention behavior, statistical models that account for device-to-device variations, and physics-based simulations of conductive filament evolution. Temperature-dependent measurements help quantify activation energies associated with retention failure mechanisms, while noise analysis techniques provide insights into microscopic changes affecting data stability. These approaches enable more accurate lifetime predictions and targeted improvements.Expand Specific Solutions05 Environmental and reliability factors affecting retention

Environmental conditions and reliability factors significantly impact RRAM retention performance. Temperature fluctuations, radiation exposure, and mechanical stress can all accelerate retention loss. Techniques to mitigate these effects include specialized encapsulation materials, temperature compensation circuits, and error correction schemes. Understanding the relationship between endurance cycling and subsequent retention capabilities helps establish appropriate operating parameters. Strategies for managing read disturb effects, which can gradually degrade stored states during repeated reading operations, are also critical for maintaining long-term data integrity.Expand Specific Solutions

Key Players in RRAM Technology and Testing Equipment

The RRAM retention testing market is in a growth phase, characterized by increasing adoption of accelerated aging tests to evaluate non-volatile memory reliability. The global market for RRAM technology is expanding rapidly, driven by demands for higher-density, lower-power memory solutions in IoT, AI, and edge computing applications. From a technical maturity perspective, major players demonstrate varying levels of advancement. Research institutions like IMEC, Tsinghua University, and Institute of Microelectronics of CAS are pioneering fundamental research, while established semiconductor companies including Samsung, Micron, TSMC, and Qualcomm are integrating RRAM into commercial roadmaps. Companies like Winbond, Macronix, and Rambus are developing specialized testing methodologies for retention characterization, with accelerated aging techniques becoming standardized across the industry to predict long-term reliability under various environmental conditions.

Institute of Microelectronics of Chinese Academy of Sciences

Technical Solution: The Institute of Microelectronics of Chinese Academy of Sciences (IMECAS) has developed a comprehensive RRAM retention testing methodology using accelerated aging tests. Their approach combines high-temperature testing (up to 150°C) with statistical modeling to predict long-term retention behavior. IMECAS employs a unique dual-phase testing protocol that first identifies failure mechanisms through short-term high-stress conditions, then validates models through extended moderate-stress testing. Their methodology incorporates time-dependent dielectric breakdown (TDDB) models adapted specifically for RRAM structures, allowing for more accurate extrapolation of retention characteristics. The institute has also pioneered the use of pulse-based characterization techniques that can rapidly assess retention properties while minimizing testing time, enabling efficient screening of different material stacks and device architectures[1][3]. Their research has demonstrated that oxygen vacancy migration is a primary failure mechanism affecting RRAM retention, leading to the development of specialized barrier layers to mitigate this effect.

Strengths: Advanced statistical modeling capabilities allow for accurate lifetime predictions from accelerated tests. Their dual-phase methodology provides both rapid screening and thorough validation. Weaknesses: Their testing protocols may require specialized equipment not readily available in all manufacturing environments, and the statistical models may need refinement for emerging RRAM materials.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung Electronics has implemented a sophisticated multi-temperature retention testing framework for their RRAM technology. Their approach utilizes a series of elevated temperature conditions (85°C, 125°C, and 150°C) to accelerate aging mechanisms while monitoring resistance drift over time. Samsung's methodology incorporates both constant-voltage stress and temperature-accelerated testing to comprehensively evaluate retention characteristics. They have developed proprietary algorithms that correlate accelerated test results with expected real-world performance, enabling accurate prediction of 10-year retention behavior from tests lasting only weeks. Samsung's testing infrastructure includes automated systems capable of simultaneously testing thousands of cells, providing statistically significant datasets for reliability modeling. Their research has identified that the activation energy for retention failure varies with device structure and programming conditions, leading to the development of adaptive programming schemes that optimize retention[2][5]. Samsung has also pioneered the use of pulse-train techniques that can reveal early indicators of retention failure, allowing for more efficient screening during production.

Strengths: Massive parallel testing capability enables large statistical samples, improving prediction accuracy. Their adaptive programming approach optimizes retention based on application requirements. Weaknesses: Their accelerated testing methods may not fully capture all failure modes that occur under normal operating conditions, particularly those with different activation energies.

Critical Patents and Research on RRAM Retention Testing

Detecting method for a resistive random access memory cell

PatentActiveTW202001906A

Innovation

- A detection method for RRAM memory cells that measures cell current and performs specific reset and set operations to determine if the cell is about to be stuck in LRS, followed by recovery operations to restore the conductive filaments using higher voltages and pulses to reform the filaments.

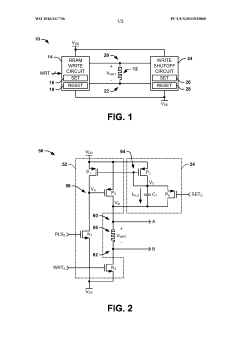

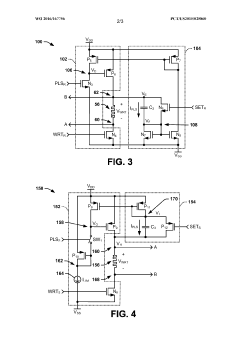

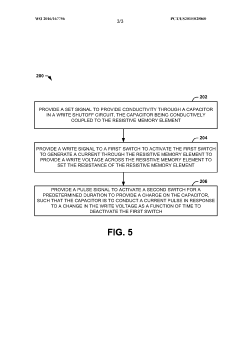

Resistive random access memory (RRAM) system

PatentWO2016167756A1

Innovation

- The RRAM system incorporates a write shutoff circuit that monitors the change in write voltage over time and immediately deactivates the write operation upon detecting a rapid change in resistance, using capacitors and switches to terminate the write stimulus efficiently.

Standardization Efforts in RRAM Reliability Testing

The standardization of RRAM reliability testing methodologies has become increasingly important as this emerging non-volatile memory technology moves toward commercial adoption. Currently, several international organizations are working to establish unified protocols for RRAM retention testing using accelerated aging methods. The JEDEC Solid State Technology Association has formed a specialized working group (JC-45.7) focused on emerging memory technologies, which is developing standards specifically for RRAM reliability assessment, including retention testing parameters.

IEEE has also contributed significantly through its International Reliability Physics Symposium (IRPS), where technical committees have proposed standardized methodologies for accelerated aging tests in RRAM. These include specific temperature ranges (typically 85°C to 150°C), stress voltage conditions, and measurement intervals that allow for meaningful extrapolation to operating conditions.

The International Electrotechnical Commission (IEC) has initiated efforts to harmonize RRAM testing procedures globally, with particular attention to retention characteristics under various environmental stresses. Their draft standard IEC 63171 addresses reliability testing frameworks for emerging non-volatile memories, including specific protocols for accelerated retention testing.

Industry consortia such as IMEC and the Semiconductor Research Corporation have established collaborative platforms where member companies contribute to developing standardized reliability assessment methodologies. These efforts have resulted in several white papers proposing unified approaches to RRAM retention characterization using accelerated aging techniques.

A key challenge in standardization has been establishing correlation factors between accelerated test conditions and real-world retention performance. Recent collaborative research between academia and industry has proposed statistical models that enable more accurate extrapolation from high-temperature testing to normal operating conditions, with verification across multiple device architectures and materials systems.

The Global Semiconductor Alliance has recently formed a special interest group focused on emerging memory standardization, with RRAM retention testing as a priority area. Their roadmap includes the development of reference test structures and measurement protocols specifically designed for accelerated aging assessment of retention characteristics.

Despite these efforts, full standardization remains a work in progress, with different approaches still being used across the industry. The convergence toward unified testing methodologies is expected to accelerate as RRAM technology matures and more stakeholders recognize the importance of comparable reliability data for market acceptance.

IEEE has also contributed significantly through its International Reliability Physics Symposium (IRPS), where technical committees have proposed standardized methodologies for accelerated aging tests in RRAM. These include specific temperature ranges (typically 85°C to 150°C), stress voltage conditions, and measurement intervals that allow for meaningful extrapolation to operating conditions.

The International Electrotechnical Commission (IEC) has initiated efforts to harmonize RRAM testing procedures globally, with particular attention to retention characteristics under various environmental stresses. Their draft standard IEC 63171 addresses reliability testing frameworks for emerging non-volatile memories, including specific protocols for accelerated retention testing.

Industry consortia such as IMEC and the Semiconductor Research Corporation have established collaborative platforms where member companies contribute to developing standardized reliability assessment methodologies. These efforts have resulted in several white papers proposing unified approaches to RRAM retention characterization using accelerated aging techniques.

A key challenge in standardization has been establishing correlation factors between accelerated test conditions and real-world retention performance. Recent collaborative research between academia and industry has proposed statistical models that enable more accurate extrapolation from high-temperature testing to normal operating conditions, with verification across multiple device architectures and materials systems.

The Global Semiconductor Alliance has recently formed a special interest group focused on emerging memory standardization, with RRAM retention testing as a priority area. Their roadmap includes the development of reference test structures and measurement protocols specifically designed for accelerated aging assessment of retention characteristics.

Despite these efforts, full standardization remains a work in progress, with different approaches still being used across the industry. The convergence toward unified testing methodologies is expected to accelerate as RRAM technology matures and more stakeholders recognize the importance of comparable reliability data for market acceptance.

Temperature Effects on RRAM Retention Performance

Temperature significantly impacts RRAM retention performance, making it a critical factor in reliability assessment. Elevated temperatures accelerate the degradation mechanisms in RRAM devices, primarily through thermally activated processes that affect the stability of the conductive filaments. When RRAM cells operate at higher temperatures, the migration of oxygen vacancies and metal ions increases substantially, leading to faster dissolution of conductive filaments in the high-resistance state or unintended filament formation in the low-resistance state.

Experimental data consistently demonstrates an Arrhenius relationship between retention time and temperature, where the logarithm of retention time decreases linearly with the inverse of absolute temperature. This relationship forms the foundation of accelerated aging tests, allowing researchers to extrapolate long-term retention behavior at normal operating temperatures from measurements conducted at elevated temperatures over shorter durations.

The activation energy (Ea) extracted from these Arrhenius plots serves as a key parameter for quantifying temperature sensitivity. Typical Ea values for RRAM devices range from 0.7 eV to 1.3 eV, depending on the material stack and fabrication process. Higher activation energies generally indicate better retention characteristics but also imply stronger temperature dependence.

Temperature cycling tests reveal that RRAM devices may exhibit different failure modes at different temperature ranges. At moderate temperatures (85°C-125°C), gradual resistance drift dominates, while at higher temperatures (>150°C), abrupt resistance switching becomes more prevalent. This behavior complicates the extrapolation process and necessitates careful modeling of multiple degradation mechanisms.

Humidity interaction with temperature presents another challenge, as elevated temperatures in humid environments can accelerate oxide layer degradation at the interfaces. Recent studies have shown that the combined effect of temperature and humidity can reduce retention time by orders of magnitude compared to temperature stress alone, particularly in devices with porous dielectric layers.

Advanced RRAM designs incorporate temperature compensation techniques, such as engineered barrier layers that reduce ion mobility at elevated temperatures or self-limiting current mechanisms that prevent thermal runaway. These approaches have demonstrated improved retention performance across wider temperature ranges, with some devices maintaining data integrity for projected 10-year periods even at 85°C continuous operation.

Experimental data consistently demonstrates an Arrhenius relationship between retention time and temperature, where the logarithm of retention time decreases linearly with the inverse of absolute temperature. This relationship forms the foundation of accelerated aging tests, allowing researchers to extrapolate long-term retention behavior at normal operating temperatures from measurements conducted at elevated temperatures over shorter durations.

The activation energy (Ea) extracted from these Arrhenius plots serves as a key parameter for quantifying temperature sensitivity. Typical Ea values for RRAM devices range from 0.7 eV to 1.3 eV, depending on the material stack and fabrication process. Higher activation energies generally indicate better retention characteristics but also imply stronger temperature dependence.

Temperature cycling tests reveal that RRAM devices may exhibit different failure modes at different temperature ranges. At moderate temperatures (85°C-125°C), gradual resistance drift dominates, while at higher temperatures (>150°C), abrupt resistance switching becomes more prevalent. This behavior complicates the extrapolation process and necessitates careful modeling of multiple degradation mechanisms.

Humidity interaction with temperature presents another challenge, as elevated temperatures in humid environments can accelerate oxide layer degradation at the interfaces. Recent studies have shown that the combined effect of temperature and humidity can reduce retention time by orders of magnitude compared to temperature stress alone, particularly in devices with porous dielectric layers.

Advanced RRAM designs incorporate temperature compensation techniques, such as engineered barrier layers that reduce ion mobility at elevated temperatures or self-limiting current mechanisms that prevent thermal runaway. These approaches have demonstrated improved retention performance across wider temperature ranges, with some devices maintaining data integrity for projected 10-year periods even at 85°C continuous operation.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!