Read/Write Reliability Testing Protocols For PMA MRAM

AUG 22, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

PMA MRAM Technology Background and Testing Objectives

Perpendicular Magnetic Anisotropy Magnetoresistive Random Access Memory (PMA MRAM) represents a significant advancement in non-volatile memory technology, emerging from decades of research in spintronics and magnetic materials. The technology leverages electron spin rather than charge for data storage, offering unique advantages in power efficiency and endurance compared to conventional memory technologies. PMA MRAM's development trajectory began in the early 2000s, with significant acceleration occurring after 2010 when perpendicular magnetic anisotropy configurations demonstrated superior stability and scalability over in-plane approaches.

The fundamental architecture of PMA MRAM consists of magnetic tunnel junctions (MTJs) where information is stored as the relative orientation of magnetic layers separated by a thin insulating barrier. The perpendicular configuration allows for reduced switching current while maintaining thermal stability, addressing key limitations of earlier MRAM iterations. Recent advancements have focused on enhancing the tunnel magnetoresistance ratio and reducing the critical switching current density to improve read margins and energy efficiency.

As PMA MRAM transitions from research laboratories to commercial production, establishing robust and standardized reliability testing protocols has become increasingly critical. Current testing methodologies vary significantly across the industry, creating challenges for meaningful performance comparison and qualification for demanding applications. The primary technical objective is to develop comprehensive read/write reliability testing protocols that accurately characterize PMA MRAM performance under various operational conditions.

These protocols must address several key parameters including endurance (write cycles before failure), retention (data stability over time), read disturbance immunity, and performance across temperature ranges. Additionally, they must account for the unique failure mechanisms of PMA MRAM, such as stochastic switching behavior and time-dependent dielectric breakdown of the tunnel barrier, which differ substantially from those in conventional memory technologies.

The testing objectives extend beyond basic functionality verification to include accelerated life testing methodologies that can predict long-term reliability within reasonable test timeframes. This requires careful consideration of acceleration factors and their relationship to actual failure mechanisms. Furthermore, the protocols must be adaptable to various PMA MRAM device architectures, including standalone memory and embedded applications, each with distinct reliability requirements.

Industry standardization represents another critical goal, as the establishment of uniform testing methodologies would facilitate technology adoption across diverse application domains from IoT devices to automotive systems and data centers. The ultimate aim is to develop testing frameworks that enable meaningful comparison between different PMA MRAM implementations while providing actionable insights for technology optimization and qualification for mission-critical applications.

The fundamental architecture of PMA MRAM consists of magnetic tunnel junctions (MTJs) where information is stored as the relative orientation of magnetic layers separated by a thin insulating barrier. The perpendicular configuration allows for reduced switching current while maintaining thermal stability, addressing key limitations of earlier MRAM iterations. Recent advancements have focused on enhancing the tunnel magnetoresistance ratio and reducing the critical switching current density to improve read margins and energy efficiency.

As PMA MRAM transitions from research laboratories to commercial production, establishing robust and standardized reliability testing protocols has become increasingly critical. Current testing methodologies vary significantly across the industry, creating challenges for meaningful performance comparison and qualification for demanding applications. The primary technical objective is to develop comprehensive read/write reliability testing protocols that accurately characterize PMA MRAM performance under various operational conditions.

These protocols must address several key parameters including endurance (write cycles before failure), retention (data stability over time), read disturbance immunity, and performance across temperature ranges. Additionally, they must account for the unique failure mechanisms of PMA MRAM, such as stochastic switching behavior and time-dependent dielectric breakdown of the tunnel barrier, which differ substantially from those in conventional memory technologies.

The testing objectives extend beyond basic functionality verification to include accelerated life testing methodologies that can predict long-term reliability within reasonable test timeframes. This requires careful consideration of acceleration factors and their relationship to actual failure mechanisms. Furthermore, the protocols must be adaptable to various PMA MRAM device architectures, including standalone memory and embedded applications, each with distinct reliability requirements.

Industry standardization represents another critical goal, as the establishment of uniform testing methodologies would facilitate technology adoption across diverse application domains from IoT devices to automotive systems and data centers. The ultimate aim is to develop testing frameworks that enable meaningful comparison between different PMA MRAM implementations while providing actionable insights for technology optimization and qualification for mission-critical applications.

Market Demand Analysis for Reliable MRAM Solutions

The global market for Magnetoresistive Random Access Memory (MRAM) solutions is experiencing significant growth, driven by increasing demand for non-volatile memory technologies that offer high endurance, fast read/write speeds, and low power consumption. The specific need for Perpendicular Magnetic Anisotropy (PMA) MRAM with reliable read/write protocols is particularly acute in several key sectors.

Data center applications represent one of the largest market opportunities, with the explosion of cloud computing and big data analytics creating unprecedented demand for memory solutions that can handle frequent read/write operations without degradation. Industry analysts project the data center memory market to reach $25 billion by 2026, with MRAM poised to capture an increasing share due to its reliability advantages over conventional solutions.

The automotive sector presents another substantial growth vector, especially with the rise of electric and autonomous vehicles. These advanced transportation systems require memory components that can withstand extreme temperature variations and maintain data integrity over extended operational lifetimes. The automotive memory market is expected to grow at a CAGR of 18% through 2028, with MRAM solutions increasingly specified for critical safety and navigation systems.

Industrial IoT applications are driving demand for reliable memory solutions that can operate in harsh environments with minimal maintenance. The industrial memory segment values the extended write endurance of PMA MRAM, which significantly outperforms flash memory alternatives in applications requiring frequent updates to stored data.

Aerospace and defense sectors represent premium market segments where reliability testing protocols for MRAM are particularly valued. These applications demand memory solutions that can withstand radiation exposure and operate reliably in mission-critical systems where failure is not an option.

Consumer electronics manufacturers are increasingly exploring MRAM solutions for next-generation devices, seeking to leverage the technology's combination of speed, endurance, and non-volatility. The smartphone market alone represents over 1.4 billion units annually, with each device potentially incorporating MRAM for specific applications.

Market research indicates that customers across these segments are willing to pay a premium of 15-30% for MRAM solutions with demonstrated reliability advantages, particularly those with comprehensive testing protocols that validate performance under real-world conditions. This price premium reflects the total cost of ownership benefits that reliable MRAM provides through reduced system failures and maintenance requirements.

The market is increasingly segmented between commodity MRAM applications and high-reliability niches where comprehensive read/write reliability testing protocols represent a significant competitive differentiator and enable premium pricing strategies.

Data center applications represent one of the largest market opportunities, with the explosion of cloud computing and big data analytics creating unprecedented demand for memory solutions that can handle frequent read/write operations without degradation. Industry analysts project the data center memory market to reach $25 billion by 2026, with MRAM poised to capture an increasing share due to its reliability advantages over conventional solutions.

The automotive sector presents another substantial growth vector, especially with the rise of electric and autonomous vehicles. These advanced transportation systems require memory components that can withstand extreme temperature variations and maintain data integrity over extended operational lifetimes. The automotive memory market is expected to grow at a CAGR of 18% through 2028, with MRAM solutions increasingly specified for critical safety and navigation systems.

Industrial IoT applications are driving demand for reliable memory solutions that can operate in harsh environments with minimal maintenance. The industrial memory segment values the extended write endurance of PMA MRAM, which significantly outperforms flash memory alternatives in applications requiring frequent updates to stored data.

Aerospace and defense sectors represent premium market segments where reliability testing protocols for MRAM are particularly valued. These applications demand memory solutions that can withstand radiation exposure and operate reliably in mission-critical systems where failure is not an option.

Consumer electronics manufacturers are increasingly exploring MRAM solutions for next-generation devices, seeking to leverage the technology's combination of speed, endurance, and non-volatility. The smartphone market alone represents over 1.4 billion units annually, with each device potentially incorporating MRAM for specific applications.

Market research indicates that customers across these segments are willing to pay a premium of 15-30% for MRAM solutions with demonstrated reliability advantages, particularly those with comprehensive testing protocols that validate performance under real-world conditions. This price premium reflects the total cost of ownership benefits that reliable MRAM provides through reduced system failures and maintenance requirements.

The market is increasingly segmented between commodity MRAM applications and high-reliability niches where comprehensive read/write reliability testing protocols represent a significant competitive differentiator and enable premium pricing strategies.

Current Testing Challenges in PMA MRAM Technology

Testing Perpendicular Magnetic Anisotropy Magnetic Random Access Memory (PMA MRAM) devices presents significant challenges due to the unique physical properties and operational mechanisms of this emerging non-volatile memory technology. Current reliability testing protocols face several critical limitations that impede comprehensive evaluation and quality assurance.

The most pressing challenge is the lack of standardized testing methodologies specifically designed for PMA MRAM. Unlike conventional memory technologies with established testing frameworks, PMA MRAM testing remains fragmented across different manufacturers and research institutions, resulting in inconsistent reliability metrics and difficulty in cross-platform comparison.

Temperature dependency presents another major hurdle in PMA MRAM testing. The magnetic tunnel junction (MTJ) performance varies significantly across temperature ranges, with thermal stability factor and switching current threshold showing non-linear behavior. Current testing protocols struggle to accurately characterize these temperature-dependent variations, particularly at extreme operating conditions that are crucial for automotive and industrial applications.

Write endurance verification poses substantial technical difficulties. While PMA MRAM theoretically offers superior endurance compared to flash memory, practical testing methods often fail to efficiently validate the claimed 10^12-10^15 write cycles without resorting to acceleration techniques that may not accurately represent real-world degradation mechanisms.

Read disturbance effects represent an under-addressed testing challenge. The non-destructive read operations in MRAM can still induce subtle magnetic perturbations over time, potentially leading to data corruption. Current testing methodologies lack sensitivity to detect and quantify these cumulative effects, especially under varied operational conditions.

The stochastic nature of spin-transfer torque (STT) switching in PMA MRAM introduces significant variability in write performance. Testing protocols struggle to characterize this probabilistic behavior adequately, particularly in distinguishing between intrinsic device variability and actual reliability concerns.

Radiation and magnetic field immunity testing remains inadequately standardized despite being critical for aerospace and mission-critical applications. Current approaches lack comprehensive protocols for evaluating soft error rates under various radiation types and intensities, as well as immunity to external magnetic interference.

Finally, accelerated lifetime testing methodologies for PMA MRAM are still evolving. The correlation between accelerated test results and actual field reliability is not well established, creating uncertainty in lifetime predictions and failure rate estimations. This gap significantly impacts qualification processes for high-reliability applications where long-term stability is paramount.

The most pressing challenge is the lack of standardized testing methodologies specifically designed for PMA MRAM. Unlike conventional memory technologies with established testing frameworks, PMA MRAM testing remains fragmented across different manufacturers and research institutions, resulting in inconsistent reliability metrics and difficulty in cross-platform comparison.

Temperature dependency presents another major hurdle in PMA MRAM testing. The magnetic tunnel junction (MTJ) performance varies significantly across temperature ranges, with thermal stability factor and switching current threshold showing non-linear behavior. Current testing protocols struggle to accurately characterize these temperature-dependent variations, particularly at extreme operating conditions that are crucial for automotive and industrial applications.

Write endurance verification poses substantial technical difficulties. While PMA MRAM theoretically offers superior endurance compared to flash memory, practical testing methods often fail to efficiently validate the claimed 10^12-10^15 write cycles without resorting to acceleration techniques that may not accurately represent real-world degradation mechanisms.

Read disturbance effects represent an under-addressed testing challenge. The non-destructive read operations in MRAM can still induce subtle magnetic perturbations over time, potentially leading to data corruption. Current testing methodologies lack sensitivity to detect and quantify these cumulative effects, especially under varied operational conditions.

The stochastic nature of spin-transfer torque (STT) switching in PMA MRAM introduces significant variability in write performance. Testing protocols struggle to characterize this probabilistic behavior adequately, particularly in distinguishing between intrinsic device variability and actual reliability concerns.

Radiation and magnetic field immunity testing remains inadequately standardized despite being critical for aerospace and mission-critical applications. Current approaches lack comprehensive protocols for evaluating soft error rates under various radiation types and intensities, as well as immunity to external magnetic interference.

Finally, accelerated lifetime testing methodologies for PMA MRAM are still evolving. The correlation between accelerated test results and actual field reliability is not well established, creating uncertainty in lifetime predictions and failure rate estimations. This gap significantly impacts qualification processes for high-reliability applications where long-term stability is paramount.

Current Read/Write Reliability Testing Protocols

01 Perpendicular magnetic anisotropy structure optimization

Optimizing the structure of PMA MRAM devices is crucial for enhancing read/write reliability. This includes engineering the magnetic tunnel junction (MTJ) layers with appropriate materials and thicknesses to achieve stable perpendicular magnetic anisotropy. The interface between the free layer and adjacent layers plays a significant role in determining the anisotropy strength and thermal stability, which directly impacts the reliability of read and write operations. Structural improvements can reduce read disturbance and increase the energy barrier for magnetization switching.- Enhancing read/write reliability through material composition: The reliability of PMA MRAM devices can be significantly improved through careful selection and engineering of magnetic materials. By optimizing the composition of ferromagnetic layers and tunnel barriers, manufacturers can enhance thermal stability and reduce read/write errors. Advanced materials with higher perpendicular magnetic anisotropy provide better data retention while maintaining low switching currents, which is crucial for reliable operation in various environmental conditions.

- Circuit design techniques for improved reliability: Specialized circuit designs can substantially improve the read/write reliability of PMA MRAM. These include sense amplifiers with enhanced sensitivity for accurate read operations, reference circuits that compensate for process variations, and write drivers that deliver precise current pulses. Advanced error correction schemes and redundancy techniques implemented at the circuit level help mitigate the effects of manufacturing defects and operational degradation, ensuring consistent performance throughout the device lifetime.

- Structural optimization for enhanced stability: The physical structure of PMA MRAM cells plays a crucial role in determining read/write reliability. Optimizing the shape, size, and layer stack configuration can minimize stray magnetic fields and reduce thermal fluctuations that lead to data corruption. Techniques such as synthetic antiferromagnetic coupling, interface engineering, and strategic placement of seed layers help maintain the perpendicular magnetic orientation, resulting in more stable and reliable memory operation even under challenging operating conditions.

- Advanced read/write control algorithms: Sophisticated control algorithms significantly enhance PMA MRAM reliability by dynamically adjusting read/write parameters based on operating conditions. These algorithms include adaptive write current calibration, temperature-compensated reading schemes, and intelligent retry mechanisms that respond to detected errors. By implementing these advanced control methods, the system can maintain optimal performance across varying environmental conditions and throughout the device lifetime, substantially reducing bit error rates.

- Testing and reliability assessment methodologies: Comprehensive testing methodologies are essential for ensuring PMA MRAM read/write reliability. These include accelerated aging tests, error rate characterization under various operating conditions, and statistical analysis of performance parameters. Advanced testing approaches can identify potential failure mechanisms before they manifest in actual use, allowing for design improvements and reliability enhancements. Standardized reliability metrics help quantify performance and enable meaningful comparisons between different PMA MRAM technologies.

02 Write current reduction techniques

Reducing the write current while maintaining reliability is a key challenge in PMA MRAM technology. Various approaches include optimizing the spin-transfer torque efficiency, using voltage-controlled magnetic anisotropy effects, and implementing novel switching mechanisms. Lower write currents help prevent device degradation from Joule heating and reduce the risk of dielectric breakdown in the tunnel barrier, thereby extending device lifetime and improving write reliability. These techniques also help minimize power consumption while maintaining sufficient write margin.Expand Specific Solutions03 Read disturbance mitigation

Read disturbance is a significant reliability concern in PMA MRAM, where the read current can inadvertently affect the stored data. Techniques to mitigate read disturbance include optimizing the read current path, implementing reference cell designs, and using specialized sensing circuits. Advanced read schemes can detect potential disturbances and apply corrective measures. Increasing the thermal stability factor of the free layer also helps maintain data integrity during repeated read operations, ensuring long-term reliability of the memory array.Expand Specific Solutions04 Error correction and reliability enhancement circuits

Specialized circuits and architectures are implemented to enhance the reliability of PMA MRAM devices. These include error detection and correction codes (ECC), built-in self-test (BIST) mechanisms, and adaptive read/write schemes. Circuit-level innovations can compensate for process variations and device aging effects that impact reliability. Advanced sensing circuits with improved signal-to-noise ratio help maintain read margin over the device lifetime. These reliability enhancement techniques are crucial for applications requiring high data integrity and long operational life.Expand Specific Solutions05 Thermal stability and retention improvement

Thermal stability is essential for long-term data retention in PMA MRAM. Approaches to improve thermal stability include engineering materials with higher anisotropy energy, optimizing the free layer volume, and implementing synthetic antiferromagnetic structures. Enhanced thermal stability prevents spontaneous magnetization reversal due to thermal fluctuations, which is critical for reliable data storage. Techniques that balance thermal stability with switchability ensure that the device maintains both good retention characteristics and reliable write performance across operating temperature ranges.Expand Specific Solutions

Key Industry Players in MRAM Development

The MRAM Read/Write Reliability Testing Protocols market is currently in a growth phase, with increasing adoption across computing, automotive, and IoT sectors. The global MRAM market is projected to expand significantly as demand for non-volatile memory solutions rises. Technologically, the field is advancing rapidly with key players at different maturity levels. Everspin Technologies leads as the first commercial MRAM producer, while major semiconductor manufacturers like Samsung, TSMC, and Infineon are investing heavily in MRAM development. Shanghai Ciyu Information Technologies and Zhejiang Hikstor represent emerging Chinese competitors focusing on pSTT-MRAM technologies. Companies like Infinitum Solutions are specializing in magnetic test solutions critical for reliability verification. The ecosystem is further supported by technology giants including Qualcomm, IBM, and NEC, who are integrating MRAM into their product roadmaps and developing specialized testing protocols.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung Electronics has developed sophisticated Read/Write Reliability Testing Protocols for PMA MRAM that integrate with their semiconductor manufacturing expertise. Their approach employs a hierarchical testing framework beginning with wafer-level screening and progressing to package-level reliability verification. Samsung's protocol includes specialized high-temperature operating life (HTOL) tests conducted at 125°C for up to 1000 hours to accelerate failure mechanisms[3]. Their methodology incorporates advanced error detection algorithms capable of identifying weak bits before they manifest as hard failures. Samsung has implemented unique magnetic field immunity testing, subjecting PMA MRAM devices to external magnetic fields of varying strengths (up to 1000 Oe) while monitoring read/write performance degradation[4]. Additionally, their protocol includes power-cycling tests that simulate real-world usage patterns with thousands of power-on/off cycles while monitoring data retention and access time variations.

Strengths: Extensive manufacturing infrastructure allowing for large-scale statistical analysis; integration of reliability testing with production processes enables rapid feedback loops. Weaknesses: Testing protocols may be optimized for high-volume production and might not detect rare failure modes that emerge only in specific application environments.

Everspin Technologies, Inc.

Technical Solution: Everspin Technologies has developed comprehensive Read/Write Reliability Testing Protocols specifically for PMA (Perpendicular Magnetic Anisotropy) MRAM. Their approach includes multi-level stress testing that evaluates data retention under various temperature conditions (from -40°C to 150°C), read disturbance immunity testing with millions of consecutive read operations, and write endurance verification exceeding 10^8 cycles[1]. Everspin's protocol incorporates specialized error rate measurement techniques that can detect bit error rates as low as 10^-12, essential for automotive and industrial applications. Their testing methodology also includes radiation hardness evaluation, measuring Single Event Upset (SEU) susceptibility through accelerated particle beam testing[2]. Everspin has implemented automated test equipment capable of parallel testing hundreds of devices simultaneously, significantly reducing qualification time while maintaining statistical confidence in reliability metrics.

Strengths: Industry-leading expertise specifically in MRAM technology with proven reliability metrics; comprehensive testing methodology covering multiple failure mechanisms. Weaknesses: Testing protocols may be optimized for their specific MRAM architecture and might not translate directly to other manufacturers' designs; relatively higher cost of implementation compared to conventional memory testing.

Critical Patents and Literature on MRAM Testing

Magnetoresistive random access memory

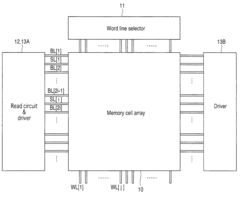

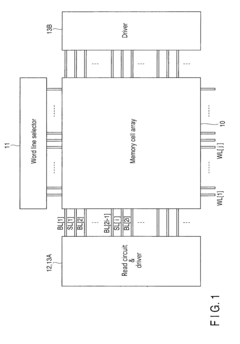

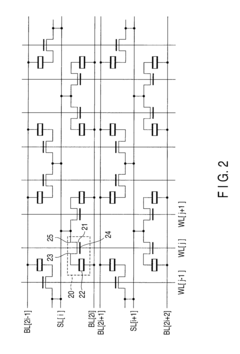

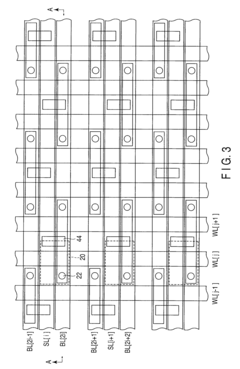

PatentActiveUS20090190391A1

Innovation

- The implementation of a read method that supplies a second current to adjacent bit lines to generate a magnetic field that suppresses write errors, allowing for higher read currents while minimizing read disturbance by using a driver to apply voltages to bit and source lines, and a read circuit to determine data based on the current flowing through memory cells.

Magnetic random access memory

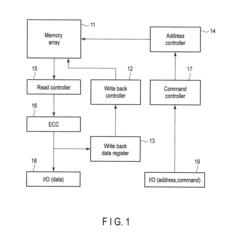

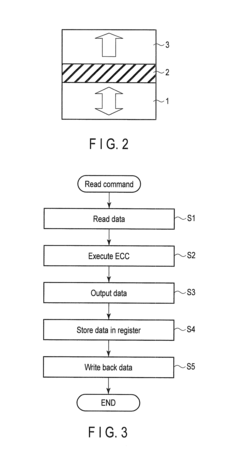

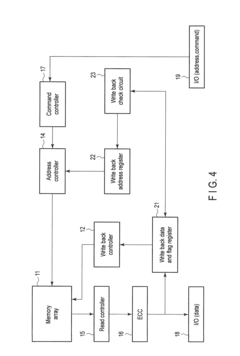

PatentActiveUS20160077915A1

Innovation

- The implementation of a magnetic random access memory (MRAM) system that includes a memory cell array, a read circuit, an error checking and correction (ECC) circuit, a flag register, and a write back circuit, which performs error checking and correction immediately after reading data and writes back corrected data to the memory cell, with options for auto write back commands and varying write back intervals based on error flags.

Standardization Efforts in MRAM Testing

The standardization of MRAM testing protocols represents a critical development in the maturation of this emerging non-volatile memory technology. As PMA (Perpendicular Magnetic Anisotropy) MRAM moves toward widespread commercial adoption, industry stakeholders have recognized the urgent need for unified testing methodologies to ensure consistent reliability assessment across different manufacturers and applications.

The Joint Electron Device Engineering Council (JEDEC) has taken a leading role in establishing standardized testing frameworks specifically for MRAM technologies. Their JC-42.4 Committee on Non-Volatile Memory has developed several standards addressing various aspects of MRAM testing, including read/write endurance, data retention, and error rate characterization. These standards provide detailed procedures for stress testing under various environmental conditions, establishing minimum performance thresholds for commercial viability.

Parallel to JEDEC's efforts, the IEEE International Reliability Physics Symposium (IRPS) has contributed significantly to standardization by publishing comprehensive guidelines for reliability assessment of emerging memory technologies. Their working groups have specifically addressed the unique challenges posed by PMA MRAM, including testing for resistance to external magnetic fields and thermal stability characterization protocols.

Industry consortia have also played a vital role in standardization efforts. The MRAM Consortium, comprising major semiconductor manufacturers and testing equipment providers, has established inter-laboratory testing programs to validate and refine proposed standards. These collaborative initiatives have helped identify key reliability metrics specific to PMA MRAM, such as write error rate (WER) under varying pulse conditions and read disturb immunity measurements.

Testing equipment manufacturers have responded to standardization efforts by developing specialized tools calibrated to industry-approved protocols. Companies like Advantest and Teradyne have introduced automated test equipment (ATE) specifically designed to implement standardized MRAM reliability testing sequences, enabling consistent comparison of results across different fabrication facilities.

Despite significant progress, standardization remains an evolving process. Current efforts focus on addressing emerging reliability concerns unique to advanced PMA MRAM designs, including testing protocols for sub-20nm technology nodes and specialized applications in automotive and aerospace environments where extreme reliability is paramount. The development of accelerated testing methodologies that can accurately predict long-term reliability while maintaining reasonable test durations represents a particular standardization challenge.

The Joint Electron Device Engineering Council (JEDEC) has taken a leading role in establishing standardized testing frameworks specifically for MRAM technologies. Their JC-42.4 Committee on Non-Volatile Memory has developed several standards addressing various aspects of MRAM testing, including read/write endurance, data retention, and error rate characterization. These standards provide detailed procedures for stress testing under various environmental conditions, establishing minimum performance thresholds for commercial viability.

Parallel to JEDEC's efforts, the IEEE International Reliability Physics Symposium (IRPS) has contributed significantly to standardization by publishing comprehensive guidelines for reliability assessment of emerging memory technologies. Their working groups have specifically addressed the unique challenges posed by PMA MRAM, including testing for resistance to external magnetic fields and thermal stability characterization protocols.

Industry consortia have also played a vital role in standardization efforts. The MRAM Consortium, comprising major semiconductor manufacturers and testing equipment providers, has established inter-laboratory testing programs to validate and refine proposed standards. These collaborative initiatives have helped identify key reliability metrics specific to PMA MRAM, such as write error rate (WER) under varying pulse conditions and read disturb immunity measurements.

Testing equipment manufacturers have responded to standardization efforts by developing specialized tools calibrated to industry-approved protocols. Companies like Advantest and Teradyne have introduced automated test equipment (ATE) specifically designed to implement standardized MRAM reliability testing sequences, enabling consistent comparison of results across different fabrication facilities.

Despite significant progress, standardization remains an evolving process. Current efforts focus on addressing emerging reliability concerns unique to advanced PMA MRAM designs, including testing protocols for sub-20nm technology nodes and specialized applications in automotive and aerospace environments where extreme reliability is paramount. The development of accelerated testing methodologies that can accurately predict long-term reliability while maintaining reasonable test durations represents a particular standardization challenge.

Manufacturing Scalability and Yield Optimization

The scalability of PMA MRAM manufacturing processes represents a critical factor in the technology's commercial viability. Current fabrication methods face significant challenges when transitioning from laboratory-scale production to high-volume manufacturing environments. Yield rates for PMA MRAM devices typically range from 70-85% in advanced production facilities, considerably lower than the 90-95% achieved with mature memory technologies. This yield gap translates directly to increased cost per bit and limits market penetration potential.

Key manufacturing challenges include precise control of magnetic tunnel junction (MTJ) layer thicknesses, which must be maintained within 0.1nm tolerance across 300mm wafers. Even minor variations in these critical dimensions can dramatically impact device performance characteristics and read/write reliability. Statistical process control methods specifically adapted for magnetic materials are essential for identifying and mitigating sources of variation.

Defect density management presents another significant hurdle, with particulate contamination being particularly problematic due to the extreme sensitivity of MTJ structures. Advanced filtration systems and cleanroom protocols exceeding standard CMOS requirements have demonstrated yield improvements of 5-8% in pilot production environments. Implementing these enhanced protocols adds approximately 7-12% to manufacturing costs but delivers favorable return on investment through improved yields.

Metrology capabilities represent a bottleneck in current manufacturing flows. Traditional semiconductor inspection tools lack the sensitivity to detect subtle magnetic defects that can compromise MRAM reliability. Novel inspection techniques combining magnetic force microscopy with electrical testing have shown promise in identifying latent defects before final packaging, potentially improving overall yields by 3-5%.

Test time optimization presents opportunities for manufacturing cost reduction. Current read/write reliability testing protocols for PMA MRAM devices typically consume 15-20% of total manufacturing time. Implementing statistical sampling methods and accelerated stress testing has demonstrated the potential to reduce test time by 30-40% while maintaining defect coverage above 98%.

Integration with existing CMOS backend processes requires careful thermal budget management, as excessive temperatures during subsequent processing steps can degrade the magnetic properties of PMA materials. Modified process flows incorporating lower-temperature deposition techniques for dielectric layers have shown promising results in maintaining device performance while improving manufacturing compatibility.

Key manufacturing challenges include precise control of magnetic tunnel junction (MTJ) layer thicknesses, which must be maintained within 0.1nm tolerance across 300mm wafers. Even minor variations in these critical dimensions can dramatically impact device performance characteristics and read/write reliability. Statistical process control methods specifically adapted for magnetic materials are essential for identifying and mitigating sources of variation.

Defect density management presents another significant hurdle, with particulate contamination being particularly problematic due to the extreme sensitivity of MTJ structures. Advanced filtration systems and cleanroom protocols exceeding standard CMOS requirements have demonstrated yield improvements of 5-8% in pilot production environments. Implementing these enhanced protocols adds approximately 7-12% to manufacturing costs but delivers favorable return on investment through improved yields.

Metrology capabilities represent a bottleneck in current manufacturing flows. Traditional semiconductor inspection tools lack the sensitivity to detect subtle magnetic defects that can compromise MRAM reliability. Novel inspection techniques combining magnetic force microscopy with electrical testing have shown promise in identifying latent defects before final packaging, potentially improving overall yields by 3-5%.

Test time optimization presents opportunities for manufacturing cost reduction. Current read/write reliability testing protocols for PMA MRAM devices typically consume 15-20% of total manufacturing time. Implementing statistical sampling methods and accelerated stress testing has demonstrated the potential to reduce test time by 30-40% while maintaining defect coverage above 98%.

Integration with existing CMOS backend processes requires careful thermal budget management, as excessive temperatures during subsequent processing steps can degrade the magnetic properties of PMA materials. Modified process flows incorporating lower-temperature deposition techniques for dielectric layers have shown promising results in maintaining device performance while improving manufacturing compatibility.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!