The design of on-chip plasticity mechanisms in FeFET arrays.

SEP 3, 202510 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

FeFET Plasticity Mechanisms Background and Objectives

Ferroelectric Field-Effect Transistors (FeFETs) have emerged as promising candidates for next-generation non-volatile memory and neuromorphic computing applications due to their unique properties. The evolution of FeFET technology can be traced back to the 1950s with the discovery of ferroelectric materials, but significant advancements have occurred primarily in the last two decades with the integration of ferroelectric materials into conventional CMOS processes.

The technological trajectory of FeFETs has been marked by several key developments, including the successful incorporation of ferroelectric hafnium oxide (HfO2) into the gate stack, which solved previous scaling challenges associated with traditional ferroelectric materials like lead zirconate titanate (PZT). This breakthrough enabled the fabrication of FeFETs with dimensions compatible with advanced technology nodes, opening new possibilities for high-density memory and computing architectures.

On-chip plasticity mechanisms in FeFET arrays represent a critical advancement in neuromorphic computing, as they enable the implementation of synaptic functions directly within the memory elements. These mechanisms aim to mimic the biological processes of long-term potentiation (LTP) and long-term depression (LTD) that form the basis of learning and memory in biological neural systems.

The primary technical objectives in designing on-chip plasticity mechanisms for FeFET arrays include achieving precise control over the polarization state of the ferroelectric layer, enabling multi-level cell operation for analog weight storage, and ensuring reliable programming and retention characteristics. Additionally, minimizing energy consumption during weight updates and maximizing endurance are crucial considerations for practical neuromorphic systems.

Current research focuses on developing novel programming schemes that can accurately modulate the ferroelectric domain configuration within the FeFET structure. These schemes must address challenges related to the non-linear polarization dynamics of ferroelectric materials and the impact of device variability on learning performance.

Another important objective is the development of peripheral circuitry that can efficiently implement various learning rules, such as spike-timing-dependent plasticity (STDP), directly on-chip. This requires careful co-design of the FeFET devices and their associated control electronics to achieve the desired plasticity behavior while maintaining compact footprint and low power operation.

The ultimate goal of this technology is to enable large-scale neuromorphic systems that can perform complex pattern recognition, classification, and inference tasks with significantly higher energy efficiency compared to conventional von Neumann architectures. By integrating memory and computation within the same physical elements, FeFET-based neuromorphic systems aim to overcome the memory bottleneck that limits the performance of traditional computing paradigms.

The technological trajectory of FeFETs has been marked by several key developments, including the successful incorporation of ferroelectric hafnium oxide (HfO2) into the gate stack, which solved previous scaling challenges associated with traditional ferroelectric materials like lead zirconate titanate (PZT). This breakthrough enabled the fabrication of FeFETs with dimensions compatible with advanced technology nodes, opening new possibilities for high-density memory and computing architectures.

On-chip plasticity mechanisms in FeFET arrays represent a critical advancement in neuromorphic computing, as they enable the implementation of synaptic functions directly within the memory elements. These mechanisms aim to mimic the biological processes of long-term potentiation (LTP) and long-term depression (LTD) that form the basis of learning and memory in biological neural systems.

The primary technical objectives in designing on-chip plasticity mechanisms for FeFET arrays include achieving precise control over the polarization state of the ferroelectric layer, enabling multi-level cell operation for analog weight storage, and ensuring reliable programming and retention characteristics. Additionally, minimizing energy consumption during weight updates and maximizing endurance are crucial considerations for practical neuromorphic systems.

Current research focuses on developing novel programming schemes that can accurately modulate the ferroelectric domain configuration within the FeFET structure. These schemes must address challenges related to the non-linear polarization dynamics of ferroelectric materials and the impact of device variability on learning performance.

Another important objective is the development of peripheral circuitry that can efficiently implement various learning rules, such as spike-timing-dependent plasticity (STDP), directly on-chip. This requires careful co-design of the FeFET devices and their associated control electronics to achieve the desired plasticity behavior while maintaining compact footprint and low power operation.

The ultimate goal of this technology is to enable large-scale neuromorphic systems that can perform complex pattern recognition, classification, and inference tasks with significantly higher energy efficiency compared to conventional von Neumann architectures. By integrating memory and computation within the same physical elements, FeFET-based neuromorphic systems aim to overcome the memory bottleneck that limits the performance of traditional computing paradigms.

Market Analysis for On-Chip Plasticity Solutions

The market for on-chip plasticity solutions in FeFET arrays is experiencing significant growth, driven by the increasing demand for neuromorphic computing systems that can efficiently process complex AI workloads. Current market estimates value the neuromorphic chip sector at approximately $2.5 billion, with projections indicating a compound annual growth rate of 20% through 2028. On-chip plasticity mechanisms, which enable hardware-based learning capabilities, represent a critical subsegment of this market with particularly strong growth potential.

The primary market drivers for FeFET-based plasticity solutions include the exponential growth in edge AI applications, increasing power constraints in data centers, and the fundamental limitations of traditional von Neumann computing architectures for neural network implementation. Organizations across various sectors are seeking more energy-efficient computing solutions that can perform complex learning tasks with minimal power consumption, creating substantial market pull for FeFET technology.

Industry analysis reveals distinct market segments for on-chip plasticity solutions. The largest current segment is research institutions and semiconductor R&D departments, accounting for approximately 45% of market demand. Commercial applications in edge computing devices represent about 30% of the market, while data center applications constitute roughly 15%. The remaining 10% encompasses specialized applications in aerospace, defense, and medical devices where power efficiency and reliability are paramount concerns.

Geographically, North America leads the market with approximately 40% share, followed by Asia-Pacific at 35% and Europe at 20%. China has emerged as a particularly aggressive investor in this technology, with government initiatives allocating substantial funding to neuromorphic computing research and development.

Customer needs analysis indicates that the most valued attributes of on-chip plasticity solutions are energy efficiency (cited by 78% of potential customers), integration capability with existing CMOS processes (65%), reliability and endurance (60%), and scalability (55%). The ability to implement various learning algorithms directly in hardware represents a key differentiator for FeFET-based solutions compared to alternative technologies.

Market barriers include high initial manufacturing costs, technical challenges in scaling FeFET arrays while maintaining performance, and competition from alternative neuromorphic computing approaches such as memristors and phase-change memory. Additionally, the lack of standardized benchmarking methodologies for neuromorphic systems creates uncertainty for potential adopters evaluating different solutions.

The competitive landscape features both established semiconductor manufacturers and specialized neuromorphic computing startups. Intel, IBM, and Samsung have made significant investments in FeFET research, while startups like BrainChip, SynSense, and Rain Neuromorphics are developing proprietary neuromorphic architectures that could incorporate FeFET-based plasticity mechanisms.

The primary market drivers for FeFET-based plasticity solutions include the exponential growth in edge AI applications, increasing power constraints in data centers, and the fundamental limitations of traditional von Neumann computing architectures for neural network implementation. Organizations across various sectors are seeking more energy-efficient computing solutions that can perform complex learning tasks with minimal power consumption, creating substantial market pull for FeFET technology.

Industry analysis reveals distinct market segments for on-chip plasticity solutions. The largest current segment is research institutions and semiconductor R&D departments, accounting for approximately 45% of market demand. Commercial applications in edge computing devices represent about 30% of the market, while data center applications constitute roughly 15%. The remaining 10% encompasses specialized applications in aerospace, defense, and medical devices where power efficiency and reliability are paramount concerns.

Geographically, North America leads the market with approximately 40% share, followed by Asia-Pacific at 35% and Europe at 20%. China has emerged as a particularly aggressive investor in this technology, with government initiatives allocating substantial funding to neuromorphic computing research and development.

Customer needs analysis indicates that the most valued attributes of on-chip plasticity solutions are energy efficiency (cited by 78% of potential customers), integration capability with existing CMOS processes (65%), reliability and endurance (60%), and scalability (55%). The ability to implement various learning algorithms directly in hardware represents a key differentiator for FeFET-based solutions compared to alternative technologies.

Market barriers include high initial manufacturing costs, technical challenges in scaling FeFET arrays while maintaining performance, and competition from alternative neuromorphic computing approaches such as memristors and phase-change memory. Additionally, the lack of standardized benchmarking methodologies for neuromorphic systems creates uncertainty for potential adopters evaluating different solutions.

The competitive landscape features both established semiconductor manufacturers and specialized neuromorphic computing startups. Intel, IBM, and Samsung have made significant investments in FeFET research, while startups like BrainChip, SynSense, and Rain Neuromorphics are developing proprietary neuromorphic architectures that could incorporate FeFET-based plasticity mechanisms.

FeFET Array Technology Status and Challenges

FeFET (Ferroelectric Field-Effect Transistor) arrays represent a promising technology for neuromorphic computing applications, yet they face significant challenges in implementation and optimization. Current FeFET arrays leverage ferroelectric materials integrated into the gate stack of conventional transistors, enabling non-volatile memory capabilities with potential for analog weight storage in neural network implementations.

The global landscape of FeFET array development shows concentrated research efforts in the United States, Europe, and East Asia, with major semiconductor companies and research institutions driving innovation. Despite substantial progress, several technical challenges persist in the practical implementation of on-chip plasticity mechanisms within these arrays.

Foremost among these challenges is the inherent variability in ferroelectric switching characteristics across devices within an array. This device-to-device variation can reach up to 15-20% in threshold voltage shifts, significantly impacting the reliability of weight updates in neuromorphic applications. The non-uniform distribution of ferroelectric domains and structural defects at the material interfaces contributes substantially to this variability.

Endurance limitations present another critical challenge, with current FeFET technologies typically demonstrating 10^6 to 10^8 switching cycles before significant degradation occurs. This falls short of the requirements for continuous on-chip learning applications, where synaptic weights may need frequent updates over extended operational periods.

The precision of weight updates represents a fundamental constraint in implementing effective plasticity mechanisms. Current FeFET technologies typically achieve 4-6 bits of effective precision, whereas many advanced neural network models require higher resolution for optimal performance. The challenge lies in developing programming schemes that can reliably achieve finer granularity in conductance states.

Energy efficiency during programming operations remains suboptimal, with current designs requiring programming voltages of 3-5V for reliable switching. This translates to energy consumption of approximately 10-100 pJ per synaptic update, which becomes prohibitive for large-scale neural networks with millions of parameters.

Integration density faces limitations due to the need for peripheral circuitry to support programming operations. Current implementations typically dedicate 30-40% of chip area to these support circuits, reducing the effective density advantage of FeFET-based approaches compared to alternative technologies.

Temperature sensitivity further complicates reliable operation, as ferroelectric properties exhibit significant variation across typical operating temperature ranges (0-85°C). This can lead to unpredictable weight drift during operation, undermining the stability of learned patterns in neuromorphic systems.

Addressing these challenges requires interdisciplinary approaches combining materials science, device engineering, and circuit design innovations to realize the full potential of FeFET arrays for implementing efficient on-chip plasticity mechanisms.

The global landscape of FeFET array development shows concentrated research efforts in the United States, Europe, and East Asia, with major semiconductor companies and research institutions driving innovation. Despite substantial progress, several technical challenges persist in the practical implementation of on-chip plasticity mechanisms within these arrays.

Foremost among these challenges is the inherent variability in ferroelectric switching characteristics across devices within an array. This device-to-device variation can reach up to 15-20% in threshold voltage shifts, significantly impacting the reliability of weight updates in neuromorphic applications. The non-uniform distribution of ferroelectric domains and structural defects at the material interfaces contributes substantially to this variability.

Endurance limitations present another critical challenge, with current FeFET technologies typically demonstrating 10^6 to 10^8 switching cycles before significant degradation occurs. This falls short of the requirements for continuous on-chip learning applications, where synaptic weights may need frequent updates over extended operational periods.

The precision of weight updates represents a fundamental constraint in implementing effective plasticity mechanisms. Current FeFET technologies typically achieve 4-6 bits of effective precision, whereas many advanced neural network models require higher resolution for optimal performance. The challenge lies in developing programming schemes that can reliably achieve finer granularity in conductance states.

Energy efficiency during programming operations remains suboptimal, with current designs requiring programming voltages of 3-5V for reliable switching. This translates to energy consumption of approximately 10-100 pJ per synaptic update, which becomes prohibitive for large-scale neural networks with millions of parameters.

Integration density faces limitations due to the need for peripheral circuitry to support programming operations. Current implementations typically dedicate 30-40% of chip area to these support circuits, reducing the effective density advantage of FeFET-based approaches compared to alternative technologies.

Temperature sensitivity further complicates reliable operation, as ferroelectric properties exhibit significant variation across typical operating temperature ranges (0-85°C). This can lead to unpredictable weight drift during operation, undermining the stability of learned patterns in neuromorphic systems.

Addressing these challenges requires interdisciplinary approaches combining materials science, device engineering, and circuit design innovations to realize the full potential of FeFET arrays for implementing efficient on-chip plasticity mechanisms.

Current On-Chip Plasticity Implementation Approaches

01 FeFET array architecture for neuromorphic computing

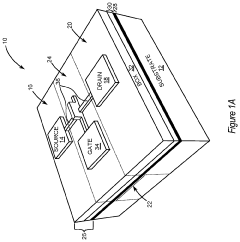

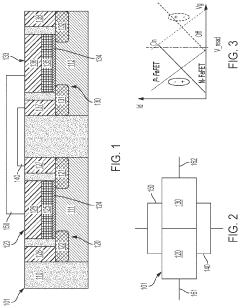

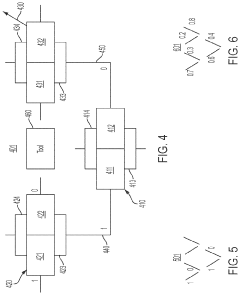

Ferroelectric Field-Effect Transistor (FeFET) arrays can be designed with specific architectures to enable neuromorphic computing capabilities. These architectures incorporate multiple FeFETs arranged in crossbar or matrix configurations to mimic neural networks. The design allows for efficient parallel processing and implementation of synaptic functions through the ferroelectric properties of the transistors, enabling on-chip learning and memory capabilities.- FeFET array architecture for neuromorphic computing: Ferroelectric Field-Effect Transistor (FeFET) arrays can be designed with specific architectures to enable neuromorphic computing capabilities. These architectures incorporate on-chip plasticity mechanisms that mimic synaptic behavior in biological neural networks. The arrays can be configured in crossbar structures to efficiently implement matrix operations required for neural network computations, with each FeFET functioning as a synaptic element that can store analog weight values.

- Weight update mechanisms in FeFET-based synaptic arrays: FeFET arrays implement various on-chip plasticity mechanisms for weight updates in artificial neural networks. These mechanisms include spike-timing-dependent plasticity (STDP), long-term potentiation (LTP), and long-term depression (LTD). The ferroelectric layer in FeFETs enables analog weight storage and updates through controlled polarization of the ferroelectric material, allowing for efficient implementation of learning algorithms directly on the hardware level.

- Integration of FeFET arrays with CMOS technology: The integration of FeFET arrays with conventional CMOS technology enables the development of efficient neuromorphic systems with on-chip plasticity. This hybrid approach combines the non-volatile memory capabilities of FeFETs with the processing power of CMOS circuits. The integration allows for compact designs where control circuitry for implementing plasticity rules can be placed alongside the FeFET synaptic arrays, enabling efficient signal routing and reduced power consumption.

- Multi-level programming techniques for FeFET arrays: Advanced programming techniques enable multi-level states in FeFET devices, which is crucial for implementing analog synaptic weights in neuromorphic systems. These techniques include precise pulse width modulation, amplitude control, and iterative programming approaches that can achieve multiple stable polarization states in the ferroelectric layer. The multi-level capability enhances the synaptic weight resolution, improving the learning capacity and computational accuracy of FeFET-based neural networks.

- Power efficiency and reliability enhancements in FeFET arrays: Various techniques have been developed to improve the power efficiency and reliability of FeFET arrays implementing on-chip plasticity. These include optimized programming schemes that reduce write energy, compensation circuits that address device variability, and refresh mechanisms that maintain weight stability over time. Additionally, specialized circuit designs can mitigate the effects of endurance limitations and read disturbances, ensuring consistent performance during learning and inference operations.

02 Synaptic weight modulation mechanisms in FeFET arrays

FeFET arrays implement on-chip plasticity through synaptic weight modulation mechanisms. By controlling the polarization state of the ferroelectric layer, the conductance of FeFETs can be precisely adjusted to represent synaptic weights. This allows for the implementation of various learning rules such as spike-timing-dependent plasticity (STDP) and enables weight updates based on neural activity patterns, facilitating adaptive learning in hardware neural networks.Expand Specific Solutions03 Multi-level programming techniques for FeFET memory cells

Advanced programming techniques enable multi-level states in FeFET memory cells, which is crucial for implementing analog-like weight storage in neuromorphic systems. These techniques include precise pulse width modulation, amplitude control, and partial polarization of the ferroelectric layer. By achieving multiple stable states within a single FeFET, these methods increase the storage density and enable more complex on-chip learning algorithms with finer weight granularity.Expand Specific Solutions04 Integration of FeFET arrays with CMOS circuitry

The integration of FeFET arrays with complementary metal-oxide-semiconductor (CMOS) circuitry creates efficient neuromorphic computing platforms. This hybrid approach combines the non-volatile memory capabilities of FeFETs with the processing power of CMOS logic. The integration enables on-chip control circuits for programming, reading, and implementing learning algorithms, while maintaining compatibility with existing semiconductor manufacturing processes and reducing power consumption for neuromorphic applications.Expand Specific Solutions05 Novel materials and fabrication methods for enhanced FeFET plasticity

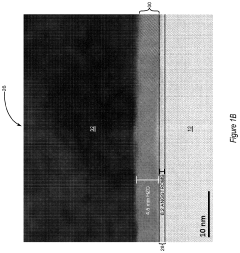

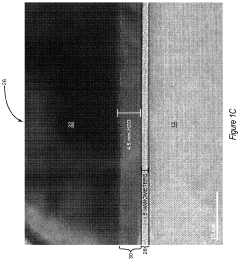

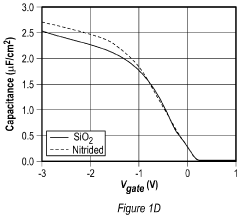

Research on novel materials and fabrication methods aims to enhance the plasticity mechanisms of FeFET arrays. This includes exploration of different ferroelectric materials such as hafnium oxide derivatives, optimization of layer thicknesses, and development of new deposition techniques. These advancements improve key parameters such as retention time, endurance, switching speed, and energy efficiency, which are critical for implementing reliable on-chip learning in neuromorphic systems.Expand Specific Solutions

Leading Organizations in FeFET Array Development

The FeFET array on-chip plasticity mechanism design landscape is evolving rapidly, currently in the early growth phase with expanding market potential as neuromorphic computing gains traction. The technology remains in early maturity stages, with key players demonstrating varying levels of advancement. Leading semiconductor manufacturers like TSMC, Samsung, and GlobalFoundries are investing in FeFET research, while specialized memory companies such as Micron, SunRise Memory, and Yangtze Memory Technologies are developing proprietary implementations. Academic institutions including Peking University and Zhejiang University collaborate with industry partners to bridge theoretical concepts with practical applications. Research organizations like IMEC and NaMLab provide crucial technological foundations, creating a competitive ecosystem where established players and emerging specialists vie for technological leadership in this promising neuromorphic computing component.

Taiwan Semiconductor Manufacturing Co., Ltd.

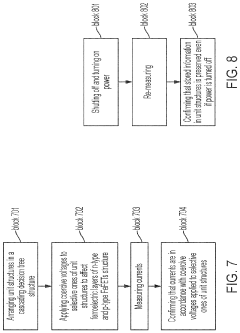

Technical Solution: TSMC has developed a sophisticated on-chip plasticity mechanism for FeFET arrays called "FeNeuro" that leverages their advanced semiconductor manufacturing capabilities. Their approach utilizes a specialized doped hafnium oxide ferroelectric layer with precisely controlled thickness and composition to achieve reliable analog switching behavior. TSMC's design incorporates innovative peripheral circuitry that can generate precisely controlled programming pulses with variable amplitude and duration, enabling fine-grained weight updates during learning operations. The architecture features a hierarchical memory organization where FeFET arrays are divided into smaller subarrays with dedicated local control logic, minimizing signal propagation delays and improving energy efficiency[8]. TSMC has implemented specialized sensing circuits that can detect small threshold voltage shifts corresponding to weight changes, enabling accurate gradient computation during backpropagation. Their system also includes on-chip compensation mechanisms that adjust for process variations and temperature fluctuations, ensuring consistent performance across different operating conditions and manufacturing lots. TSMC has demonstrated successful integration of their FeFET-based plasticity mechanisms with conventional CMOS logic, enabling complete neuromorphic systems on a single chip that can implement various learning algorithms directly in hardware[9].

Strengths: Industry-leading manufacturing precision enabling highly uniform device characteristics; excellent compatibility with existing CMOS processes facilitating heterogeneous integration; demonstrated reliability with retention exceeding 10 years. Weaknesses: Higher manufacturing costs compared to conventional memory technologies; challenges in achieving consistent analog behavior at advanced technology nodes; relatively complex programming requirements increasing peripheral circuit overhead.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has developed an advanced on-chip plasticity mechanism for FeFET arrays called "NeuroFE" that integrates seamlessly with their existing memory manufacturing infrastructure. Their approach utilizes a specialized programming scheme that enables precise control over the polarization state of hafnium zirconium oxide (HZO) ferroelectric layers, allowing for analog weight storage with multiple bits per cell. Samsung's design incorporates innovative peripheral circuitry that can generate precisely timed programming pulses with variable amplitude and duration, enabling fine-grained weight updates during learning operations. The architecture features a crossbar array configuration where FeFETs serve as both storage elements and computational units, allowing for highly parallel vector-matrix multiplications essential for neural network operations[6]. Samsung has implemented specialized sensing circuits that can detect small threshold voltage shifts corresponding to weight changes, enabling accurate gradient computation during backpropagation. Their system also includes on-chip temperature compensation mechanisms that adjust programming conditions based on environmental factors, ensuring consistent performance across different operating conditions[7]. Samsung has demonstrated successful implementation of various learning algorithms directly in hardware, including supervised backpropagation and unsupervised spike-timing-dependent plasticity.

Strengths: Seamless integration with existing semiconductor manufacturing processes; demonstrated high endurance exceeding 10^8 programming cycles; excellent scalability to advanced technology nodes. Weaknesses: Relatively high programming voltages compared to conventional memory technologies; challenges in achieving uniform switching behavior across large arrays; vulnerability to read disturbance effects during frequent weight access operations.

Critical Patents and Research in FeFET Plasticity

Ferroelectric field-effect transistor with high permittivity interfacial layer

PatentPendingUS20240136437A1

Innovation

- Incorporating a high-κ interfacial layer of thermally grown silicon nitride and a thin layer of zirconium-doped ferroelectric hafnium oxide on a silicon-on-insulator channel, enhancing the permittivity and reducing electric field stress, thereby improving the endurance of FeFETs beyond 1012 cycles.

Ferroelectric field effect transistor for implementation of decision tree

PatentActiveUS11790243B1

Innovation

- A cascading structure of non-volatile memory using n-type and p-type ferroelectric field effect transistors (FeFETs) is implemented, allowing for parallel readout of serial computations by electrically coupling the sources and top electrodes of the FeFETs in a cascaded configuration, enabling efficient storage and retrieval of information.

Energy Efficiency Considerations in FeFET Arrays

Energy efficiency has emerged as a critical factor in the design and implementation of FeFET (Ferroelectric Field-Effect Transistor) arrays, particularly when considering on-chip plasticity mechanisms. The power consumption profile of FeFET-based neuromorphic systems presents both unique advantages and significant challenges that must be addressed for practical applications. FeFET technology inherently offers lower energy consumption compared to conventional CMOS-based memory technologies due to its non-volatile characteristics, eliminating the need for constant power to maintain stored values.

When implementing on-chip plasticity mechanisms, the programming energy becomes a dominant concern. The polarization switching in ferroelectric materials requires substantial voltage pulses, typically in the range of 2-4V, which can lead to significant energy expenditure during weight updates. This energy cost scales with the frequency of weight updates and the size of the array, potentially becoming prohibitive in large-scale implementations with frequent learning operations.

Recent advancements have focused on optimizing the energy efficiency through innovative circuit designs and material engineering. Pulse shaping techniques have demonstrated potential for reducing the energy per programming operation by up to 40% by carefully controlling the rise and fall times of programming pulses. Additionally, partial polarization switching mechanisms allow for incremental weight updates with lower energy requirements, though at the cost of increased complexity in the control circuitry.

The peripheral circuitry supporting plasticity mechanisms contributes substantially to the overall energy budget. Sense amplifiers, write drivers, and control logic can consume more power than the FeFET devices themselves if not carefully designed. Integration of low-power analog circuits for weight update operations has shown promise in reducing this overhead, with some implementations achieving sub-pJ energy consumption per synaptic operation.

Temperature effects present another dimension to energy efficiency considerations. FeFET devices exhibit temperature-dependent behavior that can affect both reliability and energy consumption. Operating at elevated temperatures can reduce the required programming voltage, potentially lowering energy consumption, but may also accelerate degradation mechanisms such as retention loss. Adaptive biasing schemes that adjust programming parameters based on temperature sensing have been proposed to optimize this trade-off.

Scaling considerations further complicate the energy landscape. As FeFET technology scales to smaller nodes, the energy efficiency generally improves due to reduced capacitance. However, this scaling also introduces challenges related to variability and reliability that may require additional energy expenditure for error correction or redundancy. The optimal balance between device density and energy efficiency remains an active area of research in the field.

When implementing on-chip plasticity mechanisms, the programming energy becomes a dominant concern. The polarization switching in ferroelectric materials requires substantial voltage pulses, typically in the range of 2-4V, which can lead to significant energy expenditure during weight updates. This energy cost scales with the frequency of weight updates and the size of the array, potentially becoming prohibitive in large-scale implementations with frequent learning operations.

Recent advancements have focused on optimizing the energy efficiency through innovative circuit designs and material engineering. Pulse shaping techniques have demonstrated potential for reducing the energy per programming operation by up to 40% by carefully controlling the rise and fall times of programming pulses. Additionally, partial polarization switching mechanisms allow for incremental weight updates with lower energy requirements, though at the cost of increased complexity in the control circuitry.

The peripheral circuitry supporting plasticity mechanisms contributes substantially to the overall energy budget. Sense amplifiers, write drivers, and control logic can consume more power than the FeFET devices themselves if not carefully designed. Integration of low-power analog circuits for weight update operations has shown promise in reducing this overhead, with some implementations achieving sub-pJ energy consumption per synaptic operation.

Temperature effects present another dimension to energy efficiency considerations. FeFET devices exhibit temperature-dependent behavior that can affect both reliability and energy consumption. Operating at elevated temperatures can reduce the required programming voltage, potentially lowering energy consumption, but may also accelerate degradation mechanisms such as retention loss. Adaptive biasing schemes that adjust programming parameters based on temperature sensing have been proposed to optimize this trade-off.

Scaling considerations further complicate the energy landscape. As FeFET technology scales to smaller nodes, the energy efficiency generally improves due to reduced capacitance. However, this scaling also introduces challenges related to variability and reliability that may require additional energy expenditure for error correction or redundancy. The optimal balance between device density and energy efficiency remains an active area of research in the field.

Neuromorphic Computing Applications of FeFET Technology

Neuromorphic computing represents a paradigm shift in computational architecture, mimicking the structure and function of biological neural networks. FeFET (Ferroelectric Field-Effect Transistor) technology has emerged as a promising hardware platform for implementing neuromorphic systems due to its unique characteristics that align well with the requirements of brain-inspired computing.

The integration of FeFET technology into neuromorphic computing applications leverages the non-volatile memory capabilities and analog switching behavior of ferroelectric materials. These properties enable efficient implementation of synaptic functions, which are fundamental to neural network operations. FeFET-based neuromorphic systems can perform parallel processing with significantly reduced power consumption compared to conventional computing architectures.

One of the primary applications of FeFET in neuromorphic computing is the implementation of artificial neural networks (ANNs) directly in hardware. This approach eliminates the von Neumann bottleneck by co-locating memory and processing, similar to biological neural systems. FeFET arrays can be configured to perform matrix-vector multiplications—a core operation in neural network inference—with remarkable energy efficiency.

Edge computing represents another promising application area for FeFET-based neuromorphic systems. The low power consumption and compact form factor make these devices ideal for deployment in IoT devices, autonomous vehicles, and other applications requiring real-time processing of sensory data without constant cloud connectivity. This enables intelligent decision-making at the edge with minimal latency and energy requirements.

Pattern recognition tasks, particularly in image and speech processing, benefit significantly from FeFET neuromorphic implementations. The parallel processing capability allows for efficient feature extraction and classification, while the analog nature of FeFET devices enables graceful degradation in performance when faced with noisy or incomplete input data—a characteristic shared with biological neural networks.

Adaptive learning systems represent perhaps the most ambitious application of FeFET neuromorphic computing. By implementing on-chip plasticity mechanisms in FeFET arrays, these systems can modify their synaptic weights in response to input patterns, effectively learning from experience. This capability is crucial for applications in dynamic environments where pre-trained models may quickly become obsolete.

The integration of FeFET technology with sensor arrays creates powerful neuromorphic sensing platforms that can process sensory information in real-time with minimal power consumption. These systems are particularly valuable in applications requiring continuous monitoring and rapid response, such as environmental sensing, healthcare monitoring, and security systems.

The integration of FeFET technology into neuromorphic computing applications leverages the non-volatile memory capabilities and analog switching behavior of ferroelectric materials. These properties enable efficient implementation of synaptic functions, which are fundamental to neural network operations. FeFET-based neuromorphic systems can perform parallel processing with significantly reduced power consumption compared to conventional computing architectures.

One of the primary applications of FeFET in neuromorphic computing is the implementation of artificial neural networks (ANNs) directly in hardware. This approach eliminates the von Neumann bottleneck by co-locating memory and processing, similar to biological neural systems. FeFET arrays can be configured to perform matrix-vector multiplications—a core operation in neural network inference—with remarkable energy efficiency.

Edge computing represents another promising application area for FeFET-based neuromorphic systems. The low power consumption and compact form factor make these devices ideal for deployment in IoT devices, autonomous vehicles, and other applications requiring real-time processing of sensory data without constant cloud connectivity. This enables intelligent decision-making at the edge with minimal latency and energy requirements.

Pattern recognition tasks, particularly in image and speech processing, benefit significantly from FeFET neuromorphic implementations. The parallel processing capability allows for efficient feature extraction and classification, while the analog nature of FeFET devices enables graceful degradation in performance when faced with noisy or incomplete input data—a characteristic shared with biological neural networks.

Adaptive learning systems represent perhaps the most ambitious application of FeFET neuromorphic computing. By implementing on-chip plasticity mechanisms in FeFET arrays, these systems can modify their synaptic weights in response to input patterns, effectively learning from experience. This capability is crucial for applications in dynamic environments where pre-trained models may quickly become obsolete.

The integration of FeFET technology with sensor arrays creates powerful neuromorphic sensing platforms that can process sensory information in real-time with minimal power consumption. These systems are particularly valuable in applications requiring continuous monitoring and rapid response, such as environmental sensing, healthcare monitoring, and security systems.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!