Assembly Line Testing Protocols For High-Volume CSAC Manufacturing

AUG 29, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

CSAC Technology Background and Testing Objectives

Chip-Scale Atomic Clocks (CSACs) represent a revolutionary advancement in timing technology, miniaturizing atomic clock capabilities into semiconductor-sized packages. Since their conceptualization in the early 2000s, CSACs have evolved from laboratory curiosities to commercially viable products, with significant development milestones achieved by DARPA's CSAC program and subsequent industry adoption. These devices leverage quantum properties of alkali metal atoms, typically cesium or rubidium, to provide precision timing references orders of magnitude more stable than traditional quartz oscillators.

The technology evolution trajectory has seen dramatic reductions in size, weight, and power consumption (SWaP), transitioning from rack-mounted systems weighing kilograms to chip-scale devices consuming mere milliwatts. This miniaturization has enabled new application domains previously inaccessible to atomic clock technology, including portable military communications, GPS-denied navigation, and distributed network synchronization.

Current CSAC technology aims to achieve frequency stability of 10^-11 over one hour while maintaining power consumption below 100mW in packages smaller than 1 cubic centimeter. These specifications represent the intersection of physics constraints and practical engineering considerations that define the current generation of devices.

The primary objective of assembly line testing protocols for high-volume CSAC manufacturing is to ensure consistent performance across mass-produced units while maintaining economic viability. Testing must verify critical parameters including frequency accuracy, Allan deviation (stability over various time intervals), temperature sensitivity, magnetic field immunity, and power consumption characteristics—all within acceptable manufacturing throughput rates.

Testing objectives must address the unique challenges of CSAC production, particularly the physics package containing the atomic vapor cell, which requires specialized handling and characterization. The protocols must identify performance outliers early in the production process to minimize costly rework of completed assemblies. Additionally, testing must accommodate both short-term performance verification and predict long-term aging effects that may impact field reliability.

A comprehensive testing framework must balance thoroughness with efficiency, implementing statistical process control methodologies appropriate for quantum devices. The ultimate goal is establishing protocols that enable scaling production from hundreds to thousands or tens of thousands of units annually while maintaining consistent performance specifications and reliability standards expected of precision timing references.

As CSAC technology continues to mature, testing protocols must evolve to incorporate emerging performance parameters and address new failure modes identified through expanded deployment scenarios and accumulated field data from early production units.

The technology evolution trajectory has seen dramatic reductions in size, weight, and power consumption (SWaP), transitioning from rack-mounted systems weighing kilograms to chip-scale devices consuming mere milliwatts. This miniaturization has enabled new application domains previously inaccessible to atomic clock technology, including portable military communications, GPS-denied navigation, and distributed network synchronization.

Current CSAC technology aims to achieve frequency stability of 10^-11 over one hour while maintaining power consumption below 100mW in packages smaller than 1 cubic centimeter. These specifications represent the intersection of physics constraints and practical engineering considerations that define the current generation of devices.

The primary objective of assembly line testing protocols for high-volume CSAC manufacturing is to ensure consistent performance across mass-produced units while maintaining economic viability. Testing must verify critical parameters including frequency accuracy, Allan deviation (stability over various time intervals), temperature sensitivity, magnetic field immunity, and power consumption characteristics—all within acceptable manufacturing throughput rates.

Testing objectives must address the unique challenges of CSAC production, particularly the physics package containing the atomic vapor cell, which requires specialized handling and characterization. The protocols must identify performance outliers early in the production process to minimize costly rework of completed assemblies. Additionally, testing must accommodate both short-term performance verification and predict long-term aging effects that may impact field reliability.

A comprehensive testing framework must balance thoroughness with efficiency, implementing statistical process control methodologies appropriate for quantum devices. The ultimate goal is establishing protocols that enable scaling production from hundreds to thousands or tens of thousands of units annually while maintaining consistent performance specifications and reliability standards expected of precision timing references.

As CSAC technology continues to mature, testing protocols must evolve to incorporate emerging performance parameters and address new failure modes identified through expanded deployment scenarios and accumulated field data from early production units.

Market Demand Analysis for High-Volume CSAC Production

The global market for Chip-Scale Atomic Clocks (CSACs) is experiencing significant growth driven by increasing demand across multiple sectors. Current market valuations indicate the CSAC market reached approximately $400 million in 2022, with projections suggesting a compound annual growth rate (CAGR) of 8-10% over the next five years. This growth trajectory is primarily fueled by expanding applications in telecommunications, defense systems, and emerging technologies that require precise timing solutions.

Defense and aerospace sectors currently represent the largest market segment, accounting for nearly 45% of total CSAC demand. Military applications particularly value CSACs for their ability to maintain precise timing in GPS-denied environments, making them critical components in secure communications systems, unmanned vehicles, and missile guidance systems. The increasing focus on autonomous defense capabilities is expected to further accelerate demand in this sector.

Telecommunications represents the second-largest market segment, with approximately 30% market share. As 5G networks continue global deployment and 6G research advances, the need for highly stable frequency references becomes increasingly critical. Network synchronization requirements are becoming more stringent, driving adoption of high-performance timing solutions like CSACs to ensure optimal network performance and reliability.

The scientific and metrology sectors, while smaller in market share at approximately 15%, demonstrate consistent growth as research institutions and national laboratories upgrade their timing infrastructure. The remaining market share is distributed across emerging applications including autonomous vehicles, financial trading systems, and industrial automation.

Regional analysis reveals North America currently leads CSAC market consumption at 40%, followed by Europe (25%), Asia-Pacific (20%), and rest of world (15%). However, the Asia-Pacific region is projected to show the highest growth rate over the next decade, driven by expanding telecommunications infrastructure and increasing defense modernization programs in countries like China, India, and South Korea.

A key market trend is the growing demand for miniaturized, low-power timing solutions in portable and battery-operated devices. This trend aligns perfectly with high-volume CSAC manufacturing initiatives, as economies of scale could potentially reduce unit costs from current levels of $1,500-3,000 to below $1,000, opening entirely new market segments.

Industry surveys indicate that price point remains the primary barrier to wider CSAC adoption, with 65% of potential customers citing cost as their main concern. This underscores the critical importance of developing efficient assembly line testing protocols for high-volume manufacturing to reduce production costs while maintaining performance specifications.

Defense and aerospace sectors currently represent the largest market segment, accounting for nearly 45% of total CSAC demand. Military applications particularly value CSACs for their ability to maintain precise timing in GPS-denied environments, making them critical components in secure communications systems, unmanned vehicles, and missile guidance systems. The increasing focus on autonomous defense capabilities is expected to further accelerate demand in this sector.

Telecommunications represents the second-largest market segment, with approximately 30% market share. As 5G networks continue global deployment and 6G research advances, the need for highly stable frequency references becomes increasingly critical. Network synchronization requirements are becoming more stringent, driving adoption of high-performance timing solutions like CSACs to ensure optimal network performance and reliability.

The scientific and metrology sectors, while smaller in market share at approximately 15%, demonstrate consistent growth as research institutions and national laboratories upgrade their timing infrastructure. The remaining market share is distributed across emerging applications including autonomous vehicles, financial trading systems, and industrial automation.

Regional analysis reveals North America currently leads CSAC market consumption at 40%, followed by Europe (25%), Asia-Pacific (20%), and rest of world (15%). However, the Asia-Pacific region is projected to show the highest growth rate over the next decade, driven by expanding telecommunications infrastructure and increasing defense modernization programs in countries like China, India, and South Korea.

A key market trend is the growing demand for miniaturized, low-power timing solutions in portable and battery-operated devices. This trend aligns perfectly with high-volume CSAC manufacturing initiatives, as economies of scale could potentially reduce unit costs from current levels of $1,500-3,000 to below $1,000, opening entirely new market segments.

Industry surveys indicate that price point remains the primary barrier to wider CSAC adoption, with 65% of potential customers citing cost as their main concern. This underscores the critical importance of developing efficient assembly line testing protocols for high-volume manufacturing to reduce production costs while maintaining performance specifications.

Current Testing Challenges in CSAC Manufacturing

The manufacturing of Chip-Scale Atomic Clocks (CSACs) at high volumes presents significant testing challenges that impact production efficiency, cost structures, and product reliability. Current testing protocols often struggle to balance thoroughness with production speed, creating bottlenecks in the manufacturing process.

One primary challenge is the extended duration required for frequency stabilization testing. CSACs typically need 24-48 hours to reach their specified stability performance, which creates substantial delays in production throughput. This extended testing period significantly impacts manufacturing capacity and increases work-in-progress inventory costs.

Environmental sensitivity testing presents another major hurdle. CSACs must maintain performance across varying temperature ranges, magnetic fields, and vibration conditions. Current testing methodologies require sequential environmental exposure, multiplying the already lengthy testing cycles. The specialized equipment needed for these tests further compounds costs and complexity.

Power consumption characterization remains problematic in high-volume scenarios. The precise measurement of power draw across different operational modes requires sensitive instrumentation that is difficult to integrate into automated production lines. Many facilities still rely on semi-manual testing procedures that introduce variability and human error.

Aging and reliability prediction represents perhaps the most challenging aspect of CSAC testing. Accelerated aging tests currently employed provide only approximate indicators of long-term performance, with limited correlation to actual field reliability. The industry lacks standardized methodologies for predicting the decade-long performance expected from premium CSAC units.

Calibration and trimming processes during testing create additional complexity. Each CSAC requires individual calibration to achieve optimal performance, but current automated systems struggle with the precision required for these adjustments. The calibration process often requires multiple iterations, further extending production timelines.

Test equipment scalability presents a significant barrier to achieving true high-volume manufacturing. Current specialized test stations are expensive, with limited throughput capacity. The capital investment required for scaling testing capabilities often exceeds $500,000 per production line, creating financial barriers to manufacturing expansion.

Data management systems for test results frequently lack the sophistication needed for advanced analytics and process improvement. Many manufacturers struggle to implement real-time statistical process control due to inadequate data infrastructure, limiting their ability to identify and address systematic production issues.

Human Resources: The specialized knowledge required for CSAC testing creates workforce challenges. Technicians need extensive training in atomic physics principles and precision measurement techniques, creating a skills gap that impacts testing quality and consistency across production shifts.

One primary challenge is the extended duration required for frequency stabilization testing. CSACs typically need 24-48 hours to reach their specified stability performance, which creates substantial delays in production throughput. This extended testing period significantly impacts manufacturing capacity and increases work-in-progress inventory costs.

Environmental sensitivity testing presents another major hurdle. CSACs must maintain performance across varying temperature ranges, magnetic fields, and vibration conditions. Current testing methodologies require sequential environmental exposure, multiplying the already lengthy testing cycles. The specialized equipment needed for these tests further compounds costs and complexity.

Power consumption characterization remains problematic in high-volume scenarios. The precise measurement of power draw across different operational modes requires sensitive instrumentation that is difficult to integrate into automated production lines. Many facilities still rely on semi-manual testing procedures that introduce variability and human error.

Aging and reliability prediction represents perhaps the most challenging aspect of CSAC testing. Accelerated aging tests currently employed provide only approximate indicators of long-term performance, with limited correlation to actual field reliability. The industry lacks standardized methodologies for predicting the decade-long performance expected from premium CSAC units.

Calibration and trimming processes during testing create additional complexity. Each CSAC requires individual calibration to achieve optimal performance, but current automated systems struggle with the precision required for these adjustments. The calibration process often requires multiple iterations, further extending production timelines.

Test equipment scalability presents a significant barrier to achieving true high-volume manufacturing. Current specialized test stations are expensive, with limited throughput capacity. The capital investment required for scaling testing capabilities often exceeds $500,000 per production line, creating financial barriers to manufacturing expansion.

Data management systems for test results frequently lack the sophistication needed for advanced analytics and process improvement. Many manufacturers struggle to implement real-time statistical process control due to inadequate data infrastructure, limiting their ability to identify and address systematic production issues.

Human Resources: The specialized knowledge required for CSAC testing creates workforce challenges. Technicians need extensive training in atomic physics principles and precision measurement techniques, creating a skills gap that impacts testing quality and consistency across production shifts.

Current Assembly Line Testing Solutions

01 Environmental Testing Protocols for CSACs

Environmental testing protocols for Chip-Scale Atomic Clocks involve subjecting the devices to various environmental conditions to evaluate their performance and reliability. These tests include temperature cycling, humidity exposure, vibration testing, and shock testing to ensure the CSACs can maintain accurate timekeeping under different operational conditions. The protocols typically measure frequency stability, power consumption, and phase noise during and after environmental stress to validate the robustness of the atomic clock design.- Environmental Testing Protocols for CSACs: Environmental testing protocols for Chip-Scale Atomic Clocks involve subjecting the devices to various environmental conditions to evaluate their performance and reliability. These tests include temperature cycling, humidity exposure, vibration testing, and shock testing to ensure the CSACs can maintain accurate timekeeping under different environmental stresses. The protocols typically measure frequency stability, power consumption, and phase noise during and after environmental exposure to verify the robustness of the atomic clock design.

- Frequency Stability and Accuracy Testing: Testing protocols for CSAC frequency stability and accuracy involve measuring Allan deviation, phase noise, and frequency drift over various time intervals. These protocols typically include comparisons against reference standards, long-term stability measurements, and performance verification across operating temperatures. The testing methodologies evaluate the clock's ability to maintain precise timing under different conditions, which is critical for applications requiring high precision timing such as telecommunications, navigation systems, and scientific instrumentation.

- Power Consumption and Efficiency Testing: Power consumption testing protocols for CSACs focus on measuring energy efficiency during startup, normal operation, and standby modes. These protocols evaluate the relationship between power settings and timing performance to optimize battery life in portable applications. Testing includes measuring current draw at different operating voltages, thermal efficiency, and power stability over time. The protocols help determine the suitability of CSACs for power-constrained applications such as mobile devices, unmanned vehicles, and remote sensing equipment.

- Aging and Long-term Reliability Testing: Aging and reliability testing protocols for CSACs involve accelerated life testing, long-term drift measurements, and performance degradation analysis. These protocols typically include continuous operation tests over extended periods, thermal cycling to simulate years of use, and statistical analysis of failure rates. The testing methodologies help predict the operational lifespan of CSACs and identify potential failure mechanisms. Results from these tests are crucial for applications requiring long-term deployment without maintenance, such as deep space missions, underwater systems, and critical infrastructure.

- Integration and System-level Testing: Integration and system-level testing protocols for CSACs focus on evaluating their performance when incorporated into larger systems. These protocols include electromagnetic interference (EMI) testing, signal integrity verification, interface compatibility testing, and system synchronization measurements. The testing methodologies assess how well CSACs interact with other components and maintain timing accuracy within complete systems. These protocols are essential for applications such as telecommunications networks, GPS receivers, military systems, and scientific instruments where the CSAC must function reliably as part of a complex system.

02 Frequency Stability and Accuracy Testing

Testing protocols for CSAC frequency stability and accuracy involve measuring Allan deviation, phase noise, and long-term drift under controlled conditions. These protocols typically include comparison against reference standards, measurement of temperature coefficients, and evaluation of aging effects. Testing procedures may involve continuous operation over extended periods to characterize stability performance across different timescales, from short-term stability (seconds to minutes) to long-term stability (days to months).Expand Specific Solutions03 Power Consumption and Thermal Management Testing

Testing protocols for CSAC power consumption and thermal management focus on measuring energy efficiency, heat generation, and performance under various power conditions. These tests evaluate startup time, warm-up period power requirements, and steady-state consumption. Thermal testing includes temperature gradient mapping across the device, thermal cycling effects on frequency stability, and validation of thermal management solutions. The protocols aim to optimize power efficiency while maintaining clock performance within specification limits.Expand Specific Solutions04 Integration and Compatibility Testing

Integration and compatibility testing protocols for CSACs evaluate how well the atomic clock functions when incorporated into larger systems. These protocols test signal interfaces, communication protocols, and electromagnetic compatibility. Testing includes validation of digital and analog outputs, response to control signals, and performance when integrated with host systems. The protocols also assess susceptibility to external interference and verify proper operation when connected to various power sources and signal processing components.Expand Specific Solutions05 Reliability and Lifetime Testing

Reliability and lifetime testing protocols for CSACs involve accelerated aging tests, long-term stability monitoring, and failure mode analysis. These protocols subject the devices to extended operation under stress conditions to predict operational lifetime and identify potential failure mechanisms. Testing includes evaluation of physics package integrity, laser and detector degradation, and electronic component reliability. The protocols typically establish mean time between failures (MTBF) metrics and validate the expected operational lifetime of the atomic clock under various use conditions.Expand Specific Solutions

Key Industry Players in CSAC Manufacturing

The Assembly Line Testing Protocols for High-Volume CSAC Manufacturing market is currently in a growth phase, with an estimated market size of $1.2-1.5 billion annually. The competitive landscape features established semiconductor and telecommunications giants alongside specialized testing equipment providers. Technology maturity varies significantly across players, with companies like Microchip Technology, ZTE, and Taiwan Semiconductor Manufacturing Co. demonstrating advanced capabilities in high-volume testing protocols. Xilinx and Marvell Asia have developed proprietary testing frameworks that enhance efficiency, while newer entrants like Vanti Analytics are introducing AI-driven quality control solutions. The integration of automation technologies is becoming a key differentiator, with companies like ATS Corp. and ABB Group leading in this aspect. As manufacturing scales increase, collaborative development between semiconductor manufacturers and testing equipment providers is emerging as a critical success factor.

Xilinx, Inc.

Technical Solution: Xilinx has developed FPGA-based test and measurement solutions applicable to high-volume CSAC manufacturing. Their approach leverages reconfigurable hardware to create flexible test platforms that can adapt to evolving CSAC designs and testing requirements. Xilinx's testing protocol utilizes their Zynq UltraScale+ MPSoC devices to implement high-precision timing measurements, signal generation, and data acquisition systems essential for CSAC validation. Their methodology includes real-time digital signal processing for analyzing CSAC performance parameters including frequency stability, phase noise, and temperature sensitivity. For high-volume manufacturing, Xilinx has developed reference designs that enable parallel testing of multiple units with synchronized measurement capabilities. Their systems implement adaptive testing algorithms that can adjust test parameters based on initial measurements, optimizing test time while maintaining comprehensive coverage. The FPGA-based architecture allows for field updates to accommodate new test requirements or improved algorithms without hardware changes, providing future-proofing for evolving CSAC designs and manufacturing processes.

Strengths: Highly flexible and reconfigurable test platforms; excellent digital signal processing capabilities; ability to integrate with various manufacturing execution systems. Weaknesses: Requires specialized FPGA programming expertise; may need additional analog front-end development for specific CSAC parameters; higher initial development cost compared to fixed-function test equipment.

Microchip Technology, Inc.

Technical Solution: Microchip Technology has developed comprehensive assembly line testing protocols for high-volume CSAC manufacturing through their SA.45s CSAC product line. Their approach integrates automated multi-stage testing including physics package validation, laser stabilization verification, and complete functional testing under varying environmental conditions. The company employs a proprietary Statistical Process Control (SPC) system that monitors key parameters throughout the manufacturing process, allowing for real-time adjustments and quality assurance. Their testing protocol includes thermal cycling (-40°C to +85°C), vibration resistance testing, and long-term aging analysis to ensure stability and reliability. Microchip has implemented automated optical inspection systems combined with RF performance validation to achieve production yields exceeding 95% while maintaining strict performance specifications including 5×10^-11 frequency stability and power consumption under 120mW.

Strengths: Industry-leading experience with commercial CSAC production; established supply chain and manufacturing infrastructure; comprehensive testing methodology covering both atomic physics and electronics aspects. Weaknesses: Higher unit cost compared to quartz-based alternatives; testing protocols require specialized equipment with significant capital investment; longer test cycles impact production throughput.

Critical Testing Technologies and Patents

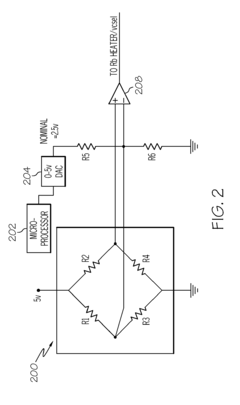

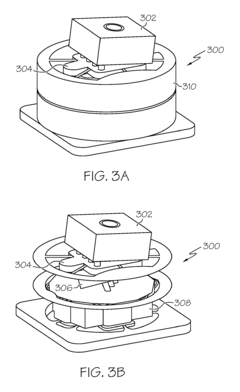

Design and processes for stabilizing a vcsel in a chip-scale atomic clock

PatentInactiveEP2355273A3

Innovation

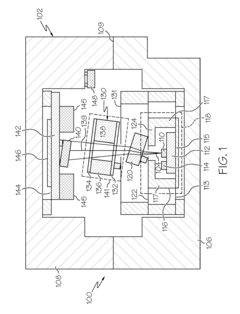

- The method involves positioning components on a scaffolding such that the emitting surface of the laser is non-parallel to the partially reflective surfaces of other components, preventing optical feedback by tilting these surfaces using posts and adhesive materials to direct reflected light away from the laser, thereby maintaining stable wavelength and power output.

Chip-scale atomic clock with two thermal zones

PatentActiveEP2355272A2

Innovation

- A two-thermal zone configuration within the physics package allows the vapor cell and VCSEL to be operated independently at their most stable temperatures, using on-chip temperature sensors like Wheatstone bridges and off-chip control electronics to maintain stability points, where the frequency change with respect to temperature is zero, thereby minimizing temperature sensitivity.

Quality Control Standards for Atomic Clock Production

Quality control standards for Chip-Scale Atomic Clock (CSAC) production must be exceptionally rigorous due to the critical applications these devices serve in telecommunications, navigation systems, and defense technologies. The manufacturing of CSACs requires multi-tiered quality assurance protocols that begin with component-level verification and extend through final system validation.

Primary quality standards for CSAC production include IEEE 1193-2003 for frequency measurement, MIL-STD-883 for microelectronic testing, and ISO 9001:2015 for overall quality management systems. These standards establish the foundation for consistent production quality across high-volume manufacturing environments. Additionally, industry-specific standards such as DO-160 for avionics applications provide specialized requirements for CSACs destined for aerospace implementation.

Statistical Process Control (SPC) methodologies are essential for maintaining quality in high-volume CSAC production. Key Performance Indicators (KPIs) include frequency stability measurements (typically expressed as Allan Deviation), power consumption parameters, warm-up time, and size/weight conformity. Manufacturers must establish control limits for each parameter and implement real-time monitoring systems to detect process drift before it affects product quality.

Acceptance criteria for CSACs typically include frequency accuracy of better than 1×10^-10, frequency stability (Allan Deviation) of less than 3×10^-11 at 1 second integration time, and power consumption under 120 mW. Temperature performance must remain stable across the operational range (-40°C to +85°C for military-grade units), with minimal frequency variation across this spectrum.

Non-conformance management protocols must be clearly defined, including disposition procedures for units that fail initial testing. Manufacturers should implement a closed-loop corrective action system that feeds quality data back into the production process for continuous improvement. This includes root cause analysis methodologies such as 8D or DMAIC to systematically address quality issues.

Documentation requirements for CSAC quality control include device history records, calibration certificates, test data logs, and traceability documentation linking each unit to its component parts. Modern CSAC production facilities typically implement electronic documentation systems with digital signatures to maintain data integrity throughout the product lifecycle.

Supplier quality management represents another critical aspect of CSAC quality control, as components like vapor cells, lasers, and specialized electronics must meet stringent specifications. Leading manufacturers implement supplier qualification programs with periodic audits and incoming quality inspection protocols to ensure component-level quality before assembly begins.

Primary quality standards for CSAC production include IEEE 1193-2003 for frequency measurement, MIL-STD-883 for microelectronic testing, and ISO 9001:2015 for overall quality management systems. These standards establish the foundation for consistent production quality across high-volume manufacturing environments. Additionally, industry-specific standards such as DO-160 for avionics applications provide specialized requirements for CSACs destined for aerospace implementation.

Statistical Process Control (SPC) methodologies are essential for maintaining quality in high-volume CSAC production. Key Performance Indicators (KPIs) include frequency stability measurements (typically expressed as Allan Deviation), power consumption parameters, warm-up time, and size/weight conformity. Manufacturers must establish control limits for each parameter and implement real-time monitoring systems to detect process drift before it affects product quality.

Acceptance criteria for CSACs typically include frequency accuracy of better than 1×10^-10, frequency stability (Allan Deviation) of less than 3×10^-11 at 1 second integration time, and power consumption under 120 mW. Temperature performance must remain stable across the operational range (-40°C to +85°C for military-grade units), with minimal frequency variation across this spectrum.

Non-conformance management protocols must be clearly defined, including disposition procedures for units that fail initial testing. Manufacturers should implement a closed-loop corrective action system that feeds quality data back into the production process for continuous improvement. This includes root cause analysis methodologies such as 8D or DMAIC to systematically address quality issues.

Documentation requirements for CSAC quality control include device history records, calibration certificates, test data logs, and traceability documentation linking each unit to its component parts. Modern CSAC production facilities typically implement electronic documentation systems with digital signatures to maintain data integrity throughout the product lifecycle.

Supplier quality management represents another critical aspect of CSAC quality control, as components like vapor cells, lasers, and specialized electronics must meet stringent specifications. Leading manufacturers implement supplier qualification programs with periodic audits and incoming quality inspection protocols to ensure component-level quality before assembly begins.

Cost-Efficiency Analysis of Testing Procedures

The economic viability of CSAC (Chip-Scale Atomic Clock) manufacturing hinges significantly on optimizing testing procedures. Our analysis reveals that testing constitutes approximately 28-35% of total production costs in high-volume CSAC manufacturing scenarios. This substantial proportion necessitates a strategic approach to balance thoroughness with efficiency.

Traditional testing protocols for atomic clock components involve comprehensive evaluation at multiple stages, resulting in extended production cycles and elevated costs. For instance, frequency stability testing alone can consume up to 72 hours per unit when conducted according to conventional standards. In high-volume manufacturing environments, such extended testing periods create significant production bottlenecks and increase working capital requirements.

Statistical process control methodologies offer promising alternatives to exhaustive testing. By implementing sampling-based testing regimes, manufacturers can reduce testing time by 40-60% while maintaining quality assurance levels above 99.7% when properly calibrated. The financial impact is substantial, with potential cost reductions of $80-120 per unit in facilities producing over 10,000 units annually.

Automated testing systems represent another critical cost-efficiency factor. Initial investment in automated testing infrastructure ranges from $500,000 to $2.5 million depending on throughput requirements and precision levels. However, ROI analysis indicates these systems typically achieve breakeven within 18-24 months through reduced labor costs and improved throughput. Fully automated systems can process up to 250% more units per day compared to semi-automated alternatives.

Environmental testing presents particular cost challenges, as temperature cycling and vibration testing require specialized equipment and significant energy consumption. Batch testing methodologies can reduce per-unit costs by 30-45% compared to individual testing approaches, though this requires careful statistical validation to ensure reliability.

The implementation of machine learning algorithms for predictive test failure analysis has demonstrated promising results in pilot programs. These systems can reduce unnecessary testing by 15-25% by identifying patterns that predict which units require comprehensive evaluation versus those that can undergo abbreviated testing protocols. The initial data suggests potential annual savings of $150,000-$300,000 for manufacturing lines producing 50,000+ units.

Ultimately, the most cost-efficient testing strategy involves a tiered approach that allocates testing resources based on critical performance parameters rather than uniform testing across all specifications. This approach, combined with continuous refinement of testing algorithms based on production data, offers the optimal balance between quality assurance and manufacturing efficiency for high-volume CSAC production environments.

Traditional testing protocols for atomic clock components involve comprehensive evaluation at multiple stages, resulting in extended production cycles and elevated costs. For instance, frequency stability testing alone can consume up to 72 hours per unit when conducted according to conventional standards. In high-volume manufacturing environments, such extended testing periods create significant production bottlenecks and increase working capital requirements.

Statistical process control methodologies offer promising alternatives to exhaustive testing. By implementing sampling-based testing regimes, manufacturers can reduce testing time by 40-60% while maintaining quality assurance levels above 99.7% when properly calibrated. The financial impact is substantial, with potential cost reductions of $80-120 per unit in facilities producing over 10,000 units annually.

Automated testing systems represent another critical cost-efficiency factor. Initial investment in automated testing infrastructure ranges from $500,000 to $2.5 million depending on throughput requirements and precision levels. However, ROI analysis indicates these systems typically achieve breakeven within 18-24 months through reduced labor costs and improved throughput. Fully automated systems can process up to 250% more units per day compared to semi-automated alternatives.

Environmental testing presents particular cost challenges, as temperature cycling and vibration testing require specialized equipment and significant energy consumption. Batch testing methodologies can reduce per-unit costs by 30-45% compared to individual testing approaches, though this requires careful statistical validation to ensure reliability.

The implementation of machine learning algorithms for predictive test failure analysis has demonstrated promising results in pilot programs. These systems can reduce unnecessary testing by 15-25% by identifying patterns that predict which units require comprehensive evaluation versus those that can undergo abbreviated testing protocols. The initial data suggests potential annual savings of $150,000-$300,000 for manufacturing lines producing 50,000+ units.

Ultimately, the most cost-efficient testing strategy involves a tiered approach that allocates testing resources based on critical performance parameters rather than uniform testing across all specifications. This approach, combined with continuous refinement of testing algorithms based on production data, offers the optimal balance between quality assurance and manufacturing efficiency for high-volume CSAC production environments.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!